Paper 9

Entered: January 4, 2017

## UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_\_

## BEFORE THE PATENT TRIAL AND APPEAL BOARD

TAIWAN SEMICONDUCTOR MANUFACTURING COMPANY, LTD., Petitioner,

v.

GODO KAISHA IP BRIDGE 1, Patent Owner.

Cases IPR2016-01246 and IPR2016-01247 Patent 7,126,174 B2

Before JUSTIN T. ARBES, MICHAEL J. FITZPATRICK, and JENNIFER MEYER CHAGNON, *Administrative Patent Judges*.

ARBES, Administrative Patent Judge.

DECISION Institution of *Inter Partes* Review 37 C.F.R. § 42.108

Petitioner Taiwan Semiconductor Manufacturing Company, Ltd. filed two Petitions requesting *inter partes* review of claims 1–12 and 14–18 of U.S. Patent No. 7,126,174 B2 (Ex. 1001, "the '174 patent")<sup>1</sup> pursuant to 35 U.S.C. § 311(a). Patent Owner Godo Kaisha IP Bridge 1 filed a Preliminary Response and Motion for District Court-Type Claim Construction in each proceeding, as listed in the following chart.

| Case Number   | Challenged<br>Claims            | Petition                  | Preliminary<br>Response                  | Motion                       |

|---------------|---------------------------------|---------------------------|------------------------------------------|------------------------------|

| IPR2016-01246 | 1–3, 5–7,<br>9–12, and<br>14–18 | Paper 2<br>("Pet.")       | Paper 7<br>("Prelim.<br>Resp.")          | Paper 6<br>("Mot.")          |

| IPR2016-01247 | 1, 4, 5,<br>8–12, 14,<br>and 16 | Paper 2<br>("-1247 Pet.") | Paper 7<br>("-1247<br>Prelim.<br>Resp.") | Paper 6<br>("-1247<br>Mot.") |

Pursuant to 35 U.S.C. § 314(a), the Director may not authorize an *inter partes* review unless the information in the petition and preliminary response "shows that there is a reasonable likelihood that the petitioner would prevail with respect to at least 1 of the claims challenged in the petition." For the reasons that follow, we institute an *inter partes* review as to claims 1–12 and 14–18 of the '174 patent on certain grounds of unpatentability. We also exercise our authority under 35 U.S.C. § 315(d) to consolidate the two proceedings and conduct the proceedings as one trial.

<sup>&</sup>lt;sup>1</sup> Unless otherwise specified with the "-1247" prefix, references to exhibits herein are to those filed in Case IPR2016-01246.

## I. BACKGROUND

## A. The '174 Patent<sup>2</sup>

The '174 patent discloses a "semiconductor device including transistors and connection[s] between the transistors for constituting [a large-scale integration (LSI) integrated circuit (IC)] with high integration and a decreased area." Ex. 1001, col. 1, ll. 13-16. At the time of the '174 patent, various improvements had been made in semiconductor manufacturing due to "increasing demands for more refinement of the semiconductor device." *Id.* at col. 1, 11. 17–22. The '174 patent describes one known method of forming an isolation structure (for shielding devices from each other on a substrate) known as Local Oxidation of Silicon (LOCOS), which was "conventionally adopted in view of its simpleness and low cost." Id. at col. 1, ll. 22-25. The LOCOS isolation method involves selective oxidation of a silicon substrate, but has a disadvantage in that it results in a "bird's beak" overhanging area of silicon dioxide. *Id.* at col. 1, 11. 29–31. "As a result, the dimension of a transistor is changed because an insulating film of the isolation invades [the] transistor region against the actually designed mask dimension." *Id.* at col. 1, 11. 31–34. According to the '174 patent, compared to LOCOS, "trench buried type isolation" (or "trench isolation") was determined to be "more advantageous for manufacturing a refined semiconductor device." *Id.* at col. 1, 11. 25–28.

The '174 patent describes a "conventional semiconductor device" with a trench isolation structure "whose top surface is flattened so as to be at the same level as the top surface of the silicon substrate" (as shown in

<sup>&</sup>lt;sup>2</sup> The '174 patent is a division of a series of U.S. applications ultimately descending from a U.S. application filed on July 24, 1996, and claims the benefit of foreign applications filed on July 27 and December 19, 1995.

Figure 17) or whose top surface is higher than the surface of the silicon substrate (as shown in Figure 20(e)). *Id.* at col. 1, 1. 52–col. 2, 1. 6 (structure 2b), col. 4, 1. 16–col. 5, 1. 11 (trench isolation 105a). By using the "conventional trench isolation" structure, "the dimensional change of the source/drain region can be suppressed because the bird's beak" created using LOCOS is avoided. *Id.* at col. 4, 1l. 16–19, col. 5, 1l. 12–17. According to the '174 patent, using the trench isolation method caused various problems of its own due to the etching required. *Id.* at col. 5, 1l. 21–58.

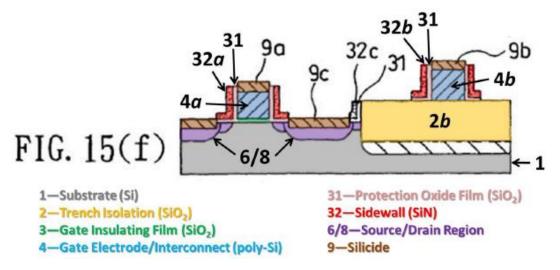

The '174 patent describes various embodiments of semiconductor devices and methods of manufacturing the same. The manufacturing process for Embodiment 10 is depicted in the sequence of Figures 12, 13(a)–(e), and 15(a)–(f). *Id.* at col. 21, ll. 33–34, col. 26, ll. 36–45 (referring to the previously described process of Embodiment 8). Petitioner provides on page 13 of the Petition a colored and annotated version of Figure 15(f) of the '174 patent, reproduced below, which is consistent with the '174 patent's disclosure.

The figure above depicts a device including isolation 2b, which is the result of forming a trench in silicon substrate 1 and filling it with insulating

material. *Id.* at col. 21, ll. 39–50, col. 22, ll. 34–44. "[E]lectrode sidewalls 32a, interconnection sidewalls 32b and a step sidewall 32c each having an L-shape remain on the sides of the gate electrode 4a, the gate interconnection 4b and the step portion, respectively." *Id.* at col. 27, ll. 4–8. The '174 patent describes various advantages of forming "L-shaped sidewalls" in the manner disclosed. *Id.* at col. 27, ll. 34–47.

### B. Illustrative Claim

Claim 1 of the '174 patent recites:

- 1. A semiconductor device, comprising:

- a trench isolation surrounding an active area of a semiconductor substrate;

- a gate insulating film formed over the active area;

- a gate electrode formed over the gate insulating film;

- first L-shaped sidewalls formed over the side surfaces of the gate electrode;

first silicide layers formed on regions located on the sides of the first L-shaped sidewalls within the active area

an interconnection formed on the trench isolation; and

second L-shaped sidewalls formed over the side surfaces of the interconnection.

### C. The Prior Art

Petitioner relies on the following prior art:

- U.S. Patent No. 4,506,434, issued Mar. 26, 1985 (Ex. 1010, "Ogawa");

- U.S. Patent No. 5,021,353, issued June 4, 1991 (Ex. 1017, "Lowrey");

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.