US007074709B2

## (12) United States Patent

Young

(10) Patent No.: US 7,074,709 B2

(45) **Date of Patent:** Jul. 11, 2006

#### (54) LOCALIZED DOPING AND/OR ALLOYING OF METALLIZATION FOR INCREASED INTERCONNECT PERFORMANCE

(75) Inventor: Bradley Scott Young, Irving, TX (US)

(73) Assignee: Texas Instruments Incorporated,

Dallas, TX (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 258 days.

(21) Appl. No.: 10/288,974

(22) Filed: Nov. 6, 2002

(65) Prior Publication Data

US 2004/0002211 A1 Jan. 1, 2004

#### Related U.S. Application Data

- (60) Provisional application No. 60/392,715, filed on Jun. 28, 2002.

- (51) **Int. Cl.**

**H01L 21/4763** (2006.01) **H01L 21/44** (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,955,688 | Α            | * | 9/1990  | Chapin et al      | 385/123 |

|-----------|--------------|---|---------|-------------------|---------|

| 4,995,698 | Α            | * | 2/1991  | Myers             | 385/147 |

| 5,221,060 | Α            | * | 6/1993  | Couvillion et al  | 242/159 |

| 5,594,829 | Α            | * | 1/1997  | LoStracco et al   | 385/134 |

| 5,822,065 | $\mathbf{A}$ | * | 10/1998 | Mark et al        | 356/465 |

| 6,023,100 | Α            |   | 2/2000  | Tao et al.        |         |

| 6,268,291 | В1           |   | 7/2001  | Andricacos et al. |         |

| 6,376,353 | В1           | * | 4/2002  | Zhou et al        | 438/612 |

| 6,387,806 | В1           | * | 5/2002  | Wang et al        | 438/687 |

| 6,420,262    | В1 | 7/2002    | Farrar 438/652     |

|--------------|----|-----------|--------------------|

| 2002/0076925 | A1 | 6/2002    | Marieb et al.      |

| 2003/0203617 | A1 | * 10/2003 | Lane et al 438/627 |

#### FOREIGN PATENT DOCUMENTS

| FR | 2816758 A1   | 5/2002  |

|----|--------------|---------|

| JР | 2000150522   | 5/2000  |

| WO | WO 0197283 A | 12/2001 |

| WO | WO 0245142   | 6/2002  |

#### OTHER PUBLICATIONS

C. P. Wang et al., Binary Cu-alloy layers for Cu-interconnections reliability improvement (3 pp.).

E. T. Ogawa et al., Stress-Induced Voiding Under Vias Connected To Wide Cu Metal Leads (10 pp.).

Development of electroless copper metallisation, [online] Retrieved from the Internet:<URL: http://www.hut.fi/Units/Electron/Research/res2000/ElectrolessCu/electroless\_copper.html (3 pp.).

\* cited by examiner

Primary Examiner—William M. Brewster (74) Attorney, Agent, or Firm—Jacqueline J. Garner; W. James Brady, III; Frederick J. Telecky, Jr.

#### (57) ABSTRACT

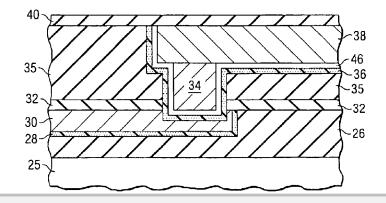

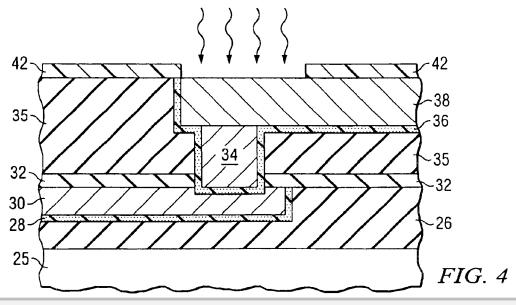

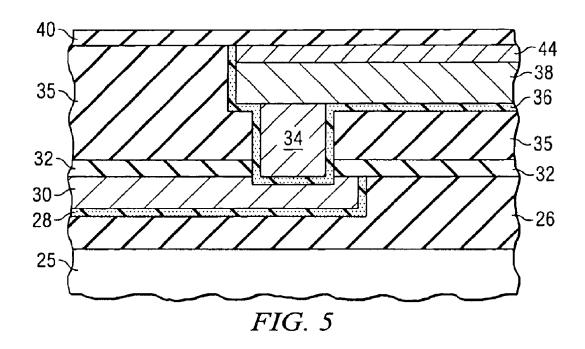

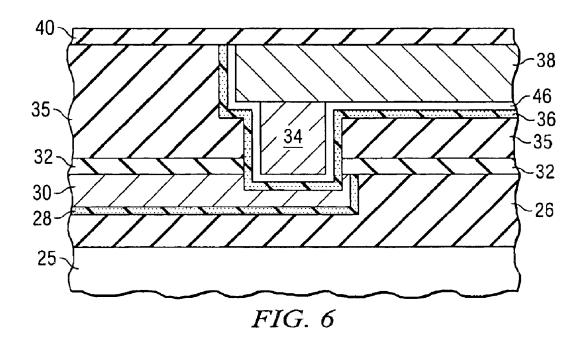

Methods and compositions are disclosed for modifying a semiconductor interconnect layer to reduce migration problems while minimizing resistance increases induced by the modifications. One method features creating trenches in the interconnect layer and filling these trenches with compositions that are less susceptible to migration problems. The trenches may be filled using traditional vapor deposition methods, or electroplating, or alternately by using electroless plating methods. Ion implantation may also be used as another method in modifying the interconnect layer. The methods and compositions for modifying interconnect layers may also be limited to the via/interconnect interface for improved performance. A thin seed layer may also be placed on the semiconductor substrate prior to applying the interconnect layer. This seed layer may also incorporate similar dopant and alloying materials in the otherwise pure metal.

#### 17 Claims, 3 Drawing Sheets

IP Bridge Exhibit 2009

TSMC v. IP Bridge IPR2016-01246

Jul. 11, 2006

1

#### LOCALIZED DOPING AND/OR ALLOYING OF METALLIZATION FOR INCREASED INTERCONNECT PERFORMANCE

## CROSS-REFERENCE TO RELATED APPLICATIONS

This application is entitled to the benefit of a provisional patent application Ser. No. 60/392,715 filed Jun. 28, 2002.

STATEMENT REGARDING FEDERALLY SPONSORED RESEARCH OR DEVELOPMENT

Not applicable.

#### BACKGROUND OF THE INVENTION

#### 1. Technical Field of the Invention

The present invention generally relates to semiconductor processing techniques. More particularly, the present invention relates to selective modification of the interconnects of an integrated circuit to achieve improved mechanical and electrical properties.

#### 2. Description of Related Art

The semiconductor technology central to the modern integrated circuit ("IC") has been developing for over a century. In the late nineteenth century, the special properties of the semiconductor selenium were first observed and recognized. The field of semiconductor physics advanced rapidly and the first transistor was proposed in the 1930s. However, not until the late 1940s was a functional point contact transistor constructed. The IC, which employs a plurality of circuit elements in a monolithic semiconductor substrate rather than using discrete components, was first developed in the late 1950s by Jack Kilby at Texas Instruments, Inc. and by Robert Noyce at Fairchild Semiconductor Corporation.

Since the late 1950s, IC technology has evolved rapidly and has revolutionized virtually every industry and capacity in which ICs are used. Today's ICs frequently employ hundreds of thousands or even millions of transistors and 40 highly complex, multi-layered architectures. The proliferation of electronics in general, and ICs in particular, has resulted in large part from the ability to increase circuit functionality while simultaneously reducing device cost and size. An important catalyst for these improvements has been 45 advances in semiconductor processing technologies. Although a wide array of semiconductor companies and products exist, for the most part, semiconductor processing is completed through a series of common steps. Semiconductor processing begins with a wafer or substrate, upon 50 which various processing techniques are used to construct circuit elements such as transistors, resistors and capacitors. The formation of circuit elements comprises a process called doping—i.e., deliberately introducing impurities into certain regions of the monolithic crystalline substrate. After the 55 circuit elements are formed, a series of conductive and insulating layers are used to form connections, called interconnects, between the appropriate circuit elements.

As increasingly complex ICs utilize an increasing number of circuit elements, more electrical interconnects between 60 circuit elements and a greater number of conductor-insulator layers are required. A chief objective of semiconductor processing is the minimization of interconnect electrical resistance. Increased resistance is undesirable because as the interconnect resistance between two electrical devices 65

- 2

overall speed at which the IC functions. Additionally, increased resistance also increases the amount of overall power consumed by the IC.

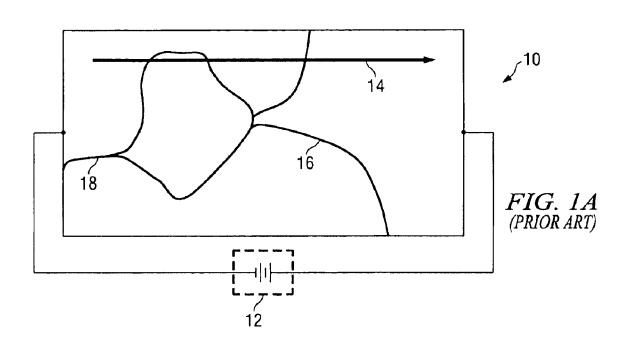

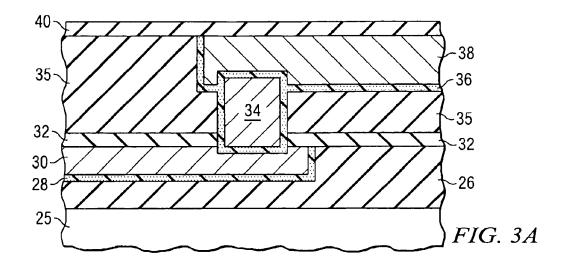

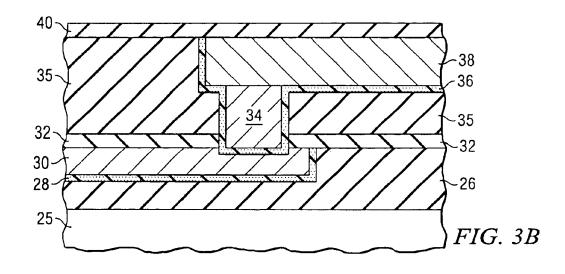

Another important consideration is the mechanical stability of the interconnects, which is negatively impacted by a phenomenon known as electromigration, the migration of atoms in the interconnect induced by applying an electric potential across the interconnect. The principle of electromigration is depicted graphically in FIGS. 1A, 1B and 2. FIG.  $_{10}$  1A shows an electron flow 14 in a conductor 10 due to a potential difference supplied by a battery 12. The momentum of the electrons in the electron flow 14 causes atoms in the conductor 10 to migrate in the same direction as the electron flow 14. Grain boundaries occur at the intersection between two crystalline grains. The intersection of three or more crystalline grains may be susceptible to electromigration. Consequently, grain boundary 16 and intersection point 18 are likely places for electromigration damage, but usually at higher activation energy than surface diffusion in the case of Cu metallization.

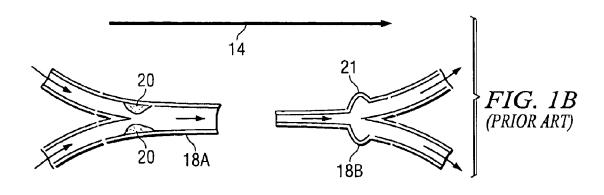

FIG. 1B shows electron flow 14 through grain boundary intersection points 18A and 18B. In intersection point 18A, electron flow 14 from two grains is merging into a single grain, resulting in the formation of void 20. In intersection point 18B, in contrast, electron flow 14 from a single grain is diverging into two different grains, resulting in the formation of hillock 21.

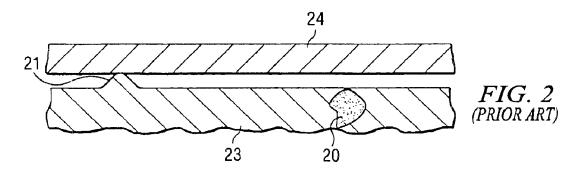

Conductors are often processed using aluminum with a small concentration (i.e., less than about 2% by weight), of Copper ("Cu"). More recently, pure Cu has been the metal of choice for producing metal interconnect on ICs. To contain the Cu and keep it from entering and moving within the glass dielectric layers and the active areas of the substrate, barrier layers surround the Cu. These barriers are carefully chosen so as to not cause adhesion problems between the metallization and the encapsulating/insulating dielectric layers. With the advancement of technology, new materials are sought to reduce parasitic capacitance and resistance for greater circuit performance and lower power consumption. These new materials possess lower dielectric constants but also lower thermal conductance. This reduces the efficiency with which heat is transferred to the substrate. Also, these material are more brittle and mechanically less robust than the more traditional silicone dioxide. Lower mechanical strength means less resistance to cracking and possibly a greater tendency toward electromigration, due to tensile forces on the metallization or lower strength in general. The surface between the Cu lead and the barrier is observed to be a path for metal movement of relatively low activation energy. Voids can nucleate and/or grow at this surface, and the other interfacial surfaces. Metal will electromigrate, that is, drift or diffuse in the direction of electron flow under electrical bias. Voids, depletion of metal in an area, can form near the electron source. These voids are usually paired downstream with hillocks, an accumulation of metal. Hillocks can cause the formation of metal filaments into the dielectric, that is, unwanted paths of current leakage, and even cracking of the barrier and/or dielectric.

The impact on circuit performance of void 20 and hillock 21 in FIG. 1 is depicted graphically in FIG. 2. FIG. 2 shows interconnect 23 and parallel interconnect 24, which is desirably electrically isolated from interconnect 23. Proper circuit performance requires not only high electrical conductance along interconnect 23 and interconnect 24 but a high electrical resistance between them. Void 20 and hillock 21

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.