## **VERIFICATION OF TRANSLATION**

I, Yukiko Toyoda Buntin

of 1950 Roland Clarke Place

Reston, VA 20191

declare that I am well acquainted with both the Japanese and English languages, and that the attached is an accurate partial translation, to the best of my knowledge and ability, of Japanese Patent Application Publication No. H9-120964 (translation of first page only), published May 6, 1997.

I further declare that all statements made herein of my own knowledge are true and that all statements made on information and belief are believed to be true; and further that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of Title 18 of the United States Code and that such willful false statements may jeopardize the validity of the above-captioned application or any patent issued thereon.

Signature.

Yukiko Toyoda Buntin

Date\_ 6-22-2017

(19) Japan Patent Office (JP) (12) Patent Publication (A)

(11) Patent Application Publication No:

H9-120964

(43) Publication Date: May 6, 1997

| (51) Int.Cl. <sup>6</sup> | Classification Symbol | JPO Ref. FI |              | Technical display area |

|---------------------------|-----------------------|-------------|--------------|------------------------|

| H 01L 21/3205             | H01L                  | 21/88       | $\mathbf{J}$ |                        |

| 21/3065                   |                       | 21/302      | $\mathbf{J}$ |                        |

| 21/768                    |                       | 21/88       | P            |                        |

|                           |                       | 21/90       | A            |                        |

Examination Request – None – Number of Claims 16 OL (19 pages total)

(21) Application No: H7-278546

(22) Filing Date: October 26, 1995

(71) Applicant: 000005821

Matsushita Electric Industrial Co., Ltd. 1006, Oaza Kadoma, Kadoma-shi, Osaka

(72) Inventor: Tetsuya UEDA

c/o Matsushita Electric Industrial Co., Ltd. 1006, Oaza Kadoma, Kadoma-shi, Osaka

(72) Inventor: Satoshi UEDA

c/o Matsushita Electric Industrial Co., Ltd. 1006, Oaza Kadoma, Kadoma-shi, Osaka

(74) Agent: Patent Attorney: Hiroshi MAEDA (and 2 others)

(54) Title of Invention

FORMATION METHOD FOR WIRING AND SEMICONDUCTOR ELEMENT

## (57)【要約】

【課題】 フォトリソグラフィーの解像限界を超えたピッチ幅を有する微細配線層の形成方法を提供する。

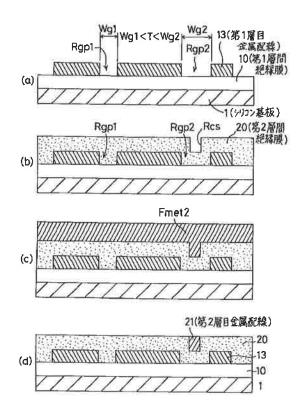

【解決手段】 シリコン基板1上に第1層間絶縁膜10 を堆積し、さらにその上に第1金属膜からなる第1層目金属配線13を形成する。第1層目金属配線13の各残存部の間には、所定値Tよりも小さい間隙Wg1を有する第1間隙部Rgp1と、所定値Tよりも大きい間隙Wg2を有する第2間隙部Rgp2とが形成されている。基板の全面上に、1/2Tよりも薄い第2層間絶縁膜20を堆積すると、第1間隙部Rgp1は第2層間絶縁膜20によって埋め込まれ、第2間隙部Rgp2の上方には溝部Rcsが形成される。その後、平坦化を行うことなく第2金属膜下met2を堆積し、全面エッチバックして溝部に第2層目金属配線21を残す。この各配線13,21の間隔はリソグラフィーの解像限界よりも微細となる。