# Arsenic dopant mapping in State-of-the-art semiconductor devices using electron energy loss spectroscopy

A con en fo owng hspage was up oaded by R. an e on 01 Ap 2014.

The user has requested enhancement of the down oaded f e. A n text references under ned n b ue are added to the or g na document and are nked to pub cat ons on ResearchGate ett ng you access and read them mmed ate y.

#### Contents lists available at ScienceDirect

#### Micron

### Arsenic dopant mapping in state-of-the-art semiconductor devices using electron energy-loss spectroscopy

Germain Servanton\*, Roland Pantel

STMicroelectronics, 850 rue Jean Monnet, F-38926 Crolles, France

ARTICLE INFO

Article history: Received 18 August 2009 Received in revised form 2 October 2009 Accepted 3 October 2009

Keywords: STEM EELS Arsenic dopant mapping Silicon semiconductors CMOS BiCMOS

#### ABSTRACT

Knowledge of the dopant distribution in nanodevices is critical for optimising their electrical performances. We demonstrate with a scanning transmission electron microscope the direct detection and two dimensional distribution maps of arsenic dopant in semiconductor silicon devices using electron energy loss spectroscopy. The technique has been applied to 40 45 nm high density static random access memory and to  $n \ p \ n$  BiCMOS transistors. The quantitative maps have been compared with secondary ion mass spectrometry analysis and show a good agreement. The sensitivity using this approach is in the low  $10^{19} \ \text{cm}^{-3}$  range with a spatial resolution of about 2 nm.

© 2009 Elsevier Ltd. All rights reserved.

#### 1. Introduction

The expansion of smart electronic systems for customer applications has been stimulated by the continuous progress of device performances and integration density. One of the key processes in optimising these silicon devices is to adapt the three dimensional dopant distribution to maximize the device electrical characteristics. This is obtained by combining the physical doping processes (ion implantation, thermal annealing) to elaborated computer simulations. However due to the low concentration level of impurities there is not up to now a simple technique that can be used to verify at the nanometre scale the actual dopant distribution. This is why the task of visualising the dopants in silicon nanodevices has been highlighted by the international technology roadmap for semiconductors (ITRS, 2009) as an objective to aid the continuous development of silicon devices. To face this challenge, numerous techniques have been developed and evaluated during the last ten years either with a nanometric resolution (Castell et al., 2003) or at the atomic scale (Voyles et al., 2002). For the analysis of electrically active dopants, the near field microscopy methods, i.e. scanning spreading resistance (SSRM) or capacitance (SCM) microscopy (Eybens et al., 2007) and electron holography (Twitchett et al., 2003; Cooper et al., 2007) have been shown to be the most promising techniques. For chemical dopant analysis, the three dimensional atom probe tomography (APT) (Thompson et al., 2005, 2007) gives unsurpassed spatial resolution (nearly atomic) and sensitivity below 10<sup>19</sup> cm<sup>3</sup>. However for advanced CMOS technology nodes (45 and 32 nm) and inside high density circuits such as static random access memory (SRAM), none of these techniques are presently suitable. Indeed, the APT technique is limited by tip preparation difficulties added to insulator materials problems inside the SRAM devices (Kölling and Vandervorst, 2009). The direct detection of arsenic dopant using scanning transmission electron microscopy (STEM) energy dis persive X ray spectroscopy (EDX) has also been tested (Topuria et al., 2001) and was recently improved by lowering primary beam energy and applied in 45 nm *n* MOS transistors but with a limited resolution (Servanton et al., 2009, Submitted for publication).

In this paper we demonstrate a significant progress in quantitative arsenic dopant mapping by using electron energy loss spectroscopy (EELS) in STEM mode. The STEM EELS technique

In this paper we demonstrate a significant progress in quantitative arsenic dopant mapping by using electron energy loss spectroscopy (EELS) in STEM mode. The STEM EELS technique consists of focusing and scanning an intense electron probe on a sample. The direct ionization of core electrons from the atoms cause an energy loss in the detected electrons which can then be quantified as these energy losses are specific to different atom species. The improvements presented come from the high electron doses per pixel without saturating the detector using a low primary electron beam energy (120 keV instead of 200 keV); i.e. below the knock on damage threshold for silicon (Servanton et al., 2009, Submitted for publication). In addition, the higher electron collection efficiency (about 80%) with high current (8 nA) using STEM EELS makes this method of dopant profiling more suitable than STEM EDX (2% efficiency with a current lower than 1 nA to avoid the detector saturation). Importantly, STEM EELS is

<sup>\*</sup> Corresponding author.

E-mail address: germain.servanton@st.com (G. Servanton).

compatible with focused ion beam (FIB) TEM lamella preparation that enables a large thickness range to be examined (from 30 to 200 nm). Such thin lamella can be extracted from high density 32 nm SRAM circuits. The STEM EELS arsenic maps can be quantified and the sensitivity is estimated to be near the low  $10^{19}\,\mathrm{cm}^{-3}$  range. The pixel sampling is high for reasonable experimental times (4000 pixels/h) and the spatial resolution is around 2 nm.

Here we present experimental data from n MOS transistors integrated in high density circuits (45  $\,$  40 nm SRAM) and will show that exact arsenic distribution limit can be obtained around the CMOS source/drain and LDD regions. The examination of 90 nm bipolar transistor compatible MOS (BiCMOS) (Avenier et al., 2008) show high arsenic fluctuations in the arsenic doped silicon emitter. Finally, quantitative STEM EELS measurements have been compared to secondary ion mass spectrometry (SIMS) experiments which show good agreement.

#### 2. Experimental details

These experiments have been performed using an FEI S Twin TEM TECNAI F20 equipped with a field emission gun (FEG) electron source and a Gatan energy filter GIF200 with  $1K \times 1K$  CCD camera. The samples were prepared using FIB milling (Gallium ions accelerated at 30 keV) with a final cleaning stage at 5 keV. During STEM EELS mapping, the sample drift is actively compensated every minute using a cross correlation with an initial STEM image. The EELS experiments, method and data processing principles for arsenic signal extraction and arsenic doped silicon quantification are described in references (Pantel et al., 2008; Servanton et al., 2009, Submitted for publication).

#### 3. Results

#### 3.1. Arsenic dopant maps in 45 40 nm CMOS transistors

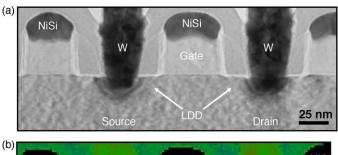

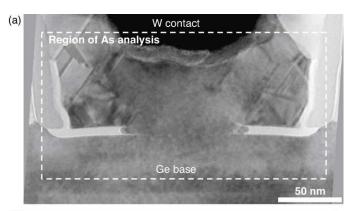

Our first example shows that STEM EELS is compatible with state of the art semiconductor nodes, such as the analysis of high density 40 nm SRAM (0.3  $\mu$ m<sup>2</sup> bitcell area). Fig. 1(a) presents a

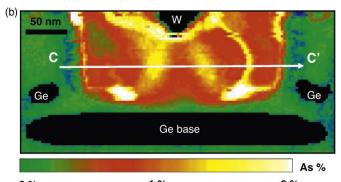

**Fig. 1.** (a) TEM bright field image of 40 nm n-MOS transistors in a SRAM device. (b) Arsenic concentration distribution obtained using STEM EELS for the same SRAM

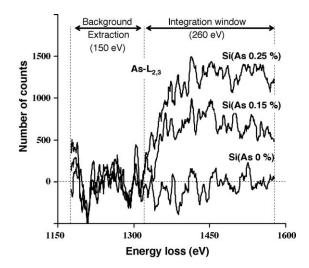

**Fig. 2.** As- $L_{2.3}$  EELS signals extracted from three single pixels (Si(As 0%), Si(As 0.15%) and Si(As 0.25%)).

TEM bright field image of a FIB cross section of n MOS transistors. The TEM contrast reveals only materials with different compositions (nickel silicide, tungsten) but not the arsenic dopants inside silicon, as their relative concentration is small. Fig. 1(b) presents an arsenic concentration distribution map, for the same sample, obtained using STEM EELS. The colour map, acquired during 2 h for  $140 \times 60$  pixels, clearly shows areas with different arsenic concentrations such as the low doped drains (LDDs), the source/drain junction below the nickel silicide, the gate side walls and the top of spacers. The two dimensional quantitative distribution,

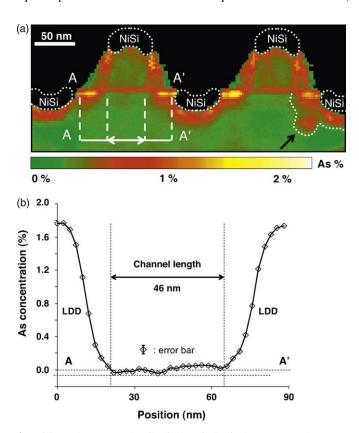

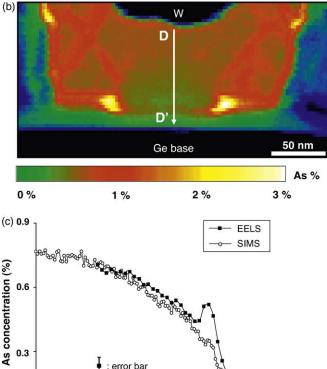

**Fig. 3.** (a) Arsenic concentration distribution obtained using STEM EELS in a 45 nm SRAM with high implantation process (150  $\times$  60 pixels, acquisition time 2.2 h). (b)

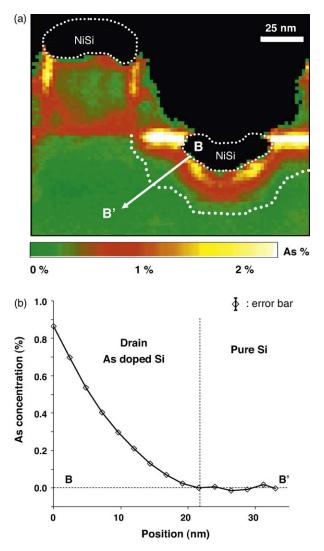

**Fig. 4.** (a) STEM EELS arsenic concentration distribution showing a magnified area covering the gate and drain of a n-MOS transistor in 45 nm SRAM device ( $80 \times 80$  pixels, acquisition time 1.5 h). The arsenic distribution limit is drawn (dot line). (b) Arsenic concentration profile (raw data) extracted from the map of Fig. 3(a) along BB'.

when compared with device processing models is as expected. The experimental results show that the transistor gates are uniformly doped. Additionally, it can be seen that the spacers have played their role by protecting the LDD (first implantation) during the second source/drain implantation. The smooth arsenic extension limit (pixels where arsenic concentration is near to zero) shown in Fig. 1(b) (left) indicates a high quality dopant implantation process. The EELS background extraction that has been optimised for low arsenic doped silicon (Servanton et al., 2009, Submitted for publication) fails in heavy alloys (NiSi, SiGe) which are displayed in black in the following figures.

Fig. 2 displays typical As  $L_{2,3}$  EELS signals extracted from three single pixels (Si(As 0%), Si(As 0.15%) and Si(As 0.25%)). The background extrapolation and the signal windows are shown (150 and 260 eV width, respectively). For the Si(As 0.15%), the total number of electrons integrated in the As  $L_{2,3}$  window is about  $700 \times 260$ , i.e.  $1.8 \times 10^5$  electrons. This suggests that the signal over noise determined by the number of detected electrons  $(S/N - \sqrt{1.8 \times 10^5} \approx 4.10^2)$  is high for Si As 0.15% and will stay acceptable even if one decreases the dose by a factor of ten

**Fig. 5.** (a) TEM bright field image of n-p-n 90 nm BiCMOS. (b) Arsenic concentration distribution map obtained using STEM EELS in the same area:  $(150 \times 60 \text{ pixels}, \text{acquisition time } 2.2 \text{ h})$ . (c) Arsenic concentration profile extracted along CC'.

tion error. The background extraction precision depends on the sample quality (possible Ga contamination due to FIB preparation) and on the EELS detector. Cumulated with the As/Si sensitivity factor around  $14.0 \pm 0.3$ , we estimated the error bar in the arsenic detection to be  $\pm 0.05\%$  (see displays in Figs. 3b, 4b, 5c and 6c).

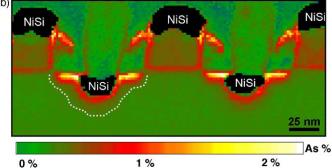

The second application shows the analysis of a 45 nm SRAM with an extremely high implantation dose which has been processed in order to study the instability of the nickel silicide (commonly called encroachment) (Imbert et al., 2009). The process was stopped after the silicide formation. Fig. 3(a) shows a STEM EELS arsenic concentration distribution map acquired during 2.2 h for  $150 \times 60$  pixels. On the right of the figure, a high concentration of arsenic separated from the source/drain is detected and the arsenic distribution limit shows an unexpected arsenic extension (see black arrow in Fig. 3(a)). This is probably due to arsenic segregation at silicon defects that were created at the end of range (FOR) implantation. These defects observed using TEM imaging on

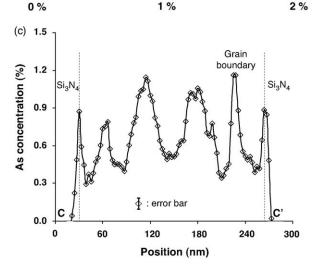

**Fig. 6.** (a) TEM bright field image of another n-p-n 90 nm BiCMOS showing stacking faults at the emitter edges. (b) Arsenic concentration distribution map obtained using STEM EELS in the same area  $(130 \times 60 \text{ pixels}, \text{ acquisition time } 2 \text{ h})$ . (c) Comparison of an arsenic concentration profile extracted along DD' and SIMS profile obtained in larger test structure from the same wafer.

Position (nm)

60

D

80

100

the source (drain) due to implantation angle. Arsenic segregation on same defects were also observed using STEM EDX (Servanton et al., 2009, Submitted for publication). As indicated on the left of Fig. 3(a), a line profile can be extracted in the n MOS channel from LDD (A) to LDD (A'). The result is displayed in Fig. 3(b), with a chemical channel length estimation of 46 nm. Note that this profile presents the raw data (no smoothing) and that the detectable arsenic level is below 0.1%, i.e. approximately  $1 \times 10^{19}$  at cm $^{-3}$ .

Fig. 4(a) shows a STEM EELS arsenic distribution map, acquired during 1.5 h for  $80 \times 80$  pixels, zoomed on to one single n MOS transistor extracted from a 45 nm SRAM identical to the one shown in Fig. 3(a). In this case, the poly crystalline silicon gate seems to be

concentration profiles can be extracted such as indicated by BB' in Fig. 4(b). The point where the arsenic concentration curve crosses zero (near  $1.10^{19}$  at cm  $^{3}$ ) is about the arsenic extension limit. By using this process, the As dopant extension limit has been drawn (dot line) in Fig. 4(a).

#### 3.2. Arsenic dopant maps in 90 nm BiCMOS transistors

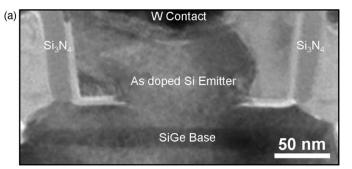

STEM EELS arsenic maps can be applied to any device integrating arsenic doped mono or poly crystalline silicon and in particular to BiCMOS transistors. Fig. 5(a) presents a TEM bright field image of such a n p n bipolar device (the emitter is arsenic doped silicon and the base is  $Si_{0.78}Ge_{0.22}$  boron doped). In the emitter part, the contrast shows a grain boundary between the mono crystalline silicon at centre and the poly crystalline silicon to the right. While the arsenic distribution cannot be seen in this image, Fig. 5(b) shows the STEM EELS arsenic map, acquired during 2.2 h for  $150 \times 60$  pixels, which corresponds exactly to the same area than Fig. 5(a). The emitter is highly doped but, as it was thought to be uniform following SIMS measurements, strong concentration variations are revealed. Fig. 5(c) shows a profile of arsenic distribution along the line indicated CC'. Six maxima are observed whose variations are more than a factor two. Arsenic depletion near the bottom centre of the emitter is observed surrounded by two maxima. It is likely that the arsenic atoms might be poorly incorporated in the silicon mono crystalline central regions during the epitaxy process as these dopants tend to concentrate at the defects in the lateral areas. After annealing, the arsenic has then diffused to the grain boundaries and to the external interfaces.

Fig. 6(a) shows a TEM bright field image of a different BiCMOS transistor. Silicon crystal planar defects are observed in the quasi mono crystalline part of the emitter. The arsenic STEM EELS map presented in Fig. 6(b) (2 h acquisition time for  $130 \times 60$  pixels) highlights arsenic segregation at these stacking faults. The emitter base interface shows a high arsenic concentration as confirmed in Fig. 6(c) which presents the arsenic concentration profile extracted along DD'. This profile is compared to SIMS analysis which has been carried out on large test structure found on the same BiCMOS wafer. The measured profile validates our STEM EELS quantification method. An arsenic concentration peak is detected at the emitter base interface in the BiCMOS, however this is not seen in the large test structures observed by SIMS; this is certainly due to size related effects during the interface process cleaning.

#### 4. Conclusion

In this paper we have presented a solution for two dimensional quantitative mapping of arsenic doped areas in nanometer scale semiconductor silicon devices. The method can be applied using standard FIB TEM lamella preparation and is compatible with the analysis of high density SRAM 32 45 nm (0.2 0.3  $\mu$ m<sup>2</sup> bit cell area). The spatial resolution is 2 nm, which suggests that this method will still be compatible with future 32 22 nm technologies. As indicated by the single line profiles (without lateral averaging), the signal to noise ratio is excellent and the sensitivity limit is in the low 10<sup>19</sup> cm<sup>-3</sup> range. This spatial resolution and sensitivity could be improved using new electron source generation (high brightness (Freitag et al., 2008) or probe Cs aberration corrected (Krivanek et al., 2008)). However probe size reduction should be coupled with sample holder stability and drift correction improvement if one wants to really gain in spatial resolution. It is reasonable to think that 1 nm resolution and  $1 \times 10^{19}$  cm<sup>-3</sup> sensitivity are the limits since for a 100 nm thick sample the number of arsenic atoms present in the probed volume is about the unity. The presented technique opens a new field of

0.0 +

20

40

## DOCKET

### Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

#### **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

#### **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

#### **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

#### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.