#### OXIDE-FILLED TRENCH ISOLATION PLANARIZED USING CHEMICAL/MECHANICAL POLISHING

J. M. Pierce, P. Renteln, W. R. Burger<sup>1</sup> and S. T. Ahn<sup>2</sup> Fairchild Research Center, National Semiconductor Corporation Santa Clara, CA 95052

An oxide-filled shallow trench isolation process is described, which includes a chemical/mechanical polishing (CMP) step to planarize the CVD oxide used to fill the trenches. The stringent leveling requirements for this application are discussed, and a newly developed CMP process is demonstrated with a leveling length of several mm. The isolation process has been applied to both CMOS and bipolar devices with good results.

#### INTRODUCTION

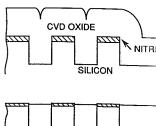

Shallow trench isolation (STI) filled with CVD oxide is attractive for scaled ULSI, because the encroachment and stress problems associated with field oxide growth are largely avoided. Figure 1 shows a simplified STI process flow, a key requirement of which is planarization of the CVD oxide to expose the nitride mask while controlling the relative heights of the active areas and field areas. The final height of the field oxide must be higher than that of the active silicon under the nitride mask, but not high enough to produce a substantial step. A reasonable range for the step is 0-100 nm, which poses a severe challenge for the planarization process. Previous STI processes [1,2] have used planarizing resist over the CVD oxide and RIE etchback of the composite stack. Field areas wider than a few micrometers must be protected by a blocking resist layer patterned using an extra photomasking step, because planarizing resists lose leveling ability beyond this range. Chemical/mechanical polishing (CMP) has also been used in conjunction with resist etchback to improve process margins [2]. These processes are obviously complex and expensive, and accumulation of tolerances associated with the many steps makes it difficult to achieve the final tolerances required.

In this work, an improved CMP process has been used alone to planarize STI, without resist etchback and without the use of an extra masking step. We have named this simplified process ISO-P. The improved CMP process which makes the ISO-P process feasible levels over much longer distances than those leveled by spin-on processes. In addition, exposure of the masking nitride results in a reduction of the polishing rate of oxide in nearby field areas to match that of the nitride. Thus the nitride mask tends to act as a polishing stop layer.

650

DOCKET

Fig. 1. ISO-P process cr before and after CMP pla

Nevertheless, STI pla extremely long planarizing polishing in low density re naturally polish faster. T from the masking nitride in nitride in low density areas ratio is only about 3/1, the is quite limited. Therefore ability of the CMP process. layout where the density va indicating the range of lew CMP process used for ISO-F approaching the size of a length is not desirable, h oxide removal rates acro thickness. The leveling le must therefore be optimized.

The process used for Fig. 1. A 20 nm layer o substrate, followed by depen masking and etching the a stack, the silicon substrate depth 0 - 100 nm less thickness. Trench depths in study. After removing chemically, 20 - 40 nm sidewalls of the trenches.

Find authenticated court documents without watermarks at docketalarm.com.

# ION PLANARIZED

urger<sup>1</sup> and S. T. Ahn<sup>2</sup> Center, Corporation 5052

h isolation process is cal/mechanical polishing oxide used to fill the requirements for this and developed CMP process gth of several mm. The to both CMOS and bipolar

#### I

I with CVD oxide is attractive achment and stress problems largely avoided. Figure 1 largely avoided. key requirement of which is pose the nitride mask while active areas and field areas. t be higher than that of the out not high enough to produce e for the step is 0-100 nm, the planarization process. lanarizing resist over the CVD Field areas wider e stack. ed by a blocking resist layer ng step, because planarizing is range. Chemical/mechanical njunction with resist etchback rocesses are obviously complex ances associated with the many final tolerances required.

press has been used alone to nd without the use of an extra mplified process ISO-P. The ISO-P process feasible levels leveled by spin-on processes. ride results in a reduction of leld areas to match that of the s to act as a polishing stop

DOCKET

RM

Fig. 1. ISO-P process cross-sections before and after CMP planarization.

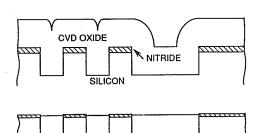

Fig. 2. Typical wafer layout showing need for long distance leveling.

Nevertheless, STI planarization using CMP alone requires an extremely long planarizing range or leveling length to avoid over polishing in low density regions of the circuit where elevated areas naturally polish faster. The key requirement is to remove all oxide from the masking nitride in dense areas without breaking through the nitride in low density areas. Since the oxide/nitride polishing rate ratio is only about 3/1, the stopping power of a 150 nm nitride layer is quite limited. Therefore most of the burden falls on the leveling ability of the CMP process. Figure 2 shows a typical memory wafer layout where the density varies from high to low to high over 5 mm, indicating the range of leveling required. One can conclude that a CMP process used for ISO-P isolation must have a leveling length approaching the size of a chip. A significantly greater leveling length is not desirable, however, because it results in nonuniform oxide removal rates across a wafer due to variations in wafer thickness. The leveling length of a CMP process for ISO-P isolation must therefore be optimized.

#### **PROCESS DETAILS**

The process used for this work followed the scheme shown in Fig. 1. A 20 nm layer of thermal SiO<sub>2</sub> was grown on the silicon substrate, followed by deposition of 150 nm of CVD Si<sub>3</sub>N<sub>4</sub>. After masking and etching the active area pattern in the oxide/nitride stack, the silicon substrate was anisotropically etched using RIE to a depth 0 - 100 nm less than the desired final isolation oxide thickness. Trench depths in the range 0.5 - 1.0 um were used in this study. After removing the photoresist and cleaning the wafers chemically, 20 - 40 nm of thermal SiO<sub>2</sub> was grown to seal the sidewalls of the trenches. At this point, channel stop implants were

651

Find authenticated court documents without watermarks at docketalarm.com.

made in some cases. Next, the trench fill oxide was deposited using CVD to a thickness approximately 50% greater than the trench depth.

CMP planarization was carried out using a glass-impregnated polyurethane polishing pad with fumed colloidal silica slurry. Polishing was terminated when the nitride over the active silicon areas was completely exposed. The pad, slurry and polishing parameters were optimized to produce the leveling results discussed below. After planarization, the nitride/oxide stack was stripped, and the devices were completed using normal process steps.

#### RESULTS

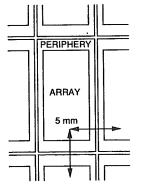

Figure 3 shows the leveling characteristics of the CMP process used in this work. Previously reported results [3] are also shown for comparison. The parameter used in Fig. 3 to characterize leveling is the planarization rate, p, a useful quantitative measure of the planarizing ability of CMP processes on wide patterns [3]. For pattern widths of approximately 1 mm or more, CMP processes quickly smooth the sharp steps at pattern edges and begin eroding oxide from low areas as well as high ones. Nevertheless, planarization continues because high areas are eroded faster than low ones. In this regime, the remaining step height A is decreases exponentially with the mean amount, d, of oxide removed, and p is defined to be the slope of the ln(A) vs. d line. As Fig. 3 indicates, p is high for narrow patterns and declines for wider ones. The current process shows useful planarization out to 5 mm widths, which is in the range needed for ULSI isolation. For example,  $p = 2 \text{ um}^{-1}$  at w = 5 mm implies that the residual step height of a 5 mm wide pattern can be reduced by a factor of  $e^2 = 7.4$  by polishing away 1 um of oxide.

DOCKE

Fig. 3. Leveling characteristics of improved CMP process compared with process reported previously [3].

652

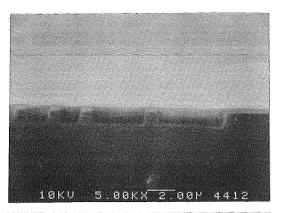

Figure 4 shows SEM vie and before stripping the been added to improve coni quality local planarizati is shown in Figs. 5-6. F memory wafer before and a one array to the next acro The initial step height w Fig. 5C shows, the total than 40 nm. At this scale, it necessary to measure a Figure 6 shows the remain series of adjacent points

Fig. 4. SEM cross-sect planarization. A poly

ill oxide was deposited using ter than the trench depth.

It using a glass-impregnated ed colloidal silica slurry. ide over the active silicon pad, slurry and polishing e leveling results discussed oxide stack was stripped, and rocess steps.

teristics of the CMP process results [3] are also shown for 3 to characterize leveling is quantitative measure of the on wide patterns [3]. For more, CMP processes quickly and begin eroding oxide from eless, planarization continues an low ones. In this regime, s exponentially with the mean effined to be the slope of the p is high for narrow patterns current process shows useful is in the range needed for  $^{-1}$  at w = 5 mm implies that pattern can be reduced by a of oxide.

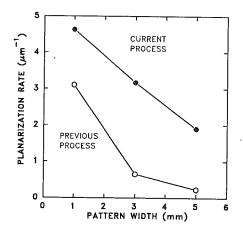

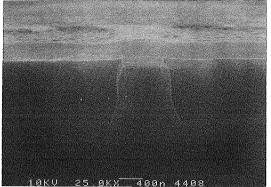

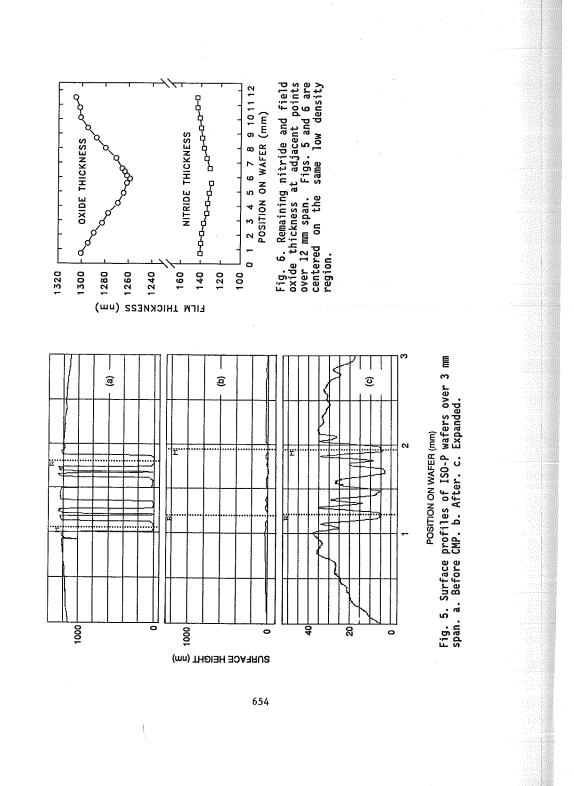

Fig. 3. Leveling characteristics of improved CMP process compared with process reported previously [3]. Figure 4 shows SEM views of an ISO-P wafer after CMP planarization and before stripping the exposed nitride mask. A poly-Si layer has been added to improve contrast and delineate surface topography. High quality local planarization is evident. Long distance planarization is shown in Figs. 5-6. Figure 5 shows surface profilometer scans of a memory wafer before and after planarization. The 3 mm scans run from one array to the next across a low density region more than 1 mm wide. The initial step height was 1.2 um. As the expanded scale trace in Fig. 5C shows, the total remaining amplitude over a 3 mm span is less than 40 nm. At this scale, the bow in the wafer is significant, making it necessary to measure actual film thicknesses to evaluate leveling. Figure 6 shows the remaining nitride and field oxide thicknesses at a series of adjacent points along a 12 mm path crossing the low density

Fig. 4. SEM cross-sections of ISO-P structures after CMP planarization. A poly-Si layer was added to improve contrast.

653

Find authenticated court documents without watermarks at docketalarm.com.

region of Fig. 5. The orig to 133 nm with a variation of nm. This excellent planariz between nitride and oxide m sufficient extra margin to a deposition and CMP.

The ISO-P process has b devices. No significant deg which could be attributed to encroachment of STI means the is available for active devi the transconductances of NM LOCOS isolated controls. T are approximately 0.7 um gre reduced encroachment.

Planarization of shallow demonstrated, without resist masking step. A newly de leveling lengths in the ra bridge regions of varying isolation has been applied results, and the field oxide

Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

Δ

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

## LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

## FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

## E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.