#### CERTIFICATE OF TRANSLATION

I Roger P. Lewis, whose address is 42 Bird Street North, Martinsburg WV 25401, declare and state the following:

I am well acquainted with the English and Japanese languages and have in the past translated numerous English/Japanese documents of legal and/or technical content.

I hereby certify that the Japanese translation of the attached documents identified as:

JP Hei 7 - 183518 Semiconductor Device and the Production Method Thereof

is true, and that all statements of information and belief are believed to be true, and that these and similar statements are punishable by fines or imprisonment, or both, under Section 1001 of Title 18 of the United States Code.

SINCERELY,

Her P. Lenie

ROGER P. LEWIS Date: October 20, 2016

Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

| (19) Japan Patent Office (JP)                                                                                                                                                                         | (11) [Unexamined] Patent Application Publication No.                                                     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|

| (12) Publication of Patent Application (A)<br>Pat. Pub. Hei. 7 [1995] – 183518<br>(Publication Date) 7 <sup>th</sup> Year of Heisei (1995) 7 <sup>th</sup> Month 21 <sup>st</sup> Day [July 21, 1995] |                                                                                                          |  |

| (51) Int.Cl. <sup>6</sup> Classification Symbol<br>H01L 29/78<br>21/336<br>21/28 301 T                                                                                                                | JPO File No. F1 Basis for Classification   8826-4M 7514-4M H01L 29/78 301 Y   21/76 M M                  |  |

| Examination Request: Not Reque                                                                                                                                                                        | ested No. of Claims: 15 FD (Total 17 Pages)<br>Continued on Last Page                                    |  |

| (21) Application No.                                                                                                                                                                                  | Pat. App. Hei. 6 [1994] - 303260                                                                         |  |

| (22) Application Date                                                                                                                                                                                 | 6 <sup>th</sup> Year of Heisei (1994) 11 <sup>th</sup> Month 10 <sup>th</sup> Day<br>[November 10, 1994] |  |

| <ul><li>(31) Priority Application No.</li><li>(32) Priority Date</li><li>(33) Priority Country</li></ul>                                                                                              | Pat. App. Hei. 5 [1993] – 2842820<br>Hei. 5 (1993)<br>Japan (JP)                                         |  |

| (71) Applicant                                                                                                                                                                                        | 000005821<br>Matsushita Electric Industrial Co., Ltd.                                                    |  |

| (72) Inventor                                                                                                                                                                                         | 1006 Ōaza Kadoma, Kadoma-shi, Ōsaka-fu<br>Tetsuya UEDA<br>Matsushita Electric Industrial Co., Ltd.       |  |

| (72) Inventor                                                                                                                                                                                         | 1006 Ōaza Kadoma, Kadoma-shi, Ōsaka-fu<br>Takashi UEHARA<br>Matsushita Electric Industrial Co., Ltd.     |  |

| (72) Inventor                                                                                                                                                                                         | 1006 Ōaza Kadoma, Kadoma-shi, Ōsaka-fu<br>Kōsaku Yano<br>Matsushita Electric Industrial Co., Ltd.        |  |

| (74) Agent                                                                                                                                                                                            | 1006 Ōaza Kadoma, Kadoma-shi, Ōsaka-fu<br><i>Benrishi</i> Hiroshi MAEDA (and 2 others)                   |  |

[Translation of 1<sup>st</sup> page of source document continued on 2/2]

DOCKET

Α

[Translation of 1<sup>st</sup> page of source document continued from 1/2]

(54) [Title of the Invention] Semiconductor Device and the Production Method Thereof

#### (57) Abstract

[Objective] To provide a method for producing semiconductor devices that are easily planarized whilst making an effort to achieve low resistance of the diffusion layer without causing reaction of the substrate silicon.

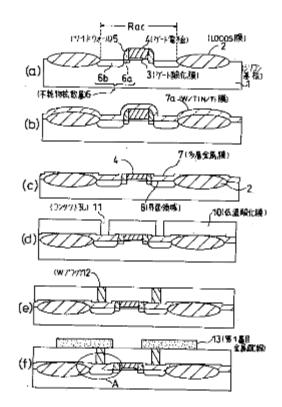

**[Composition]** A process for the formation of LOCOS film 2 for the purpose of dividing the active region Rac into a plurality of regions in the vicinity of the surface of the semiconductor substrate, a process for the formation of gate electrode 4, which has a gate oxide film in the active region Rac, a process for the formation of side wall 5 on both sides of gate electrode 4, a process for the formation of impurity diffusion layer 6 in the active region Rac of both sides of gate electrode 4, [and] a process for the deposition of multi-layer metal film 7 over the entire surface of the substrate so that the entire surface of metal layer is polished by means of chemical machine polishing (CMP) and only metal film 7 remains on the impurity diffusion layer 6. When the CMP is completed, the polished surface is such that the surroundings of each of the metal layers 7 are encompassed by side wall 5 of both sides of gate electrode 4 and the LOCOS film, and each of the multi-layer metal films 7 are individually isolated.

[Legend for Figure in the lower left of the 1<sup>st</sup> source document page]

DOCKET

Α

| (a) (サイドウォール) 5     | (Side Wall) 5                               |

|---------------------|---------------------------------------------|

| 4 (ゲート電極)           | 4 (Gate Electrode)                          |

| (LOCOS 膜) 2         | (LOCOS Film) 2                              |

| 3(ゲート酸化膜)           | 3 (Gate Oxide Film)                         |

| (シリコン基板)1           | (Silicon Substrate) 1                       |

| (不純物拡散層) 6          | (Impurity Diffusion Layer) 6                |

| (b) 7a (W/TiN/Ti 膜) | (b) 7a (W/TiN/Ti Film)                      |

| (c) 7 (多層金属膜)       | (c) 7 (Multi-Layer Metal Film)              |

| 8 (界面領域)            | 8 (Surface Region)                          |

| (d) (コンタクト孔) 11     | (d) (Contact Hole) 11                       |

| 10 (低温酸化膜)          | 10 (Low Temperature Oxide Film)             |

| (e) (W プラグ) 12      | (e) (W Plug) 12                             |

| (f) 13 (第 1 層目金属配線) | (f) 13 (1 <sup>st</sup> Metal Interconnect) |

[Scope of Claims]

DOCKE

[Claim 1] A production method for semiconductors that include a plurality of MISFET and which is characterized by the fact that it is equipped with

a process for the formation of an outer periphery separation portion of the active region of the semiconductor substrate at a location that is higher than the surface of the above described active region,

a process for the introduction of threshold value control impurity of the above described MISFEET [sic],

a process for the formation, within the above described active region, of the gate electrode and gate insulation film of the above described MISFET,

a process for the formation of side walls, which are composed of insulation material, on both sides of the above described gate electrode,

a process for the formation of the above described MISFET's drain source, which becomes the 2 impurity diffusion layers,

a process for the deposition of a metal film on the entire surface of the substrate after the formation of the above described gate electrode, side wall and outer periphery separation part, [and]

a process by which a portion of the above described metal films, the outer periphery portion and the gate electrode are removed, and when the chemical machine polishing is completed, within the polished surface, the metal films on the above described impurity diffusion layer is surrounded by the above described gate electrode and outer periphery separation part so as to electrically isolate each [metal film].

[Claim 2] A production method for semiconductors that described in Claim 1 and that is characterized by the fact that it is equipped, in the production method for semiconductors,

so that a LOCOS film is formed in the process for the formation of the above described outer periphery separation part, [and]

in the process wherein the above described chemical machine polishing is performed, when the chemical machine polishing is completed, within the polished surface, each of the metal films on the above described impurity diffusion layer is surrounded by the above described side wall and LOCOS film.

[Claim 3] A production method for semiconductors that is described in Claim 1 that is characterized by the fact that it is equipped, in the production method for semiconductors,

so that in the process for the formation of the above described outer periphery separation part, after the formation on the semiconductor substrate of a groove that surrounds the above described active region a LOCOS film is formed in the process for the formation of the above described outer periphery separation part, [and] so that in the process for performing the chemical machine polishing, when the chemical machine polishing is completed, within the polished surface, each of the metals films on each of the above described impurity diffusion layers are surrounded by each of the above described side wall and the above described embedded oxide film.

## DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.