US006967409B2

## (12) United States Patent

Segawa et al.

(10) Patent No.: US 6,967,409 B2

(45) **Date of Patent:**

Nov. 22, 2005

## (54) SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

(75) Inventors: Mizuki Segawa, Osaka (JP); Isao

Miyanaga, Osaka (JP); Toshiki Yabu,

Osaka (JP); Takashi Nakabayashi,

Osaka (JP); Takashi Uehara, Osaka

(JP); Kyoji Yamashita, Osaka (JP);

Takaaki Ukeda, Osaka (JP); Masatoshi

Arai, Osaka (JP); Takayuki Yamada,

Osaka (JP); Michikazu Matsumoto,

Osaka (JP)

(73) Assignee: Matsushita Electric Industrial Co.,

Ltd., Osaka (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 127 days.

(21) Appl. No.: 10/454,682

(22) Filed: Jun. 5, 2003

(65) Prior Publication Data

US 2003/0205820 A1 Nov. 6, 2003

## Related U.S. Application Data

(62) Division of application No. 09/902,157, filed on Jul. 11, 2001, now Pat. No. 6,709,950, which is a division of application No. 08/685,726, filed on Jul. 24, 1996, now Pat. No. 6,281,562.

## (30) Foreign Application Priority Data

|      | 27, 1995 (JP)            |           |

|------|--------------------------|-----------|

| (51) | Int. Cl. <sup>7</sup> H0 | 1L 29/40  |

| (52) | U.S. Cl                  | 257/774   |

| (58) | Field of Search 257/     | 304, 510, |

|      | 257                      | /774, 311 |

(56) References Cited

### U.S. PATENT DOCUMENTS

4,578,128 A 3/1986 Mundt et al. 4,966,870 A 10/1990 Barber et al. 5,177,028 A 1/1993 Manning 5,196,910 A 3/1993 Moriuchi et al.

(Continued)

#### FOREIGN PATENT DOCUMENTS

EP 0234988 A1 4/1987 EP 0 243 988 11/1987

(Continued)

Primary Examiner—Roy Potter (74) Attorney, Agent, or Firm—McDermott Will & Emery

### (57) ABSTRACT

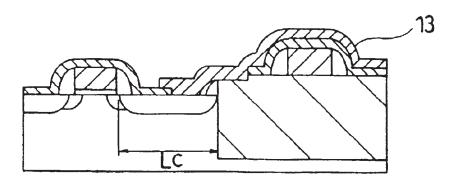

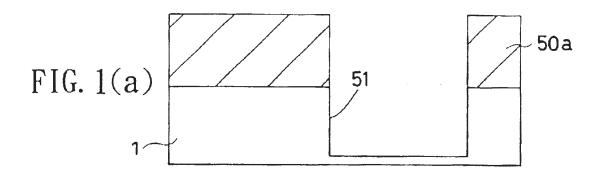

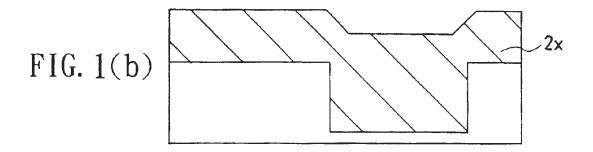

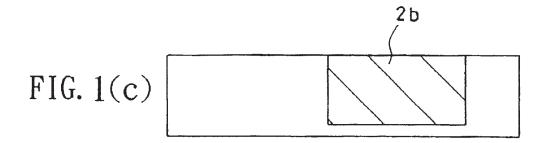

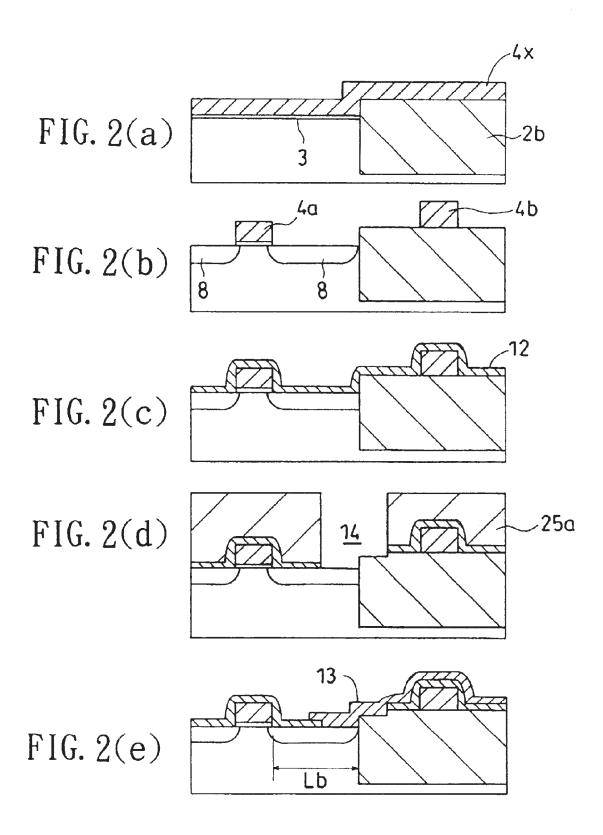

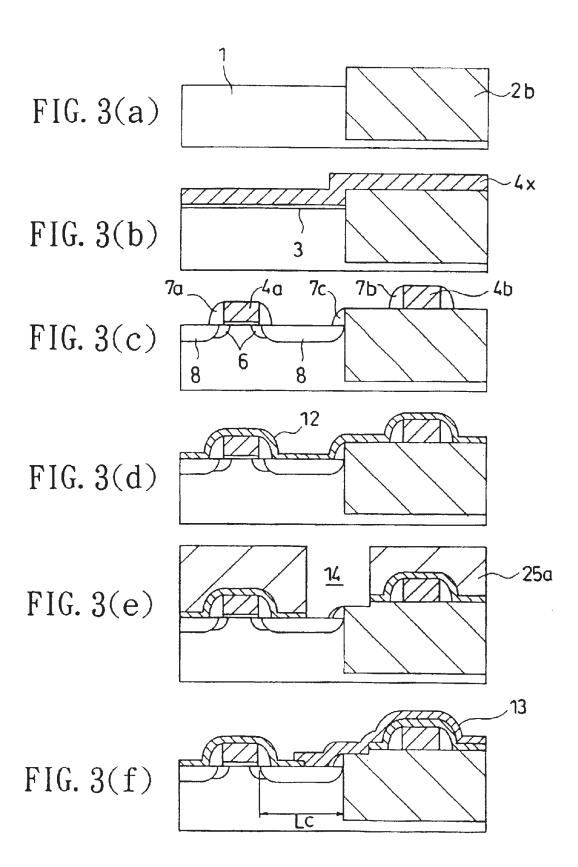

An isolation which is higher in a stepwise manner than an active area of a silicon substrate is formed. On the active area, an FET including a gate oxide film, a gate electrode, a gate protection film, sidewalls and the like is formed. An insulating film is deposited on the entire top surface of the substrate, and a resist film for exposing an area stretching over the active area, a part of the isolation and the gate protection film is formed on the insulating film. There is no need to provide an alignment margin for avoiding interference with the isolation and the like to a region where a connection hole is formed. Since the isolation is higher in a stepwise manner than the active area, the isolation is prevented from being removed by over-etch in the formation of a connection hole to come in contact with a portion where an impurity concentration is low in the active area. In this manner, the integration of a semiconductor device can be improved and an area occupied by the semiconductor device can be decreased without causing degradation of junction voltage resistance and increase of a junction leakage current in the semiconductor device.

### 81 Claims, 21 Drawing Sheets

Exhibit 2076

#### U.S. PATENT DOCUMENTS FOREIGN PATENT DOCUMENTS 2/1994 Roth et al. 5,286,674 A 11/1992 EP 0 513 639 5,319,235 A 6/1994 Kihara et al. 0 706 206 A2 4/1996 5,384,281 A 1/1995 Kenney et al. JP 59181062 A 10/1984 5,393,708 A 2/1995 Hsia et al. JP 62-85461 4/1987 5,397,910 A 3/1995 Ishimaru JP 03079033 A 4/1991 3/1995 Urayama 5,401,673 A JP 4-48647 2/1992 5,413,961 A 5/1995 Kim JP 4-68564 3/1992 7/1995 Fazan et al. 5,433,794 A JP 4-305922 10/1992 5,497,016 A 3/1996 Koh JP 6-45432 2/1994 5,521,422 A 5/1996 Mandelman et al. JP 6-163843 6/1994 5,561,311 A 10/1996 Hamamoto et al. JP 7-273330 10/1995 7/1998 Omid-Zohoor et al. 5,777,370 A 09162392 A JP 6/1997 5,804,862 A \* 9/1998 Matumoto ...... 257/396 6,022,781 A 2/2000 Noble, Jr. \* cited by examiner 6,281,562 B1 8/2001 Segawa et al.

# DOCKET

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.