Filed on behalf of Godo Kaisha IP Bridge 1

# UNITED STATES PATENT AND TRADEMARK OFFICE

# **BEFORE THE PATENT TRIAL AND APPEAL BOARD**

TAIWAN SEMICONDUCTOR MANUFACTURING COMPANY LIMITED, Petitioner,

v.

GODO KAISHA IP BRIDGE 1, Patent Owner.

Case IPR2016-01246<sup>1</sup> U.S. Patent No. 7,126,174

## DECLARATION OF DR. E. FRED SCHUBERT, PH.D. IN SUPPORT OF PATENT OWNER'S RESPONSE

<sup>&</sup>lt;sup>1</sup> Case IPR2016-01247 has been consolidated with this proceeding.

# **Table of Contents**

| Introduction 1                                                            |

|---------------------------------------------------------------------------|

| Summary Of Opinions 1                                                     |

| Background And Qualifications 3                                           |

| Previous Expert Witness Experience                                        |

| Compensation                                                              |

| Background 4                                                              |

| Materials Reviewed10                                                      |

| Understanding Of Claim Terms10                                            |

| Legal Standards11                                                         |

| Dr. Banerjee's Declaration                                                |

| Technological Background19                                                |

| Acronyms19                                                                |

| Silicon Integrated Circuit (IC) Processing20                              |

| Electrical Isolation In Silicon Integrated Circuit Wafers                 |

| Differences Between LOCOS Isolation And Trench Isolation                  |

| LOCOS Isolation And Trench Isolation Are Not Functionally Equivalent37    |

| Difficulties Of Employing STI On Wafers Having A Non-Planar Topology42    |

| Benefits Of The Claimed Features Of The '174 Patent And Their Synergies50 |

| Applied Prior Art60                                                       |

| U.S. Patent No. 5,153,145 ("Lee")60                                       |

| U.S. Patent No. 5,021,353 ("Lowrey")                                      |

| U.S. Patent No. 5,539,229 ("Noble")                                       |

| U.S. Patent No. 4,506,434 ("Ogawa")80                                     |

| Overview Of Why The References Are Not Combinable                         |

| Combination: <i>Lee &amp; Noble</i>                                       |

| The Initial Processing Sequence Of Noble Is Opposite From Lee             |

| Lee And Noble Processes Are Not Compatible                                |

| No L-Shaped Second Sidewalls103                                           |

i

| Summary109                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lee-Noble Rejection Fails On Further Grounds111                                                                                                                   |

| Silicidation Of <i>Lee</i>                                                                                                                                        |

| Conclusions regarding the <i>Lee-Noble</i> combination113                                                                                                         |

| Petitioner Fails To Meet Its Burden To Establish That Lee In Combination With                                                                                     |

| Noble Renders At Least Claim 1 Unpatentable                                                                                                                       |

| Combination: Lee & Ogawa115                                                                                                                                       |

| Initial Processing Sequence of Ogawa Is Opposite From Lee                                                                                                         |

| Lee And Ogawa Processes Are Not Compatible                                                                                                                        |

| No L-Shaped Second Sidewalls127                                                                                                                                   |

| Petitioner's Proposed Silicide "Layer" Is Portrayed To Be A Small Diameter<br>Circular Element (Wire or Cylinder) That Runs Along the Gate Width Of The<br>Device |

| Conclusions Regarding The <i>Lee-Ogawa</i> Combination                                                                                                            |

| Petitioner Fails To Meet Its Burden To Establish That <i>Lee</i> In Combination With <i>Ogawa</i> Renders At Least Claim 1 Unpatentable                           |

| Conclusions Regarding Claim 1134                                                                                                                                  |

| Dependent Claims                                                                                                                                                  |

| <i>Lee</i> In Combination With <i>Noble/Ogawa</i> Would Not Render Claim 2 And 6<br>Obvious                                                                       |

| <i>Lee</i> In Combination With <i>Noble/Ogawa</i> Would Not Render Claim 3 And 15<br>Obvious                                                                      |

| <i>Lee</i> In Combination With <i>Noble/Ogawa</i> Would Not Render Either Claim 5<br>And 16 Obvious                                                               |

| <i>Lee</i> In Combination With <i>Noble/Ogawa</i> Would Not Render Claim 7, 17, And 18 Obvious                                                                    |

| <i>Lee</i> In Combination With <i>Noble/Ogawa</i> Would Not Render Claim 9 Obvious                                                                                |

| <i>Lee</i> In Combination With <i>Noble/Ogawa</i> Would Not Render Claim 10 Obvious                                                                               |

| <i>Lee</i> In Combination With <i>Noble/Ogawa</i> Would Not Render Claim 11 and 12<br>Obvious                                                                     |

| <i>Lee</i> In Combination With <i>Noble/Ogawa</i> Would Not Render Claim 14 Obvious                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Summary Of Argument141                                                                                                                        |

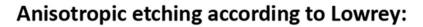

| Combination: <i>Lowrey &amp; Noble</i> 144                                                                                                    |

| Lowrey Is Not Compatible With Trench Isolation144                                                                                             |

| The Initial Processing Sequence Of Lowrey147                                                                                                  |

| Trench Isolation Is Incompatible With Lowrey152                                                                                               |

| Lowrey Cannot Be Combined With Noble157                                                                                                       |

| No Second L-Shaped Sidewalls169                                                                                                               |

| Conclusions Regarding The Lowrey-Noble Combination176                                                                                         |

| Petitioner Fails To Meet Its Burden To Establish That <i>Lowrey</i> In Combination With <i>Noble</i> Renders At Least Claim 1 Unpatentable    |

| Combination: Lowrey And Ogawa178                                                                                                              |

| Initial Processing Sequence Of <i>Ogawa</i>                                                                                                   |

| The Petition Fails To Describe How <i>Lowrey</i> Could Be Combined With <i>Ogawa</i><br>To Render The Challenged Claims Unpatentable          |

| Lowrey And Ogawa Do Not Suggest L-Shaped Sidewalls186                                                                                         |

| Summary188                                                                                                                                    |

| Petitioner Fails To Meets Its Burden To Establish That A POSITA Would<br>Combine <i>Lowrey</i> with <i>Ogawa</i>                              |

| Conclusions Regarding The Lowrey-Ogawa Combination193                                                                                         |

| Petitioner Fails To Meet Its Burden To Establish That <i>Lowrey</i> In Combination<br>With <i>Ogawa</i> Renders At Least Claim 1 Unpatentable |

| Nothing Suggests That L-Shaped Sidewalls Would Form On The<br>Interconnection                                                                 |

| Conclusions Regarding Claim 1197                                                                                                              |

| Dependent Claims                                                                                                                              |

| <i>Lowrey</i> In Combination With <i>Noble/Ogawa</i> Would Not Render Claims 4, 5, 8, And 16 Obvious200                                       |

| <i>Lowrey</i> In Combination With <i>Noble/Ogawa</i> Would Not Render Claims 9 And 10 Obvious                                                 |

| Lowrey In Combination With Noble/Ogawa Would Not Render Claims 11<br>And 12 Obvious |      |

|-------------------------------------------------------------------------------------|------|

|                                                                                     | .200 |

| Lowrey In Combination With Noble/Ogawa Would Not Render Claim 14<br>Obvious         | .202 |

| Summary Of Argument                                                                 | .203 |

I, E. Fred Schubert, declare as follows:

#### **Introduction**

1. My name is Dr. E. Fred Schubert. I have been asked to submit this declaration on behalf of Godo Kaisha IP Bridge 1 ("IP Bridge" or "Patent Owner") in connection with a Petition for *Inter Partes Review* of U.S. Patent No. 7,126,174 ("the '174 patent"), which I understand was submitted to the Patent Trial and Appeal Board of the United States Patent and Trademark Office by petitioner Taiwan Semiconductor Manufacturing Company Ltd. ("TSMC").

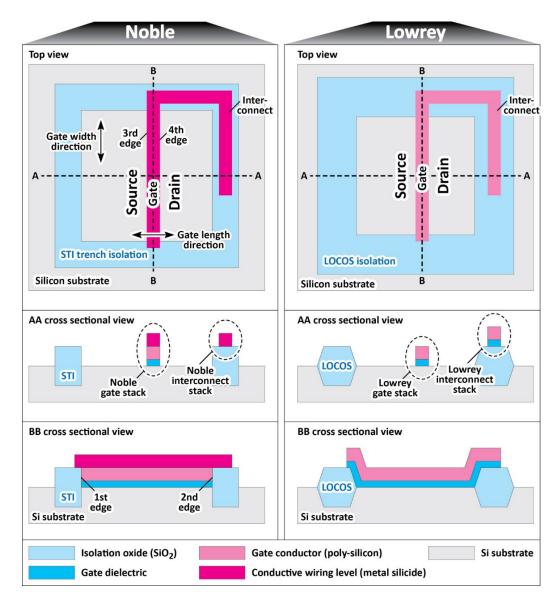

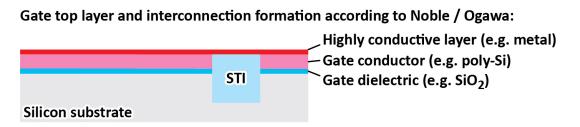

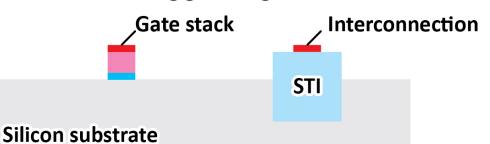

2. I have been retained as a technical expert by IP Bridge to study and provide my opinions on the technology claimed in, and the patentability or non-patentability of, claims 1-3, 5-7, 9-12, and 14-18 in the '174 patent ("the Challenged Claims").

3. I understand the '174 patent is related to U.S. Patent Nos. 6,967,409 (the '409 patent), 6,709,950 (the '950 patent), and 6,281,562 (the '562 patent) and also claims the benefit of priority to two Japanese applications, JP 7-192181, which was filed on July 27, 1995, and JP 7-330112, which was filed on December 19, 1995.

#### **Summary Of Opinions**

4. I have reviewed the '174 patent, associated prior art, the TSMC Petition, the Declaration of Dr. Banerjee, as well as references cited therein. I

understand that the Petitioner and its expert, Dr. Banerjee, express the following contentions:

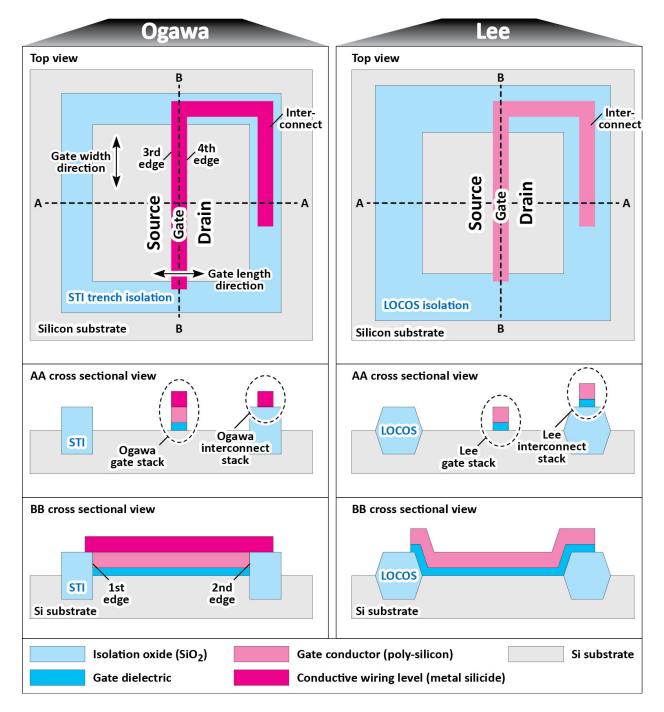

5. *First*, Petitioner and its expert contend that LOCOS isolation and trench isolation are interchangeable and one could simply substitute LOCOS isolation with trench isolation.

6. Second, Petitioner and its expert offer four combinations, (1) Lee and Noble, (2) Lee and Ogawa, (3) Lowrey and Noble, (4) Lowrey and Ogawa, and contend that the substitution of Lee's LOCOS isolation or Lowrey's LOCOS isolation, with either Noble's or Ogawa's trench isolation would result in the claimed invention of the '174 patent.

7. Based on my experience and knowledge in the field and based on my review of the documents, I express my opinions as follows:

8. *First*, it is my opinion that LOCOS isolation and trench isolation are substantially different structures thereby requiring that their fabrication processes as well as the processes that they are integrated into must be modified substantially when transitioning from LOCOS isolation to trench isolation.

9. *Second*, it is my opinion that a simple substitution of LOCOS isolation with trench isolation, without a detailed re-engineering of a fabrication process, is generally not obvious, not possible, and if done nonetheless, would result in a non-working Si IC device.

10. Accordingly, it is my opinion that the '174 patent is not obvious based on the prior art asserted by Petitioner and its expert. That is, the '174 patent is not obviated by the *Lee* and *Noble*, *Lee* and *Ogawa*, *Lowrey* and *Noble*, or *Lowrey* and *Ogawa* combinations.

## **Background And Qualifications**

## Previous Expert Witness Experience

11. I have served as a technical expert witness since the late 1990s. My expert activity included semiconductor materials, processing, devices, packaging, and systems. I have worked on behalf of Plaintiffs and Defendants, on behalf of domestic companies and foreign companies, and in proceedings at the USPTO (including *inter partes reviews*), District Court, and the International Trade Commission (ITC). My work included mostly utility patent cases, but also included design patent cases, a case of alleged misappropriation of a trade secret, and a case of alleged mishandling of a patent application.

## **Compensation**

12. I am compensated at my customary rate of \$500 per hour worked on the case plus reasonable and customary expenses. My compensation does not depend on the outcome of the *inter partes review*.

#### Background

13. I am currently a Professor in the Department for Electrical, Computer, and Systems Engineering at the Rensselaer Polytechnic Institute (RPI) located in Troy, New York.

I received a Master's Degree in Electrical Engineering from the 14. University of Stuttgart, Germany, in 1981. While working towards my Master's Degree in Electrical Engineering, I had hands-on experience working in a silicon IC fabrication facility, working on silicon integrated piezo-resistive sensors. I received a Ph.D. degree in Electrical Engineering from the University of Stuttgart, Germany, in 1986. While working towards my Ph.D., in 1982, I worked as a summer intern at IBM's silicon integrated circuit fabrication facility in Böblingen, Germany. In this capacity, my work specifically focused on photolithography and mask design. My dissertation was titled "Modern Schottky Gate Field Effect Transistor Devices Made of III-V Semiconductors." Subsequent to my education, starting in 1985, I worked in industry, at AT&T Bell Laboratories in Holmdel and Murray Hill, New Jersey, for ten years. The transistor was invented at Bell Labs (in 1949) and the Labs were subsequently recognized as one of the world's premier industrial research laboratories. From 1990-1995, while at AT&T Bell Labs, I worked in the silicon integrated circuit fabrication facility. This facility was nicknamed "Blue Zoo" fabrication facility and was located in Murray Hill, New

Jersey. While working in this facility, my work focused on the doping of silicon, on the demonstration of shallow junctions, and on the design and fabrication of silicon MOSFETs, including LDD MOSFETs that employ gate sidewall spacers for a better control of the dopant distribution.

15. In 1995, I joined academia. My first position was at Boston University (Boston MA) where I worked as a full professor for seven years. In 2002, I joined RPI as a distinguished professor, the Wellfleet Senior Constellation Professor, with appointments in the Department for Electrical, Computer, and Systems Engineering and the Department for Physics, Applied Physics, and Astronomy. I served as Head of the Future Chips Constellation from 2002 to 2015. Furthermore, I am the founding Director of the Smart Lighting Engineering Research Center, which is funded by the US National Science Foundation at \$40 million over 10 years.

16. I am co-inventor of more than 30 U.S. patents and have co-authored more than 300 publications. I authored the books "Doping in III–V Semiconductors" (1993), "Delta Doping of Semiconductors" (1996), and the first and second editions of "Light-Emitting Diodes" (2003 and 2006). My publications have been well recognized by the technical community as illustrated by the more than 25,000 citations that my publications have received. The high number of

citations shows the recognition of my research accomplishments and puts me in the top 1% of researchers in the field of semiconductors.

17. I have received several awards for my technical contributions. They include: Senior Member IEEE (1993); Literature Prize of Verein Deutscher Elektrotechniker for book "Doping in III–V semiconductors" (1994); Fellow SPIE (1999); Alexander von Humboldt Senior Research Award (1999); Fellow IEEE (1999); Fellow OSA (2000); Boston University Provost Innovation Award (2000); Discover Magazine Award for Technological Innovation (2000); R&D 100 Award for RCLED (2001); Fellow APS (2001); RPI Trustees Award for Faculty Achievement (2002 and 2008); Honorary membership in Eta Kappa Nu (2004); 25 Most Innovative Micro- and Nano-Products of the Year Award of R&D Magazine (2007); and the Scientific American 50 Award (2007).

18. My general expertise is in the field of electrical engineering and applied physics with a particular emphasis on semiconductor devices, semiconductor materials, semiconductor processing, and semiconductor device packaging. I have worked in semiconductor processing facilities, including facilities dedicated to silicon integrated circuit (IC) processing, for many years starting in 1980. I have numerous documented contributions to the field of semiconductor doping including the fabrication and analysis of ultra-shallow junctions in silicon, namely delta-function-like doping profiles that are deposited

with near-atomic precision. These doping profiles are more precise than what is currently attainable with ion implantation. At the present time, doping by ion implantation is the dominant doping technique in the silicon IC industry. I have also taught courses on silicon integrated circuit technology. This includes teachings at RPI and Boston University. My teachings concern the theory of silicon integrated circuits as well as the fabrication of silicon integrated circuits, including silicon MOSFETs, LDD MOSFETs, HKMG MOSFETs, LDMOS FETs, FINFETs, and GAAFETs<sup>2</sup>. The courses that I taught include practical hands-on laboratory sections.

19. Furthermore, I have made pioneering contributions to the field of porous silica thin films (porous  $SiO_2$  thin films) deposited by oblique-angle deposition. These highly porous silica films, whose porosity can be as high as 90%, are highly desirable for high-speed interconnects in silicon ICs due to the low dielectric constant ("low k") of these materials and the resulting low capacitance of interconnect wires using interlayer dielectrics made of porous silica. My research also included the theoretical study, experimental verification, and the application

<sup>&</sup>lt;sup>2</sup> LDD = Low-doped drain; HKMG = High k metal gate; LDMOS = Laterally diffused metal oxide semiconductor; FINFET = Fin-shaped FET; GAAFET = Gate all around FET

of the piezo-resistive coefficients of thin silicon membranes that are subjected to a mechanical stress and strain. My research contributions also include the use of delta-doped silicon for MOSFET applications for ultra-shallow junctions. Delta-doped silicon MOSFETs possess ultra-shallow junctions. Indeed, these junctions are the shallowest junctions attainable (delta-doped junctions are shallower than ion-implanted junctions). That is, I (along with my collaborators) demonstrated the shallowest junctions in silicon.

20. At my home institution, Rensselaer Polytechnic Institute (RPI), I teach on the subject of silicon microelectronics on a regular basis. The teaching includes undergraduate and graduate courses. The subject matter includes silicon metal-oxide-semiconductor field effect transistors (MOSFETs), complementary metal-oxide-semiconductor (CMOS) technology, constant-electric-field scaling, the theory of transistors and integrated circuits, and the fabrication of integrated circuits. I am well versed in the theory and the physics of semiconductor devices and associated electrical circuits. In addition, I regularly work with students and staff of a silicon microfabrication clean room facility at my home institution (RPI). Several of my former Ph.D. and Master students have worked or are currently working in the silicon integrated circuit industry including the following companies: IBM Company in Fishkill NY, Global Foundry Company in Malta NY,

Albany Nanotech in Albany NY, Micron Company in Boise Idaho, and Intel Company in Boise Idaho.

21. My experience includes the operation, modeling, driving, design, fabrication, and analysis of solid-state devices and integrated electrical circuits. I am the inventor on patents that concern silicon semiconductor devices, including the doping of silicon. My experience includes the employment and operation of various analysis techniques including SEM (scanning electron microscopy), TEM (transmission electron microscopy), EDXS (energy dispersive x-ray spectroscopy also called EDS or EDX), EELS (electron energy loss spectroscopy), and SIMS (secondary ion mass spectrometry).

22. I have consulted for companies in the semiconductor industry, including the semiconductor processing industry. Specifically, I have consulted for Varian Company in Gloucester, Massachusetts (now part of Applied Materials Company) and for Micron Technologies in Boise, Idaho. In my capacity as a consultant, I visited these companies multiple times and on a regular basis. My consulting has allowed the companies to enhance their understanding of semiconductor devices and take advantage of the technological advancements made in academia including my research laboratory and the microfabrication facility at RPI.

23. More details about my experience and background are included in my curriculum vitae, attached as Appendix A to my report.

## Materials Reviewed

- 24. I have reviewed the following documents:

- The '174 patent and its file history

- US patent 6,281,562 and its file history

- US patent 6,709,950 and its file history

- US patent 6,967,409 and its file history

- The TSMC Petition and references cited therein

- Dr. Banerjee's expert declaration and references cited therein

- Various technical articles and patents cited herein and in Patent

Owner's Response

## **Understanding Of Claim Terms**

25. I understand that in a pending litigation involving the '174 patent (Case No. 2:16-cv-00134-JRG-RSP (E.D. Tex Feb 14, 2016)), the Court has construed certain terms in the claims of the '174 patent. In forming the opinions stated in this report, I have assumed the constructions of those terms as provided by the Court's Order (the "Order"). Dkt. No. 105. Exhibit 3001. In the claim construction order, the following terms of the '174 patent were given the following constructions:

| Claim Term                               | Construction                               |

|------------------------------------------|--------------------------------------------|

| "a trench isolation region surrounding   | Plain meaning                              |

| an active area of a semiconductor        |                                            |

| substrate" (claim 1)                     |                                            |

| "first silicide layers formed on regions | "first silicide layers formed on regions   |

| located on the sides of the first L-     | that are within the active area and        |

| shaped sidewalls within the active area" | located on the sides of the first L-       |

| (Claim 1)                                | shaped sidewalls"                          |

| "L-shaped sidewalls" (Claims 1, 14)      | "sidewalls that substantially resemble a   |

|                                          | capital letter 'L' or its mirror image"    |

| "surface of the active area" (Claims 9,  | "top of the active area"                   |

| 10)                                      |                                            |

| "a lower portion of the interconnection  | "a bottom surface of the                   |

| provided on the upper surface of the     | interconnection provided on the upper      |

| trench isolation is located higher than  | surface of the trench isolation is located |

| the surface of the active area" (Claim   | higher than the surface of the active      |

| 10)                                      | area"                                      |

| "composed of the same material"          | Plain and ordinary meaning                 |

| (Claim 11)                               |                                            |

| "made of the same insulating film"       | "made of the same insulating material"     |

See Exhibit 3001, Appendix A.

# Legal Standards

26. I am not a lawyer. Counsel for IP Bridge has advised me regarding the

legal principles governing patent law. Based on counsel's advice, my understanding is as follows below.

27. In an IPR proceeding, the Petitioner has the initial burden of persuasion to establish a reasonable likelihood that at least one claim of an issued patent are unpatentable, and this burden remains throughout the entire proceeding

28. Petitioner must provide an analysis of how or why an element from a prior art teaching could be combined with the teaching of another reference

29. A person of ordinary skill in the art (POSITA) at the time the application leading to the '174 patent was filed would have at least a Bachelor's degree in Electrical, Materials, Mechanical, or Chemical Engineering, or a related degree, and at least two years of experience working in semiconductor processing and fabrication, semiconductor equipment manufacturing, or semiconductor materials. Integrated circuit (IC) design is different from IC processing and fabrication. It is one thing to have a theoretical understanding of circuit design, but quite another to be familiar with the problems associated with the IC fabrication process. Without any direction by Petitioner how or why a feature is to be combined, a naked assertion that such would be within the skill of a POSITA is not enough to establish a reasonable likelihood that at least one claim of an issued patent is unpatentable in an IPR proceeding.

30. Although the POSITA is entitled to use "common sense" to arrive at

the conclusion that the claimed invention is obvious, the POSITA must provide a reasoned explanation that avoids conclusory generalizations.

31. An assertion of invalidity cannot be based merely on conclusory statements when dealing with prior art, but must set forth the rationale on which it relies.

32. For an invention to be obvious it is not enough that there be a reason to combine individual elements from different prior art references; the POSITA must also be in possession of sufficient knowledge to know how to incorporate features from one reference into the other reference.

33. Petitioner's expert relies on the following Legal Standard:

A person of ordinary skill often will be able to fit the teachings of multiple references together like a puzzle;

Exhibit 1004, ¶37(f).

34. I understand this to not be a generalized starting point in every analysis because it entirely fails to take into account the specific technology, the complexity of the technology, certain constraints associated with the technology, and the specific documents being relied upon and which are being combined.

## **Dr. Banerjee's Declaration**

35. I have reviewed Dr. Banerjee's Declaration to see how he addresses the issue if it would be possible to fabricate the combinations of elements that he

proposes would be obvious to combine. I note that he stated the following:

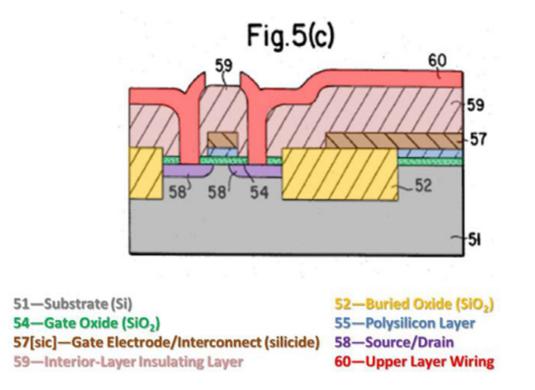

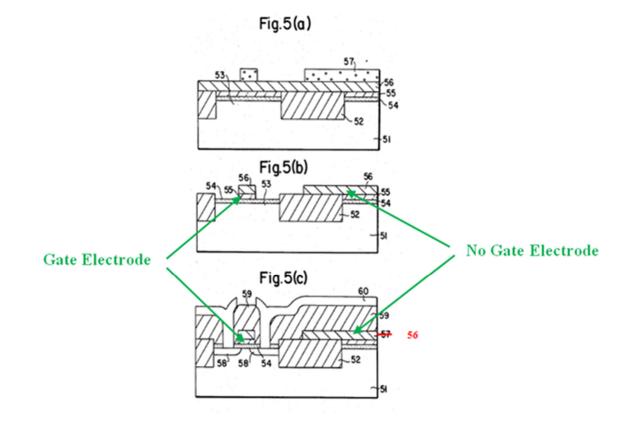

a. *Ogawa* also discusses how to implement this trench isolation with "a series of ordinary steps available in the prior art" that "are employed for production of sources and drains 58, an inter-layer insulating layer 59 and an upper layer wiring 60 for the ultimate purpose of producing a MOS IC." (*Ogawa* at 8:3–7.)

#### Exhibit 1004, ¶79.

b. Moreover, a person of ordinary skill in the art would have understood that replacing *Lee*'s LOCOS with *Noble*'s STI would have been entirely compatible and had <u>no impact on the</u> <u>processes used for gate formation, source/drain formation, L-</u> <u>shaped sidewall formation, silicide formation, or any other</u> <u>aspect of the claims.</u> LOCOS and STI are both methods for forming insulating materials in the same locations of the substrate to perform the same function. They are both performed <u>near the very beginning</u> in device processing, <u>and</u> <u>how the isolation regions are formed would not affect *Lee*'s <u>processes or the resultant device structures.</u> It is therefore my opinion that the combined teachings of *Lee* and *Noble* render the Challenged Claims obvious. (emphasis applied)</u>

#### Exhibit 1004, ¶82.

c. Moreover, a person of ordinary skill in the art would have understood that replacing *Lee*'s LOCOS with *Ogawa*'s trench isolation would have been entirely compatible and <u>had</u> no impact on the processes used for gate formation,

<u>source/drain formation, L-shaped sidewall formation, silicide</u> <u>formation, or any other aspect of the claims</u>. LOCOS and trench isolation are both methods for forming insulating materials in the same locations of the substrate to perform the same function. They are both performed <u>near the very beginning</u> in device processing, and how the isolation regions are formed would not affect *Lee*'s processes or the resultant device structures. (emphasis applied)

Exhibit 1004, ¶198.

d. Other references further demonstrate that replacing *Lee*'s LOCOS with *Ogawa*'s trench isolation would have constituted a simple substitution of one known element for another according to known methods to achieve predictable results.

Exhibit 1004, ¶201

e. *Ogawa* also discusses how to implement this trench isolation with "a series of ordinary steps available in the prior art" that "are employed for production of sources and drains 58, an inter-layer insulating layer 59 and an upper layer wiring 60 for the ultimate purpose of producing a MOS IC. (*Ogawa* at 8:3–7.)

Exhibit 1024, ¶78.

f. Moreover, a person of ordinary skill in the art would have understood that replacing *Lowrey*'s LOCOS with *Noble*'s STI would have been entirely compatible <u>and had no impact on</u> the processes used for gate formation, source/drain formation, L-shaped sidewall formation, silicide formation, or any other

aspect of the claims. LOCOS and STI are both methods for forming insulating materials in the same locations of the substrate to perform the same function. They are both performed <u>near the very beginning</u> in device processing, and <u>how the isolation regions are formed would not affect *Lowrey*'s processes or the resultant device structures. It is therefore my opinion that the combined teachings of *Lowrey* and *Noble* render the Challenged Claims obvious. (emphasis applied)</u>

Exhibit 1024, ¶93.

g. Other references further demonstrate that replacing *Lowrey*'s LOCOS with *Ogawa*'s trench isolation would have constituted a simple substitution of one known element for another according to known methods to achieve predictable results.

Exhibit 1024, ¶166.

h. A person of ordinary skill in the art would have understood that replacing *Lowrey*'s LOCOS with *Ogawa*'s STI would have been entirely compatible and <u>had no impact on the</u> <u>processes used for gate formation, source/drain formation, L-</u> <u>shaped sidewall formation, silicide formation, or any other</u> <u>aspect of the claims.</u> LOCOS and STI are both methods for forming insulating materials in the same locations of the substrate to perform the same function. They are both performed <u>near the very beginning</u> in device processing, <u>and</u> how the isolation regions are formed would not affect *Lowrey*'s processes or the resultant device structures. (emphasis applied) Exhibit 1024, ¶173.

36. I find these statements to be entirely superficial and conclusory. They do not begin to address the numerous considerations and obstacles associated with changing the configuration and processing sequence of an IC. Depending upon the configuration changes required when elements from one reference are substituted into another, such a substitution may well not be within the skill of the POSITA.

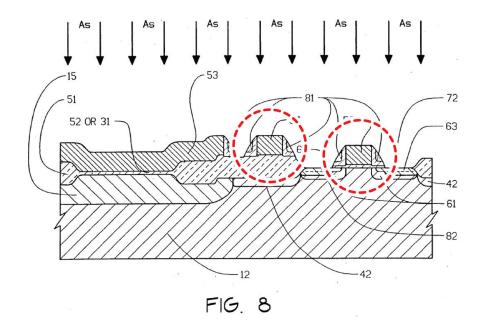

37. By way of example, I strongly disagree that "how the isolation regions are formed would not affect *Lowrey*'s processes or the resultant device structures" and that Noble's STI would have had no impact on the processes used in gate formation, source/drain formation, L-shaped sidewall formation, silicide formation, or any other aspect of the claims. Petitioner has not stated which steps of the references would be combined with one another or how this would be done, but based on the strong recognition in the literature to the effect that "Generally, a change in one phase of the fabrication process usually impacts other phases" (Exhibit 2015, 2:52-53; Exhibit 2016, 2:19-21), Dr. Banerjee is clearly in error when he dismisses the Si IC fabrication process, including the modification of the Si IC fabrication process by substitution of LOCOS isolation with trench isolation as "simple." Such characterization is contradicted by numerous reference articles (see ¶61 herein) and by the fact that hundreds of engineers work for years to

develop process modification in the field of Si ICs.

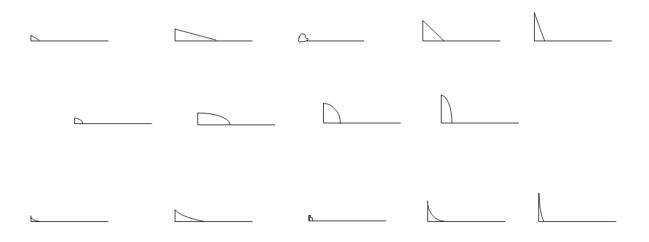

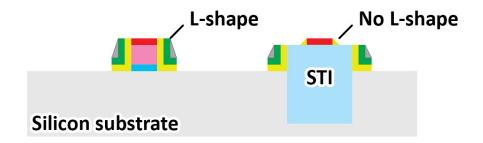

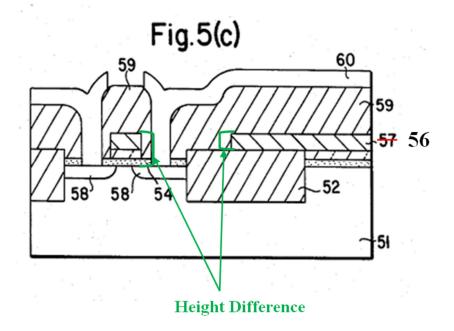

38. By way of example only, when the various references upon which Dr. Banerjee relies have their features combined in a fabrication process that he does not describe, if indeed they can be combined, there is no way of knowing what shape of sidewalls will emerge when relative dimensions are changed and different fabrication processes are used. Depending upon the relative dimensions of the structure on which the sidewalls are formed, the process by which they are formed, the substances of which they are formed, a wide variety of shapes of sidewalls may result. There is no way of knowing which shape actually results from the combinations that Dr. Banerjee is proposing as will be discussed herein. Examples of possible shapes are shown here:

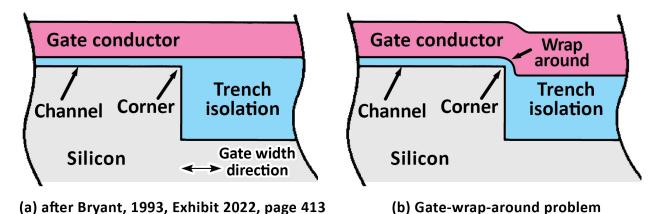

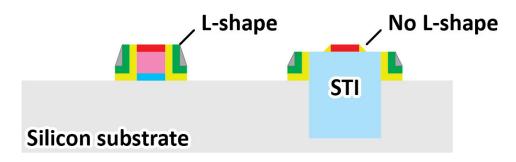

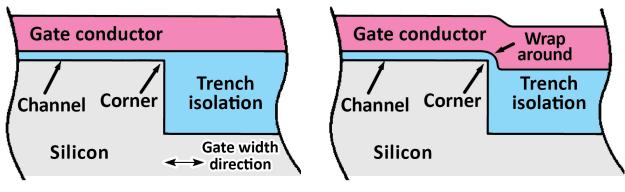

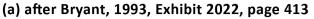

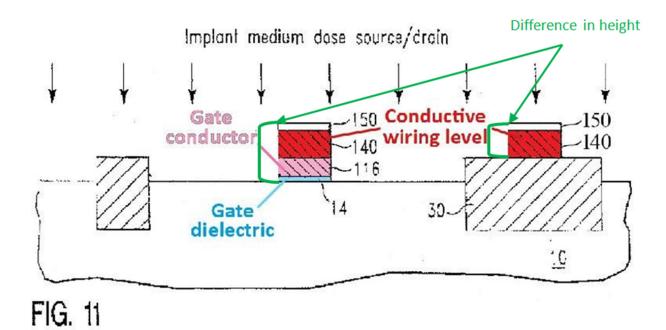

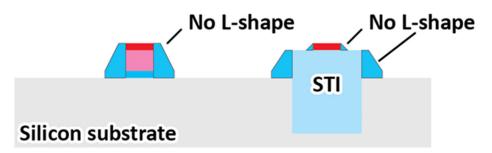

39. Petitioner had no basis for assuming that the sidewalls of the interconnect of *Lee* would remain unchanged when trench isolation is substituted

for LOCOS isolation. This is because upon substitution, the gate conductor stops at the edge of the trench isolation.

# **Technological Background**

## <u>Acronyms</u>

40. For convenience, I list some acronyms that are commonly used in the field of Si IC technology:

| BEOL    | = | Back end of line (interconnect metallization fabrication)         |

|---------|---|-------------------------------------------------------------------|

| CMOS    | = | Complementary MOS                                                 |

| CMP     | = | Chemical mechanical planarization (or polishing)                  |

| CVD     | = | Chemical vapor deposition                                         |

| FEOL    | = | Front end of line (transistor and local interconnect fabrication) |

| FET     | = | Field-effect transistor                                           |

| IC      | = | Integrated circuit                                                |

| LOCOS   | = | Local oxidation of silicon                                        |

| MOS     | = | Metal oxide semiconductor                                         |

| PVD     | = | Physical vapor deposition                                         |

| S, D, G | = | Source, Drain, Gate (respectively)                                |

| STI     | = | Shallow trench isolation                                          |

| TSMC    | = | Taiwan Semiconductor Manufacturing Company (Petitioner)           |

|         |   |                                                                   |

#### Silicon Integrated Circuit (IC) Processing

41. Si integrated circuits (ICs) are highly complex electrical systems on a small microstructured chip. An integrated circuit can have millions of transistors that serve to process, store, and transport information. ICs consist of different units, e.g. a data processing unit for processing information, a memory unit for storing information, and an input / output unit for receiving and sending information.

42. The core element of an integrated circuit is a transistor, specifically the field-effect transistor (FET) that uses an electric field ("field effect") in order to induce charge carriers in the transistor's channel region. The channel region connects the transistor's source (S) with the transistor's drain (D). The source and drain are separated by the gate (G) that controls the flow of charge in the channel between the source and drain.

43. The transistor's gate has a typical three-layer stack consisting of a <u>m</u>etal or metal-like material (M), an insulator or <u>o</u>xide (O), and a <u>s</u>emiconductor (S), thereby forming the MOS layer stack. The top two layers (gate conductor "M" and gate insulating film "O") are called the gate layer stack, or simply gate stack. Accordingly, transistors based on the MOS layer stack are called MOSFETs.

44. There are two types of transistors, those using <u>n</u>egative electrons in the channel (n-channel FET) and those using <u>p</u>ositive holes in the channel (p-

channel FET). The two types of transistors have complementary properties. For example, a *positive* gate voltage induces an *electron* channel in an n-channel FET whereas a *negative* gate voltage induces a *hole* channel in a p-channel FET. If a single voltage is applied simultaneously to the two gates of the two types of transistors, one of them will conduct electricity (ON state) whereas the other one will not conduct electricity (OFF state). Due to the complementary nature of the two types of transistors, the technology is referred to as <u>c</u>omplementary MOS technology or simply CMOS technology. At the present time, the vast majority of ICs are based on CMOS technology.

45. The circuit layout is the result of (i) the circuit functionality designed by design engineers and (ii) how the designed circuit is implemented by a processing sequence devised by process engineers.

46. The processing sequence is carried out in a fabrication facility, also abbreviated as "fab" or "IC fab". Such fabrication facilities are highly advanced facilities that are highly automated so that the handling of Si wafers by humans is minimal. Regarding the processing sequence, we distinguish between a first group of fabrication processes called <u>front end of line</u> (FEOL) processes and a second group of fabrication processes called <u>back end of line</u> (BEOL) processes. The FEOL processes include the fabrication of the actual transistors (MOSFETs) including the silicidation of source, gate, and drain. The BEOL processes include

the fabrication of metal-based interconnect lines and associated dielectric layers (interlayer dielectrics) that electrically insulate the metal interconnects from each other.

47. Hallmarks of IC processing include (i) high spatial precision by means of lithography (to attain very small patterns with nanometer feature sizes) and (ii) cleanliness (to avoid contaminations).

48. The processing of wafers proceeds in a strict sequence of processing steps that are carefully chosen in sequence and content. For example, the gate stack of a transistor requires the availability of a Si substrate. A first step, the deposition or growth of the gate dielectric (commonly an oxide), is followed by a second step, the deposition of the gate electrode (or gate conductor). The processing of Si wafers proceeds in a strict sequence of processing steps (or processing modules) that are carefully chosen in sequence and content.

49. Furthermore, certain elements of an IC require the pre-existence of other elements and rely on their presence for the proper functioning of the ensemble of elements. For example, the source / drain dopant implant commonly requires the presence of the gate electrode so that the gate can mask the channel region from the implantation ion beam. That is, the gate enables the proper definition of the source / drain implanted regions. An implantation process in which the source / drain regions are automatically aligned with the gate electrode is

referred to as a "self-aligned implantation process". Exhibit 2013, p. 5; Exhibit 2014, p.4; Exhibit 2015, 2:52-61; Exhibit 2016, 2:19-24; Exhibit 2017, 6:23-31; Exhibit 2018, 1:18-29; Exhibit 2019, 2:9-19.

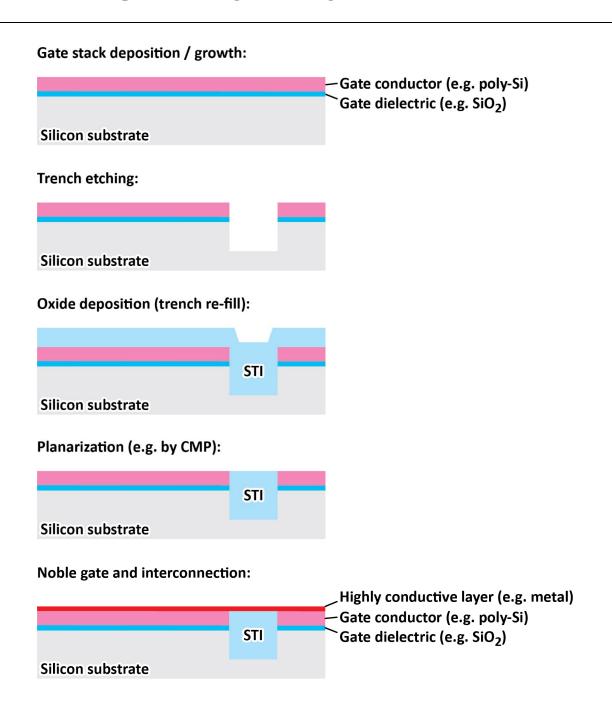

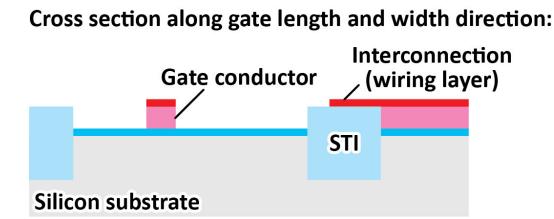

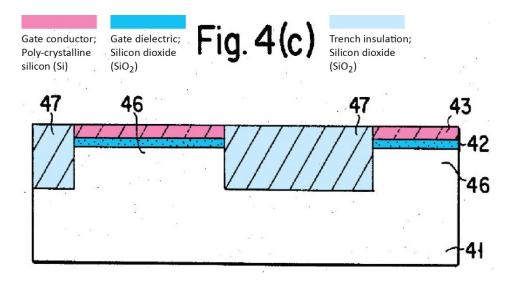

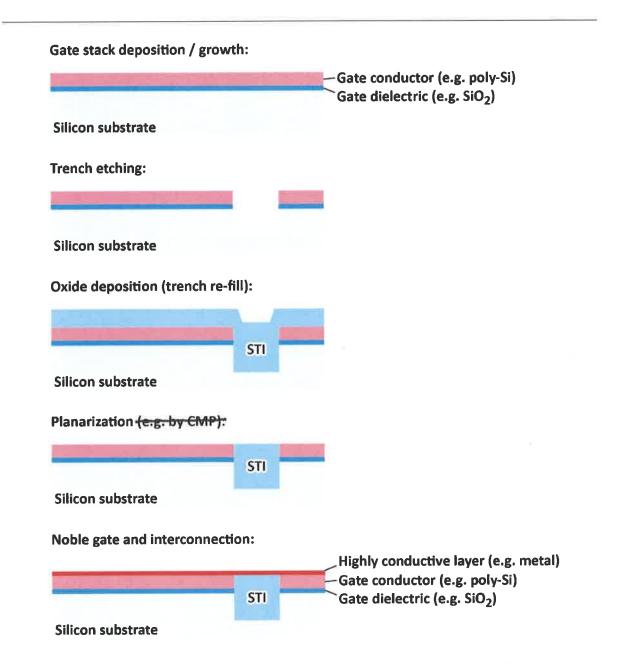

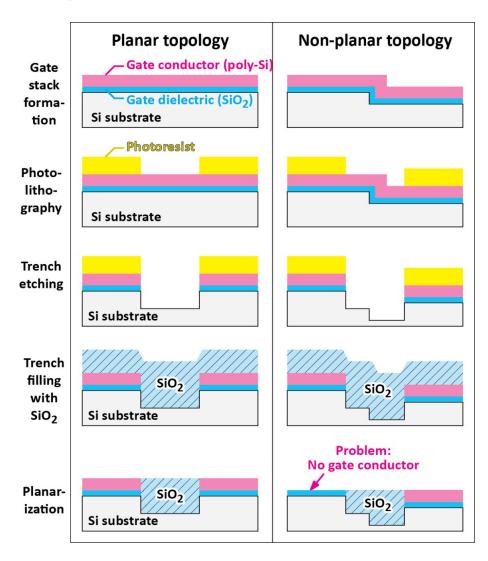

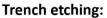

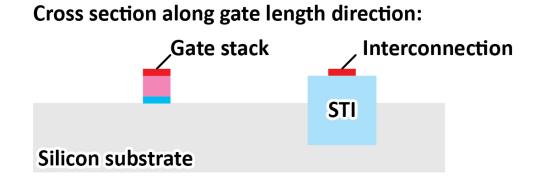

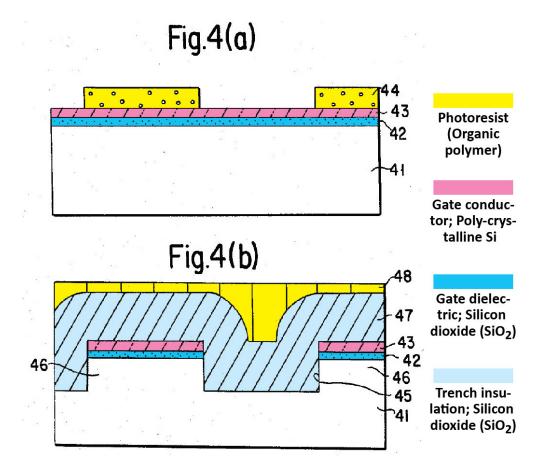

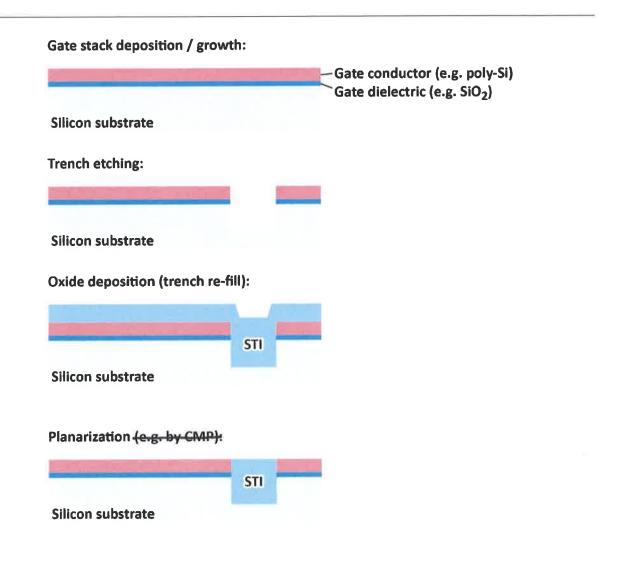

50. It is generally not possible to reverse the sequence of processing steps. A series of individual processing steps constitutes a "processing module". For example, the formation of shallow trench isolation is such a processing module with (i) trench etching, (ii) trench refill with silicon dioxide and (iii) planarization being the major steps of the module.

51. In addition to the major steps of trench formation, there are minor steps not listed above. A more complete series of steps employed for trench formation may include: pad or gate oxide deposition; pad or gate polysilicon deposition<sup>3</sup>; resist coating; photo-lithography; polysilicon etching; oxide etching; *trench etching* by means of a dry etch; resist strip; liner-oxide growth; *trench refill* with CVD silicon dioxide; annealing to improve quality of oxide; *planarization* by CMP (chemical mechanical planarization); various cleaning steps, rinsing steps, and metrology steps are used throughout the module (major steps emphasized).

52. Each processing step (or processing module) is intended and works

<sup>&</sup>lt;sup>3</sup> *Noble* and *Ogawa* use such pad / gate oxide deposition followed by pad /gate poly-silicon deposition sequence.

for a specific *initial* configuration of the Si wafer. Upon completion of the processing step (or processing module), the Si wafer has a new, *final* configuration.

53. That is, each processing step (within a processing module) *transforms* the Si wafer from an *initial configuration* to a *final configuration* associated with this processing step.

54. Likewise, each processing module (with each processing module consisting of a sequence of processing steps) *transforms* the Si wafer from an *initial configuration* to a *final configuration* associated with this processing module.

55. When taking a specific processing step (within one processing module) out of its intended sequence and inserting it at another point in the sequence of processing steps, one must ensure the following: *First*, the sequence of processing steps preceding the specific processing step must provide an initial configuration compatible with the specific processing step. *Second*, the final configuration resulting from the specific processing step must be compatible with the subsequent processing step and beyond.

56. In other words, the initial and final configuration of a wafer associated with a specific processing step must be compatible with the entire fabrication process. As would be understood by a POSITA, a random change in the sequence in processing steps would not lead to the desired result; if done nonetheless, it will

likely lead to a non-functioning IC device. Changing the sequence of processing steps requires that the fabrication process be re-engineered, e.g. the entire frontend-of-line (FEOL) fabrication process may need to be re-engineered. This elucidates that the fabrication of an IC device is based on a specific sequence of processing steps that cannot be changed at random.

57. The same tenet discussed above for processing *steps* also applies to processing *modules*: When taking a specific processing module out of its intended sequence and inserting it at another point in the sequence of processing modules, one must ensure the following: *First*, the processing modules preceding the specific processing module must provide an initial configuration that is compatible with the specific processing module. *Second*, the final configuration resulting from the specific processing module must be compatible with the subsequent processing module and beyond.

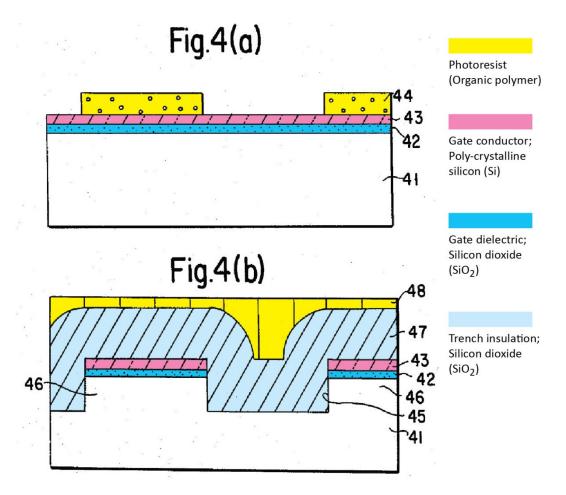

58. As would be understood by a POSITA, a random change in the sequence of processing modules would not lead to the desired result; if done nonetheless, it will likely lead to a non-functioning IC device.

59. For example, trench isolation formation consists of three major processing steps, namely (i) etching the trench, (ii) refilling the trench with CVD oxide, and (iii) planarizing the wafer. Without elaborating further, it would be understood by a POSITA that it would not be possible to change the sequence of

these three processing steps.

60. Planarizing the wafer involves a process that makes the wafer surface planar or flat. The planarization can be accomplished by, for example, a technique called chemical mechanical planarization (CMP). This process uses a chemically enhanced mechanical polishing procedure to planarize or polish a wafer.

61. By 1995, the complexity of integrated circuit fabrication was appreciated by the technical community and widely supported by the technical literature. Quotes illustrating the complexity of fabrication include the following:

The structure of an *integrated circuit is complex* both in the topography of its surface and in its internal composition. Each element of such a device has an *intricate three-dimensional architecture* that must be reproduced exactly in every circuit. The structure is made up of many layers, each of which is a detailed pattern. Some of the layers lie within the silicon wafer and others are stacked on the top. The manufacturing process consists in forming this sequence of layers precisely in accordance with the plan of the circuit designer. (Emphasis added)

Thompson, 1983, Exhibit 2013, p.5.

This photolithography process is repeated (to more than 10 times) before the <u>three-dimensional circuit geometries</u> necessary for a completed metal oxide semiconductor (MOS) or bipolar device are achieved. The <u>structure of an integrated</u>

*circuit is complex*, both in the topography of its surface and in its internal composition. Each element of this device has an intricate three-dimensional structure that must be reproduced exactly in every circuit. The structure is made up of many layers, each of which is a detailed pattern. Some of the layers lie within the silicon wafer and others are stacked on the top. (Emphasis added)

Roland, 1990, Exhibit 2014, p.4.

Generally, <u>a change in one phase of the integrated fabrication</u> <u>process usually impacts other phases</u>. Since integrated circuit fabrication processes are <u>highly complex</u> and require sophisticated equipment, developments of entirely new processes and materials can be quite costly. Thus, new apparatus and methods for control of the CMP process that can be incorporated into current fabrication technology would be highly desirable because expensive modification of equipment and processes can be avoided. (Emphasis added)

Yu, 1994 (U.S. Patent No. 5,314,843), Exhibit 2015, 2:52-61.

*Generally, a change in one phase of the fabrication process usually impacts other phases*. Since semiconductor device fabrication processes are highly complex and require sophisticated equipment, developments of entirely new processes and materials can be quite costly. (Emphasis added)

Meikle, 1993 (U.S. Patent No. 5,231,306), Exhibit 2016, 2:19-24.

The result of these <u>highly complex imaging, deposition and</u> <u>growth, and etching-masking processes</u> is the transformation of each substrate into a large number of integrated circuits which may contain literally tens or hundreds of thousands of individual circuit elements. Once these processes are completed, each wafer is scribed and diced so as to separate it into individual integrated circuits or chips, to which wire leads are then bonded prior to final encapsulation and packaging. (Emphasis added)

Ballard, 1985 (U.S. Patent No. 4,529,621), Exhibit 2017, 6:23-31.

Within the semiconductor industry, production of <u>electronic</u> <u>circuits by very large scale integration ("VLSI") techniques is</u> <u>constrained</u> by a variety of factors which limit yield and <u>inhibit</u> <u>process flexibility</u>. These detrimental factors include, for example, the exposure of wafers to contaminants and/or oxidation during fabrication. Such processing constraints adversely affect mass production of integrated circuits. In addition, conventional processes are slow and inordinately expensive for the fabrication of low-volume products, thus posing an impediment to new device and circuit designs. (Emphasis added)

Ehrlich, 1994 (U.S. Patent No. 5,310,624), Exhibit 2018, 1:18-29.

Depending on the fabrication technologies and techniques, and

the materials used, <u>different configuration constraints apply</u>. These constraints are commonly referred to as <u>"geometric</u> <u>design rules" or "design rules."</u> Design rules include, for example, specifications for minimum spacing between transistors and minimum separation between conductors to prevent shorting, specifications for minimum metal width, and specifications for maximum metal heights and slopes of walls which form metal junctions.

Corbin, II, 1992 (U.S. Patent No. 5,097,422), Exhibit 2019, p. 2:9-19.

62. The above citations directly rebut Dr. Banerjee's out of hand, dismissive, and conclusory statements regarding how the processes of the various references are to be integrated with one another. See ¶35 above.

## Electrical Isolation In Silicon Integrated Circuit Wafers

63. In a silicon (Si) integrated circuit (IC), it is necessary that different circuit elements are electrically isolated from each other. An example of a circuit element is a transistor, specifically a field-effect transistor (FET). A lack of electrical isolation would lead to undesired or parasitic electrical currents between different transistors of the IC. Such parasitic currents would negatively affect the proper functioning of the IC. Electrical isolation features have been used since the first generation of ICs back to the 1960s. The electrical isolation proceeded through several generations:

# 64. *Mesa and pn junction isolation*: Early generations of semiconductor

devices used "mesa structures" (reminiscent of mesa-shaped mountains) and pnjunction structures for the electrical isolation. That is, different circuit elements on a wafer were electrically isolated from each other (i) by being located on different mesas or (ii) by being separated from each other by an electrically blocking pn junction.

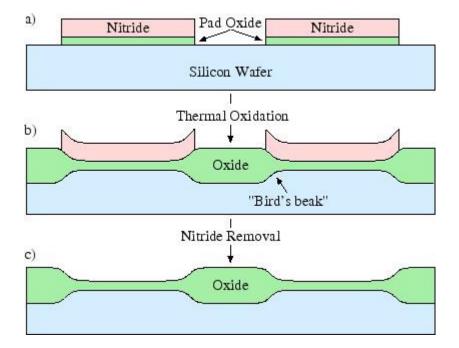

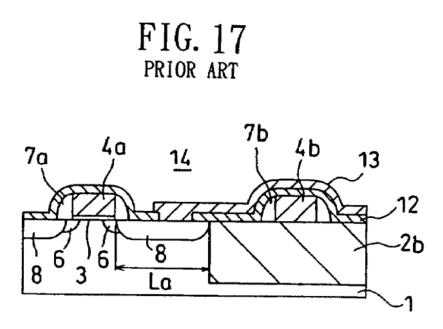

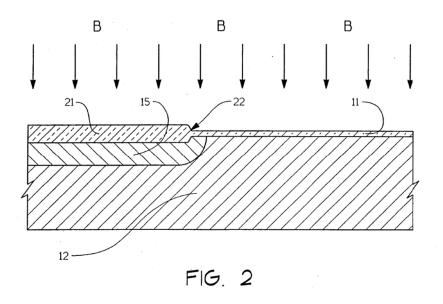

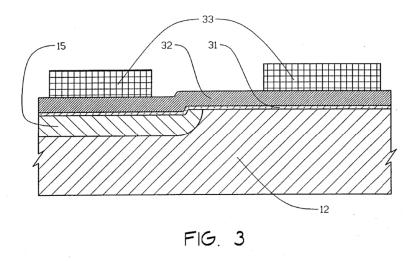

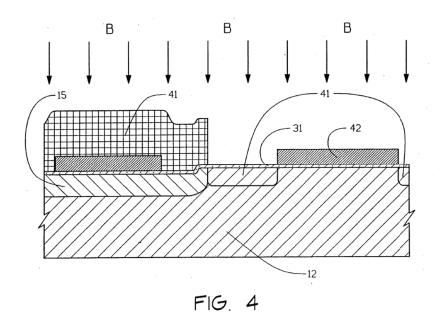

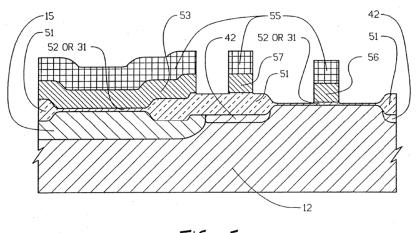

65. *LOCOS isolation*: In the 1970s, 1980s, and early 1990s, a widelyemployed structure for the electrical isolation of circuit elements was LOCOS isolation. LOCOS means "<u>loc</u>al <u>o</u>xidation of <u>s</u>ilicon". The LOCOS process forms a thermal oxide of Si, i.e. SiO<sub>2</sub>, which is a dielectric and thus electrically insulating. The formation of the oxide proceeds through a chemical reaction where the Si of the substrate chemically reacts with oxygen (O<sub>2</sub>) to form SiO<sub>2</sub>. The LOCOS oxide is also called the "field oxide" because it defines the active field where the transistors are located. The "field oxide" is distinguished from the "gate oxide". At the end of the 1990s, LOCOS isolation started to be no longer used in then-stateof-the art Si IC devices. The images below show the process sequence of LOCOS isolation as of 1995:<sup>4</sup>

<sup>&</sup>lt;sup>4</sup> The images are found at: http://www.iue.tuwien.ac.at/phd/hollauer/node7.html

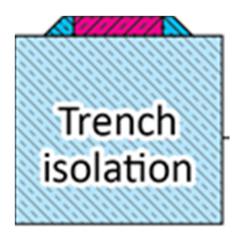

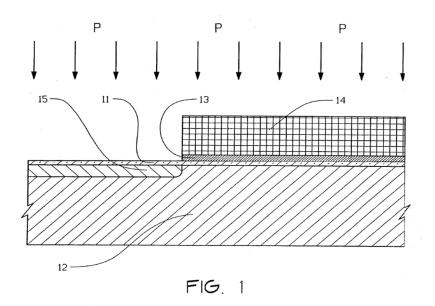

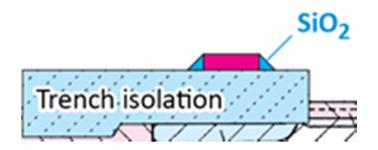

66. *Trench isolation*: A more recent generation of electrical isolation is a trench isolation which is formed by etching a trench, then refilling the trench with a dielectric material (such as  $SiO_2$ ), followed by planarization of the wafer. During planarization, the wafer surface is flattened so that the next processing step is performed on a planar wafer surface. The planarization can be accomplished by, for example, chemical mechanical planarization (CMP)<sup>5</sup>.

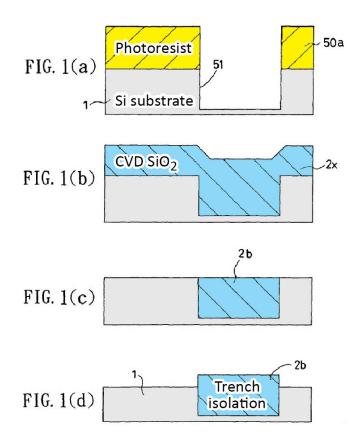

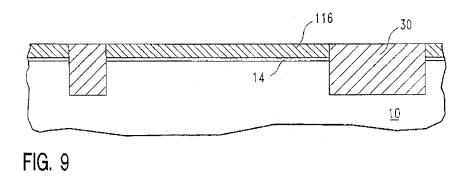

67. The process steps of forming a raised trench isolation disclosed in the '174 patent and illustrated in Figure 1 (shown below) include the (i) etching of a trench ("The silicon substrate 1 is dry-etched by using the resist film 50a as a

<sup>&</sup>lt;sup>5</sup> CMP is an acronym for both "chemical mechanical *planarization*" and "chemical mechanical *polishing*".

mask, thereby forming a trench *51* with a depth of 1 µm." Exhibit 1001, 12:35-37), (ii) refilling of the trench with deposited SiO<sub>2</sub>, e.g. CVD-deposited SiO<sub>2</sub> ("the resist film *50a* is removed, and then a silicon oxide film *2x* is deposited on the entire top surface of the silicon substrate *1*." Exhibit 1001, 12:38-40), and (iii) planarization ("the silicon oxide film *2x* on the silicon substrate *1* is removed by, for example, a CMP (chemical mechanical polishing) method." Exhibit 1001, 12:43-45).

68. CMP is a process that includes a polishing pad that is soaked with a chemical solution. The semiconductor wafer is slightly pressed onto the polishing

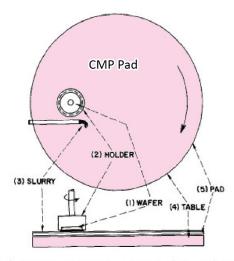

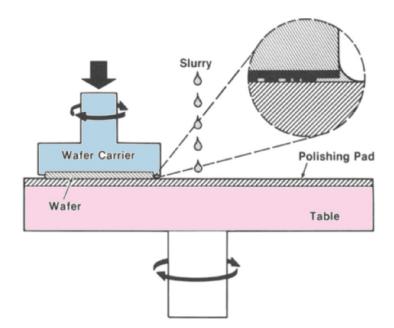

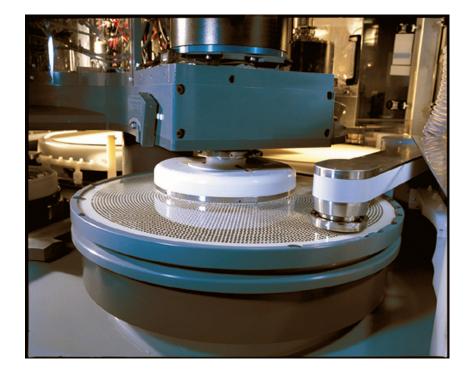

pad. The semiconductor wafer and polishing pad are subjected to rotating motions to ensure uniformity of the CMP process. CMP includes a chemical-etching component and a mechanical-polishing component both of which contribute to the planarization (or flattening) of the wafer surface. Two schematics of the CMP process<sup>6</sup> and a photograph of a CMP tool<sup>7</sup> are shown below. The schematics and photograph show a Si wafer subjected to CMP:

<sup>&</sup>lt;sup>6</sup> The first schematic illustration of the CMP process is from Kaufman et al. from 1992. Exhibit 2032. The second schematic illustration of the CMP process is from Landis et al. from 1992. Exhibit 2033.

<sup>&</sup>lt;sup>7</sup> The photograph shows a CMP tool (Chemical Mechanical Polishing tool) of the Applied Materials Company (<u>http://www.businesswire.com/news/home/</u>

<u>20040711005007/en/AppliedMaterials-Revolutionizes-Planarization-Technology-</u>

<u>Breakthrough-Reflexion</u>). Although this photograph is from after 1995, the basic concept is consistent with a CMP tool from the 1995 timeframe. Exhibit 2004.

# IPR2016-1246; IPR2016-01247 U.S. Patent No. 7,126,174

Fig. 3. Schematic of chemical mechanical-polishing technique, top and side views. For clarity, overarm mechanism connected to wafer holder has been omitted. Wafer (1) is held in holder (2) using commercially available template; slurry (3) flows between wafer surface and pad (5) covered table (4). See text for further details.

# From Kaufman et al. Exhibit 2032.

Fig. 2. Schematic diagram of a chemical-mechanical polish tool.

## From Landis et al. Exhibit 2033

# IPR2016-1246; IPR2016-01247 U.S. Patent No. 7,126,174

### From Exhibit 2004

#### Differences Between LOCOS Isolation And Trench Isolation

69. The two processes, LOCOS isolation and trench isolation, are fundamentally different. The first one, LOCOS, is based on a chemical reaction in which the silicon of the substrate wafer chemically reacts with oxygen according to the chemical reaction  $Si + O_2 \rightarrow SiO_2$ . It lies in the very nature of chemical reactions that they are primarily controlled by the laws of chemistry and only secondarily by process engineering. As a result, the oxidation of Si occurs in areas that are undesirable, specifically, the oxide growth proceeds under a silicon nitride mask that is intended to prevent the oxidation in the first place. The resulting feature is referred to as a "bird's beak" where the tip of the beak is the point that

has intruded deepest under the silicon nitride mask. Due to the chemical nature of LOCOS and the resulting "bird's beak", the LOCOS isolation feature grows to have a greater spatial extent than is desirable.

70. On the other hand, the trench isolation process starts by etching a trench into the semiconductor substrate. If the trench depth is about 1.0  $\mu$ m or shallower, the trench isolation can be referred to as a shallow trench isolation (or STI). Subsequent to etching the trench, it is refilled with SiO<sub>2</sub> (silicon dioxide) typically deposited by chemical vapor deposition (CVD). Subsequently, the wafer is planarized by a suitable planarization technique such as CMP. The planarization step is mandated due to the modulated surface topology created by the refilling of the trench (the CVD SiO<sub>2</sub> indeed coats the entire Si wafer). The planarization creates a planar or flat surface topology that is advantageous for subsequent processing steps.

71. I summarize the differences between LOCOS isolation and trench isolation as follows: (1) LOCOS is based on a chemical oxidation of the Si substrate. Trench isolation does not involve such chemical reaction. (2) Trench isolation requires a planarization step whereas LOCOS isolation does not. (3) The need for planarization (i.e. a flat surface) in conjunction with trench isolation may not be compatible with certain processing steps in conventional fabrication processes particularly if the conventional fabrication processes have produced a

non-planar surface topology before forming a trench isolation. (4) The feature size of the trench isolation is generally smaller than the feature size of the LOCOS isolation (field oxide). (5) The Si / SiO<sub>2</sub> interface of trench isolation is more prone to contamination than the Si / SiO<sub>2</sub> interface in LOCOS. This is because the unfilled (empty) trench (once "dug" out) is subject to unavoidable surface contamination. The fact that the interface in LOCOS is formed by chemical reaction involving the Si substrate makes it one of the cleanest interfaces attainable. As a consequence, the magnitude of the leakage current and the associated transport mechanism is different for LOCOS isolation and trench isolation.

#### LOCOS Isolation And Trench Isolation Are Not Functionally Equivalent

72. Dr. Banerjee characterizes LOCOS isolation and shallow trench isolation (STI) as "functionally equivalent":

Trench isolation techniques, such as shallow trench isolation (STI), replaced LOCOS to avoid the scaling problem of the latter. In STI, selected areas of a substrate are etched to form trenches, which are filled with insulating material. Although marginally more expensive and complex than LOCOS, STI does not encroach laterally into neighboring regions, thus resolving the problems of LOCOS. Because the two processes are so similar otherwise, STI and LOCOS are interchangeable

and functionally equivalent.

(Exhibit 1004 and 1024, ¶52-53; internal citations omitted).

73. I disagree with Dr. Banerjee in this regard. My detailed discussion of LOCOS and trench isolation (see above) make it abundantly clear that the two processes are fundamentally different and cannot be simply swapped out of one process into another without considering the multitude of consequences that will result from such swap.

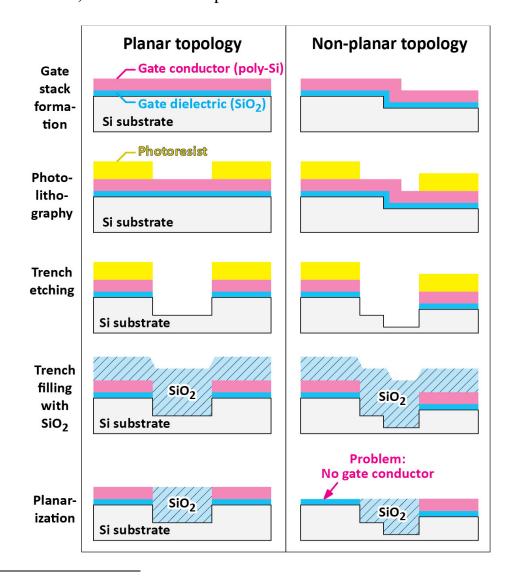

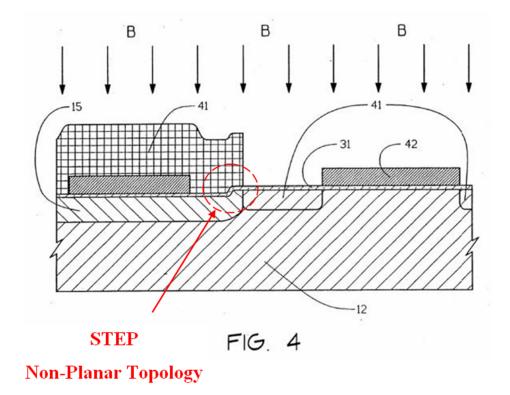

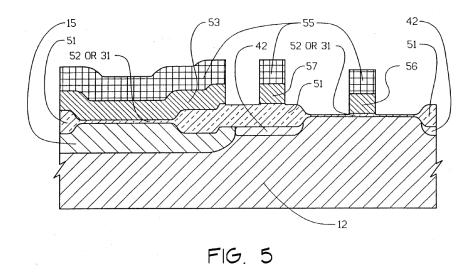

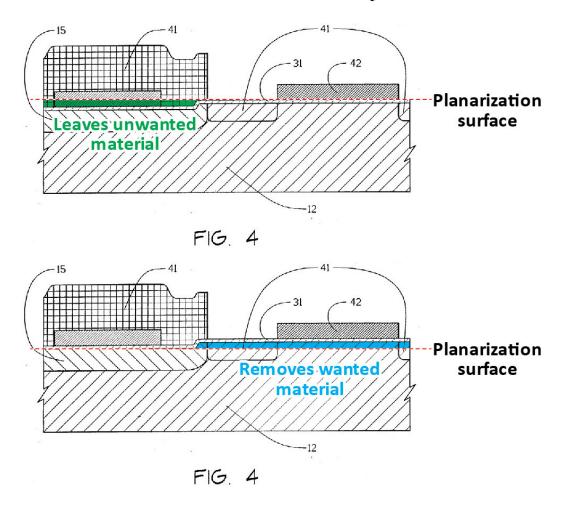

74. As an example, we consider a wafer having a non-planar surface topology, i.e. a wafer that, much like a landscape, has a modulated surface topology that varies in height, i.e. has "hills" and "valleys". Assume that such non-planar wafer is being prepared for the formation of a trench isolation. Given that the wafer's initial configuration includes a non-planar surface topology and given that the trench isolation formation concludes with a planarization step, e.g. by CMP, creates the following dilemma: Since the entire wafer is subject to planarization, a wafer-wide planar surface topology will be created, so that (i) some of the above-mentioned "hills" may be chopped off and / or (ii) some of the above-mentioned "valleys" may remain filled with oxide. Neither one of these

scenarios is acceptable.<sup>8</sup> This is because a semiconductor wafer that is being processed consists of a multitude of films that can be as thick as several 100 nm (for example interconnect-layer dielectrics) and as thin as one or a few nm (for example the gate dielectric). If planarization is performed on a wafer exhibiting a non-planar surface topology, one or more of these layers may be physically interrupted thereby creating an open circuit and potentially rendering the IC non-functional.

75. That is, as a primary consequence, "hilltops" of the modulated surface may be chopped off and/or "valleys" may remain filled with insulating material. As secondary consequences, vital elements of the wafer may be removed and/or vital elements that should be exposed become undesirably buried. In 1995, a POSITA using the CMP process would not have had the means of addressing the problems arising from the non-planar topology.

76. In his declaration, Dr. Banerjee does not address at all the planarization process that is associated with trench isolation formation. Furthermore, Dr. Banerjee gives no consideration to the interference of the

<sup>&</sup>lt;sup>8</sup> One can consider a third intermediate scenario in which hilltops are partially chopped off and valleys remain partially filled. This scenario would be unacceptable as well.

planarization process with a wafer's non-planar surface topology. Dr. Banerjee's consideration in this regard is insufficient because the effect of planarization on a non-planar surface topology will render the IC non-functional. Indeed, the employment of trench isolation on a wafer having non-planar surface topology would generally result in a non-functioning IC device unless the fabrication process is completely re-engineered. Dr. Banerjee never says how this could be done while still achieving the final structure recited in the challenged claims of the '174 patent. The purpose of the CMP process is to *planarize* the wafer surface. To suggest otherwise would be contrary to the basic purpose and teachings associated with the CMP tool. This is particularly true in 1995 when CMP tools were not as advanced as they are at the present time (2017).

77. As I have pointed out, the technical literature has detailed the complexity of Si IC fabrication numerous times. Quotes from the technical literature elucidate the small tolerances, highly constrained processes, and highly complex processes common in the art of Si ICs: "The structure of an integrated circuit is complex [...] intricate three-dimensional architecture [...] three-dimensional circuit geometries [...] structure of an integrated circuit is complex [...] a change in one phase of the integrated fabrication processes usually impacts other phases [...] integrated circuit fabrication processes are highly complex [...] Generally, a change in one phase of the fabrication process usually impacts other

phases [...] highly complex imaging, deposition and growth, and etching-masking processes [...] electronic circuits by very large scale integration ("VLSI") techniques is constrained ... which ... inhibit process flexibility [...] different configuration constraints apply" (Exhibits 2013-2019). Accordingly, details, such as the non-planar topology of a Si IC, are highly relevant and cannot be ignored.

78. If CMP is performed on a wafer surface having a non-planar topology, a multitude of problems are created: They include unintended electrical short circuits (undesired electrical connections) and unintended electrical open circuits (undesired electrical disconnects).

79. In 1995, CMP was in fact not used on a wafer having non-planar surface topology (such as *Lowrey*). Indeed, the suggestion that CMP in 1995 could have been used for non-planar surface topologies is contrary to the very nature and purpose of CMP.

80. I find it difficult to understand that Dr. Banerjee, when describing the trench isolation process, neither discloses nor discusses the planarization process that is part of trench isolation fabrication. The planarization will necessarily interfere with a modulated or non-planar topology of a partially processed Si wafer surface.

81. Petitioner's invalidity arguments assume that a POSITA could easily replace the conventional LOCOS isolation of *Lee* and *Lowrey* with the non-

conventional trench isolation of *Noble* and *Ogawa*. Petitioner's assumption is misguided. A POSITA would understand that the establishment of a new process involving trench isolation would, in the best case, require a significant reengineering of the fabrication process, and, in the worst case, not be possible because the combination would result in a non-functional device.

82. I agree with Dr. Banerjee that LOCOS isolation and trench isolation serve the purpose of electrically isolating different active areas of an IC. However, I disagree with Dr. Banerjee that LOCOS and STI are "functionally equivalent". "Functionally equivalent" implies that they would function in an equivalent manner. However, there are fundamental differences in the way these features function and are fabricated as discussed above.

83. Because of the above-discussed fundamental differences, *different components and configurations are necessary* at the initial stage, during the process, and at the final stage of LOCOS and trench isolation. Accordingly, I am unable to agree that LOCOS and trench isolation would be "functionally equivalent".

#### Difficulties Of Employing STI On Wafers Having A Non-Planar Topology

84. Performing the trench isolation process on a wafer having a nonplanar surface topology (i.e. a surface topology that varies in height and thus has "hills" and "valleys") is difficult or impossible for the reasons explained below.

85. Consider LOCOS isolation being performed on such modulated surface topology. This can be done since the LOCOS structure will add a local isolation feature to the wafer (the local isolation feature includes the LOCOS field oxide plus the two bird's beak regions).

86. Next consider the shallow trench isolation (STI) process being performed on such modulated surface topology keeping in mind that the STI process concludes with a required planarization step. When deposited, the material filling the trench (commonly SiO<sub>2</sub>) will follow the "hilltops" and "valleys" of the wafer's modulated surface topology. Upon planarization, a key question is: How far should the planarization proceed? If the planarization stops relatively early, the "valleys" will remain filled with SiO<sub>2</sub>; this is an unwanted effect.

87. On the other hand, if the planarization stops relatively late, the "hilltops" will be cut off; this is an unwanted effect as well.<sup>9</sup> In other words, every possible level at which the planarization is terminated would result in an unwanted effect (either filling in the valleys or cutting off the hilltops or both). That is, any planarization level chosen would damage at least some part of the pre-existing modulated surface topology. This makes it difficult or impossible to use trench

<sup>&</sup>lt;sup>9</sup> Planarizing the wafer to an intermediate level would leave unwanted material in "valleys" and cut off wanted materials at "hilltops".

isolation, particularly its planarization, on a preprocessed wafer that exhibits a modulated surface topology (and a POSITA in 1995 would not have proceeded this way).

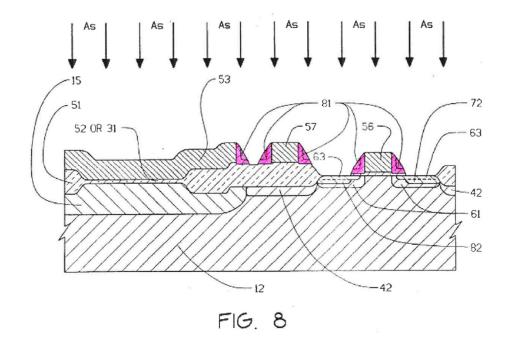

88. *Lowrey* is an example of a modulated surface topology. Indeed, *Lowrey* has several processing steps that precede the LOCOS process. Dr. Banerjee does not explain in his Declaration how or when the required planarization would be performed if a trench isolation were to be substituted for LOCOS isolation.

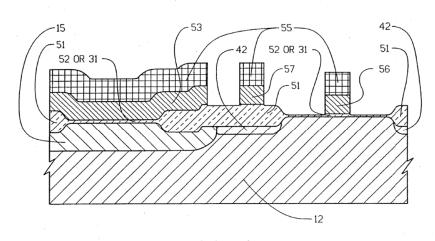

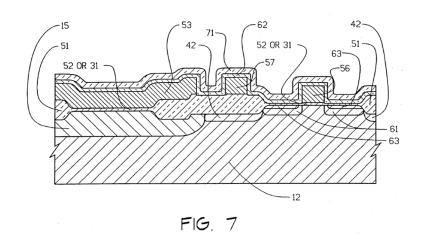

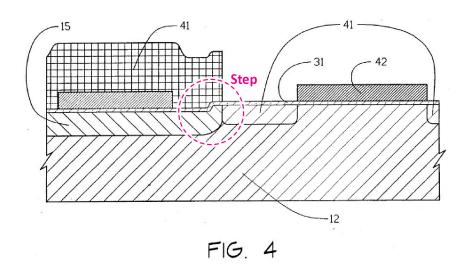

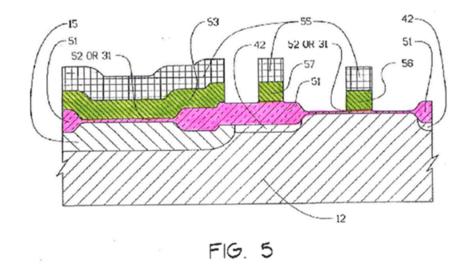

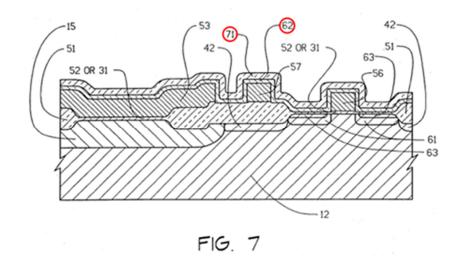

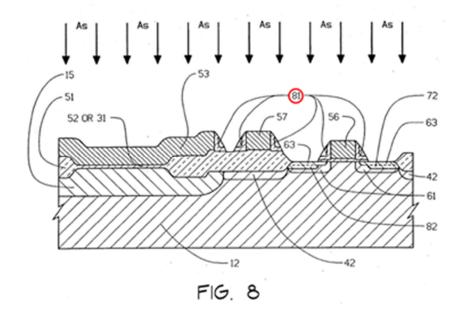

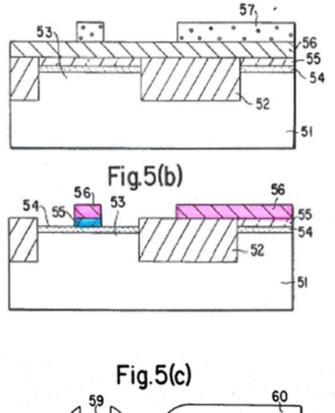

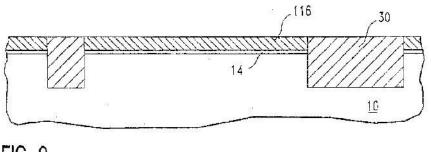

89. *Lowrey* describes a process sequence by means of several figures that illustrate the process flow. *Lowrey*'s Figures 1-4 illustrate the modulated features resulting from processes that precede LOCOS. *Lowrey*'s Figure 5 illustrates the LOCOS field oxide feature.

90. In summary, if one were to substitute trench isolation for LOCOS isolation, one would face the above-detailed dilemma of how to choose a planarization level that would not damage some part of the pre-existing modulated surface topology. Accordingly, it is difficult or impossible to form trench isolation features at a later stage of the processing, particularly at a stage when the wafer has a non-planar modulated surface topology (and a POSITA in 1995 would not have proceeded this way).

91. The Petition fails to address the fact that when combining references relating to semiconductor devices, the process ("process sequence") by which the integrated circuit (IC) devices are formed is inseparable from their final structure as claimed. As such, simply substituting a component from one device, *e.g.*, STI, for a different component in another device, *e.g.*, LOCOS isolation, can provide unworkable results, both in terms of how the substituted component cooperates with other components, and how the changed manufacturing sequence, which is required to effectuate such substitution, can be implemented. This is particularly true for Si ICs where a single film can serve multiple purposes, and where a multitude of different functional features are condensed into a minimum number of layers and processing steps.

92. Petitioner's obviousness arguments simply take out the LOCOS isolation (*Lee and Lowrey*) for the STI (*Noble* and *Ogawa*) without describing how such a substitution could be accomplished and without giving due consideration to the strong interconnectedness and interdependency of the Si IC fabrication process. A LOCOS isolation is formed using a very different process sequence than the process sequence used to form a STI. To produce an operative device, their very different respective fabrication processes must be merged, integrated, and made

compatible with their respective gate stack and interconnect stack fabrication processes. If this is not possible, a merged structure will not be possible.<sup>10</sup>

93. Petitioner never once addresses how and when *Noble's* and *Ogawa's* STI can be substituted in for *Lee or Lowrey's* LOCOS isolation. Indeed, it would have been apparent to a POSITA at the time of invention that the incompatible process sequences for forming the STI disclosed in *Noble* or *Ogawa* would not have been substitutable for the LOCOS isolation of *Lee or Lowrey*, and as such, there would have been no motivation for the POSITA to substitute the LOCOS isolation of *Lee or Lowrey* with the STI of *Noble* or *Ogawa*.

94. It is recognized that both LOCOS isolation and trench isolation serve the purpose of electrically insulating transistors of a Si IC device. However, LOCOS isolation and trench isolation are created by fundamentally different fabrication processes. LOCOS isolation is based on the oxidation of the Si wafer

<sup>10</sup> I understand that it would have been the burden of Petitioner to show that a fabrication process that follows from the various combinations of *Lee*, *Lowrey*, *Noble* and *Ogawa* would have obviated the '174 patent. To meet its burden, Petitioner could have provided a pictorial or narrative process flow of the combined prior art references. However, I was not provided with such pictorial or narrative process flow.

by means of a high-temperature chemical reaction (LOCOS means Local *Oxidation* of Si). The oxidation process proceeds according to the laws of chemistry and thus creates the undesired yet unavoidable bird's beak. In contrast, trench isolation does not involve such problematic oxidation of the Si wafer by means of a chemical reaction and therefore does not create the undesired bird's beak. Any discussion on the substitution of LOCOS isolation with trench isolation must take into account these differences.

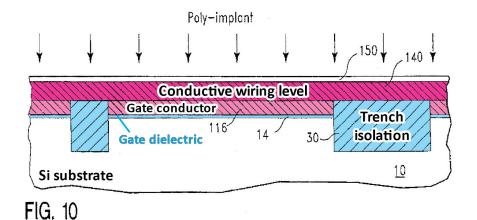

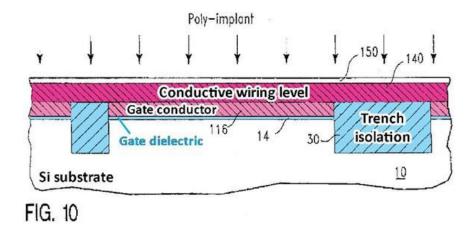

95. *Noble* and *Ogawa* are aware of these differences and for this reason employ trench isolation by using a process sequence that starts with the deposition of the gate stack (gate insulating film plus the gate conductor) followed by trench etching, trench refilling with an oxide, and CMP. This is contrary to *Lee* and *Lowrey* who are able to deposit the gate stack on the (LOCOS) isolation. *Noble* and *Ogawa*, cannot deposit the gate stack on the (trench) isolation. *Accordingly*, **although some documents say that LOCOS isolation and trench isolation can substitute for each other, that entirely misses the point because** review of the detailed process sequence elucidates that the two processes, as practiced by each of the combinations (*Lee* with *Noble*, *Lee* with *Ogawa*, *Lowrey* with *Noble*, and *Lowrey* with *Ogawa*), are incompatible.

96. Furthermore, the inventors of *Lee* and *Lowrey* were aware of trench isolation (to be discussed later). Despite their awareness, they did not suggest that

LOCOS isolation could be substituted by trench isolation. This suggests that *Lee* and *Lowrey* understood that the underpinning process design must be taken into account and that the replacement of LOCOS isolation by trench isolation is not a matter of simple substitution. Exhibit 2021, 1:8-9; Exhibit 2031, 2:23-28.

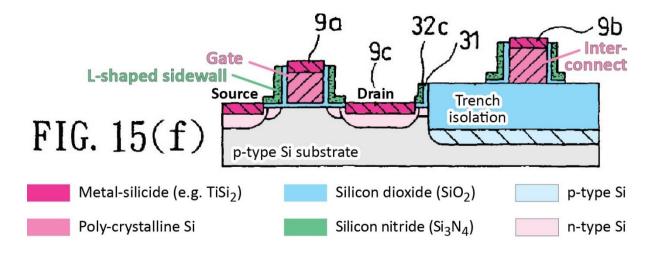

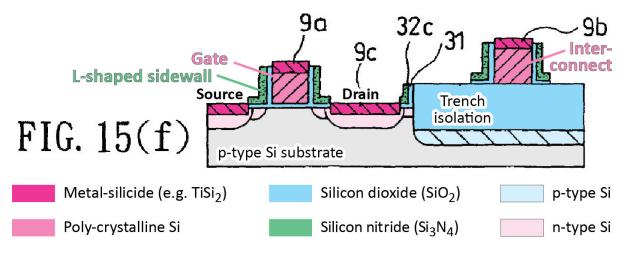

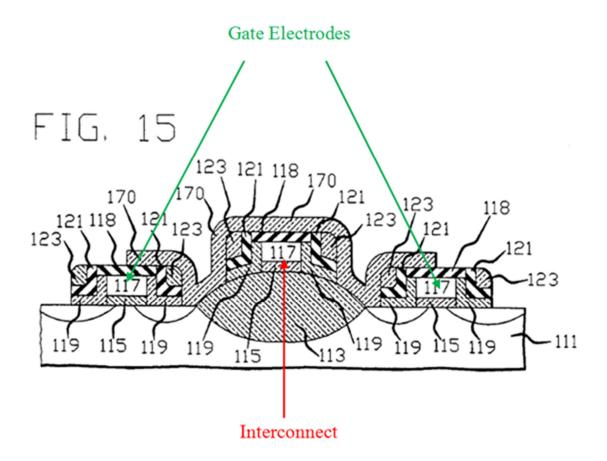

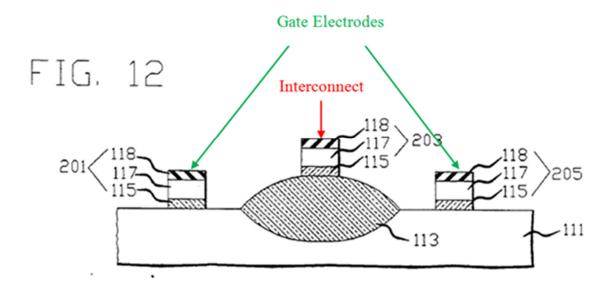

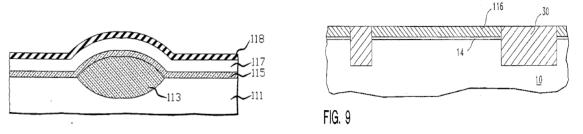

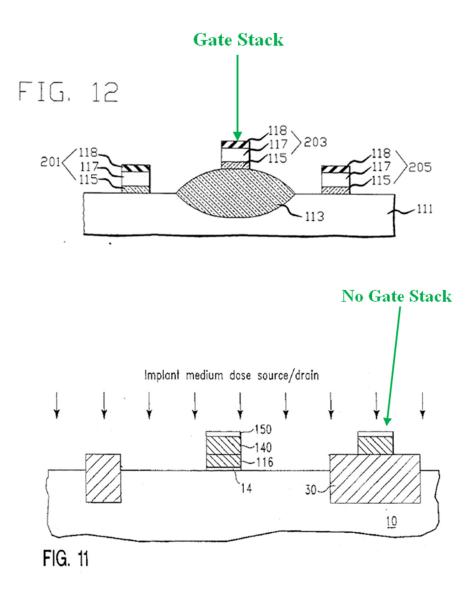

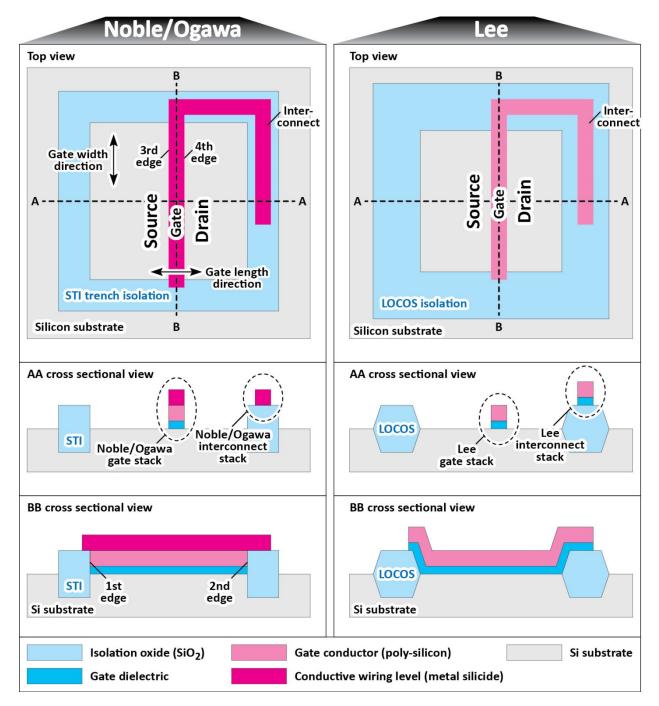

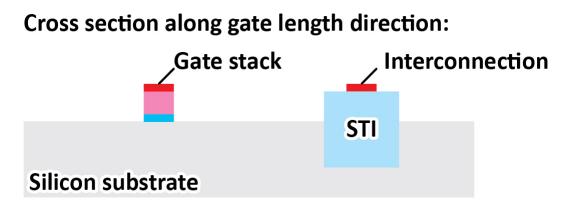

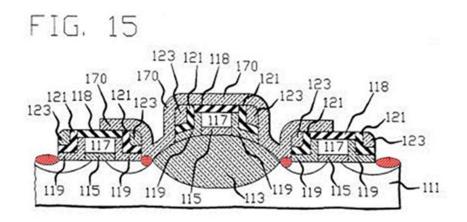

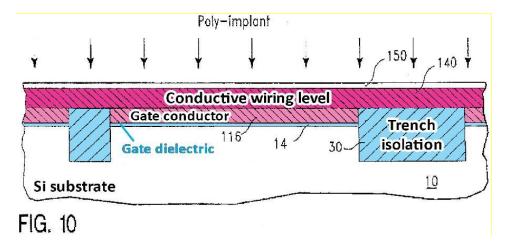

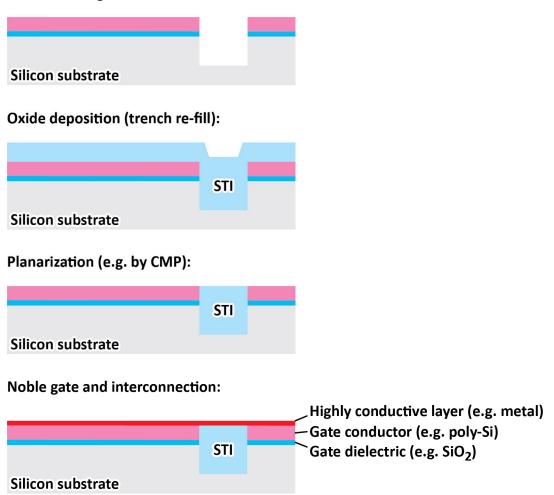

#### The Invention Of Claim 1 Of The '174 Patent

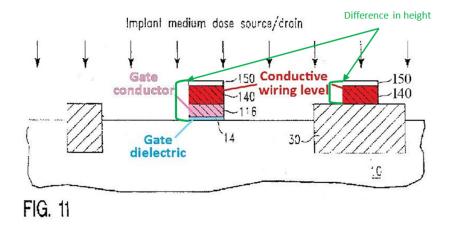

97. The '174 patent (Exhibit 1001) is directed to a semiconductor device comprising a trench isolation surrounding an active area of a semiconductor substrate. A gate insulating film is formed over the active area, and a gate electrode is formed over the gate insulating film. First L-shaped sidewalls are formed over the side surfaces of the gate electrode with first silicide layers formed on regions located on the sides of the first L-shaped sidewalls within the active area, and with an interconnection formed on the trench isolation. Second L-shaped sidewalls are formed over the side surfaces of the surfaces of the interconnection.

98. The '174 invention is directed to a semiconductor device which includes a number of claimed elements as part of a device. Thus, when combining prior art references in order to reproduce the '174 patent, it is insufficient to simply pluck out specific components from various prior-art devices and then re-assemble these components to re-construct the device claimed in the '174 patent. Not only the components themselves but also the fabrication process of how they are configured in a device must be considered. How the components are positioned

and connected in a device depends on how the device and its components have been fabricated.

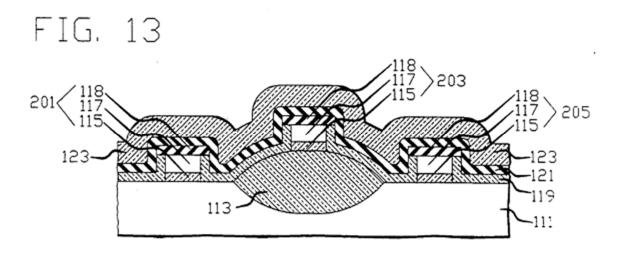

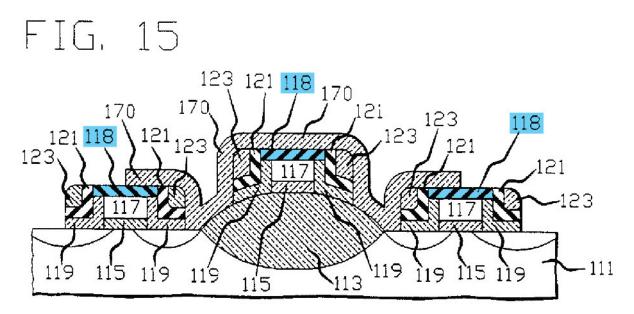

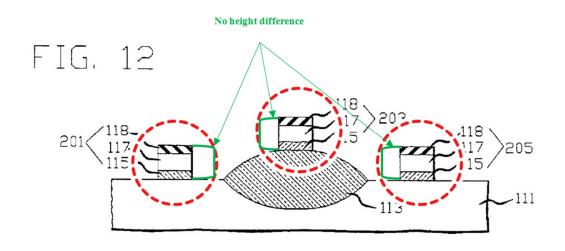

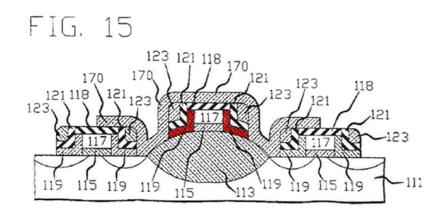

99. Fig. 15(f) of the '174 patent above illustrates a semiconductor device comprising a trench isolation (blue) surrounding an active area of a semiconductor substrate; a gate insulating film formed over the active area (blue); a gate electrode formed over the gate insulating film (pink); first L-shaped sidewalls formed over the side surfaces of the gate electrode (green); first silicide layers formed on regions located on the sides of the first L-shaped sidewalls within the active area (dark pink); an interconnection formed on the trench isolation (pink); and second L-shaped sidewalls formed over the side surfaces of the side sidewalls within the active area.

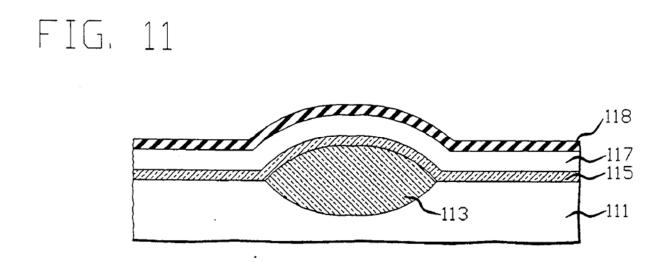

100. An intricate process is necessary to fabricate the device shown Fig. 15(f). Fig. 15(f) is identified as Embodiment 10 of the '174 patent. Exhibit 1001, 26:35 *et seq.* To explain how the device of Fig. 15 is formed, the specification refers back to Embodiment 8, depicted in Figs. 12 and 13. *Id.*, 26:36–27:51.

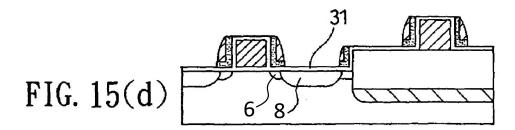

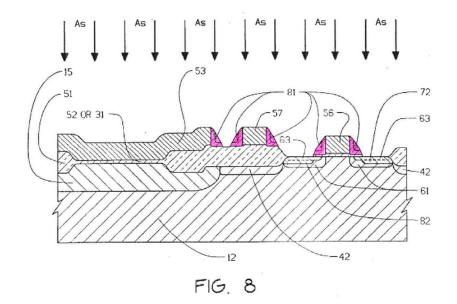

101. The '174 patent devotes several columns and Figures describing the fabrication process to form the structure of Figure 15(f). "Now, the manufacturing procedures for realizing the structure shown in FIG. 12 will be described referring to FIGS. 13(a) through 13(e)." Exhibit 1001, 22:12-53. In the embodiment shown, the gate electrode 4a (through polysilicon film 4x) is applied after the trench isolation is formed (Fig. 13(c); Exhibit 1001, 22:66-23:6).

#### Benefits Of The Claimed Features Of The '174 Patent And Their Synergies

102. The '174 related to Si integrated circuit (Si IC) fabrication. Si IC fabrication is a multi-hundred-billion-dollar business. Decades ago, more than 100 companies were active in the fabrication of Si ICs. At the present time, there are about 20 major companies active in the field of Si integrated circuits. All fabrication technology has in common that it is based on complementary MOS (CMOS) field-effect transistors, i.e. a combination of n- and p-channel MOSFETs. Each MOSFET has three electrodes, the source (S), gate (G), and drain (D) with the gate consisting of at least a gate insulating film and a gate conductor.

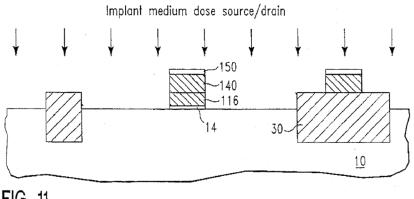

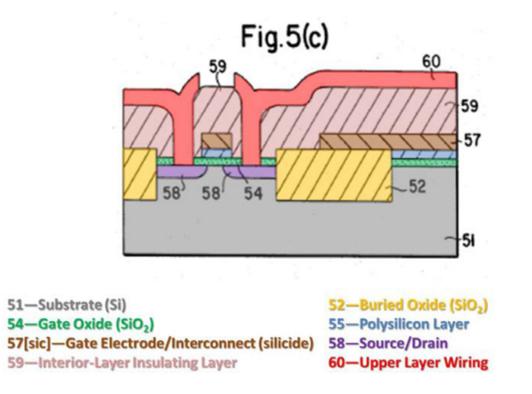

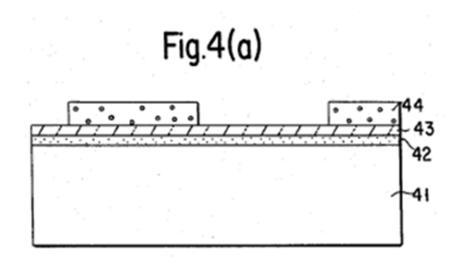

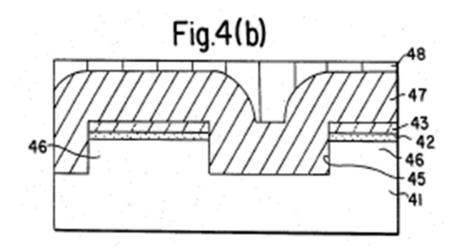

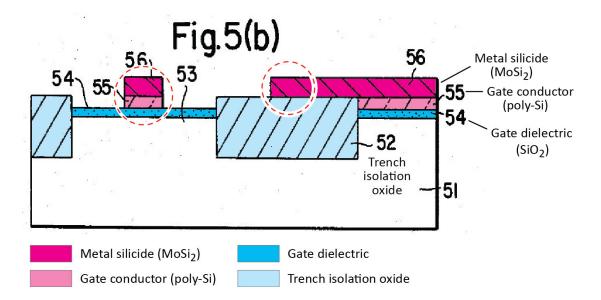

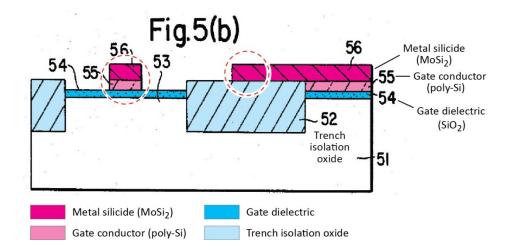

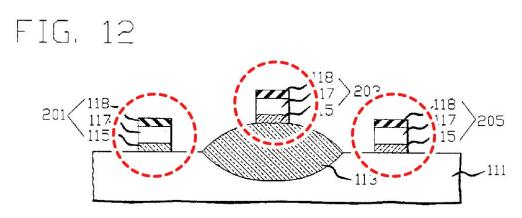

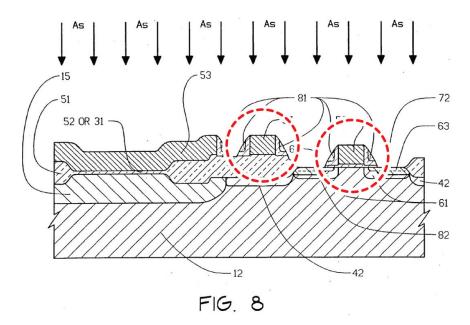

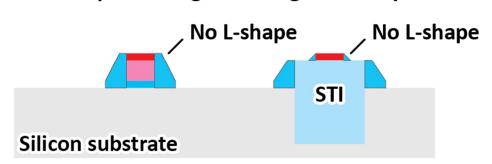

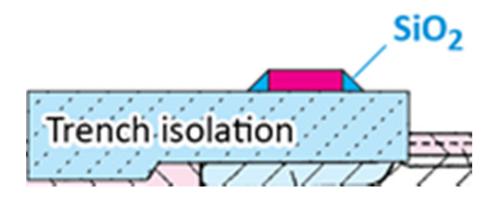

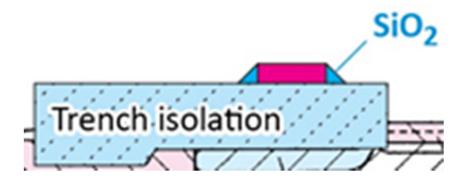

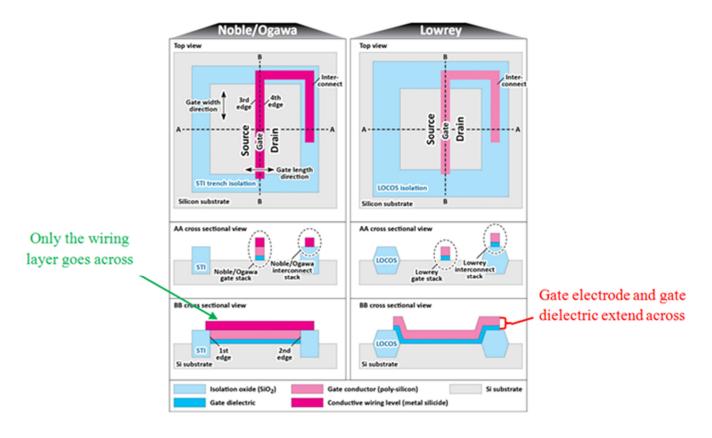

103. Transistors or groups of transistors generally need to be electrically