# AT&T DSP3210 Digital Signal Processor The Multimedia Solution

# **Features and Benefits**

| Feature                                                                                                                                                                                                                 | Benefit                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor bus compatibility:<br>32-bit, byte-addressable address space<br>Retry, relinquish/retry, and bus error support<br>Page mode DRAM support<br>Direct support for both 680x0 and 80x86 signaling            | Designed for efficient bus master designs allowing<br>the DSP3210 to easily be incorporated into $\mu$ P-<br>based systems. The 32-bit, byte-addressable<br>space enables the DSP3210 and a $\mu$ P to share<br>common address space and pointer values as well. |

| <ul> <li>AT&amp;T VCOS ™ operating system:</li> <li>Real-time, multitasking operating system</li> <li>Uses host rather than local memory</li> <li>True parallel processing</li> <li>Complete task management</li> </ul> | <ul> <li>Open development environment:</li> <li>Dramatically lower system costs</li> <li>Full utilization of both μP and DSP3210</li> <li>Simplifies both algorithm and application development</li> </ul>                                                       |

| Full 32-bit floating-point arithmetic<br>C-like assembly language<br>Single-cycle PC relative addressing                                                                                                                | Ease of programming/higher performance.                                                                                                                                                                                                                          |

| All instructions are single-cycle<br>(four memory accesses per instruction cycle)                                                                                                                                       | Higher performance.                                                                                                                                                                                                                                              |

| Access to DSP32C programs                                                                                                                                                                                               | Access to the largest existing 32-bit DSP SW base.                                                                                                                                                                                                               |

| Logic Automation* model                                                                                                                                                                                                 | Faster, more efficient system development.                                                                                                                                                                                                                       |

# Introduction

The DSP3210 brings the power of floating-point signal processing to personal computers and workstations, opening a wide range of multimedia applications. The DSP3210 has been engineered with a single focus: to enable advanced multimedia applications in personal computers and workstations. Based on AT&T's DSP32C architecture, the DSP3210 has the unique ability to be integrated into personal computer and workstation system designs. Particular attention is paid to primary bus interfacing; the DSP3210 is compatible with both 80x86 and 680x0 microprocessor signaling. This allows designers to easily create low-cost systems by using the DSP3210 as a bus-master device. A full, bus-level SmartModel<sup>#</sup> of the DSP3210 is offered by Logic Automation, Inc. for system simulation of designs incorporating the DSP3210.

Along with its optimizing C-compiler and assemblylanguage software tools, the DSP3210 is further supported with AT&T's VCOS operating system.

The VCOS operating system provides a powerful realtime, multitasking and multiprocessing environment which effectively manages multimedia applications across various computer platforms. By employing innovative task- and code-management techniques, VCOS operating system allows the DSP3210 to use existing system memory in PCs and workstations rather than expensive dedicated SRAM for DSP program and data storage.

Complete real-time debugging tools are included to speed both application and algorithm development. By separating the application and algorithm development phases of multimedia software creation, the VCOS operating system greatly simplifies and shortens development schedules.

\* Logic Automation and SmartModel are registered trademarks of Logic Automation, Inc.

PUMA Exhibit 2006

DOCKE

RM

### **Table of Contents**

Page

#### Contents

DOCKE

Δ

Δ

| Features and Benefits                                                              | 1                                     |

|------------------------------------------------------------------------------------|---------------------------------------|

| Introduction                                                                       |                                       |

| Applications                                                                       |                                       |

| PC/Workstation Multimedia Applications                                             |                                       |

| DSP3210 Motherboard Implementations                                                | ـــــــــــــــــــــــــــــــــــــ |

| DSP3210 Add-In Cards                                                               | 4                                     |

| System Integration Under the VCOS Operating System                                 | 5                                     |

| Functional Description                                                             | 5                                     |

| Functional Units                                                                   |                                       |

| Control Arithmetic Unit (CAU)                                                      | 5                                     |

| Data Arithmetic (DAU)                                                              | 5                                     |

| On-Chip Memory                                                                     |                                       |

| Bus Interface                                                                      | 6                                     |

| Serial I/O (SIO)                                                                   |                                       |

| DMA Controller (DMAC)                                                              | 7                                     |

| Timer/Bit I/O                                                                      |                                       |

| DSP3210 Instruction Set                                                            | 7                                     |

| Processor Control Features                                                         | 7                                     |

| Serial I/O DMA                                                                     | 7                                     |

| Exception Processing                                                               | 8                                     |

| Low-Power, Powerdown Mode                                                          | 8                                     |

| Boot ROM Code                                                                      |                                       |

| F12 Silicon Revision                                                               | 8                                     |

| Start-Up Options                                                                   | 8                                     |

| Operation of Boot ROM Routines                                                     |                                       |

| Detailed Description of Boot Routines                                              | 10                                    |

| Processor Mode Boot                                                                | 10                                    |

| Starting Address Redirection (SAR) Boot                                            | 10                                    |

| EPROM Boot                                                                         | 10                                    |

| Special Note for Intel-Style Signaling Implementations (Alternate Loader Routines) | 12                                    |

| Detailed Description of Self-Test Routine                                          | 12                                    |

| Listing 1. Boot ROM Code                                                           | 13                                    |

| Pin Information                                                                    | 16                                    |

| Pin Descriptions                                                                   | 17                                    |

| Absolute Maximum Ratings                                                           | 20                                    |

| Handling Precautions                                                               | 20                                    |

| Electrical Specifications                                                          | 21                                    |

| Timing Specifications                                                              | 22                                    |

| Timing Requirements for CKI                                                        | 23                                    |

| Timing Requirements for Synchronous Bus Interface Inputs                           | 23                                    |

| Timing Characteristics for Synchronous Bus Interface Outputs                       | 24                                    |

| Timing Characteristics for Synchronous Delay/Hold Times                            | 24                                    |

| Timing Relationships for Synchronous Bus Interace Operation (55 MHz)               |                                       |

| liming Relationships for Synchronous Bus Interace Operation (66 MHz)               |                                       |

| Timing Relationships for Asynchronous Bus Interace Operation                       |                                       |

| liming Characteristics for Bus Arbitration                                         |                                       |

| Timing Requirements for Serial Inputs                                              |                                       |

| liming Requirements for Serial Outputs                                             |                                       |

| I iming Characteristics for Serial Outputs                                         |                                       |

| I Iming Requirements for Serial Clock Generation                                   | 34                                    |

| I iming Characteristics for Serial Clock Generation                                |                                       |

| I iming Requirements for Bit I/O                                                   |                                       |

| I iming Characteristics for Bit I/O                                                |                                       |

| I iming Requirements for Interrupts                                                |                                       |

| I iming Characteristics for Interrupts                                             | 36                                    |

| Uming Requirements for Reset                                                       | 27                                    |

| Liming Characteristics for Reset and ZN                                            |                                       |

| Timing Characteristics for Reset and ZN<br>Outline Diagram                         | PUMA Exhibit 2006                     |

**R M** Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

#### Introduction (continued)

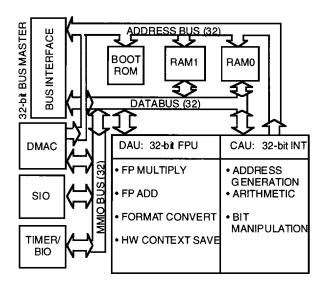

Figure 1. DSP3210 Block Diagram

The VCOS operating system includes its own multimedia library, complete with speech processing, speech recognition, graphics, music processing, and modem modules. The VCOS system is an open environment, so application developers may access third-party modules as well as AT&T's library.

Figure 1 shows the DSP3210 block diagram. In addition to a brief description of the DSP3210's application in multimedia environments, each functional unit, the instruction set, and the processor control features are described.

DOCKE

This data sheet is designed to be a companion document to the *AT&T DSP3210 Information Manual* (MN91-006OMOS). The brief descriptions of the DSP3210's architecture and instruction set are greatly expanded in the information manual. The data sheet is intended to give the latest, up-to-date, timing specifications and boot ROM firmware descriptions, while the information manual contains the detailed information needed to understand the DSP3210's operation.

# Applications

DOCKE.

The DSP3210 may be used in a variety of applications due to its raw floating-point power, low cost, low power dissipation, and interfacing flexibility. However, multimedia was the primary application considered when designing the DSP3210.

#### **PC/Workstation Multimedia Applications**

#### **DSP3210 Motherboard Implementations**

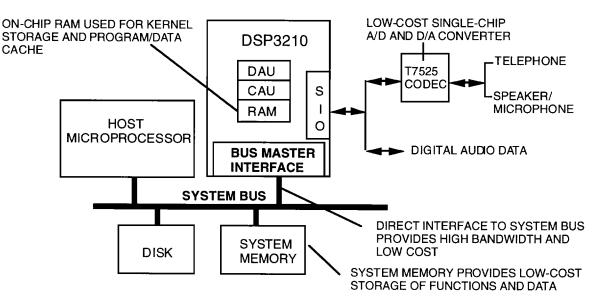

The DSP3210 is intended to be used in PC and workstation system architectures in which the DSP3210 is a parallel processor to a host processor. The DSP3210 maintains a 32-bit bus-master interface to system memory (see Figure 2).

The primary benefit of this system architecture is the DSP's ability to access program and data from system memory without host intervention. Furthermore, expensive local SRAM is replaced by the computer's existing system memory.

#### DSP3210 Add-In Cards

Existing computers with EISA, ISA, MCA, *NuBus*\*, SBus, and proprietary bus or CPU direct-slot capabilities can be easily retrofitted with low-cost DSP3210 boards to perform identical applications to motherboard-equipped PCs. In systems with direct CPU slots or 32-bit buses capable of bus mastering, these DSP3210-based cards require no DSP memory (memory is accessed via the bus or CPU direct slot).

Using the visible caching technique native to the *VCOS* operating system, boards installed in lowerbandwidth buses use inexpensive local 32-bit DRAM on the DSP3210 add-in card. In these environments, the DSP3210 uses the bus primarily to transfer tasks and I/O to and from the DSP3210 card.

\* NuBus is a registered trademark of Massachusetts Institute of Technology.

Figure 2. Typical DSP3210 PC/Workstation Motherboard Configuration

# Applications (continued)

#### System Integration Under the VCOS Operating System

Since the DSP3210 supports both big- and little-endian byte ordering, sharing both data and pointer values with any host microprocessor is easily accomplished. This is especially useful in multimedia applications where intimate communications between the host microprocessor and DSP are necessary. For real-time signal processing under the *VCOS* operating system, on-chip SRAM is loaded with code and data from system memory before executing. Applications are broken into functions that are executed successively in this fashion. Nonreal-time background jobs may be either executed from system memory or cached into the DSP3210's internal memory.

# **Functional Description**

#### **Functional Units**

The DSP3210 consists of seven functional units: control arithmetic unit (CAU), data arithmetic unit (DAU), on-chip memory (RAM0, RAM1, boot ROM), bus interface, serial I/O (SIO), DMA controller (DMAC), and timer/bit I/O (BIO) unit.

#### **Control Arithmetic Unit (CAU)**

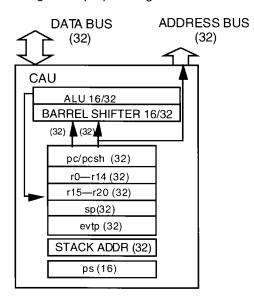

The CAU is responsible for performing address calculations, branching control, and 16- or 32-bit integer arithmetic and logic operations. It is a RISC core consisting of a 32-bit arithmetic logic unit (ALU) that performs integer arithmetic and logical operations, a full 32-bit barrel shifter for efficient bit manipulation operations, a 32-bit program counter (PC), and twenty-two 32-bit general-purpose registers.

Figure 3. Control Arithmetic Unit (CAU)

DOCK

The CAU performs two types of tasks: executing integer, data move, and control instructions (CA instructions), or generating addresses for the operands of floating-point instructions (DA instructions). CA instructions perform load/store, branching control, and 16- and 32-bit integer arithmetic and logical operations. DA instructions can have up to four memory accesses per instruction, and the CAU is responsible for generating these addresses using the postmodified, register-indirect addressing mode (one address is generated in each of the four states of an instruction cycle).

#### Data Arithmetic Unit (DAU)

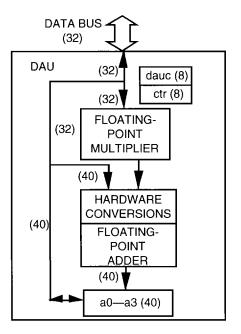

The DAU is the primary execution unit for signal processing algorithms. This unit contains a 32-bit floating-point multiplier, a 40-bit floating-point adder, four 40-bit accumulators, and a control register (dauc). The multiplier and adder work in parallel to perform 16.7 million computations per second, yielding 33 MFLOP performance. The multiplier and adder each produce one floating-point result per instruction cycle. The DAU contains a four-stage pipeline (fetch, multiply, accumulate, write). Thus, in any instruction cycle, the DAU may be processing four different instructions, each in a different stage of execution.

Figure 4. Data Arithmetic Unit (DAU)

The DAU supports two floating-point formats: single precision (32-bit) and extended single precision (40-bit). Extended single precision provides eight additional mantissa guard bits. Postnormalization logic transparently shifts binary points and adjusts exponents to prevent inaccurate rounding of bits when the floating-point numbers are added or multiplied. This eliminates concerns such as scaling and guantization error PUMA Exhibit 2006

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

# API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

#### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.