# United States Patent [19]

US006029217A

#### 6,029,217 **Patent Number:**

### Arimilli et al.

#### [54] **QUEUED ARBITRATION MECHANISM FOR** DATA PROCESSING SYSTEM

- [75] Inventors: Ravi Kumar Arimilli, Round Rock; John Michael Kaiser, Cedar Park, both of Tex.

- [73] Assignee: International Business Machines Corporation, Armonk, N.Y.

- This patent issued on a continued pros-[\*] Notice: ecution application filed under 37 CFR 1.53(d), and is subject to the twenty year patent term provisions of 35 U.S.C. 154(a)(2).

- [21] Appl. No.: 08/317,006

- Oct. 3, 1994 [22] Filed:

- Int. Cl.<sup>7</sup> ...... G06F 13/20 [51]

- U.S. Cl. ..... 710/107; 710/113; 710/116 [52]

- Field of Search ...... 395/290, 293–298, [58] 395/287, 849, 859, 865; 710/107, 110, 113-118, 29, 39, 45

#### [56] **References Cited**

#### **U.S. PATENT DOCUMENTS**

| 4,481,572 | 11/1984 | Ochsner et al 395/297   |

|-----------|---------|-------------------------|

| 4,482,949 | 11/1984 | Gates 395/860           |

| 4,953,081 | 8/1990  | Feal et al 395/291      |

| 5,006,982 | 4/1991  | Ebersole et al 395/736  |

| 5,050,066 | 9/1991  | Myers et al 395/775     |

| 5,103,393 | 4/1992  | Harris et al 395/200.56 |

| 5,202,966 | 4/1993  | Woodson 395/297         |

| 5,210,741 | 5/1993  | Grochmal 370/362        |

## [11]

#### **Date of Patent:** \*Feb. 22, 2000 [45]

| 5,276,887 | 1/1994  | Haynie 395/294          |

|-----------|---------|-------------------------|

| 5,335,335 |         | Jackson et al 395/473   |

| 5,345,578 | 9/1994  | Manasse 395/473         |

| 5,416,910 | 5/1995  | Moyer et al 395/308     |

| 5,426,765 |         | Stevens et al 395/473   |

| 5,448,701 | 9/1995  | Metz, Jr. et al 395/849 |

| 5,473,762 | 12/1995 | Krein et al 395/298     |

| 5,485,586 | 1/1996  | Brash et al 395/293     |

| 5,506,971 | 4/1996  | Gullette et al 395/473  |

| 5,506,995 | 4/1996  | Yoshimoto et al 395/287 |

| 5,557,528 | 9/1996  | Munro et al 364/478.02  |

| 5,623,628 | 4/1997  | Brayton et al 711/141   |

#### FOREIGN PATENT DOCUMENTS

| $0\ 488\ 771$ | 6/1992  | European Pat. Off G06F 13/364 |

|---------------|---------|-------------------------------|

| 0 488 771 A2  | 6/1992  | European Pat. Off G06F 13/364 |

| WO 91/20041   | 12/1991 | WIPO G06F 13/14               |

| WO91/20041    | 12/1991 | WIPO G06F 13/14               |

Primary Examiner-Glenn A. Auve

Assistant Examiner-Ario Etienne

Attorney, Agent, or Firm-Kelly K. Kordzik; Winstead Sechrest & Minick P.C.; Anthony V. S. England

#### [57] ABSTRACT

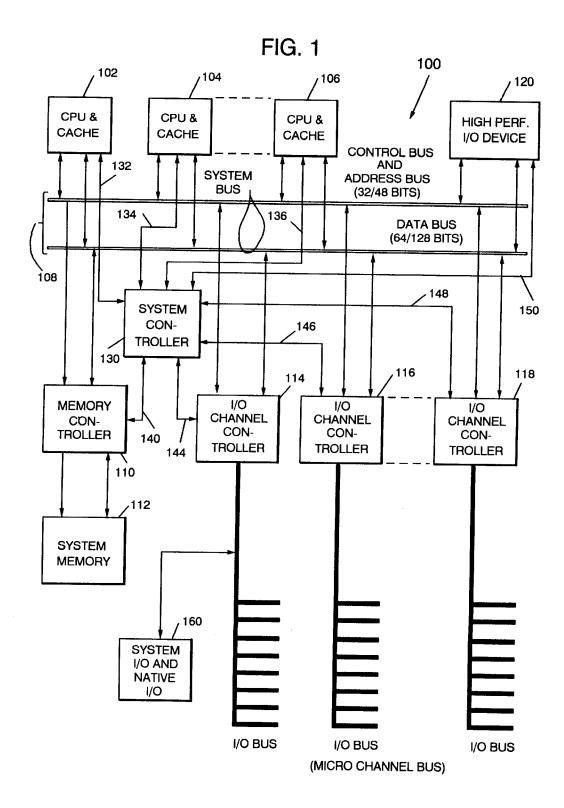

A queued arbitration mechanism transfers all queued processor bus requests to a centralized system controller/arbiter in a descriptive and pipelined manner. Transferring these descriptive and pipelined bus requests to the system controller allows the system controller to optimize the system bus utilization via prioritization of all of the requested bus operations and pipelining appropriate bus grants. Intelligent bus request information is transferred to the system controller via encoding and serialization techniques.

#### 5 Claims, 3 Drawing Sheets

Find authenticated court documents without watermarks at docketalarm.com.

Α

DOCKET A L A R M Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

1 NULL g AD ۲ ш NULL 8 O NULL ŰZ NULL ł 0 Z **B** CANCELLED NULL I ŰZ 1 ଏ ଅ υ Å I ۵ Δ NULL ŰZ ŧ g ۵ 1 1 LOW PRIORITY L AO ∢ മ ŰZ L ۵ I ł I **OPERATION GRANTED:** g 1 ł I ∢ I I 1 I NUL AD ł I ∢ ł Ű മ NULL Д С Ű ۲ OPERATION GRANTED NULL Ű BUS GRANTS BUS REQUESTS (SAME MASTER)

# DOCKET ALARM Find authenti

Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

5

40

45

#### **QUEUED ARBITRATION MECHANISM FOR** DATA PROCESSING SYSTEM

#### CROSS REFERENCE TO RELATED APPLICATIONS

This application for patent is related to the following applications for patent filed concurrently herewith:

EFFICIENT ADDRESS TRANSFER TECHNIQUE FOR A DATA PROCESSING SYSTEM, Ser. No. 08/317, 10 007:

DUAL LATENCY STATUS AND COHERENCY REPORTING FOR A MULTIPROCESSING SYSTEM, Ser. No. 08/316,980;

SYSTEM AND METHOD FOR DETERMINING 15 SOURCE OF DATA IN A SYSTEM WITH INTERVEN-ING CACHES, Ser. No. 08/317,256;

METHOD AND APPARATUS FOR REMOTE RETRY IN A DATA PROCESSING SYSTEM, Ser. No. 08/316,978;

ARRAY CLOCKING METHOD AND APPARATUS 20 FOR INPUT/OUTPUT SUBSYSTEMS, Ser. No. 08/316, 976:

DATA PROCESSING SYSTEM HAVING DEMAND BASED WRITE THROUGH CACHE WITH ENFORCED 25 ORDERING, Ser. No. 08/316,979;

COHERENCY AND SYNCHRONIZATION MECHA-NISMS FOR I/O CHANNEL CONTROLLERS IN A DATA PROCESSING SYSTEM, Ser. No. 08/316,977;

FOR HIGH PERFORMANCE DATA TRANSFER, Ser. No. 08/326,190;

LOW LATENCY ERROR REPORTING FOR HIGH PERFORMANCE BUS, Ser. No. 08/326,203.

Each of such cross-referenced applications are hereby <sup>35</sup> incorporated by reference into this Application as though fully set forth herein.

#### TECHNICAL FIELD OF THE INVENTION

The present invention relates in general to data processing systems and, in particular, to a system and method for intelligent communication of bus requests and bus grants within a data processing system.

#### BACKGROUND OF THE INVENTION

Conventional data processing systems, especially multiprocessor systems, allocate access to the shared system bus coupling the various bus devices to system memory through a mechanism whereby individual bus devices each control 50 access to the system bus. Typically, each bus device will queue it's individual bus requests for various operations internally. Then, each bus device makes the determination of which of the various operations it wishes to perform on the system bus by sending the appropriate corresponding bus 55 request to the system controller. Thus, each individual bus device determines internally which of its bus requests has higher priority. The system controller is then required to arbitrate between the received bus requests from the individual bus devices. 60

One disadvantage of this arbitration mechanism is that a portion of the decision process for accessing the various resources coupled to the system bus is delegated to each of the bus devices. As a result, the system controller is only able to view a portion of all of the various requests from the 65 individual bus devices, since each of the individual bus devices retains and queues a significant number of bus

requests. Thus, there is a need in the art for a more efficient arbitration mechanism for granting access to the system bus.

#### SUMMARY OF THE INVENTION

It is an object of the present invention to centralize the decision-making process for granting access to the system bus. In an attainment of this object, the present invention provides a mechanism of transferring all of the queued bus requests from the individual bus devices to the system controller, which has a centralized knowledge of the availability of all of the system resources coupled to the system bus.

The system controller samples the bus devices' requests on a cycle-by-cycle basis. The requests are encoded, which allows each of the bus devices to precisely communicate to the system controller each of their internally "queued" operations. Quickly transferring these "descriptive and pipelined" bus requests from each of the bus devices to a centralized control point, allows the system controller to "optimize" the system bus utilization by prioritizing all of the requested bus operations and pipelining the appropriate bus grants.

One advantage of the present invention is that it provides an ability to transfer "intelligent" bus request information from each bus device to the system controller, and provides the ability to transfer multiple packets of bus requests information (via encoding and serialization techniques).

Another advantage of the present invention is that the bus ALTERNATING DATA VALID CONTROL SIGNALS 30 requests are compact and can be issued in a pipelined manner and that bus grants may be pipelined to either the same bus device or different bus devices.

> Yet another advantage of the present invention is that it supports latch-to-latch or non-latch-to-latch implementations. Those skilled in the art will appreciate the benefit of accommodating both implementations. (Latch-to-latch implementations allow higher system bus clock rates, while non-latch-to-latch implementations provides lower system bus latencies.)

> Yet still another advantage of the present invention is that the queuing of descriptive bus requests allows the system controller to efficiently control, distribute, and allocate system bus resources.

> And, yet still another advantage of the present invention is that the system controller may resolve system level multiprocessor problems such as deadlocks and livelocks. Unlike traditional arbitration techniques, the present invention bus does not require bus devices to adhere to any arbitration "fairness" protocols.

> Another advantage of the present invention is that the bus devices may support speculative bus requests and the system controller may support speculative bus grants.

> The foregoing has outlined rather broadly the features and technical advantages of the present invention in order that the detailed description of the invention that follows may be better understood. Additional features and advantages of the invention will be described hereinafter which form the subject of the claims of the invention.

#### BRIEF DESCRIPTION OF THE DRAWING

For a more complete understanding of the present invention, and the advantages thereof, reference is now made to the following descriptions taken in conjunction with the accompanying drawings, in which:

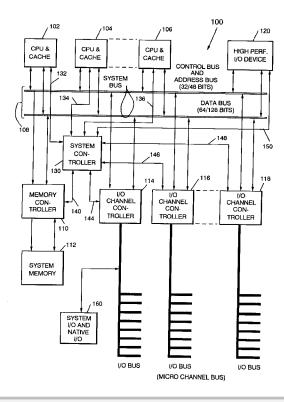

FIG. 1 illustrates a block diagram of a data processing system in accordance with the present invention;

Find authenticated court documents without watermarks at docketalarm.com.

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

# API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

## LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

## FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

## E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.