# UNITED STATES PATENT AND TRADEMARK OFFICE

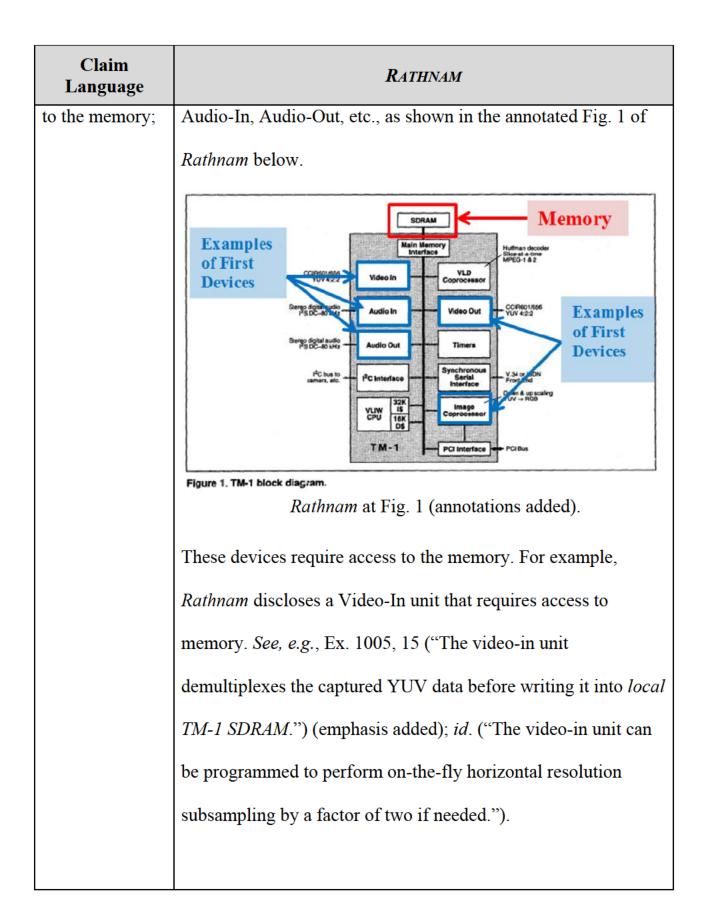

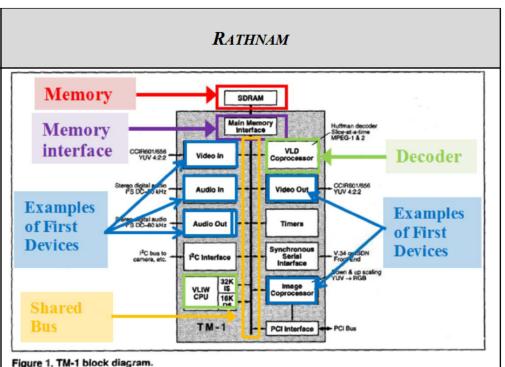

## **BEFORE THE PATENT TRIAL AND APPEAL BOARD**

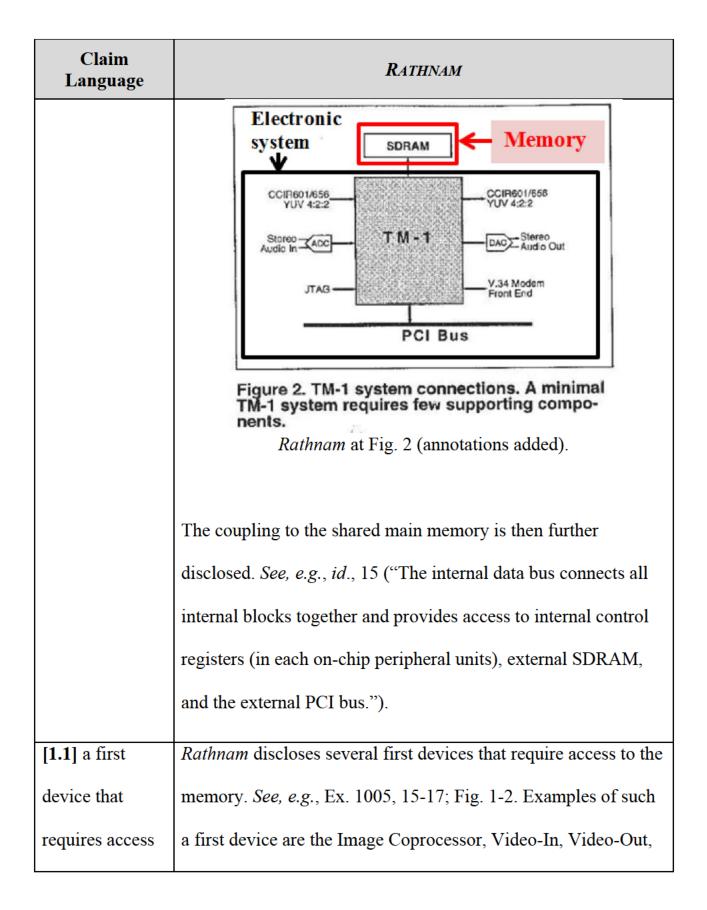

Samsung Electronics Co., Ltd., and Samsung Electronics America, Inc. Petitioners

v.

Parthenon Unified Memory Architecture LLC Patent Owner

INTER PARTES REVIEW OF U.S. PATENT NO. 5,812,789 Case IPR No.: To Be Assigned

DECLARATION OF HAROLD S. STONE, PH.D., REGARDING U.S. PATENT NO. 5,812,789

# TABLE OF CONTENTS

| I.   | INTRODUCTION1                     |                                                                     |    |  |

|------|-----------------------------------|---------------------------------------------------------------------|----|--|

|      | A.                                | Engagement                                                          | 1  |  |

|      | B.                                | Background and Qualifications                                       |    |  |

|      | C.                                | Compensation and Prior Testimony                                    | 3  |  |

|      | D.                                | Information Considered                                              |    |  |

| II.  | LEGAL STANDARDS FOR PATENTABILITY |                                                                     |    |  |

|      | A.                                | Anticipation                                                        | 7  |  |

|      | B.                                | Obviousness                                                         |    |  |

| III. | TECHNOLOGY BACKGROUND             |                                                                     |    |  |

|      | A.                                |                                                                     |    |  |

|      |                                   | 1. Tom Shanley and Don Anderson, "PCI System                        |    |  |

|      |                                   | Architecture," Third Edition, Addison-Wesley Publishing             |    |  |

|      |                                   | Company, Feb. 1995 ("Shanley") (Ex. 1019)                           | 12 |  |

|      |                                   | 2. International Organization for Standardization, "ISO/IEC         |    |  |

|      |                                   | 11172-2:1993: Information technology—Coding of                      |    |  |

|      |                                   | moving pictures and associated audio for digital storage            |    |  |

|      |                                   | media at up to about 1,5 Mbit/s—Part 2: Video," 1st ed.,            |    |  |

|      |                                   | August 1, 1993 ("MPEG Standard") (Ex. 1004)                         | 18 |  |

|      | B.                                | The Consolidation of MPEG and Other Multimedia Device's             |    |  |

|      |                                   | Memory                                                              | 22 |  |

|      |                                   | 1. Intel Corporation "Acceleration Graphics Port Interface          |    |  |

|      |                                   | Specification," Revision 1.0 ("AGP") (Ex. 1024)                     | 22 |  |

|      |                                   | 2. Video Electronics Standards Association published the            |    |  |

|      |                                   | "VESA Unified Memory Architecture Hardware                          |    |  |

|      |                                   | Specifications Proposal," Version 1.0p ("VUMA") (Ex.                |    |  |

|      |                                   | 1025)                                                               | 23 |  |

|      |                                   | 3. U.S. Patent No. 5,774,676 to Stearns ("Stearns") (Ex.            |    |  |

|      |                                   | 1007)                                                               | 24 |  |

|      |                                   | 4. U.S. Patent No. 5,797,028 to Gulick (" <i>Gulick 028</i> ") (Ex. |    |  |

|      |                                   | 1023)                                                               |    |  |

| IV.  | SUMMARY OF THE '789 PATENT        |                                                                     | 29 |  |

|      | A.                                | Effective Filing Date of the '789 Patent                            | 29 |  |

|      | B.                                | Overview of the '789 Patent                                         |    |  |

|      | C.                                | The Prosecution History of the '789 Patent                          |    |  |

|      | D.                                | Claim Construction                                                  |    |  |

| V.   |                                   | 'EL OF ORDINARY SKILL IN THE ART                                    |    |  |

| VI.  | CON                               | MPARISON OF THE PRIOR ART TO THE '789 PATENT                        | 34 |  |

| A. | Ground A: Lambrecht anticipates, under 35 U.S.C. § 102,        |    |  |  |

|----|----------------------------------------------------------------|----|--|--|

|    | claims 1, 3, 5, 11, and 13                                     | 34 |  |  |

|    | 1. Claim 1                                                     | 34 |  |  |

|    | 2. Claim 3                                                     | 51 |  |  |

|    | 3. Claim 5                                                     | 53 |  |  |

|    | 4. Claim 11                                                    | 55 |  |  |

|    | 5. Claim 13                                                    | 56 |  |  |

| В. | Ground B: Lambrecht in view of Artieri, renders obvious, under |    |  |  |

|    | 35 U.S.C. § 103, claim 4                                       | 61 |  |  |

|    | 1. Claim 4                                                     | 61 |  |  |

| C. | Ground C: Lambrecht in view of Moore, renders obvious, under   |    |  |  |

|    | 35 U.S.C. § 103, claim 6                                       | 64 |  |  |

|    | 1. Claim 6                                                     | 64 |  |  |

| D. | Ground D: Rathnam in view of Lambrecht, renders obvious,       |    |  |  |

|    | under 35 U.S.C. § 103, claims 1, 3, 4, 5, and 11               | 66 |  |  |

|    | 1. Claim 1                                                     | 66 |  |  |

|    | 2. Claim 3                                                     | 83 |  |  |

|    | 3. Claim 4                                                     | 85 |  |  |

|    | 4. Claim 5                                                     | 86 |  |  |

|    | 5. Claim 11                                                    | 89 |  |  |

| E. | Ground E: Rathnam in view of Lambrecht and Moore, renders      |    |  |  |

|    | obvious, under 35 U.S.C. § 103, claim 6                        | 91 |  |  |

|    | 1. Claim 6                                                     | 91 |  |  |

| F. | Ground F: Rathnam in view of Lambrecht and Slavenburg,         |    |  |  |

|    | renders obvious, under 35 U.S.C. § 103, claim 13               |    |  |  |

|    | 1. Claim 13                                                    | 94 |  |  |

|    |                                                                |    |  |  |

I, Harold S. Stone, Ph.D., declare as follows:

## I. INTRODUCTION

#### A. Engagement

1. I have been retained by counsel for the Petitioners to submit this declaration in connection with Petitioners' Petition for *Inter Partes* Review of claims 1, 3-6, 11 and 13 of U.S. Patent No. 5,812,789 ("'789 patent") (Ex. 1001).

## **B.** Background and Qualifications

2. I was awarded a Ph.D. and Master's Degree in Electrical Engineering from the University of California-Berkeley in 1963 and 1961, respectively. I received a Bachelor of Science degree in Electrical Engineering from Princeton University in 1960.

3. After my graduation from Berkeley in 1963, I served as a Research Engineer at Boeing and SRI International. I then held faculty positions at Stanford University and at the University of Massachusetts, where I served as a professor of computer science and electrical engineering.

4. In 1984, I started working for IBM as a Manager of Advanced Architecture Studies. In 1990, I became a Research Staff Member at IBM. During my time at IBM, I managed and conducted research in the area of memory systems and optical interconnections. I worked at IBM until 1994, when I became a Fellow at the NEC Research Institute, the highest technical position in the company. At NEC, I conducted research in image processing. I am an inventor of a patent to

1

Page 4 of 104

NEC regarding a technique for decompressing JPEG images in a novel way that permits images to be searched without fully decompressing them. The decompression technique is based on inverse discrete cosine transforms, which are one of the basic elements of MPEG decompression.

5. I have authored, coauthored, or edited 9 books in various technical areas, the most recent of which appeared in 2011. My textbooks have sold over 100,000 copies. My work on the use of the perfect shuffle interconnections for supercomputers is widely recognized, and many supercomputers based on these interconnections were developed and marketed. For this work and my textbook contributions to the field, I was elected an IEEE Fellow and ACM Fellow, and received the IEEE Piore Field Award, the IEEE Computer Society Taylor Booth Award, and the Charles Babbage Award. I am the principal inventor or co-inventor of 27 patents, including seven in the area of computer architecture - U.S. Patent Nos. 4,989,131, 5,065,310, 5,163,149, 5,611,070, 5,742,785, 5,790,823, and 6,311,260.

6. I have served as a consultant to industry while holding my academic positions and have extensive experience in computer design for embedded computers as a consequence, including low-power computers for use in satellites and ultra-reliable computers for use in nuclear submarine navigation systems. In recent years I have been a member of two Division Review Committees at Los

Alamos National Laboratory in the area of Nuclear Nonproliferation and a consultant to NASA in the area of satellite image processing.

7. My work influenced the industry to develop several different "hypercube" computers in the 1980s, all of which had interconnections based on the perfect shuffle. In the 1990s, near when the '789 patent was filed, Intel, Sun, HP, and MIPS Technologies, Inc., introduced extension instruction sets for multimedia applications, all of which incorporated perfect shuffle data movement operations. The shuffle and its inverse are common operations used by MPEG software algorithms in processors that have multimedia instructions sets.

8. In 1977, together with W. Kahan and J. Coonen, I authored the original proposal ("the KCS proposal") to the working group charged for developing a floating-point standard, which is now known as the IEEE 754 Floating Point Standard. The standard that emerged is that proposal with small changes and additions. It has been implemented in several billion processors.

9. My Curriculum Vitae is submitted herewith as Ex. 1029.

## C. Compensation and Prior Testimony

10. I am being compensated at a rate of \$500 per hour for my study and other work in this matter, plus actual expenses. My compensation is not contingent on the outcome of this matter or the specifics of my testimony.

11. I am also acting as an expert in the pending litigation between Patent Owner and Petitioners.

12. I previously prepared declarations in support of *inter partes* review petitions filed by Petitioners and other defendants in the pending litigation, which I understand are now identified as IPR2015-01494, IPR2015-01500, IPR2015-01501, IPR2015-01502, and IPR2015-01503.

13. Previously, I have testified either by deposition or at trial in the following litigation matters. The list below includes all deposition and trial testimony within the last five years:

- Parthenon Unified Memory Architecture LLC v. Samsung Electronics Co., Ltd. et al. (U.S. District Court, Eastern District of Texas), Case No. 2:14-cv-00902-JRG-RSP;

- Advanced Internet Technologies, Inc. v. Dell, Inc. (U.S. District Court, Eastern District of North Carolina), Case No. 5:07-cv-00426-H;

- Microunity Systems Engineering Inc v. Acer Inc et al. (U.S. District Court, Eastern District of Texas), Case No. 2:10-cv-00091-LED-RSP;

- Technology Service Corporation v. Mountcastle et al. (U.S. District Court, Eastern District of Virginia – Alexandria), Case No. 1:10-cv-00901-TSE-TCB;

- BIAX Corporation v. Motorola Solutions, Inc. et al. (U.S. District Court, District of Colorado – Denver), Case No. 1:10-cv-03013-PAB-KLM;

- Certain Computing Devices with Associated Instructions Sets and Software (International Trade Commission), Inv. 337-TA-812;

- Stragent, LLC et al. v. Intel Corporation (U.S. District Court, Eastern District of Texas – Tyler), Case No. 6:11-cv-00421-TBD-JDL; and

- Convolve Inc. et al. v. Compaq Computer Corporation et al., (U.S. District Court, Southern District of New York Foley Square), Case No. 1:00-cv-05141-GBD-JCF.

## **D.** Information Considered

14. My opinions are based on my years of education, research, and experience, as well as my investigation and study of relevant materials. In forming my opinions, I have considered the materials I identify in this declaration and those listed in Appendix A. 15. I may rely upon these materials and/or additional materials to respond to arguments raised by the Patent Owner. I may also consider additional documents and information in forming any necessary opinions — including documents that may not yet have been provided to me.

16. My analysis of the materials produced in this investigation is ongoing and I will continue to review any new material as it is provided. This declaration represents only those opinions I have formed to date. I reserve the right to revise, supplement, and/or amend my opinions stated herein based on new information and on my continuing analysis of the materials already provided.

## II. LEGAL STANDARDS FOR PATENTABILITY

17. In expressing my opinions and considering the subject matter of the claims of the '789 patent, I am relying upon certain basic legal principles that have been explained to me.

18. First, I understand that for an invention claimed in a patent to be found patentable, it must be, among other things, new and not obvious from what was known before the invention was made.

19. I understand the information that is used to evaluate whether an invention is new and not obvious is generally referred to as "prior art" and generally includes patents and printed publications (e.g., books, journal publications, articles on websites, product manuals, etc.).

20. I understand that the prior art includes patents and printed publications that existed before the earliest filing date (the "effective filing date") of the claim in the patent. I also understand that a patent will be prior art if it was filed before the effective filing date of the claimed invention, while a printed publication will be prior art if it was publicly available before that date.

21. I understand that there are two ways in which prior art may render a patent claim unpatentable. First, the prior art can be shown to "anticipate" the claim. Second, the prior art can be shown to have made the claim "obvious" to a person having ordinary skill in the art. My understanding of the two legal standards is set forth below.

### A. Anticipation

22. I understand that the following standards govern the determination of whether a patent claim is "anticipated" by the prior art.

23. I have applied these standards in my evaluation of whether the claims of the '789 patent would have been anticipated by the prior art.

24. I understand that, for a patent claim to be "anticipated" by the prior art, each and every requirement of the claim must be found, expressly or inherently, in a single prior art reference as recited in the claim. I understand that claim limitations that are not expressly described in a prior art reference may still be there if they are "inherent" to the thing or process being described in the prior

art. For example, an indication in a prior art reference that a particular process complies with a published standard would indicate that the process must inherently perform certain steps or use certain data structures that are necessary to comply with the published standard.

25. I understand that if a reference incorporates other documents by reference, the incorporating reference and the incorporated reference(s) should be treated as a single prior art reference for purposes of analyzing anticipation.

26. I understand that it is acceptable to consider evidence other than the information in a particular prior art document to determine if a feature is necessarily present in or inherently described by that reference.

#### **B.** Obviousness

27. I understand that a claimed invention is not patentable if it would have been obvious to a person having ordinary skill in the field of the invention at the time the invention was made.

28. I understand that the obviousness standard is defined in the patent statute (35 U.S.C. § 103(a)) as follows:

A patent may not be obtained though the invention is not identically disclosed or described as set forth in section 102 of this title, if the differences between the subject matter sought to be patented and the prior art are such

that the subject matter as a whole would have been obvious at the time the invention was made to a person having ordinary skill in the art to which said subject matter pertains. Patentability shall not be negatived by the manner in which the invention was made.

29. I understand that the following standards govern the determination of whether a claim in a patent is obvious. I have applied these standards in my evaluation of whether the asserted claims of the '789 patent would have been considered obvious as of the effective filing date of the claims in the '789 patent.

30. When considering the issue of obviousness, I understand that I am to do the following: (i) determine the scope and content of the prior art; (ii) ascertain the differences between the prior art and the claims at issue; (iii) resolve the level of ordinary skill in the art; and (iv) consider objective evidence of non-obviousness (also known as "secondary considerations" of non-obviousness). Examples of evidence of secondary considerations of non-obviousness include evidence of commercial success, long-felt but unsolved needs, failure of others, and unexpected results. I am not presently aware of any evidence of "objective factors" suggesting any of the challenged claims of the '789 patent are not obvious, and reserve my right to address any such evidence if it is identified in the future.

31. I understand that a person having ordinary skill is also a person of ordinary creativity.

32. My understanding is that not all innovations are patentable. Even if a claimed product or method is not disclosed in its entirety in a single prior art reference, the patent claim is invalid if the invention would have been obvious to a person having ordinary skill in the art at the time of the invention. In particular, I understand that a patent claim is normally invalid as obvious if it would have been a matter of "ordinary innovation" within the relevant field to create the claimed product or method at the time of the invention.

33. I also understand that the following exemplary scenarios would support a conclusion that a claimed product or method would have been obvious:

- Combining prior art elements according to known methods to yield predictable results;

- Simple substitution of one known element for another to obtain predictable results;

- Use of known technique to improve similar devices (methods, or products) in the same way;

- Applying a known technique to a known device (method, or product) ready for improvement to yield predictable results;

- "Obvious to try" choosing from a finite number of identified, predictable solutions, with a reasonable expectation of success;

- Known work in one field of endeavor may prompt variations of it for use in either the same field or a different one based on design incentives or other market forces if the variations are predictable to one of ordinary skill in the art;

- Some teaching, suggestion, or motivation in the prior art that would have led one of ordinary skill to modify the prior art reference or to combine prior art reference teachings to arrive at the claimed invention.

34. I understand that sometimes it will be necessary to look to interrelated teachings of multiple patents; the effects of demands known to the design community or present in the marketplace; and the background knowledge possessed by a person having ordinary skill in the art. I understand that all these issues may be considered to determine whether there was an apparent reason to combine the known elements in the fashion claimed by the patent at issue.

35. I understand that an invention that might be considered an obvious variation or modification of the prior art may be considered non-obvious if one or more prior art references discourages or lead away from the line of inquiry disclosed in the reference(s). A reference does not "teach away" from an invention

simply because the reference suggests that another embodiment of the invention is better or preferred. My understanding of the doctrine of teaching away requires a clear indication that the combination should not be attempted (e.g., because it would not work or explicit statements saying the combination should not be made).

## III. TECHNOLOGY BACKGROUND

## A. Basics of Computer Architecture & Video Encoding/Decoding

# 1. Tom Shanley and Don Anderson, "PCI System Architecture," Third Edition, Addison-Wesley Publishing Company, Feb. 1995 ("Shanley") (Ex. 1019)

36. Tom Shanley and Don Anderson, "PCI System Architecture," Third Edition, Addison-Wesley Publishing Company, Feb. 1995 ("*Shanley*") describes PC architectures having a PCI bus. At the time of the alleged invention, the PCI bus, as defined in the PCI Special Interest Group's PCI Local Bus Specification Revision 2.1, was a high performance industry standard bus. *See, e.g.*, Ex. 1019, 58-60.

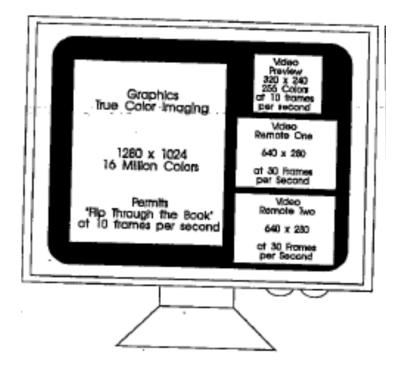

37. *Shanley* Figures 1-2 and 1-3 depict the application of a three-way realtime video teleconference with four video streams (one local video preview stream, two remote video streams, and a larger graphical stream).

Ex. 1019, 42.

Figure 1-3. The Teleconference Screen Layout

Ex. 1019, 43.

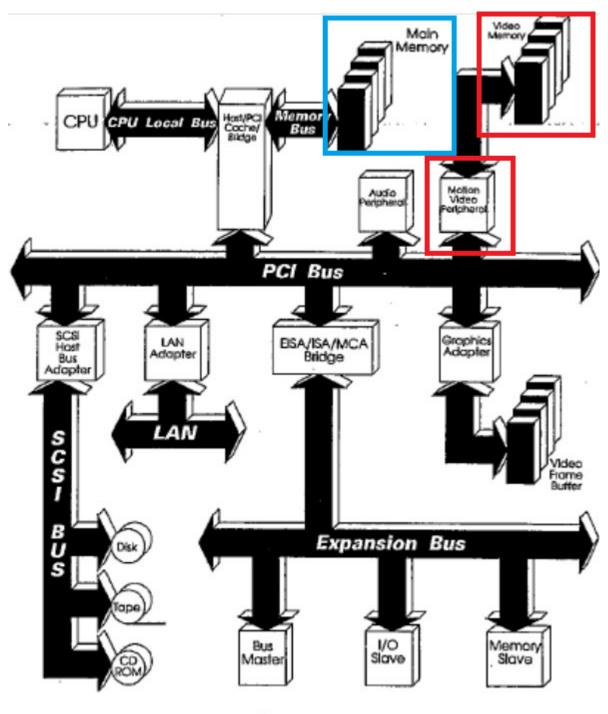

38. The PCI bus enabled such applications. An example of a PC employing the PCI bus is shown below in Figure 2-4.

Figure 2-4. The PCI Bus

Ex. 1019, 57 (Figure 2-4, annotated).

39. As shown in Figure 2-4, the system includes a PCI bus that links a motion video peripheral, audio peripheral, graphics adapter, and other devices. The

motion video peripheral (red) has its own video memory (also red) that is separate from the main memory (blue).

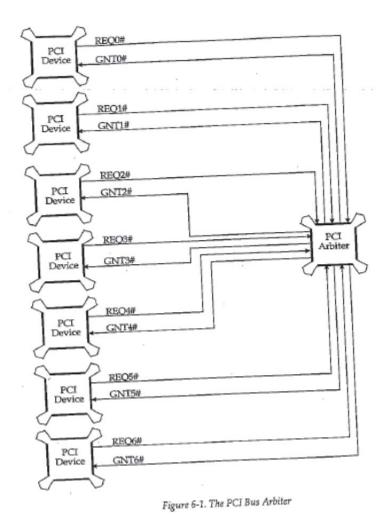

40. Arbitration for access to main memory is largely left up to the designer. Ex. 1019, 92-127. In the PCI specification, each potential bus master's interface has a set of lines to handle arbitration, REQ# and GNT#. Ex. 1019, 69. The REQ# and GNT# are separately routed from each potential bus master to the arbitration mechanism:

Ex. 1019, 93 (Figure 6-1).

41. The arbiter may be a separate component or may be integrated into another device, such as the PCI chip set. *See* Ex. 1019, 92 ("Although the arbiter is shown as a separate component, it usually is integrated into the PCI chip set; specifically, it is typically integrated into the host/PCI or the PCI/expansion bus bridge chip.")

42. *Shanley* describes one particular implementation of a system using the VLSI VL82C59x SuperCore PCI chipset. Ex. 1019, 187-220.

43. In the VL82C59x chipset, the VL82C591 Pentium System Controller in combination with the two VL82C592 Pentium Processor Data Buffers incorporate the "PCI and host bus arbiters" for memory accesses by the peripherals or CPU/processor. Ex. 1019, 189-190.

44. Arbitration must be present in any system that shares access to a resource (e.g., a memory) via a bus to prevent conflicts (i.e., two devices attempting to access a memory over a bus at the same time). Ex. 1020, 4-6. I described this in my book, "Microcomputer Interfacing," first published in 1982 by Addison-Wesley Publishing Company (Ex. 1020): "the role of the arbitration lines is then very clearly defined. They guarantee that, at most, one module at a time transmits on the bus." Ex. 1020, 6.

Page 20 of 104

2. International Organization for Standardization, "ISO/IEC 11172-2:1993: Information technology—Coding of moving pictures and associated audio for digital storage media at up to about 1,5 Mbit/s—Part 2: Video," 1st ed., August 1, 1993 ("*MPEG Standard*") (Ex. 1004)

45. I understand that the International Organization for Standardization,

"ISO/IEC 11172-2:1993: Information technology-Coding of moving pictures and

associated audio for digital storage media at up to about 1,5 Mbit/s—Part 2:

Video," 1st ed., August 1, 1993 ("MPEG Standard") describes a video

compression standard using two forms of compression: spatial and temporal. Like

JPEG, spatial compression in MPEG involves compressing a single image based

on blocks of pixels within the image in which the pixels have similar

characteristics. Because MPEG deals with video, MPEG further includes temporal

compression to compress an image based on similarities to other frames in the

video sequence. As described by MPEG Standard:

A number of techniques are used to achieve a high compression ratio. The first, which is almost independent from this part of ISO/IEC 11172, is to select an appropriate spatial resolution for the signal. The algorithm then uses block-based motion compensation to reduce the temporal redundancy. Motion compensation is used for causal prediction of the current picture from a previous picture, for non-causal prediction of the current picture from a previous picture. The difference signal, the prediction error, is further compressed using the discrete cosine transform (DCT) to remove spatial correlation before it is quantized in an irreversible process that discards the less important information. Finally, the motion vectors are combined with the DCT information, and coded using variable length codes.

Ex. 1004, 5 (§ 0.2 Overview of the algorithm).

46. The 16-pel by 16-line (16x16 pixel region) referenced above referred to as a macroblock and may vary in data size depending on the color format. Ex. 1004, 17 (2.1.86 macroblock [video]).

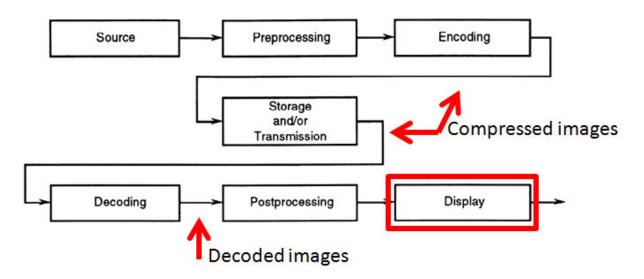

47. The compression disclosed in *MPEG Standard* is useful for storage and/or transmission. Videos can be encoded to reduce bandwidth or memory requirements during storage or transmission and subsequently decoded for display.

Ex. 1004, 62 (Figure D.1, annotated).

## 48. To permit predictive and non-causal interpolative temporal

processing, MPEG Standard defines three picture types:

Because of the conflicting requirements of random access and highly efficient compression, three main picture types are defined. Intra-coded pictures (I-Pictures) are coded without reference to other pictures. They provide access points to the coded sequence where decoding can begin, but are coded with only a moderate compression ratio. Predictive coded pictures (P-Pictures) are coded more efficiently using motion compensated prediction from a past intra or predictive coded pictures (B-Pictures) provide the highest degree of compression but require both past and future reference pictures for motion compensation. Bidirectionally-predictive coded pictures are never used as references for prediction. The organisation of the three picture types in a sequence is very flexible. The choice is left to the encoder and will depend on the requirements of the application. Figure 1 illustrates the relationship between the three different picture types.

Ex. 1004, 5 (§ 0.2.1 Temporal processing).

49. As stated above, I-pictures are coded without reference to other pictures, P-pictures are coded with reference to past pictures, and B-pictures are coded with reference to past and future pictures and are never used as references for prediction.

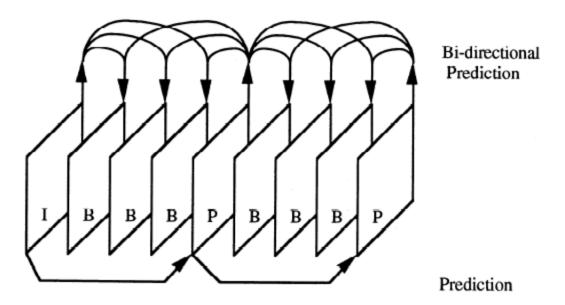

50. The following figure illustrates the relationship between the three picture types:

Figure 1 -- Example of temporal picture structure

Ex. 1004, 5 (Figure 1).

51. Note that in decoding, if a B-picture was encoded with reference to a previous P-picture and a subsequent P-picture (in sequence), the two P-pictures are decoded in time (but not displayed in time) prior to the decoding of the B-picture:

At the encoder output, in the stored bitstream, and at the decoder input, 6 10 8 B I B 9 B 13 11 12 16 14 15 19 17 18 22 20 21 25 23 24 P B B P B B I B B P B B P B B P 1 4 I P 7 5 В Р в В At the decoder output, 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 3 4 5 6 7 8 9 1 2

Ex. 1004, 24-25.

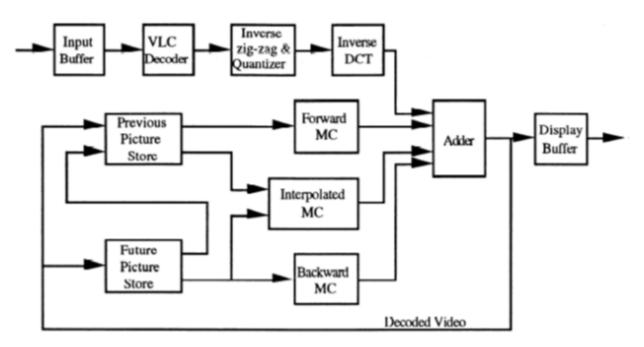

52. *MPEG Standard* depicts a simplified decoder implementation:

Figure D.7 -- Simplified decoder block diagram

Ex. 1004, 66 (Figure D.7).

53. As shown above, the decoder receives an encoded or compressed bitstream from a source (e.g., a memory). The VLC decoder, inverse zig-zag and quantizer, and inverse DCT blocks decode the bitstream, and then the various motion compensation blocks act (for the various picture types). Two frame stores are present, one for past and one for future frames to facilitate decoding of Bpictures. Once a frame is no longer needed, it may be output to a display buffer for display. Note that the MPEG Standard does not restrict the location of the picture stores. In the absence of such a constraint conforming implementations could use shared memory or a combination of shared and dedicated memory.

# B. The Consolidation of MPEG and Other Multimedia Device's Memory

54. One widely recognized goal in computing was reducing cost. As detailed below, one well known technique to reduce cost was to eliminate dedicated memory associated with an MPEG or other media device.

## 1. Intel Corporation "Acceleration Graphics Port Interface Specification," Revision 1.0 ("*AGP*") (Ex. 1024)

55. The stated purpose of Intel Corporation "Acceleration Graphics Port Interface Specification," Revision 1.0 ("*AGP*") was to control costs by sharing memory:

> In general, 3D rendering has a voracious appetite for memory bandwidth, and continues to put upward pressure on memory footprint as well. As 3D hardware and software become more pervasive, these two trends are likely to accelerate, requiring high speed access to ever larger amounts of memory, thus raising the bill of

material costs for 3D enabled platforms. Containing these costs while enabling performance improvements is the primary motivation for the A.G.P.. *By providing up to an order of magnitude bandwidth improvement between the graphics accelerator and system memory, some of the 3D rendering data structures may be effectively shifted into main memory, relieving the pressure to increase the cost of the local graphics memory.*

Ex. 1024, 11 (Motivation) (emphasis added).

## 2. Video Electronics Standards Association published the "VESA Unified Memory Architecture Hardware Specifications Proposal," Version 1.0p ("VUMA") (Ex. 1025)

56. Video Electronics Standards Association published the "VESA Unified Memory Architecture Hardware Specifications Proposal," Version 1.0p ("*VUMA*") stated purpose was to eliminate the need for a component to incorporate a dedicated memory by instead using a shared system memory to serve as the component's memory:

The concept of VESA Unified Memory Architecture

(VUMA) is to share physical system memory (DRAM)

between system and an external device, a VUMA device;

as shown in Figure 1-1. A VUMA device could be any

type of controller which needs to share physical system memory (DRAM) with system and directly access it. One example of a VUMA device is graphics controller. In a VUMA system, graphics controller will incorporate graphics frame buffer in physical system memory (DRAM) or in other words VUMA device will use a part of physical system memory as its frame buffer, thus, sharing it with system and directly accessing it. *This will eliminate the need for separate graphics memory, resulting in cost savings.*

Ex. 1025, 6 (Introduction) (emphasis added).

3. U.S. Patent No. 5,774,676 to Stearns ("Stearns") (Ex. 1007)

57. *Stearns* issued June 30, 1998 based on an application filed on October 3, 1995. *See* Ex. 1007.

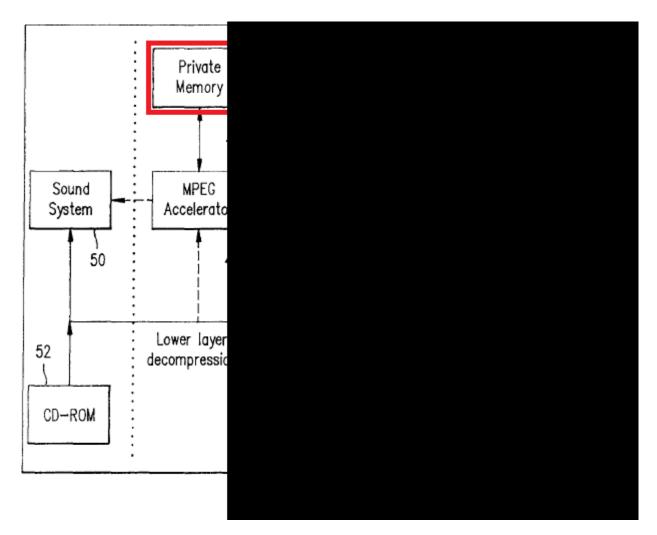

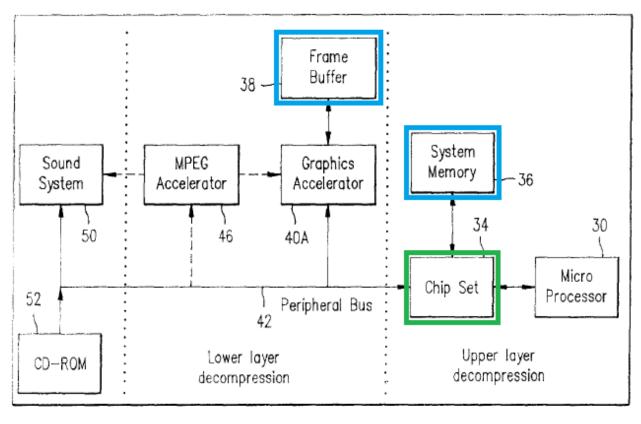

58. *Stearns* described the MPEG accelerator circuit in Figure 2 below as

"a dedicated digital signal processor for video decompression." *See* Ex. 1007,

6:56-57.

59. In contrasting Figures 2 and 3, below, *Stearns* discloses eliminating MPEG accelerator 46's private memory 44 (red) and satisfying the memory

requirements by sharing either frame buffer 38 or system memory 36 (blue). See

Ex. 1007, 5:63-6:7.

Ex. 1007, Figure 2 (annotated).

FIG. 3

## Ex. 1007, Figure 3 (annotated).

60. *Stearns* describes the core logic chip set (above, green) as follows: "The core logic chip set of a computer interfaces the microprocessor to the peripherals, manages the memory subsystem, arbitrates usage and maintains coherency." Ex. 1007, 3:53-55.

# 4. U.S. Patent No. 5,797,028 to Gulick ("Gulick 028") (Ex. 1023)

61. *Gulick 028* issued based on an application filed on September 11,1995. *See* Ex. 1023.

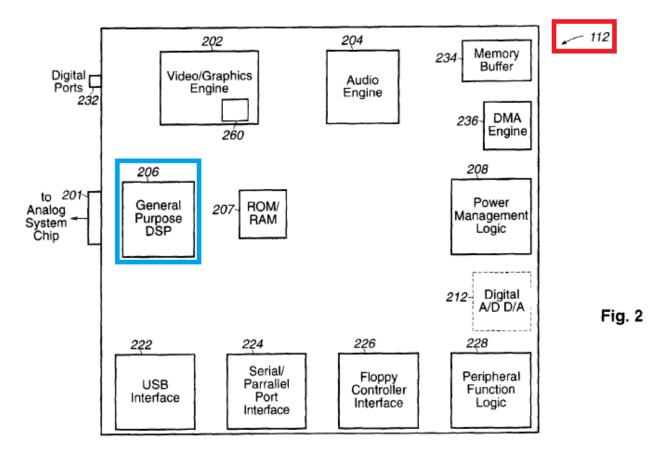

62. *Gulick 028* Figure 2, below, depicts a digital system chip 112 (red) having a general purpose DSP 206 (blue).

Ex. 1023, Figure 2 (annotated).

63. *Gulick 028* explains that "[t]he digital system chip 112 also preferably includes a general purpose DSP engine 206 which is programmable to perform various functions, such as MPEG decoding . . . ." Ex. 1023, 6:20-24.

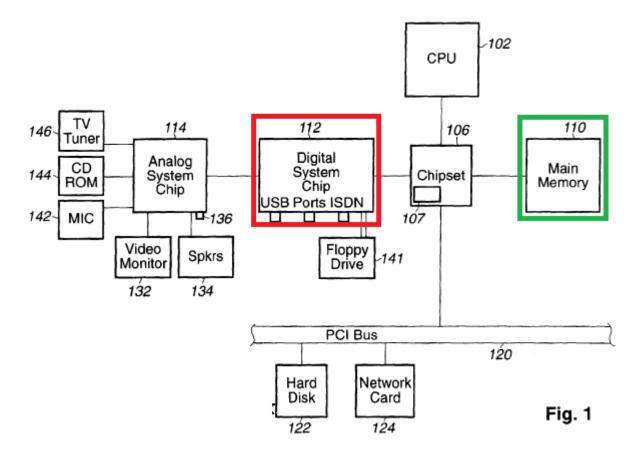

64. *Gulick 028* Figure 1, below, places the digital system chip 112 (red) in context in the larger system.

Ex. 1023, Figure 1 (annotated).

65. *Gulick 028* discloses:

In one embodiment, the digital system chip 112 does not include multimedia memory, but rather video data and audio data are stored in the system memory 110 according to a unified memory architecture. In this embodiment, the digital system chip 112 preferably includes a memory buffer 234 and a direct memory access (DMA) engine 236 for transferring data from the main memory 110 to the memory buffer 234 in the

digital system chip 112.

Ex. 1023, 6:48-55.

66. That is, *Gulick 028's* MPEG decoder operates out of main or system memory 110 depicted above in Figure 1 (green).

#### IV. SUMMARY OF THE '789 PATENT

#### A. Effective Filing Date of the '789 patent

67. The '789 patent issued from U.S. Application No. 702,911 filed August 26, 1996. Ex. 1001 at Face. I therefore understand that the effective filing date of the claims of the '789 patent is no earlier than August 26, 1996.

## **B.** Overview of the '789 patent

68. I have reviewed the '789 patent to identify its novel aspects as one skilled in the art would view them. My high-level summary is that the alleged novelty is how to use shared memory within a video system to reduce cost without compromising the ability to meet video processing performance requirements. For example, under the "Summary of the Invention," the '789 patent specification states:

Both the first device and the video and/or audio decompression and/or compression device require access to a memory. The video and/or audio decompression and/or compression device *shares the memory with the first device*.

Ex. 1001, 3:65-4:2 (emphasis added).

69. The '789 patent concerns the arbitration for access to a memory shared between a video decoder and another device, such as a central processing unit (CPU). The inventors conceded that video coding and decoding techniques such as MPEG, H.261, and H.263 were "well accepted standards" at the time. But, the inventors alleged, a video decoder conventionally would be given its own dedicated memory, to allow it to operate in "real time."<sup>1</sup> The dedicated memory would remain unused most of the time and significantly increase costs. To address these alleged problems, the inventors proposed having the video decoder share memory with other devices. The '789 patent accomplishes this using an arbiter, which arbitrates between the video decoder and the device when either one requests access to the memory.

## C. The Prosecution History of the '789 patent

70. The original application for the '789 patent contained 49 claims.These claims were rejected as being anticipated by Lin et al., On the BusArbitration for MPEG 2 Video Decoder, and obvious in view of U.S. Patent No.

<sup>&</sup>lt;sup>1</sup> The '789 patent never defines "real time."

5,557,538 (Retter et al.) and U.S. Patent No. 5,522,080 (Harney). Ex. 1002, 93, 94. In response, most notably with respect to the claims challenged here, the Applicant amended what later issued as claims 1 and 13. *Id.*, 105-108. For example, independent claim 1 was amended to additionally recite "and a shared bus coupled to the memory, the first device, and the decoder, the bus having a sufficient bandwidth to enable the decoder to access the memory and operate in real time when the first device simultaneously accesses the bus." *Id.* This claim and its dependent claims were subsequently allowed.

## **D.** Claim Construction

71. I understand that a claim subject to *inter partes* review receives the broadest reasonable interpretation in light of the specification and file history of the patent in which it appears. I also understand that any term that is not construed should be given its plain and ordinary meaning under the broadest reasonable interpretation. I have followed these principles in my analysis. I discuss certain claim terms below and what I understand to be Petitioners' construction of these terms, which I apply in my analysis. The remaining claim terms in the '789 patent are given their plain and ordinary meaning under the broadest reasonable interpretation, which I also apply in my analysis.

72. I understand that Petitioners have proposed that the broadest reasonable interpretation of the claimed term "video decoder" is "hardware and/or

software that translates data streams into video information." I agree with this construction based on the claims and specification of the '789 patent. For example, the '789 patent generally refers to a decoder as a "video and/or audio decompression device." Ex. 1001, 1:46-51. According to the specification, "[a]ny conventional decoder including a decoder complying to the MPEG-1, MPEG-2, H.261, or H.261 standards, or any combination of them, or any other conventional standard can be used as the decoder/encoder." Id., 12:23-27 (emphasis added). A conventional decoder around the time of the alleged invention of the '789 patent was understood to include "any hardware or software system that translates data streams into video or audio information." Ex. 1014 at 3. Consistent with this understanding of a decoder, the '789 patent acknowledges that a decoder can be implemented as hardware or software. See, e.g., Ex. 1001, 5:43-45. In one example, the specification explains that video decoding can be performed by hardware and audio decoding can be performed by software. Id., 5:50-56.

73. I have been asked to assume that the broadest reasonable interpretation of the claimed term "real time" is "fast enough to keep up with an input data stream." I have applied this understanding in my analysis.

Page 35 of 104

## V. LEVEL OF ORDINARY SKILL IN THE ART

74. I understand that the claims of a patent are reviewed from the point of view of a hypothetical person having ordinary skill in the art as of the effective filing date of the '789 patent.

75. Based on my review of the '789 patent specification, claims, and file history, in my opinion, a person having ordinary skill in the art as of the effective filing date of the '789 patent would have held an accredited Bachelor's degree in Electrical Engineering and/or Computer Science and/or Computer Engineering and had three years' experience in the fields of data compression and overall computer system architecture.

76. The reason that I have chosen that definition of a person having ordinary skill in the art for the '789 patent is because that person would have been exposed to compression techniques described in the '789 patent. That person would also be familiar with the basic computer components recited in the claims and would understand how to use those components to build a multimedia processing system using shared resources like a memory.

77. As described in more detail above, I was a person with at least ordinary skill in the art as of the effective filing date of the '789 patent.

Page 36 of 104

#### VI. COMPARISON OF THE PRIOR ART TO THE '789 PATENT

# A. Ground A: *Lambrecht* anticipates, under 35 U.S.C. § 102, claims 1, 3, 5, 11, and 13

#### 1. Claim 1

78. In my opinion, *Lambrecht* discloses every feature of claim 1.

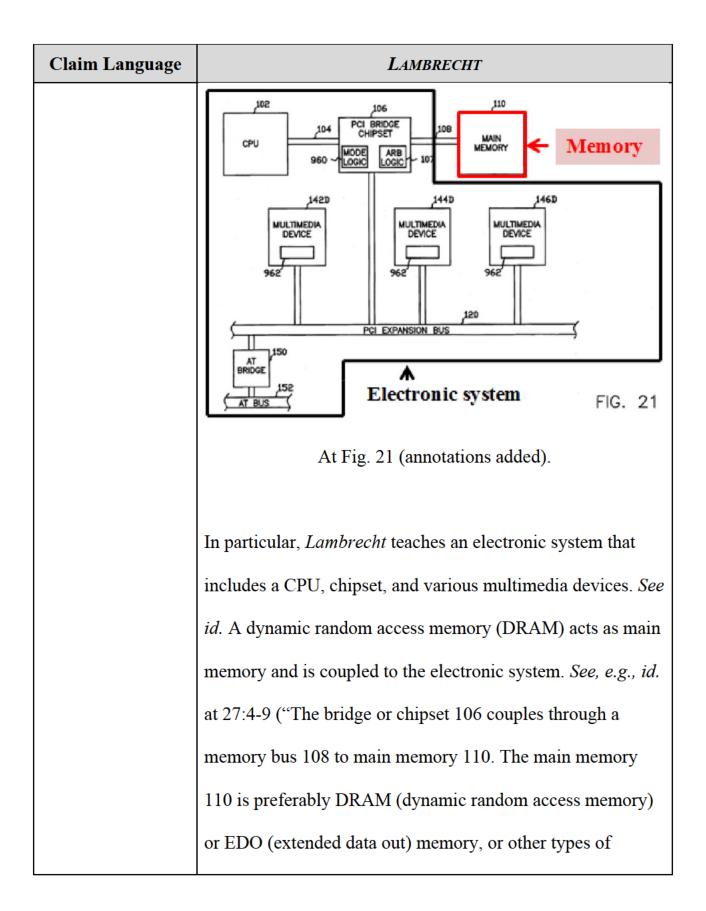

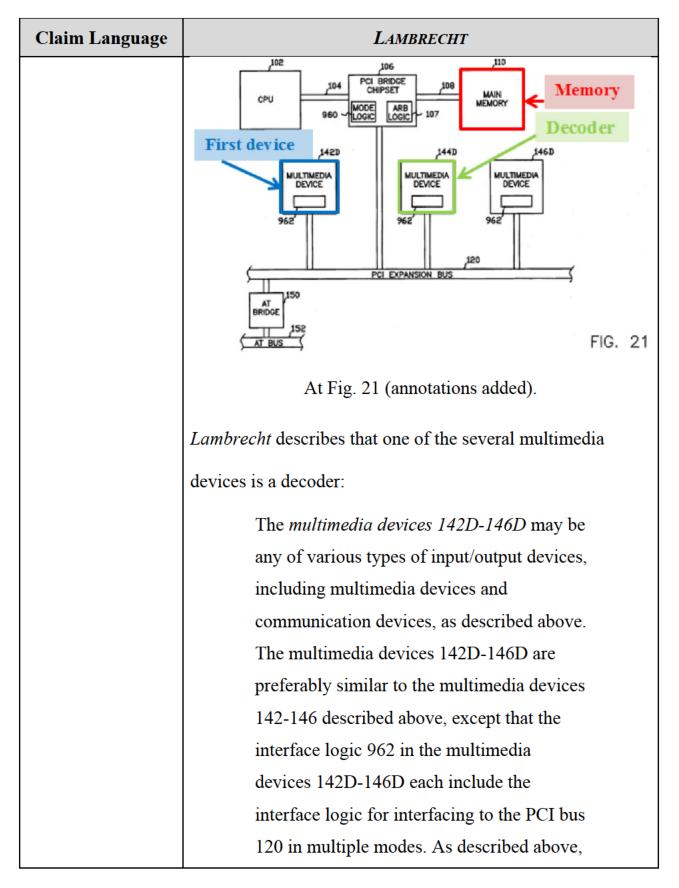

| Claim Language      | Lambrecht                                                    |

|---------------------|--------------------------------------------------------------|

| [1.0] An electronic | Lambrecht discloses an electronic system coupled to a        |

| system coupled to a | memory. See, e.g., Ex. 1032, Lambrecht at Fig. 21 (annotated |

| memory,             | below); see also id. at 27:4-9, 26:51-56 ("The computer      |

| comprising:         | system of FIG. 21 is similar to the computer system of FIG.  |

|                     | 1. However, the mode logic in the computer system of FIG.    |

|                     | 21 is operable to place the PCI bus 120 in either a normal   |

|                     | PCI mode or in a real-time/multimedia mode optimized for     |

|                     | multimedia transfers of periodic data.").                    |

| Claim Language       | LAMBRECHT                                                       |

|----------------------|-----------------------------------------------------------------|

|                      | memory, as desired. The chipset logic 106 preferably            |

|                      | includes a memory controller for interfacing to the main        |

|                      | memory 110."), Fig. 21; see also analysis and citations below   |

|                      | for other claim elements.                                       |

| [1.1] a first device | Lambrecht discloses a first device (light blue) that requires   |

| that requires access | access to the memory (red). See, e.g., Ex. 1032 at Fig. 21;     |

| to the memory;       | 27:4-9.                                                         |

|                      |                                                                 |

|                      | In particular, Lambrecht discloses a first device that requires |

|                      | access to the memory. See, e.g., Ex. 1032, Fig. 21 (annotated   |

|                      | below), 27:32-34 ("One or more multimedia devices or            |

|                      | multimedia devices 142D, 144D, and 146D are coupled to          |

|                      | each of the PCI bus 120 and the multimedia bus 130.")           |

|                      | (emphasis added).                                               |

| Claim Language       | LAMBRECHT                                                         |

|----------------------|-------------------------------------------------------------------|

|                      | comprise video accelerator or graphics                            |

|                      | accelerator cards, video playback cards,                          |

|                      | MPEG decoder cards, sound cards, network                          |

|                      | interface cards, SCSI adapters for                                |

|                      | interfacing to various input/output devices,                      |

|                      | such as CD-ROMS and tape drives, or other                         |

|                      | devices as desired.                                               |

|                      | See id. at 27:43-56 (emphasis added).                             |

|                      |                                                                   |

|                      | The first desire disclosed in Low has determined as to            |

|                      | The first device disclosed in <i>Lambrecht</i> requires access to |

|                      | memory. See id.at 27:57-59 ("Thus, the multimedia devices         |

|                      | 142D-146D communicate with each other and with the CPU            |

|                      | 102 and main memory 110 via the PCI bus 12 as is well             |

|                      | known in the art.").                                              |

| [1.2] a decoder that | Lambrecht discloses a decoder that requires access to the         |

| requires access to   | memory sufficient to maintain real time operation. See, e.g.,     |

| the memory           | Ex. 1032 at Fig. 21 (annotated below), 27:32-34 ("One or          |

| sufficient to        | more multimedia devices or multimedia devices 142D, 144D,         |

| maintain real time   | and 146D are coupled to each of the PCI bus 120 and the           |

| operation; and       | multimedia bus 130.") (emphasis added).                           |

| Claim Language | LAMBRECHT                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | the multimedia devices 142D-146D may                                                                                                                                                                                                                                                                                                                                                                                   |

|                | comprise video accelerator or graphics                                                                                                                                                                                                                                                                                                                                                                                 |

|                | accelerator cards, video playback cards,                                                                                                                                                                                                                                                                                                                                                                               |

|                | MPEG decoder cards, sound cards, network                                                                                                                                                                                                                                                                                                                                                                               |

|                | interface cards, SCSI adapters for                                                                                                                                                                                                                                                                                                                                                                                     |

|                | interfacing to various input/output devices,                                                                                                                                                                                                                                                                                                                                                                           |

|                | such as CD-ROMS and tape drives, or other                                                                                                                                                                                                                                                                                                                                                                              |

|                | devices as desired.                                                                                                                                                                                                                                                                                                                                                                                                    |

|                | See id. at 27:43-56 (emphasis added). In other words,                                                                                                                                                                                                                                                                                                                                                                  |

|                | Lambrecht discloses an arrangement in which multimedia                                                                                                                                                                                                                                                                                                                                                                 |

|                | device 144D is a decoder (i.e., an MPEG decoder card).                                                                                                                                                                                                                                                                                                                                                                 |

|                | The decoder disclosed in <i>Lambrecht</i> requires access to<br>memory. <i>See id.</i> at 27:57-59 ("Thus, the multimedia devices<br>142D-146D communicate with each other and with the CPU<br>102 and main memory 110 via the PCI bus 120, as is well<br>known in the art.").<br>The memory access is sufficient to operate in real time. <i>See</i><br><i>id.</i> at 27:66-28:2 ("In the preferred embodiment of the |

|                | invention of FIG. 21, the multimedia mode comprises                                                                                                                                                                                                                                                                                                                                                                    |

| Claim Language | LAMBRECHT                                                   |

|----------------|-------------------------------------------------------------|

|                | placing the system bus or PCI bus 120 in a special mode     |

|                | optimized for real-time data transfers."); see also:        |

|                | • "Referring now to FIG. 21, a computer system is shown     |

|                | which includes an expansion bus, preferably a PCI bus       |

|                | 120, and which includes mode logic which selects            |

|                | between different modes of the PCI bus 120. The             |

|                | computer system of FIG. 21 is similar to the computer       |

|                | system of FIG. 1. However, the mode logic in the            |

|                | computer system of FIG. 21 is operable to place the PCI     |

|                | bus 120 in either a normal PCI mode or in a real-           |

|                | time/multimedia mode optimized for multimedia transfers     |

|                | of periodic data. As described below, multimedia devices    |

|                | use the PCI bus 120 for normal PCI transfers and also use   |

|                | the PCI bus fines in the multimedia mode for high speed     |

|                | data multimedia transfers, preferably transfers of periodic |

|                | multimedia data. In the following description, elements     |

|                | which are preferably identical to elements previously       |

|                | described include the same reference numerals for           |

|                | convenience." Id. at 26:48-63 (emphasis added).             |

| Claim Language | Lambrecht                                                         |

|----------------|-------------------------------------------------------------------|

|                | • "In one embodiment, the system bus (preferably PCI)             |

|                | implements a new mode of operation specifically for real-         |

|                | time transfers. A signal (or signals) is used to indicate that    |

|                | the system bus should be placed in a special real time            |

|                | mode. When not in special real time mode, the system bus          |

|                | operates as usual. The <i>real time mode</i> is optimized for the |

|                | transfer of high bandwidth real-time information.                 |

|                | Therefore, the present invention comprises a novel                |

|                | computer system architecture and method which provides            |

|                | one or more real-time or multimedia buses, optionally             |

|                | with a local expansion bus, to increase the performance of        |

|                | real-time peripherals and applications. The multimedia            |

|                | bus of the present invention provides improved data               |

|                | transfers performance and throughput for real-time                |

|                | devices. The various embodiments discussed above may              |

|                | be combined in various ways for optimum real-time                 |

|                | and/or multimedia performance." Id. at 5:33-48 (emphasis          |

|                | added).                                                           |

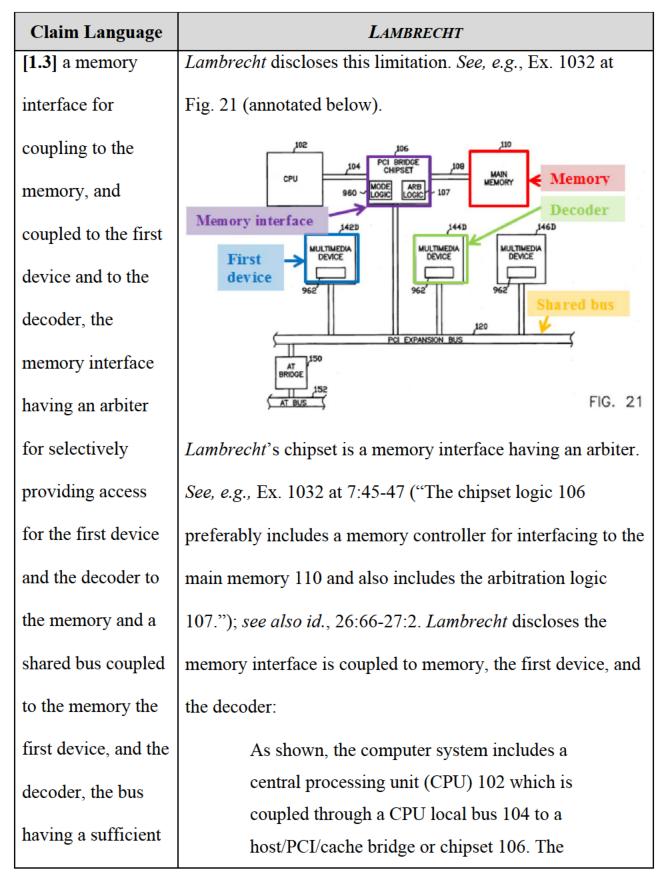

| Claim Language       | LAMBRECHT                                                   |

|----------------------|-------------------------------------------------------------|

| bandwidth to         | chipset 106 includes various bridge logic                   |

| enable the decoder   | and includes arbitration logic 107. The                     |

|                      | chipset 106 is preferably similar to the                    |

| to access the        | Triton chipset available from Intel                         |

| memory and           | Corporation, including certain arbiter                      |

| operate in real time | modifications to accommodate the real-time                  |

| -                    | bus of the present invention. A second level                |

| when the first       | or L2 cache memory (not shown) may be                       |

| device               | coupled to a cache controller in the chipset                |

| simultaneously       | 106, as desired. The bridge or chipset 106                  |

| -                    | couples through a memory bus 108 to main                    |

| accesses the bus.    | memory 110. The main memory 110 is                          |

|                      | preferably DRAM (dynamic random access                      |

|                      | memory) or EDO (extended data out)                          |

|                      | memory, or other types of memory, as                        |

|                      | desired. The chipset logic 106 preferably                   |

|                      | includes a memory controller for interfacing                |

|                      | to the main memory 110 and also includes                    |

|                      | the arbitration logic 107.                                  |

|                      | See id. at 7:30-47 (emphasis added); see also id. at 26:66- |

|                      | 27:9, Fig. 21 (annotated above).                            |

|                      | The memory interface (i.e. the chipset) includes an arbiter |

| Claim Language | Lambrecht                                                        |

|----------------|------------------------------------------------------------------|

|                | that "selectively provid[es] access for the first device and the |

|                | decoder to the memory and a shared bus coupled to the            |

|                | memory the first device, and the decoder," as claimed. See,      |

|                | e.g., Ex. 1032 at 26:66-27:2 ("The chipset logic 106             |

|                | preferably includes a memory controller for interfacing to the   |

|                | main memory 110 and also includes the arbitration logic          |

|                | 107."); see also Fig. 21 (annotated above).                      |

|                |                                                                  |

|                | Furthermore, Lambrecht's bus is of "sufficient bandwidth to      |

|                | enable the decoder to access the memory and operate in real      |

|                | time when the first device simultaneously accesses the bus,"     |

|                | as claimed. Lambrecht teaches a design that allows real-time     |

|                | operation of a bus while simultaneously allowing access to       |

|                | two different devices. See, e.g., Ex. 1032 at 5:33-48; 27:66-    |

|                | 28:11. Lambrecht discloses a "byte sliced mode" that divides     |

|                | the bus into different byte lanes, which allows for two          |

|                | different simultaneous data transfers. See Ex. 1032 at 27:66-    |

|                | 28:11. Lambrecht adds:                                           |

|                | In one embodiment, the centralized                               |

| Claim Language | LAMBRECHT                                                |

|----------------|----------------------------------------------------------|

|                | multimedia I/O processor byte slices the                 |

|                | multimedia bus to allow different data                   |

|                | streams to use different byte channels                   |

|                | simultaneously. Thus the byte sliced                     |

|                | multimedia bus allows different peripherals              |

|                | to share the bus simultaneously. The                     |

|                | centralized multimedia I/O processor thus                |

|                | may assign one data stream to a subset of the            |

|                | total byte lanes on the multimedia bus, and              |

|                | fill the unused byte lanes with another data             |

|                | stream. For example, with a 32-bit                       |

|                | multimedia bus, if an audio data stream is               |

|                | only 16 bits wide and thus only uses half of             |

|                | the multimedia data bus, the multimedia bus              |

|                | intelligently allows data stream transfers on            |

|                | the unused bits of the bus. In this                      |

|                | embodiment, the centralized multimedia I/O               |

|                | processor includes knowledge of the                      |

|                | destinations and allows transfers to occur               |

|                | without addressing information.                          |

|                | Lambrecht at 5:17-33 (emphasis added).                   |

|                |                                                          |

|                |                                                          |

|                | Byte slice mode allows for simultaneous, real-time video |

|                | and audio transfers over the same PCI bus:               |

| Claim Language | LAMBRECHT                                    |

|----------------|----------------------------------------------|

|                | In the preferred embodiment of the           |

|                | invention of FIG. 21, the multimedia mode    |

|                | comprises placing the system bus or PCI bus  |

|                | 120 in a special mode optimized for real-    |

|                | time data transfers. In one embodiment of    |

|                | FIG. 21, the special mode comprises a byte   |

|                | sliced mode which uses different byte lanes  |

|                | or channels of the PCI data lines for        |

|                | different types of multimedia transfers as   |

|                | described above. Thus, 16 bits of the PCI    |

|                | bus may be used for video transfers while    |

|                | the remaining 16 bits may be used for audio  |

|                | transfers simultaneously. Alternatively, the |

|                | special mode comprises placing the PCI bus   |

|                | 120 in a time sliced or time slotted mode as |

|                | described above with reference to FIGS. 11   |

|                | and 12. In another embodiment, the special   |

|                | or real time mode comprises placing the PCI  |

|                | bus 120 in mode for performing periodic      |

|                | multimedia data transfers as described       |

|                | above. Other types of multimedia modes       |

|                | may be used as desired.                      |

|                | See id. at 27:66-28:11 (emphasis added).     |

|                |                                              |

|                |                                              |

| Claim Language | LAMBRECHT                                                     |

|----------------|---------------------------------------------------------------|

|                | By using byte slice mode over the PCI bus disclosed in        |

|                | Lambrecht (see Fig. 21 (annotated above)), the bus has        |

|                | sufficient bandwidth to allow real-time access to memory to   |

|                | both the first device (for example, an audio circuit) and the |

|                | decoder. See also:                                            |

|                | • "In one embodiment, the centralized multimedia I/O          |

|                | processor byte slices the multimedia bus to allow             |

|                | different data streams to use different byte channels         |

|                | simultaneously. Thus the byte sliced multimedia bus           |

|                | allows different peripherals to share the bus                 |

|                | simultaneously. The centralized multimedia I/O processor      |

|                | thus may assign one data stream to a subset of the total      |

|                | byte lanes on the multimedia bus, and fill the unused byte    |

|                | lanes with another data stream. For example, with a 32-       |

|                | bit multimedia bus, if an audio data stream is only 16 bits   |

|                | wide and thus only uses half of the multimedia data bus,      |

|                | the multimedia bus intelligently allows data stream           |

|                | transfers on the unused bits of the bus. In this              |

|                | embodiment, the centralized multimedia I/O processor          |

| Claim Language | LAMBRECHT                                                   |

|----------------|-------------------------------------------------------------|

|                | includes knowledge of the destinations and allows           |

|                | transfers to occur without addressing information." Id. at  |

|                | 19:39-54 (emphasis added).                                  |

|                |                                                             |

|                | See also:                                                   |

|                | • "Referring now to FIG. 21, a computer system is shown     |

|                | which includes an expansion bus, preferably a PCI bus       |

|                | 120, and which includes mode logic which selects            |

|                | between different modes of the PCI bus 120. The             |

|                | computer system of FIG. 21 is similar to the computer       |

|                | system of FIG. 1. However, the mode logic in the            |

|                | computer system of FIG. 21 is operable to place the PCI     |

|                | bus 120 in either a normal PCI mode or in a real-           |

|                | time/multimedia mode optimized for multimedia transfers     |

|                | of periodic data. As described below, multimedia devices    |

|                | use the PCI bus 120 for normal PCI transfers and also use   |

|                | the PCI bus fines in the multimedia mode for high speed     |

|                | data multimedia transfers, preferably transfers of periodic |

|                | multimedia data. In the following description, elements     |

| Claim Language | Lambrecht                                                  |

|----------------|------------------------------------------------------------|

|                | which are preferably identical to elements previously      |

|                | described include the same reference numerals for          |

|                | convenience." Id. at 26:48-63 (emphasis added).            |

|                | • "In one embodiment, the system bus (preferably PCI)      |

|                | implements a new mode of operation specifically for        |

|                | real-time transfers. A signal (or signals) is used to      |

|                | indicate that the system bus should be placed in a special |

|                | real time mode. When not in special real time mode, the    |

|                | system bus operates as usual. The real time mode is        |

|                | optimized for the transfer of high bandwidth real-time     |

|                | information. Therefore, the present invention comprises a  |

|                | novel computer system architecture and method which        |

|                | provides one or more real-time or multimedia buses,        |

|                | optionally with a local expansion bus, to increase the     |

|                | performance of real-time peripherals and applications.     |

|                | The multimedia bus of the present invention provides       |

|                | improved data transfers performance and throughput for     |

|                | real-time devices. The various embodiments discussed       |

|                | above may be combined in various ways for optimum          |

| Claim Language | Lambrecht                                                |

|----------------|----------------------------------------------------------|

|                | real-time and/or multimedia performance." Id. at 5:33-48 |

|                | (emphasis added).                                        |

# 79. In my opinion, *Lambrecht* discloses every feature of claim 3.

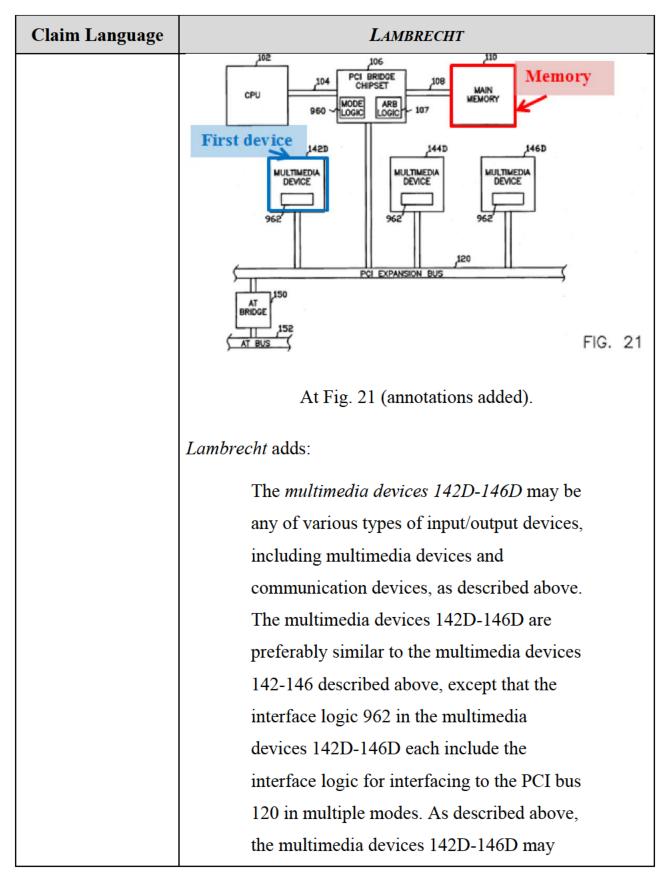

| Claim Language       | LAMBRECHT                                                       |

|----------------------|-----------------------------------------------------------------|

| [3.1] The electronic | As discussed above, Lambrecht discloses all elements of         |

| system of claim 1,   | claim 1. Further, Lambrecht teaches that the decoder is a       |

| wherein the          | video decoder. See, e.g., Ex. 1032 at 27:51-53; see also id. at |

| decoder comprises    | 27:43-56 ("The multimedia devices 142D-146D may be any          |

| a video decoder.     | of various types of input/output devices, including             |

|                      | multimedia devices and communication devices, as described      |

|                      | above. The multimedia devices 142D-146D are preferably          |

|                      | similar to the multimedia devices 142-146 described above,      |

|                      | except that the interface logic 962 in the multimedia devices   |

|                      | 142D-146D each include the interface logic for interfacing to   |

|                      | the PCI bus 120 in multiple modes. As described above, the      |

|                      | multimedia devices 142D-146D may comprise video                 |

|                      | accelerator or graphics accelerator cards, video playback       |

| Claim Language | LAMBRECHT                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------|

|                | cards, MPEG decoder cards, sound cards, network interface                                                   |

|                | cards, SCSI adapters for interfacing to various input/output                                                |

|                | devices, such as CD-ROMS and tape drives, or other devices                                                  |

|                | as desired."), Fig. 21 (annotated below).                                                                   |

|                | Memory interface<br>960<br>WOOR<br>Memory interface<br>962<br>962<br>962<br>962<br>962<br>962<br>962<br>962 |

|                | FIG. 21                                                                                                     |

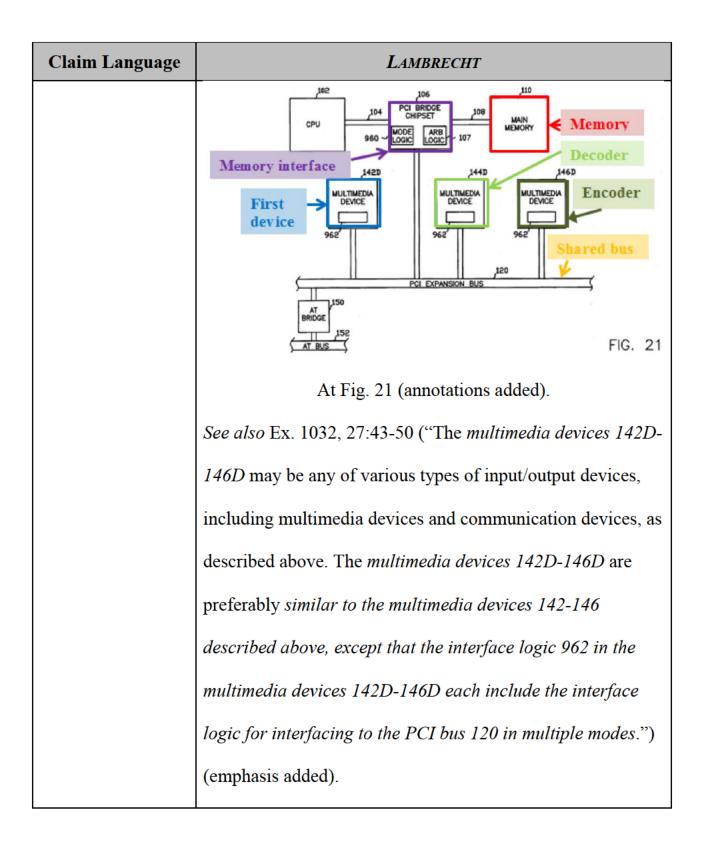

| Claim Language       | LAMBRECHT                                                    |

|----------------------|--------------------------------------------------------------|

| [5.1] The electronic | As discussed above, Lambrecht discloses all elements of      |

| system of claim 1,   | claim 1. Further, Lambrecht teaches the inclusion of an      |

| further comprising   | encoder coupled to the memory interface. See, e.g., Ex. 1032 |

| an encoder coupled   | at 2:66-3:7 ("In the preferred embodiment, the computer      |

| to the memory        | system comprises a CPU coupled through chip set or bridge    |

| interface.           | logic to main memory. The bridge logic couples to a local    |

|                      | bus such as the PCI bus. The computer system also includes   |

|                      | a real-time expansion bus or multimedia bus for transferring |

|                      | real-time or multimedia data. A plurality of multimedia      |

|                      | devices, such video devices, audio devices, MPEG encoders    |

|                      | and/or decoders, and/or communications devices, are coupled  |

|                      | to each of the PCI bus and the multimedia bus.") (emphasis   |

|                      | added); id. at 8:13-17 ("For example, the multimedia devices |

|                      | 142-146 may comprise video accelerator or graphics           |

|                      | accelerator devices, video playback devices, MPEG encoder    |

|                      | or decoder devices") (emphasis added); id. at Fig. 21        |

|                      | (annotated below).                                           |

80. In my opinion, *Lambrecht* discloses every feature of claim 5.

| Claim<br>Language | LAMBRECHT                                                           |

|-------------------|---------------------------------------------------------------------|

| [11.1] The        | As discussed above, Lambrecht discloses all elements of claim       |

| electronic        | 1. Lambrecht also teaches that the first device can be a graphics   |

| system of claim   | accelerator. See, e.g., Ex. 1032, 27:43-56 ("The multimedia         |

| 1, wherein the    | devices 142D-146D may be any of various types of input/output       |

| first device is a | devices, including multimedia devices and communication             |

| graphics          | devices, as described above. The multimedia devices 142D-           |

| accelerator.      | 146D are preferably similar to the multimedia devices 142-146       |

|                   | described above, except that the interface logic 962 in the         |

|                   | multimedia devices 142D-146D each include the interface logic       |

|                   | for interfacing to the PCI bus 120 in multiple modes. As            |

|                   | described above, the multimedia devices 142D-146D may               |

|                   | comprise video accelerator or graphics accelerator cards, video     |

|                   | playback cards, MPEG decoder cards, sound cards, network            |

|                   | interface cards, SCSI adapters for interfacing to various           |

|                   | input/output devices, such as CD-ROMS and tape drives, or           |

|                   | other devices as desired.") (emphasis added).; see also id. at Fig. |

## 81. In my opinion, *Lambrecht* discloses every feature of claim 11.

| Claim<br>Language | Lambrecht |

|-------------------|-----------|

|                   | 21.       |

## 82. In my opinion, *Lambrecht* discloses every feature of claim 13.

| Claim<br>Language | Lambrecht                                                        |

|-------------------|------------------------------------------------------------------|

| [13.1] The        | As discussed above, Lambrecht discloses all elements of claim    |

| electronic        | 1. Furthermore, Lambrecht teaches that the bus has a bandwidth   |

| system of claim   | of at least twice the bandwidth required for the decoder to      |

| 1, wherein the    | operate in real time.                                            |

| bus has a         |                                                                  |

| bandwidth of at   | Lambrecht discloses that its bus, which is preferably a PCI bus, |

| least twice the   | can service real time operation. See, e.g.,                      |

| bandwidth         | • Ex. 1032 at 27:66-28:2 ("In the preferred embodiment of        |

| required for the  | the invention of FIG. 21, the multimedia mode comprises          |

| decoder to        | placing the system bus or PCI bus 120 in a special mode          |

| operate in real   | optimized for real-time data transfers.") (emphasis              |

| time.             | added).                                                          |

|                   | • Ex. 1032 at 26:48-63 ("Referring now to FIG. 21, a             |

| Claim<br>Language | Lambrecht                                                   |

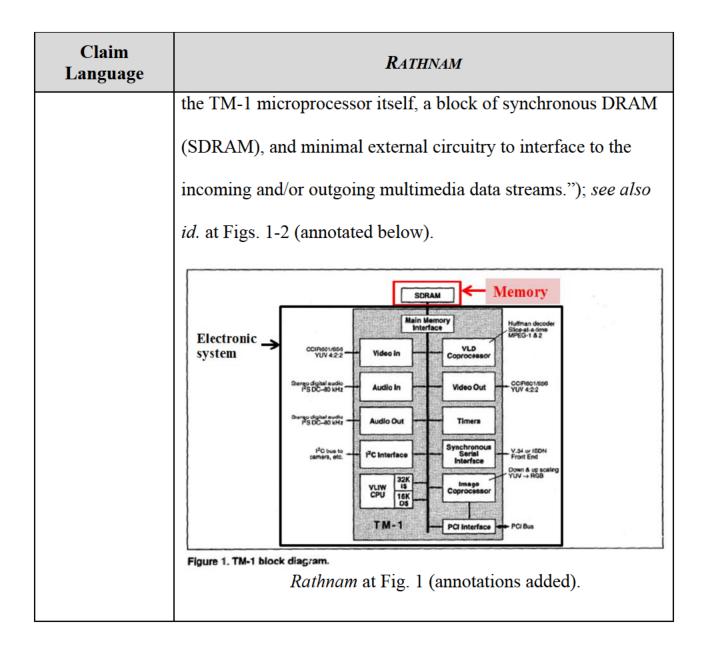

|-------------------|-------------------------------------------------------------|