#### 6.4 Consistency Model

In their paper on the parallel API, Igehy, Stoll and Hanrahan defined the concept of sequential consistency for parallel graphics systems. The graphics system presented in their paper provides commandsequential consistency, which means that each OpenGL command is considered to be an atomic operation. WireGL provides a weaker form of consistency called fragment-sequential consistency. In this consistency model, only operations on the framebuffer are con-sidered to be atomic. When considered in isolation, each tile in WireGL is command-sequentially consistent, but the final image is not. If two clients each draw a triangle without any explicit ordering or depth buffering, WireGL may show one or the other on top on a per-tile basis. Igehy notes that any graphics system that supports the parallel API should provide at least fragment-sequential consistency. Parallel applications that must always produce exactly the same final image can achieve this in one of two ways: they can use depth buffering, or they may express their ordering requirements through the use of the parallel API. WireGL provides both of these capabilities, and we have not found any application that both produces deterministic images and also relies on the stronger command-sequential consistency model.

#### 6.5 Future Work

The main future direction of the WireGL project is to add additional flexibility. The current system is suitable for many applications, but some parallel rendering tasks require a more flexible configuration. When considering the visualization server configuration of WireGL, it is clear that each node in the cluster is acting as an OpenGL stream processor. The application is a stream source, generating multiple streams to a number of rendering tiles. The intermediate pipeservers accept an incoming stream of geometry and generate a new outgoing stream of imagery. The final compositing pipeserver accepts multiple imagery streams and generates a final image for display.

Because the system is closed (that is, each stream is in exactly the same format), it is easy to imagine that other useful stream processing configurations could be constructed. The next version of our cluster rendering software will allow the user to describe an arbitrary directed graph of graphics stream processing units. Stream processors will be written using a standardized interface so that new stream processors can easily be created and plugged into the cluster rendering framework. This will provide researchers with a framework for testing their own cluster rendering algorithms, be they sort-last, sort-first, retained-mode, or extremely specialized. We will be developing parallel applications for volume rendering, interactive exploration of unstructured grid data, terrain flythroughs, as well as parallelized versions of commonly used visualization packages such as VTK, all targeted at this new common cluster rendering framework.

Another promising application of this new technology is transparent support for CAVEs or arrays of casually aligned projectors. A version of WireGL has already been adapted to allow unmodified applications to run in a CAVE, and we have seen a demonstration of WireGL used for a tiled display consisting of off-axis projectors. In addition, we have nearly completed a Microsoft DirectShow backend for the Visualization Server to leverage the latest technology in streaming video codecs for rendering at a distance. Our latest results allow us to deliver the rendering power of our cluster at  $640 \times 480$  across a 100 megabit network, and recent codec advances will allow us to use even slower networks for scalable remote visualization. A version of the system described in this paper has already been developed to perform sort-last parallel rendering, using Lightning-2 to perform depth compositing on the pixel chain.

#### 7 Conclusions

We have described WireGL, a scalable graphics system for clusters of workstations. By integrating parallel submission into our sort-first parallel renderer, we are able to achieve scalable rendering performance for a variety of application types. WireGL allows users to build a graphics system capable of handling demanding real-time, immediate mode tasks at a fraction of the cost of a traditional graphics supercomputer. Alternately, it is possible to realize much higher performance on a cluster of workstations for the same price.

WireGL is a more flexible graphics system than an internally parallel standalone graphics accelerator. By leveraging commodity parts, the building blocks of WireGL can be easily upgraded as technology improves. WireGL enjoys the economies of scale of off-the-shelf parts, providing excellent price performance. In addition, algorithm or system designers can use WireGL as a base for experimentation with parallel rendering. WireGL's flexibility and scalable performance make it an attractive system for real-time rendering on clusters.

#### Acknowledgments

The authors would like to thank the entire Lightning-2 team for their efforts, without which much of this work would be impossible. John Gerth and Chris Niederauer were instrumental in procuring, constructing, and setting up our cluster. Randy Frank, Dino Pavlakos and Brian Wylie provided valuable guidance in designing the cluster and selecting equipment. Nick Triantos and Andrew Ritger provided timely updates to NVIDIA Linux drivers, often providing top-of-tree driver builds. Bob Felderman and Glenn Brown from Myricom were very helpful in tracking down our Myrinet bugs (performance and otherwise). Maureen Stone and François Guimbretière have been very patient users of WireGL as it was maturing. This work was sponsored by the DOE VIEWS program (contract B504665) and the DARPA DIS program (contract DABT63-95-C-0085-P00006).

#### References

- W. Blanke, C. Bajaj, D. Fussel, and X. Zhang. The Metabuffer: A Scalable Multiresolution Multidisplay 3-D Graphics System Using Commodity Rendering Engines. TR2000-16, University of Texas at Austin, February 2000.

- [2] N. Boden, D. Cohen, R. Felderman, A. Kulawik, C. Seitz, J. Seizovic, and W. Su. Myrinet: A Gigabit-per-second Local Area Network. *IEEE Micro*, pages 29-36, February 1995.

- [3] I. Buck, G. Humphreys, and P. Hanrahan. Tracking Graphics State for Networked Rendering. Proceedings of SIGGRAPH/Eurographics Workshop on Graphics Hardware, August 2000.

- [4] R. Cunniff. visualize fx Graphics Scalable Architecture. Proceedings of Eurographics/SIGGRAPH Hot3D, pages 29-38, August 2000.

- [5] Digital Visual Interface Specification. http://www.ddwg.org.

- [6] M. Eldridge, H. Igehy, and P. Hanrahan. Pomegranate: A Fully Scalable Graphics Architecture. *Proceedings of* SIGGRAPH 2000, pages 443-454, July 2000.

- [7] H. Fuchs, J. Poulton, J. Eyles, T. Greer, H. Goldfeather, D. Ellsworth, S. Moinar, G. Turk, B. Tebbs, and L. Israel.

Pixel-Planes 5: A Heterogeneous Multiprocessor Graphics System Using Processor-Enhanced Memories. *Proceedings* of SIGGRAPH 89, pages 79–88, July 1989.

- [8] P. D. Heermann. Production Visualization for the ASCI One TeraFLOPS Machine. *Proceedings of IEEE Visualization*, pages 459–462, October 1998.

- [9] A. Heirich and L. Moll. Scalable Distributed Visualization Using Off-the-Shelf Components. *IEEE Parallel* Visualization and Graphics Symposium, pages 55–59, October 1999.

- [10] G. Humphreys, I. Buck, M. Eldridge, and P. Hanrahan. Distributed Rendering for Scalable Displays. *IEEE Supercomputing 2000*, October 2000.

- [11] H. Igehy, M. Eldridge, and P. Hanrahan. Parallel Texture Caching. Proceedings of SIGGRAPH / Eurographics Workshop on Graphics Hardware, pages 95–106, August 1999.

- [12] H. Igehy, G. Stoll, and P. Hanrahan. The Design of a Parallel Graphics Interface. *Proceedings of SIGGRAPH* 98, pages 141-150, July 1998.

- [13] M. Kilgard. GLR, an OpenGL Render Server Facility. Proceedings of X Technical Conference, February 1996.

- [14] M. Levoy, K. Pulli, B. Curless, S. Rusinkiewicz, D. Koller, L. Pereira, M. Ginzton, S. Anderson, J. Davis, J. Ginsberg, J. Shade, and D. Fulk. The Digital Michelangelo Project: 3D Scanning of Large Statues. *Proceedings of SIGGRAPH* 2000, pages 131–144, July 2000.

- [15] W. E. Lorensen and H. E. Cline. Marching Cubes: A High Resolution 3D Surface Construction Algorithm. *Proceedings* of SIGGRAPH 87, pages 163–169, July 1987.

- [16] S. Molnar, M. Cox, D. Ellsworth, and H. Fuchs. A Sorting Classification of Parallel Rendering. *IEEE Computer Graphics and Algorithms*, pages 23-32, July 1994.

- [17] S. Molnar, J. Eyles, and J. Poulton. PixelFlow: High-Speed Rendering Using Image Composition. *Proceedings of* SIGGRAPH 92, pages 231-240, August 1992.

- [18] J. Montrym, D. Baum, D. Dignam, and C. Migdal. InfiniteReality: A Real-Time Graphics System. *Proceedings* of SIGGRAPH 97, pages 293-302, August 1997.

- [19] C. Mueller. The Sort-First Rendering Architecture for High-Performance Graphics. 1995 Symposium on Interactive 3D Graphics, pages 75–84, April 1995.

- [20] OpenGL Specifications. http://www.opengl.org/Documentation/Specs.html.

- [21] W. C. Reynolds and M. Fatica. Stanford Center for Integrated Turbulence Simulations. *IEEE Computing in Science and Engineering*, pages 54-63, April 2000.

- [22] J. Rohlf and J. Helman. IRIS Performer: A High Performance Multiprocessing Toolkit for Real-Time 3D Graphics. In Proceedings of SIGGRAPH 94, pages 381-395, July 1994.

- [23] R. Samanta, T. Funkhouser, K. Li, and J. P. Singh. Sort-First Parallel Rendering with a Cluster of PCs. SIGGRAPH 2000 Technical Sketch, August 2000.

- [24] R. Samanta, J. Zheng, T. Funkhouser, K. Li, and J. P. Singh. Load Balancing for Multi-Projector Rendering Systems. Proceedings of SIGGRAPH/Eurographics Workshop on Graphics Hardware, pages 107-116, August 1999.

- [25] SGI multipipe. http://www.sgi.com/software/multipipe/.

- [26] SGI vizserver. http://www.sgi.com/software/vizserver/.

. ·

· ·

[27] G. Stoll, M. Eldridge, D. Patterson, A. Webb, S. Berman, R. Levy, C. Caywood, M. Taveira, S. Hunt, and P. Hanrahan. Lightning-2: A High-Performance Display Subsystem for PC Clusters. *Proceedings of SIGGRAPH 2001*, August 2001.

| E (070) 3 40 20 40<br>AX (070) 3 40 30 16         | Concurrent discription of                        | Directorate Consult    | Direction of the last |

|---------------------------------------------------|--------------------------------------------------|------------------------|-----------------------|

|                                                   | Generaldirektion 1                               | Directorate General 1  | Direction générale 1  |

| Howe, Steven<br>Lloyd Wise<br>Commonwealth House, |                                                  |                        |                       |

| 1-19 New Oxford Street                            |                                                  | EPO Customer Servi     | ces                   |

| London WC1A 1LW<br>GRANDE BRETAGNE                |                                                  | Tel.: +31 (0)70 340 45 | 00                    |

|                                                   |                                                  |                        |                       |

|                                                   |                                                  | Date 04.01.06          |                       |

| Reference<br>SH-46739                             | Application No./Paterit No.<br>03257464.2 - 2218 |                        |                       |

#### **COMMUNICATION**

The European Patent Office herewith transmits as an enclosure the European search report (under R. 44 or R. 45 EPC) for the above-mentioned European patent application.

If applicable, copies of the documents cited in the European search report are attached.

Additional set(s) of copies of the documents cited in the European search report is (are) enclosed as well.

The following specifications given by the applicant have been approved by the Search Division :

- Abstract 🗹

- The abstract was modified by the Search Division and the definitive text is attached to this communication.

Title

The following figure will be published together with the abstract : 2

#### Refund of search fee

If applicable under Article 10 Rules relating to fees, a separate communication from the Receiving Section on the refund of the search fee will be sent later.

European Patent Office

## EUROPEAN SEARCH REPORT

Application Number EP 03 25 7464

> - --

|                                                   | DOCUMENTS CONSIDER                                                                                                                                                                                                  | RED TO BE RELEVANT                                                                                                                                                      |                                                                                          |                                                    |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------|

| Category                                          | Citation of document with indi<br>of relevant passag                                                                                                                                                                |                                                                                                                                                                         | Relevant<br>to claim                                                                     | CLASSIFICATION OF THE<br>APPLICATION (IPC)         |

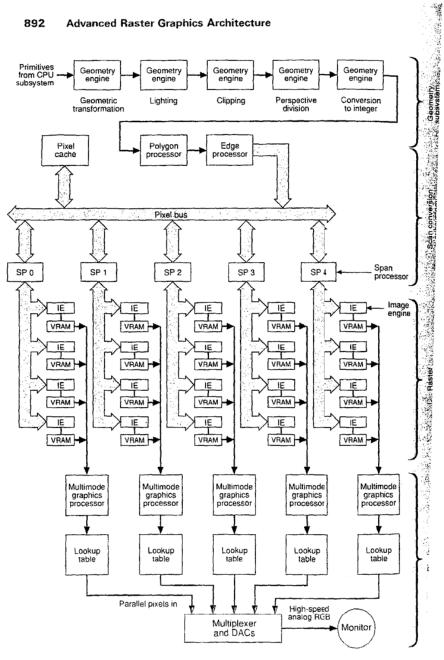

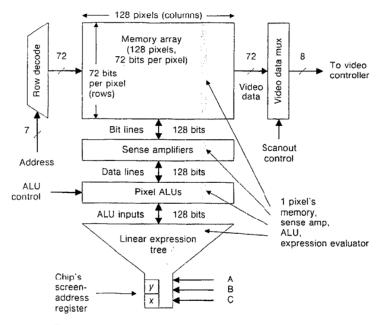

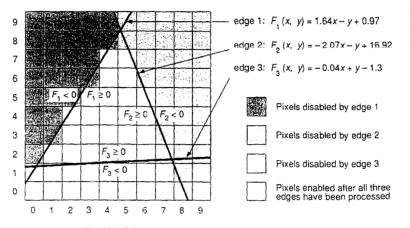

| X<br>Y                                            | FOLEY JAMES ET AL: '<br>Principles and Practi<br>COMPUTER GRAPHICS. PF<br>PRACTICE, READING, AD<br>1990, pages 873-899,<br>* pages 874,876, *                                                                       | Ce"<br>RINCIPLES AND<br>DDISON WESLEY, US                                                                                                                               | 1-7,9-24<br>1-3,8,<br>19-24                                                              | G06T15/00                                          |

|                                                   | * pages 887,888 *                                                                                                                                                                                                   |                                                                                                                                                                         | 15 24                                                                                    |                                                    |

| X                                                 | 819-843, XP004729969                                                                                                                                                                                                |                                                                                                                                                                         | 1-7,<br>9-18,<br>20-24                                                                   |                                                    |

| Y                                                 | ISSN: 0167-8191<br>* pages 822-823 *<br>* page 828 *                                                                                                                                                                |                                                                                                                                                                         | 1-3,<br>20-24                                                                            |                                                    |

| Y                                                 | ACM NEW YORK, NY, USA<br>293-302, XP002360078<br>ISBN: 0-89791-896-7                                                                                                                                                | CEEDINGS, SIGGRAFH 97<br>, 1997, pages                                                                                                                                  | 1-3,<br>20-24                                                                            | TECHNICAL FIELDS<br>SEARCHED (IPC)<br>G06T<br>G09G |

| A                                                 | * pages 294-296; figu                                                                                                                                                                                               | res 1-3 *                                                                                                                                                               |                                                                                          |                                                    |

| Y                                                 | US 6 424 345 B1 (SMIT<br>23 July 2002 (2002-07<br>* column 3, line 31 -<br>* column 6, line 20 -                                                                                                                    | -23)<br>line 60; figure 7 *                                                                                                                                             | 1-3,8,<br>19-24                                                                          |                                                    |

|                                                   | -                                                                                                                                                                                                                   |                                                                                                                                                                         |                                                                                          |                                                    |

|                                                   | The present search report has bee                                                                                                                                                                                   | -                                                                                                                                                                       | -                                                                                        |                                                    |

|                                                   | Place of search                                                                                                                                                                                                     | Date of completion of the search                                                                                                                                        | N.                                                                                       | Examiner ·                                         |

| C/<br>X : parti<br>Y : parti<br>docu<br>A : techr | Munich<br>ATEGORY OF CITED DOCUMENTS<br>cularly relevant if taken alone<br>cularly relevant if combined with another<br>ment of the same category<br>hological background<br>written disclosure<br>mediate document | 19 December 2005<br>T : theory or principle<br>E : earlier patent dor<br>after the filing dat<br>D : document cited in<br>L : document cited fo<br>& : member of the sa | e underlying the in<br>cument, but publis<br>te<br>n the application<br>or other reasons | shed on, or                                        |

European Patent Office

## EUROPEAN SEARCH REPORT

Application Number EP 03 25 7464

|                                                        | DOCUMENTS CONSIL                                                                                                                                                                                       | ERED TO BE RELEVANT                                                                      |                                                                    |                                            |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------|

| Category                                               | Citation of document with<br>of relevant pas                                                                                                                                                           | ndication, where appropriate, sages                                                      | Relevant<br>to claim                                               | CLASSIFICATION OF THI<br>APPLICATION (IPC) |

| Χ.                                                     | HUMPHREYS G ET AL:<br>graphics system for<br>COMPUTER GRAPHICS A                                                                                                                                       | "WireGL: a scalable<br>clusters"<br>PROCEEDINGS. SIGGRAFH<br>NY, USA, 2001, pages        | 1-3,<br>20-24                                                      | TECHNICAL FIELDS<br>SEARCHED (IPC)         |

|                                                        | The present search report has<br>Place of search                                                                                                                                                       | been drawn up for all claims<br>Date of completion of the search                         | -                                                                  | Examiner                                   |

|                                                        | Munich                                                                                                                                                                                                 | 19 December 2005                                                                         | Mei                                                                | nl, W                                      |

| X : parti<br>Y : parti<br>docu<br>A : tech<br>O : non- | ATEGORY OF CITED DOCUMENTS<br>cularly relevant if taken alone<br>cularly relevant if combined with ano<br>ment of the same category<br>nological background<br>-written disclosure<br>mediate document | E : earliér patent do<br>after the filing da<br>D : document cited<br>L : document cited | cument, but publi<br>ite<br>in the application<br>or other reasons | shed on, or                                |

#### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 03 25 7464

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

#### 19-12-2005

| cited in search report |    | date       | Patent family<br>member(s)     | date |

|------------------------|----|------------|--------------------------------|------|

| US 6424345             | B1 | 23-07-2002 | NONE                           |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

| <b>*:</b>              |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            |                                |      |

|                        |    |            | ppean Patent Office, No. 12/82 |      |

|                        |    |            |                                |      |

# XP-002360077

# SECOND EDITION IN C

# Computer Graphics

# PRINCIPLES AND PRACTICE

James D. Foley

Georgia Institute of Technology

## Andries van Dam Brown University

# Steven K. Feiner Columbia University

# John F. Hughes

Brown University

## ₹₹

ADDISON-WESLEY PUBLISHING COMPANY Reading, Massachusetts • Menlo Park, California • New York Don Mills, Ontario • Wokingham, England • Amsterdam • Bonn Sydney • Singapore • Tokyo • Madrid • San Juan • Milan • Paris Summing the floating-point requirements for all of the geometry stages gives a total of 2.220.000 multiplications/divisions and 1.470.000 additions/subtractions per frame. Since a new frame is calculated every  $\frac{1}{10}$  second, a total of 22.2 million multiplications/divisions and 14.7 million additions/subtractions (36.9 million aggregate floating-point operations) as required per second—a very substantial number.

**Rasterization calculations and frame-buffer accesses.** Let us now estimate the number of pixel calculations and frame-buffer memory accesses required in each frame. We assume that z values and RGB triples each occupy one word (32 bits) of frame-buffer memory (typical in most current high-performance systems). For each pixel that is initially visible (i.e., results in an update to the frame buffer), z, R, G, and B values are calculated (4 additions per pixel if forward differences are used), a z value is read from the frame buffer (1 frame-buffer cycle), the z values are compared (1 subtraction) and new z values and colors are written (2 frame-buffer cycles). For each pixel that is initially not visible, only the z value needs to be calculated (1 addition), and a z value is read from the frame buffer (1 frame-buffer cycle), and the two z values are compared (1 subtraction). Note that initially visible pixels may get covered, but initially invisible pixels can never be exposed.

Since we assume that one-half of the pixels of each triangle are visible in the final scene, a reasonable guess is that three-quarters of the pixels are initially visible and one-quarter of the pixels are initially invisible. Each triangle covers 100 pixels, so  $\frac{3}{4} \cdot 100 \cdot 10,000 = 750,000$  pixels are initially visible and  $\frac{1}{4} \cdot 100 \cdot 10,000 = 250,000$  pixels are initially visible and  $\frac{1}{4} \cdot 100 \cdot 10,000 = 250,000$  pixels are initially invisible. To display an entire frame, therefore, a total of (750,000  $\cdot$  5) + (250,000  $\cdot$  2) = 4.25 million additions and (750,000  $\cdot$  3) + (250,000  $\cdot$  1) = 2.5 million frame-buffer accesses is required. To initialize each frame, both color and z-buffers must be cleared, an additional 1280  $\cdot 1024 \cdot 2 = 2.6$  million frame-buffer accesses. The total number of frame-buffer accesses per frame, therefore, is 2.5 million + 2.6 million = 5.1 million. If 10 frames are generated per second, 42.5 million additions and 51 million frame-buffer accesses are required per second.

In 1989, the fastest floating-point processors available computed approximately 20 million floating-point operations per second, the fastest integer processors computed approximately 40 million integer operations per second, and DRAM memory systems had cycle times of approximately 100 nanoseconds. The floating-point and integer requirements of our sample application, therefore, are just at the limit of what can be achieved in a single CPU. The number of frame-buffer accesses, however, is much higher than is possible in a conventional memory system. As we mentioned earlier, this database is only modestly sized for systems available in 1989. In the following sections, we show how multiprocessing can be used to achieve the performance necessary to display databases that are this size and larger.

#### 18.4 INTRODUCTION TO MULTIPROCESSING

Displaying large databases at high frame rates clearly requires dramatic system performance, both in terms of computations and of memory of bandwidth. We have seen that the geometry portion of a graphics system can require more processing power than a single CPU can provide. Likewise, rasterization can require more bandwidth into memory than a single memory system can provide. The only way to attain such performance levels is to

13.4

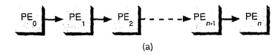

Fig. 18.9 Basic forms of multiprocessing: (a) pipelining, and (b) parallelism.

perform multiple operations concurrently and to perform multiple reads and writes memory concurrently—we need concurrent processing.

Concurrent processing, or *multiprocessing*, is the basis of virtually all high-performance graphics architectures. Multiprocessing has two basic forms: *pipelining* and *parallelism* (we reserve the term *concurrency* for multiprocessing in general). A *pipeline* processor contains a number of processing elements (PEs) arranged such that the output of one becomes the input of the next, in pipeline fashion (Fig. 18.9a). The PEs of a parallel processor are arranged side by side and operate simultaneously on different portions of the data (Fig. 18.9b).

#### 18.4.1 Pipelining

To pipeline a computation, we partition it into stages that can be executed sequentially in separate PEs. Obviously, a pipeline can run only as fast as its slowest stage, so the processing load should be distributed evenly over the PEs. If this is not possible, PEs can be sized according to the jobs they must perform.

An important issue in pipeline systems is *throughput* versus *latency*. Throughput is the overall rate at which data are processed; latency is the time required for a single data element to pass from the beginning to the end of the pipeline. Some calculations can be pipelined using a large number of stages to achieve very high throughput. Pipeline latency increases with pipeline length, however, and certain computations can tolerate only a limited amount of latency. For example, real-time graphics systems, such as flight simulators, must respond quickly to changes in flight controls. If more than one or two frames are in the rendering pipeline at once, the system's interactivity may be impaired regardless of the frame rate.

#### 18.4.2 Parallelism

To parallelize a computation, we partition the data into portions that can be processed independently by different PEs. Frequently, PEs can execute the same program. *Homogeneous* parallel processors contain PEs of the same type; *heterogeneous* parallel processors contain PEs of different types. In any parallel system, the overall computation speed is determined by the time required for the slowest PE to finish its task. It is important, therefore, to balance the processing load among the PEs.

A further distinction is useful for homogeneous parallel processors: whether the processors operate in *lock step* or independently. Processors that operate in lock step generally share a single code store and are called *single-instruction multiple-data* (SIMD) processors. Processors that operate independently must have a separate code store for each PE and are called *multiple-instruction multiple-data* (MIMD) processors.

**SIMD processors.** Because all the PEs in a SIMD processor share a single code store, SIMD processors are generally less expensive than MIMD processors. However, they do not perform well on algorithms that contain conditional branches or that access data using pointers or indirection. Since the path taken in a conditional branch depends on data specific to a PE, different PEs may follow different branch paths. Because all the PEs in a SIMD processor operate in lock step, they all must follow every possible branch path. To accommodate conditional branches, PEs generally contain an *enable register* to qualify write operations. Only PEs whose enable registers are set write the results of computations. By appropriately setting and clearing the enable register, PEs can execute conditional branches (see Fig. 18.10a).

Algorithms with few conditional branches execute efficiently on SIMD processors. Algorithms with many conditional branches can be extremely inefficient, however, since

| statement 1;                    | statement 1;                   |

|---------------------------------|--------------------------------|

| if not condition then           | if condition then              |

| enable = FALSE;                 | statement 2;                   |

| statement 2;                    | else                           |

| toggle enable;                  | begin                          |

| statement 3;                    | statement 3;                   |

| statement 4;                    | statement 4;                   |

| enable = TRUE;                  | end;                           |

| statement 5;                    | statement 5;                   |

| statement 6;                    | statement 6;                   |

| Total operations:               | Total operations:              |

| 10 if condition evaluates TRUE, | 5 if condition evaluates TRUE, |

| 10 if condition evaluates FALSE | 6 if condition evaluates FALSE |

| (a)                             | (b)                            |

Fig. 18.10 (a) SIMD and (b) MIMD expressions of the same algorithm. In a SIMD program, conditional branches transform into operations on the enable register. When the enable register of a particular PE is FALSE, the PE executes the current instruction, but does not write the result.

#### 18.4

most PEs may be disabled at any given time. Data structures containing pointers (such as linked lists or trees) or indexed arrays cause similar problems. Since a pointer or array index may contain a different value at each PE, all possible values must be enumerated to ensure that each PE can make its required memory reference. For large arrays or pointers, this is an absurd waste of processing resources. A few SIMD processors provide separate address wires for each PE in order to avoid this problem, but this adds size and complexity to the system.

MIMD processors. MIMD processors are more expensive than SIMD processors, since each PE must have its own code store and controller. PEs in a MIMD processor often execute the same program. Unlike SIMD PEs, however, they are not constrained to operate in lock step. Because of this freedom, MIMD processors suffer no disadvantage when the encounter conditional branches; each PE makes an independent control-flow decision skipping instructions that do not need to be executed (see Fig. 18.10b). As a result, MIMD processors achieve higher efficiency on general types of computations. However, since processors may start and end at different times and may process data at different rates synchronization and load balancing are more difficult, frequently requiring FIFO buffers at the input or output of each PE.

#### 18.4.3 Multiprocessor Graphics Systems

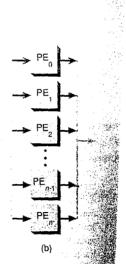

Pipeline and parallel processors are the basic building blocks of virtually all current high-performance graphics systems. Both techniques can be used to accelerate front-end and back-end subsystems of a graphics system, as shown in Fig. 18.11.

In the following sections, we examine each of these strategies. Sections 18.5 and 18.6 discuss pipeline and parallel front-end architectures. Sections 18.8 and 18.9 discuss pipeline and parallel back-end architectures. Section 18.10 discusses back-end architectures that use parallel techniques in combination.

Fig. 18.11 Pipelining and parallelism can be used to accelerate both front-end and back-end portions of a graphics system.

#### **18.5 PIPELINE FRONT-END ARCHITECTURES**

Recall from Section 18.3 that the front end of a graphics display system has two major tasks: traversing the display model and transforming primitives into screen space. As we have seen, to achieve the rendering rates required in current applications, we must use concurrency to speed these computations. Both pipelining and parallelism have been used for decades to build front ends of high-performance graphics systems. Since the front end is intrinsically pipelined, its stages can be assigned to separate hardware units. Also, the large numbers of primitives in most graphics databases can be distributed over multiple processors and processed in parallel. In this section, we discuss pipeline front-end systems. We discuss parallel front-end systems in Section 18.6.

In introducing the standard graphics pipeline of Fig. 18.7, we mentioned that it provides a useful conceptual model of the rendering process. Because of its linear nature and fairly even allocation of processing effort, it also maps well onto a physical pipeline of processors. This has been a popular approach to building high-performance graphics systems since the 1960s, as described in [MYER68], a classic paper on the evolution of graphics architectures. Each stage of the pipeline can be implemented in several ways: as an individual general-purpose processor, as a custom hardware unit, or as a pipeline or parallel processor itself. We now discuss implementations for each stage in the front-end pipeline.

#### 18.5.1 Application Program and Display Traversal

Some processor must execute the application program that drives the entire graphics system. In addition to feeding the graphics pipeline, this processor generally handles input devices, file I/O, and all interaction with the user. In systems using immediate-mode traversal, the display model is generally stored in the CPU's main memory. The CPU must therefore traverse the model as well as run the application. In systems using retained mode, the model is generally (but not always) stored in the display processor's memory, with the display processor performing traversal. Because such systems use two processors for these tasks, they are potentially faster, although they are less flexible and have other limitations, as discussed in Section 7.2.2.

Where very high performance is desired, a single processor may not be powerful enough to traverse the entire database with sufficient speed. The only remedy is to partition the database and to traverse it in parallel. This relatively new technique is discussed in Section 18.6.1.

#### 18.5.2 Geometric Transformation

Statistic Lines

The geometric transformation stages (modeling transformation and viewing transformation) are highly compute-intensive. Fortunately, vector and matrix multiplications are simple calculations that require no branching or looping, and can readily be implemented in hardware.

The most common implementation of these stages is a single processor or functional unit that sequentially transforms a series of vertices. A pioneering processor of this type was the Matrix Multiplier [SUTH68], which could multiply a four-element vector by a

homogeneous transformation matrix in 20 microseconds. Other special-purpose geometry processors have been developed since then, most notably Clark's Geometry Engine, which can perform clipping as well (see Section 18.5.5). Recent geometry processors have exploited the power and programmability of commercial floating-point chips.

If pipelining does not provide enough performance, transformation computations can be parallelized in several ways:

- Individual components of a vertex may be calculated in parallel. Four parallel processors, each containing the current transformation matrix, can evaluate the expressions for x, y, z, and w in parallel.

- Multiple vertices can be transformed in parallel. If primitives are all of a uniform type—say, triangles—the three vertices of each triangle can be transformed simultaneously.

- Entire primitives can be transformed in parallel. If n transformation engines are available, each processor can transform every nth primitive. This technique has many of the advantages and disadvantages of parallel front-end systems, which we will discuss in Section 18.6.

#### 18.5.3 Trivial Accept/Reject Classification

Trivial accept and reject tests are straightforward to implement, since they require at worst is dot product and at best a single floating-point comparison (or subtract) to determine on which side of each clipping plane each vertex lies. Because these tests require little computation, they are generally performed by the processor that transforms primitives.

#### 18.5.4 Lighting

Like geometric transformation, lighting calculations are straightforward and are floating point-intensive. A specialized hardware processor can calculate vertex colors based on a polygon's color and the light vector. More frequently, lighting calculations are performed using a programmable floating-point processor. In lower-performance systems, lighting calculations can be done in the same processor that transforms vertices. Note that if Phong shading is used, lighting calculations are deferred until the rasterization stage.

#### 18.5.5 Clipping

Polygon clipping was once considered cumbersome, since the number of vertices can change during the clipping process and concave polygons can fragment into multiple polygons during clipping. Sutherland and Hodgman [SUTH74] showed that arbitrary convex or concave polygons can be clipped to a convex view volume by passing the polygon's vertices through a single processing unit multiple times. Each pass through the unit clips the polygon to a different plane. In 1980, Clark proposed unwrapping this processing loop into a simple pipeline of identical processors, each of which could be implemented in a single VLSI chip, which he named the *Geometry Engine* [CLAR82]. The Geometry Engine was general enough that it could transform primitives and perform perspective division as well. Clipping using a Geometry Engine (or similar processor) can be performed either by a single processor that clips each polygon by as many planes as necessary, or by a pipeline of clipping processors, one for each clipping plane. The technique chosen affects the worst-case performance of the graphics system: Systems with only one clipping processor may bog down during frames in which large numbers of primitives need to be clipped, whereas systems with a clipping processor for each clipping plane can run at full speed. However, most of the clipping processors are idle for most databases and views in the latter approach.

General-purpose floating-point units recently have begun to replace custom VLSI transformation and clipping processors. For example, Silicon Graphics, which for many years employed custom front-end processors, in 1989 used the Weitek 3332 floating-point chip for transformations and clipping in their POWER IRIS system (described in detail in Section 18.8.2). The delicate balance between performance and cost now favors commodity processors. This balance may change again in the future if new graphics-specific functionality is needed and cannot be incorporated economically into general-purpose processors.

#### 18.5.6 Division by w and Mapping to 3D Viewpoint

Like geometric transformation and lighting, the calculations in this stage are straightforward but require substantial floating-point resources. A floating-point divide is time consuming even for most floating-point processors (many processors use an iterative method to do division). Again, these stages can be implemented in custom functional units or in a commercial floating-point processor. In very high-performance systems, these calculations can be performed in separate, pipelined processors.

#### 18.5.7 Limitations of Front-End Pipelines

Even though pipelining is the predominant technique for building high-performance front-end systems, it has several limitations that are worth considering. First, a different algorithm is needed for each stage of the front-end pipeline. Thus, either a variety of hard-wired functional units must be designed or, if programmable processors are used, different programs must be written and loaded into each processor. In either case, processor or functional-unit capabilities must be carefully matched to their tasks, or bottlenecks will occur.

Second, since the rendering algorithm is committed to hardware (or at least to firmware, since few systems allow users to reprogram pipeline processors), it is difficult to add new features. Even if users have programming support for the pipeline processors, the distribution of hardware resources in the system may not adequately support new features such as complex primitives or collision detection between primitives.

A final shortcoming of pipelined front ends is that the approach breaks down when display traversal can no longer be performed by a single processor, and this inevitably occurs at some performance level. For example, if we assume that traversal is performed by a 20-MHz processor and memory system, that the description of each triangle in the database requires 40 words of data (for vertex coordinates, normal vectors, colors, etc.), and that each word sent to the pipeline requires two memory/processor cycles (one to read it

13.5

from memory, another to load it into the pipeline), then a maximum of 20,000,000 / (2-40) = 250,000 triangles per second can be displayed by the system, no matter how powerful the processors in the pipeline are. Current systems are rapidly approaching such limits

What else can be done, then, to achieve higher performance? The alternative to pipelining front-end calculations is to parallelize them. The following section describes this second way to build high-performance front-end systems.

#### 18.6 PARALLEL FRONT-END ARCHITECTURES

Since graphics databases are regular, typically consisting of a large number of primitives that receive nearly identical processing, an alternate way to add concurrency is to partition the data into separate streams and to process them independently. For most stages of the front-end subsystem, such partitioning is readily done, for example, the geometric transformation stages can use any of the parallel techniques described in Section 18.5.2. However, stages in which data streams diverge (display traversal) or converge (between the front end and back end) are problematic, since they must handle the full data bandwidth.

#### 18.6.1 Display Traversal

Almost all application programs assume a single, contiguous display model or database. In a parallel front-end system, the simplest technique is to traverse the database in a singles processor (serial traversal) and then to distribute primitives to the parallel processors. Unfortunately, this serial traversal can become the bottleneck in a parallel front-end system. Several techniques can be used to accelerate serial traversal:

- Traversal routines can be optimized or written in assembly code

- The database can be stored in faster memory (i.e., SRAM instead of DRAM)

- A faster traversal processor (or one optimized for the particular structure format) can be used.

If these optimizations are not enough, the only alternative is to traverse the database in parallel. The database either can be stored in a single memory system that allows parallel access by multiple processors (a shared-memory model), or can be distributed over multiple processors, each with its own memory system (a distributed-memory model).

The advantage of the shared-memory approach is that the database can remain in one place, although traversal must be divided among multiple processors. Presumably, each processor is assigned a certain portion of the database to traverse. Unfortunately, inherited attributes in a hierarchical database model mean that processors must contend for access to the same data. For example, each processor must have access to the current transformation matrix and to other viewing and lighting parameters. Since the data bandwidth to and from a shared-memory system may not be much higher than that of a conventional memory system, the shared-memory approach may not provide enough performance.

In the distributed-memory approach, each processor contains a portion of the database in its local memory. It traverses its portion of the database for each frame and may also perform other front-end computations. Distributing the database presents its own problems, however: Unless the system gives the application programmer the illusion of a contiguous database, it cannot support portable graphics libraries. Also, the load must be balanced

#### Parallel Front-End Architectures 881

over the traversal processors if system resources are to be utilized fully. Hierarchical databases exacerbate both of these problems, since attributes in one level of a hierarchy affect primitives below them, and structures deep in a hierarchy may be referenced by multiple higher-level structure calls.

The following two sections examine two ways to distribute a hierarchical database over multiple processors: by structure, where each traversal processor is given a complete branch of the structure hierarchy; or by primitive, where each traversal processor is given a fraction of the primitives at each block in the hierarchy.

**Distributing by structure.** Distributing by structure is outwardly appealing, since state-changing elements in the structure apparently need to be stored only once. This can be an illusion, however, since multiple high-level structures may refer to the same lower-level substructure. For example, a database containing several cars, each described by a separate *car* structure, can be distributed by assigning each *car* structure to a separate processor. However, if each *car* structure refers to a number of *wheel* structures, *wheel* structures must also be replicated at every processor.

Load balancing among processors is also difficult. Since primitives in a structure are likely to be spatially coherent, changing the viewpoint or geometry within a scene may cause entire portions of the structure to be clipped or to reappear. Maintaining even loading among the multiple processors would require reassigning portions of the database dynamically.

**Distributing by primitive.** Distributing by primitive is costly, since the entire hierarchical structure of the database and any state-changing commands must be replicated at each processor. Structure editing is also expensive, since changes must be broadcast to every processor. Load balancing, however, is automatic. Since objects in a hierarchical database typically contain a large number of simple primitives (e.g., polygons forming a tiled surface), these primitives will be scattered over all the processors, and each processor will have a similar processing load.

Parallel display traversal is a relatively new technique. In 1989, the highestperformance architectures were just approaching the point where serial traversal becomes insufficient, and only a few systems had experimented with parallel traversal [FUCH89]. Neither of the distribution techniques for hierarchical databases that we have described is ideal. Compared to geometry processing, which easily partitions into parallel tasks, display traversal is much more difficult. Nevertheless, parallel traversal is likely to become increasingly important as system performance levels increase.

#### 18.6.2 Recombining Parallel Streams

The transition between the front-end and back-end portions of the rendering pipeline is troublesome as well. In a parallel front-end system, the multiple streams of transformed and clipped primitives must be directed to the processor or processors doing rasterization. This can require sorting primitives based on spatial information if different processors are assigned to different screen regions.

A second difficulty in parallel front-end systems is that the ordering of data may change as those data pass through parallel processors. For example, one processor may transform two small primitives before another processor transforms a single, larger one. This does not

18.6

matter for many graphics primitives and rendering techniques. Certain global commands however, such as commands to update one window instead of another or to switch between double buffers, require that data be synchronized before and after the command. If a large number of commands such as these occurs, some type of hardware support for synchronization may be necessary. A Raster Technologies system [TORB87] incorporates a special FIFO into each PE that stores tag codes for each command and allows commands to be resynchronized after they have been processed in separate PEs.

#### 18.6.3 Pipelining versus Parallelism

We have seen that both pipelining and parallelism can be used to build high-performance front-end subsystems. Although pipelining has been the predominant technique in systems of the last decade, parallelism offers several advantages, including reconfigurability for different algorithms, since a single processor handles all front-end calculations, and more modularity, since PEs in a parallel system can be made homogeneous more easily than in a pipeline system. Because the performance of a pipeline system is limited by the throughput of its slowest stage, pipelines do not scale up as readily as do parallel systems. Parallel systems, on the other hand, require more complicated synchronization and load balancing and cannot use specialized processors as well as can pipeline systems. Both designs are likely to be useful in the future; indeed, the highest-performance systems are likely to combine the two.

#### 18.7 MULTIPROCESSOR RASTERIZATION ARCHITECTURES

Recall that the output of the front-end subsystem is typically a set of primitives in screen coordinates. The rasterization (back-end) subsystem creates the final image by scan converting each of these primitives, determining which primitives are visible at each pixel, and shading the pixel accordingly. Section 18.2.4 identified two basic reasons why simple display-processor/frame-buffer systems are inadequate for high-performance rasterization subsystems:

- A single display processor does not have enough processing power for all the pixel calculations.

- Memory bandwidth into the frame buffer is insufficient to handle the pixel traffic even if the display processor could compute pixels rapidly enough.

Much of the research in graphics architecture over the past decade has concerned ways to overcome these limitations. A great variety of techniques has been proposed, and many have been implemented in commercial and experimental systems. In this section, we consider low-cost, moderate-performance architectures that cast conventional algorithms into hardware. In Sections 18.8 and 18.9, we consider ways to improve performance by adding large amounts of parallelism to speed the calculation of the algorithm's "inner loop." In Section 18.10, we consider hybrid architectures that combine multiple techniques for improved efficiency or even higher performance. Figure 18.12 summarizes the concurrent approaches we shall discuss here.

#### Multiprocessor Rasterization Architectures 883

| Rasterization                                                        | 1                                                                  | Architectural technique                                                   |                                                                 |

|----------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|

| algorithm                                                            | Serial pipeline                                                    | Highly parallel                                                           | Hybrid                                                          |

| Object order<br>z-buffer, depth-<br>sort, and BSP-tree<br>algorithms | Pipelined object order<br>Polygon/edge/span-<br>processor pipeline | Image parallel<br>Partitioned image<br>memory<br>Logic-enhanced<br>memory | Virtual buffer/<br>virtual processor<br>Parallel virtual buffer |

| Image order<br>Scanline algorithms                                   | Pipelined image order<br>Scan-line pipeline                        | Object parallel<br>Processor per<br>primitive pipeline<br>Tree-structured | Image composition                                               |

Fig. 18.12 Taxonomy of concurrent rasterization approaches.

#### 18.7.1 Pipelined Object-Order Architectures

18.7

A direct way to add concurrency to rasterization calculations is to cast the various steps of a software algorithm into a hardware pipeline. This technique has been used to build a number of inexpensive, moderately high-performance systems. This approach can be used with either of the two main rasterization approaches: object order (z-buffer, depth-sort, and BSP-tree algorithms) and image order (scan-line algorithms). We consider object-order rasterization now and image-order rasterization in Section 18.7.2.

Object-order rasterization methods include the z-buffer, depth-sort, and BSP-tree algorithms (the z-buffer is by far the most common in 3D systems). The outer loop of these algorithms is an enumeration of primitives in the database, and the inner loop is an enumeration of pixels within each primitive. For polygon rendering, the heart of each of these algorithms is rasterizing a single polygon.

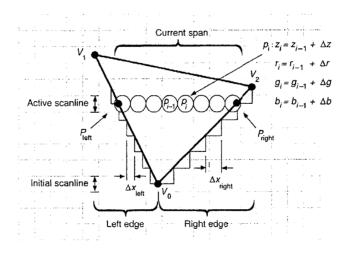

Figure 18.13 shows the most common rasterization algorithm for convex polygons. This algorithm is an extension of the 2D polygon scan-conversion algorithm presented in Section 3.6, using fixed-point arithmetic rather than integer arithmetic. Delta values are used to calculate the expressions for x, z, R, G, and B incrementally from scan line to scan line, and from pixel to pixel. We shall describe each step of the algorithm.

**Polygon processing.** Computations performed only once per polygon are grouped into this stage. The first step is to determine the initial scan line intersected by the polygon (this is determined by the vertex with the smallest y value). In most cases, the polygon intersects this scan line at a single pixel, with two edges projecting upward, the *left* and *right* edges. Delta values are calculated for x, z, R, G, and B for each edge. These delta values are sometimes called *slopes*.

**Edge processing.** Computations performed once for each scan line are grouped here. Scan lines within each primitive are processed one by one. The delta values computed previously are used to calculate x, z, R, G, and B values at the intersection points of the left and right edges with the current scan line  $(P_{\text{left}} \text{ and } P_{\text{right}})$  in the figure). A contiguous sequence of pixels on a scan line, such as those between  $P_{\text{left}}$  and  $P_{\text{right}}$  is called a *span*. Delta

**Fig. 18.13** Rasterizing a triangle. Each vertex  $(V_0, V_1, \text{ and } V_2)$ , span endpoint  $(P_{\text{ielt}} \text{ and } P_{\text{right}})$ , and pixel  $(p_0, p_1, \text{ etc.})$  has z, R, G, and B components.

values for incrementing z, R, G, and B from pixel to pixel within the span are then calculated from the values at  $P_{\text{left}}$  and  $P_{\text{right}}$ .

**Span processing.** Operations that must be performed for each pixel within each span are performed here. For each pixel within the span, z, R, G, and B values are calculated by adding delta values to the values at the preceding pixel. The z value is compared with the previous z value stored at that location; if it is smaller, the new pixel value replaces the old one.

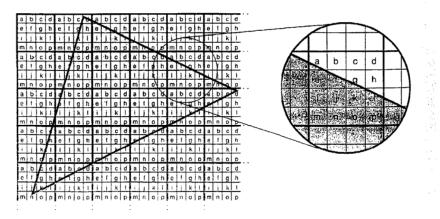

Fig. 18.14 A 4  $\times$  4 interleaved memory organization. Each memory partition ("a" through "p") contains one pixel from each 4  $\times$  4 block of pixels.

18.7

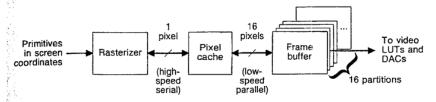

Fig. 18.15 A pixel cache matches bandwidth between a high-speed serial link to the rasterizer and a low-speed parallel link to the frame buffer.

A pipelined system containing one PE for each of the preceding three steps generates images dramatically faster than does a general-purpose display processor. In fact, it may generate pixels faster than a standard frame-buffer memory can handle. The Hewlett-Packard SRX [SWAN86], which uses this approach, generates up to 20 million pixels per second, approximately twice the speed of a typical VRAM memory system. In such systems, the rasterization bottleneck is access to frame-buffer memory.

**Pixel cache.** Pixels can be read and written faster if the frame buffer has some degree of parallel access. One way to accomplish this is to divide the memory into multiple—say, 16—partitions, each of which contains every fourth pixel of every fourth scan line, or perhaps every sixteenth pixel in every scan line (see Fig. 18.14). In this way, 16 pixels can be read or written in parallel. This technique, called *memory interleaving*, is also used in general-purpose CPU memory design.

A pixel register or pixel cache containing 16 pixels can be inserted between the rasterization pipeline and the interleaved image memory [GORI87; APGA88], as in Fig. 18.15. A cache allows the rasterizer to access individual pixels at high speed, assuming that the pixel is already in the cache. Multiple pixel values can be moved in parallel between the cache and the frame buffer at the slower speeds accommodated by the frame buffer.

As in any cache memory unit, performance depends on *locality of reference*, the principle that successive memory accesses are likely to occur in the same portion of memory. Erratic access patterns cause a high percentage of cache misses and degrade performance. For polygon rendering, the access pattern can be predicted precisely, since the extent of the polygon in screen space and the order in which pixels are generated are known before the pixels are accessed. Using this information, a cache controller can begin reading the next block of pixels from the frame buffer while the previous block of pixels is processed [APGA88].

Enhancing a rasterization subsystem with this kind of parallel-access path to frame-buffer memory may well increase the system throughput to the point where the bottleneck now becomes the single-pixel path between the rasterizer and the pixel cache. A logical next step is to enhance the rasterizer so that it can generate multiple pixel values in parallel. We consider such *image-parallel* architectures in Section 18.8.

#### 18.7.2 Pipelined Image-Order Architectures

The alternative to object-order rasterization methods is *image-order* (or *scan-line*) rasterization, introduced in Section 15.4.4. Scan-line algorithms calculate the image pixel by pixel, rather than primitive by primitive. To avoid considering primitives that do not

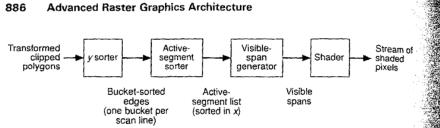

Fig. 18.16 Block diagram of a pipelined scan-line rasterizer.

contribute to the current scan line, most scan-line algorithms require primitives to be transformed into screen space and sorted into *buckets* according to the first scan line in which they each appear.

Scan-line algorithms can be implemented in hardware using the same approach as object-order algorithms: by casting the steps of the software algorithm into a pipelined series of hardware units. Much of the pioneering work on hardware scan-line systems was done at the University of Utah in the late 1960s [WYLI67 ROMN69; WATK70].

Figure 18.16 is a block diagram of a typical scan-line rasterizer. The y sorter places each edge of each polygon into the bucket corresponding to the scan line in which it first appears. The active-segment generator reads edges from these buckets, maintaining a table of active edges for the current scan line. From this table, it builds a list of active segments (a segment is a span within a single polygon), which is sorted by the x value of the left endpoint of each segment. The visible-span generator (called the depth sorter in the Utah system) traverses the active segment list, comparing z values where necessary, and outputs the sequence of visible spans on the current scan line. The shader performs Gouraud shading on these spans, producing a pixel stream that is displayed on the video screen.

11.

Notice that no frame buffer is needed in this type of system, provided that the system can generate pixels at video rates. The original Utah scan-line system generated the video signal in real time for a modest number (approximately 1200) of polygons. However, since the rate at which pixels are generated depends on local scene complexity, a small amount of buffering—enough for one scan line, for example—averages the pixel rate within a single scan line. A double-buffered frame buffer allows complete independence of image-generation and image-display rates. This architecture was the basis of several generations of flight-simulator systems built by Evans & Sutherland Computer Corporation in the 1970s [SCHA83].

#### 18.7.3 Limits of Pipeline Rasterization and the Need for Parallelism

Two factors limit the speedup possible in a pipeline approach. First, most rasterization algorithms break down easily into only a small number of sequential steps. Second, some of these steps are performed far more often than are others, particularly the steps in the inner loop of the rasterization algorithm. The processor assigned to these steps, therefore, becomes the bottleneck in the system.

The inner loop in an object-order (z-buffer) system is calculating pixels within spans; the inner loop in an image-order (scan-line) system is processing active edges on a scan line. For rasterization to be accelerated beyond the level possible by simple pipelining, these inner-loop calculations must be distributed over a number of processors. In z-buffer systems, this produces image parallelism; in scan-line systems, this produces object parallelism. The following two sections discuss each of these approaches. Virtually all of today's high-performance graphics systems use some variation of them.

#### 18.8 IMAGE-PARALLEL RASTERIZATION

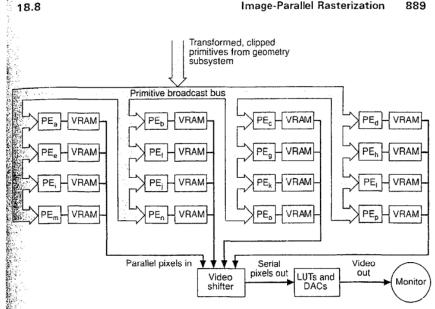

Image parallelism has long been an attractive approach for high-speed rasterization architectures, since pixels can be generated in parallel in many ways. Two principal decisions in any such architecture are (1) how should the screen be partitioned? (into rows? into columns? in an interleaved pattern?), and (2) how many partitions are needed? In the following sections, we shall describe the most heavily investigated alternatives, discussing the advantages and disadvantages of each. Also, we shall identify which schemes are approaching fundamental limits in current architectures. Note that, because an imageparallel system rasterizes in object order, a frame buffer is required to store intermediate results.

#### 18.8.1 Partitioned-Memory Architectures

Two obvious partitioning strategies are to divide pixels into contiguous blocks (Fig. 18.17a) [PARK80] and to divide them into an interleaved checkerboard pattern (Fig. 18.17b) [FUCH77a]. In either approach, a processor (or PE) is associated with each frame-buffer partition. Such organizations increase a graphics system's computation power by providing parallel processing, and its memory bandwidth by providing each PE with a separate channel into its portion of frame-buffer memory. During rasterization, polygons are transferred from the front end to the PEs in parallel, and each PE processes primitives in its portion of the frame buffer.

**Contiguous partitioning.** In the contiguous-region partitioning scheme, primitives need to be processed in only those regions in which they may be visible. These regions can be determined rapidly using geometric extents. If primitives are small compared to the region size, each primitive is likely to fall into a single region. Large primitives may fall into

| er –     |                             |   |   |   |   |     |    | _ |   |   |   |   |   |     |

|----------|-----------------------------|---|---|---|---|-----|----|---|---|---|---|---|---|-----|

|          | ╒┼┼╤┼┼╤┼╌╤┼╴╡┥┫╼╌╎╼┽┥╎┥┥┍╴  | a | b | с | d | a   | b  | с | d | а | b | с | ď | ••• |

|          |                             | e | f | g | h | e   | f  | 9 | h | e | f | g | h |     |

|          |                             | i | j | k | 1 | i i | j  | k | Γ | í | j | k | 1 |     |

|          | PEa PEb                     | m | n | 0 | р | m   | n  | 0 | р | m | n | 0 | Р |     |

|          |                             | a | b | с | d | а   | b  | с | d | а | b | с | d |     |

| ta<br>La | ┝┿┿┿┿╪┿╌┊┾╌┽┙╎╞┽┫┥╋┽╎┾┽┿┼┾╼ | e | f | g | h | е   | f  | g | h | е | f | g | h |     |

|          |                             | i | i | k | 1 | i   | j  | k | 1 | ì | j | k | 1 |     |

|          |                             | m | n | 0 | р | m   | п  | 0 | p | m | п | 0 | р |     |

|          |                             | ÷ |   |   |   |     |    |   |   | : |   |   |   |     |

|          | (a)                         |   |   |   |   |     | (b | ) |   |   |   |   |   |     |

Fig. 18.17 Two schemes for frame-buffer partitioning. In (a), processors are assigned contiguous blocks of pixels: in (b), processors are assigned pixels in an interleaved pattern.

18.8

multiple regions. If the region size is chosen appropriately, the number of primitives handled by each processor will be approximately m/p, where *m* is the number of primitives in the database and *p* is the number of processors. Note, however, that if the viewpoint is chosen so unfortunately that all of the primitives fall into a single screen region, one processor must rasterize all of the primitives, and system performance decreases dramatically. In a contiguous region system, the frame rate is determined by the number of primitives in the busiest region.

Interleaved partitioning. Interleaved partitioning, on the other hand, achieves a better balance of workload, since all but the tiniest polygons lie in all partitions of the frame buffer. Since each processor handles every primitive (although only a fraction of its pixels), this scheme is less efficient in the best case than is the contiguous region approach. However, its worst-case performance is much improved, since it depends on the *total* number of primitives, rather than on the number in the busiest region. Because of this intrinsic load balancing, interleaved systems have become the dominant partitioned memory architecture.

The polygon scan-conversion algorithm described in Section 18.7.1 requires set-up calculations to determine delta values and span endpoints before pixel computations can begin. These calculations need be performed only once per polygon or once per span, and can be shared among a number of PEs. The first proposed interleaved memory architectures [FUCH77a; FUCH79] contained no provision for factoring out these calculations from the PEs (see Fig. 18.18). Since each PE had to perform the entire rasterization algorithm for every polygon, many redundant calculations were performed.

Clark and Hannah [CLAR80] proposed an enhancement of this architecture to take advantage of calculations common to multiple PEs. In their approach, two additional levels of processors are added to perform polygon and edge processing. A single polygon a processor receives raw transformed polygon data from the front-end subsystem and determines the polygon's initial scan line, slopes of edges, and so on. Eight edge processors (one per column in an  $8 \times 8$  grid of pixel processors) calculate x, z, R, G, and B values at span endpoints. The edge processors send span information to the individual PEs (span processors), which interpolate pixel values along the span. The added levels of processing allow the PEs to perform only the calculations that are necessary for each pixel—a large improvement in efficiency. The rasterization portion of Silicon Graphics' recent highperformance systems uses this approach (see Section 18.8.2).

**SIMD versus MIMD.** A variation between systems of this type is whether PEs are SIMD or MIMD. Let us consider SIMD processors first. Figure 18.14 shows the mapping of processors to pixels in a  $4 \times 4$  interleaved scheme. With a SIMD processor, the 16 PEs work on a contiguous  $4 \times 4$  block of pixels at the same time. This arrangement is sometimes called a *footprint processor* because the  $4 \times 4$  array of processors (the footprint) marches across the polygon, stamping out 16 pixels at a time. Notice that, if any pixel of a  $4 \times 4$  block needs updating, the footprint must visit that block. For example, in the block of pixels shown in the inset of Fig. 18.14, processors *a*, *b*, *c*, *d*, *g*, and *h* must disable themselves, while processors *c*, *f*, *i*, *j*, *k*, *l*, *m*, *n*, *o*, and *p* process their respective pixels.

A disadvantage of SIMD processors is that they do not utilize their PEs fully. This occurs for two reasons. First, many of the PEs map to pixels outside the current primitive if

#### 889 Image-Parallel Rasterization

Fig. 18.18 Block diagram of a typical interleaved memory system. Each PE is responsible for one pixel in every  $4 \times 4$  block of pixels.

small primitives are being rendered. For example, PEs in a  $4 \times 4$  footprint processor rasterizing 100-pixel polygons map to pixels within the triangle as little as 45 percent of the time [APGA88]. Second, the choice of rasterization algorithm affects PE utilization. As remarked in Section 18.4.2, algorithms containing few conditional branches (including rasterizing convex polygons with Gouraud shading) can be implemented quite efficiently. Algorithms containing many conditional branches or using complicated data structures (such as rendering curved-surface primitives, texturing, shadowing, or antialiasing with a list of partially covering polygons) can be extremely difficult to make efficient. SIMD processors, however, can be built inexpensively and compactly, since a single code store and controller suffice for all the PEs. This offsets to some degree the poor PE utilization in a SIMD system. Several SIMD interleaved memory systems have been proposed and developed, including Gupta and Sproull's 8 by 8 Display [GUPT81b] and Stellar's GS2000 (see Section 18,11,3).