## (12) United States Patent

Owen et al.

#### (54) ELECTRONIC SYSTEM AND METHOD FOR SELECTIVELY ALLOWING ACCESS TO A SHARED MEMORY

(71) Applicant: STMicroelectronics, Inc., Coppell, TX

(72) Inventors: Jefferson Eugene Owen, Fremont, CA (US); Raul Zegers Diaz, Palo Alto, CA

(US); Osvaldo Colavin, Tucker, GA

Assignee: STMicroelectronics, Inc., Coppell, TX

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 13/655,152

(22)Filed: Oct. 18, 2012

(65)**Prior Publication Data**

> US 2013/0042072 A1 Feb. 14, 2013

#### Related U.S. Application Data

Continuation of application No. 13/239,200, filed on Sep. 21, 2011, now Pat. No. 8,314,808, which is a

(Continued)

(51) Int. Cl.

G06F 13/18 (2006.01)G06F 15/167 (2006.01)

(52)U.S. Cl. USPC ...... 345/535; 345/541

Field of Classification Search USPC ...... 345/541, 535, 542, 547, 555 See application file for complete search history.

(10) **Patent No.:**

(56)

(45) **Date of Patent:**

#### References Cited U.S. PATENT DOCUMENTS

4,257,095 A 3/1981 Nadir ...... 710/119 4,774,660 A 9/1988 Conforti ...... 364/200 (Continued)

US 8,681,164 B2

\*Mar. 25, 2014

#### FOREIGN PATENT DOCUMENTS

CA2100700 1/1995 DE 69631364 11/2004

(Continued)

OTHER PUBLICATIONS Accelerated Graphics Port Interface Specification, Revision 1.0, Intel Corporation, Jul. 31, 1996.\*

(Continued)

Primary Examiner — Hau Nguyen

(74) Attorney, Agent, or Firm — Seed IP Law Group PLLC

#### (57)ABSTRACT

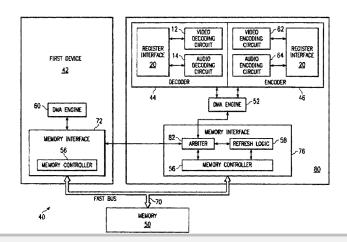

An electronic system, an integrated circuit and a method for display are disclosed. The electronic system contains a first device, a memory and a video/audio compression/decompression device such as a decoder/encoder. The electronic system is configured to allow the first device and the video/ audio compression/decompression device to share the memory. The electronic system may be included in a computer in which case the memory is a main memory. Memory access is accomplished by one or more memory interfaces, direct coupling of the memory to a bus, or direct coupling of the first device and decoder/encoder to a bus. An arbiter selectively provides access for the first device and/or the decoder/encoder to the memory based on priority. The arbiter may be monolithically integrated into a memory interface. The decoder may be a video decoder configured to comply with the MPEG-2 standard. The memory may store predicted images obtained from a preceding image.

#### 17 Claims, 6 Drawing Sheets

#### Related U.S. Application Data

(63) continuation of application No. 13/015,385, filed on Jan. 27, 2011, now Pat. No. 8,054,315, which is a continuation of application No. 12/857,455, filed on Aug. 16, 2010, now Pat. No. 7,898,548, which is a continuation of application No. 12/424,389, filed on Apr. 15, 2009, now Pat. No. 7,777,753, which is a continuation of application No. 11/956,165, filed on Dec. 13, 2007, now Pat. No. 7,542,045, which is a continuation of application No. 10/174,918, filed on Jun. 19, 2002, now Pat. No. 7,321,368, which is a continuation of application No. 09/539,729, filed on Mar. 30, 2000, now Pat. No. 6,427,194, which is a continuation of application No. 08/702,910, filed on Aug. 26, 1996, now Pat. No. 6,058,459.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4.894.565 A   | 1/1990  | Marquardt 307/518          |

|---------------|---------|----------------------------|

| 5,027,400 A   | 6/1991  | Baji et al 380/20          |

| 5,212,742 A   | 5/1993  | Normile et al              |

| 5,250,940 A   | 10/1993 | Valentaten et al 345/189   |

| 5,363,500 A   | 11/1994 | Takeda                     |

| 5,371,893 A   | 12/1994 | Price et al                |

| 5,450,542 A   | 9/1995  | Lehman et al 395/162       |

| 5,459,519 A   | 10/1995 | Scalise et al 348/431.1    |

| 5,461,679 A   | 10/1995 | Normile et al              |

| 5,522,080 A   | 5/1996  | Harney                     |

| 5,546,547 A * | 8/1996  | Bowes et al 710/114        |

| 5,557,538 A   | 9/1996  | Retter et al               |

| 5,576,765 A   | 11/1996 | Cheney et al 348/407       |

| 5,579,052 A   | 11/1996 | Artieri                    |

| 5,590,252 A   | 12/1996 | Silverbrook                |

| 5,598,525 A   | 1/1997  | Nally et al 395/520        |

| 5,621,893 A   | 4/1997  | Joh                        |

| 5,623,672 A   | 4/1997  | Popat                      |

| 5,682,484 A   | 10/1997 | Lambrecht 710/128          |

| 5,748,203 A   | 5/1998  | Tang et al 345/521         |

| 5,771,358 A * | 6/1998  | LaBerge 710/107            |

| 5,774,206 A   | 6/1998  | Wasserman et al 395/200.77 |

| 5,774,676 A   | 6/1998  | Stearns et al 709/247      |

| 5,778,096 A   | 7/1998  | Stearns 382/233            |

| 5,793,384 A   | 8/1998  | Okitsu 345/535             |

| 5,797,028 A   | 8/1998  | Gulick et al 395/800.32    |

| 5,805,921 A * | 9/1998  | Kikinis et al 710/2        |

| 5,809,245 A   | 9/1998  | Zenda 345/204              |

| 5,809,538 A   | 9/1998  | Pollmann et al 711/151     |

| 5,812,789 A   | 9/1998  | Diaz et al 709/247         |

| 5,812,800 A * | 9/1998  | Gulick et al 710/306       |

| 5,815,167 A   | 9/1998  | Muthal 345/541             |

| 5,835,082 A   | 11/1998 | Perego 345/202             |

| 5,912,676 A   | 6/1999  | Malladi et al 345/521      |

| 5,923,665 A   | 7/1999  | Sun et al 370/477          |

| 5,936,616 A   | 8/1999  | Torborg, Jr. et al 345/202 |

| 5,960,464 A   | 9/1999  | Lam 711/202                |

| 5,977,947 A * | 11/1999 | Potu 345/660               |

| 6,058,459 A   | 5/2000  | Owen et al 711/151         |

| 6,297,832 B1  | 10/2001 | Mizuyabu et al 345/540     |

| 6,330,644 B1  | 12/2001 | Yamashita et al 711/147    |

|               |         |                            |

#### FOREIGN PATENT DOCUMENTS

| EP | 0 639 032 | 7/1994 |

|----|-----------|--------|

| EP | 0 673 171 | 9/1995 |

| EP | 0 495 574 | 3/1997 |

| EP | 0827110   | 3/1998 |

| EP | 0827348   | 3/1998 |

| EP | 0 710 029 | 3/2002 |

| EP | 0772159   | 1/2004 |

| FR | 2740583   | 4/1997 |

| JP | 06-030442 | 2/1994 |

| JP | 08-018953 | 1/1996 |

|----|-----------|--------|

| JP | 10-108117 | 4/1998 |

| JP | 10-145739 | 5/1998 |

| WO | 96/20567  | 7/1996 |

#### OTHER PUBLICATIONS

Ackland, "The Role of VLSI in Multimedia," *IEEE Journal of Solid-State Circuits*, Apr. 1994, vol. 29, No. 4, pp. 381-388.

Adam et al, "The Vidboard: A Video Capture and Processing Peripheral for a Distributed Multimedia System," *ACM Multimedia*, Aug. 1-6, 1993, vol. 5, No. 2, pp. 113-120.

Adiletta, et al., "Architecture of a Flexible Real-Time Video Encoder/Decoder: The DECchip 21230," *Multimedia Hardware Architectures 1997*, Feb. 12-13, 1997, vol. 3021, pp. 136-148.

Apple Macintosh Quadra 840AV when executing the "Fusionrecorder 1.0" application as described in the 1993 Developer Note entitled Macintosh Quadra 840AV and Macintosh Centris 660AV Computers.

Araki, et al., "Video DSP Architecture for MPEG2 CODEC," ICASSP-94  $S_2AUVN$ , Speech Processing 2, Audio, Underwater Acoustics, VLSI & Neural Networks, Apr. 19-22, 1994, vol. 2, pp. 417-420.

Bailey et al., "Programmable Vision Processor/Controller for Flexible Implementation of Current and Future Image Compression Standards," *IEEE Micro*, Oct. 1992, pp. 33-39.

Bao et al., "OCP\_A: An Efficient QoS Control Scheme for Real Time Multimedia Communications," *IEEE Global Telecommunications Conference*, Conference Record, Nov. 3-8, 1997, vol. 2 of 3, pp. 741, 745

Baugher, "The OS/2 Resource Reservation System," *Multimedia Computing and Networking 1995*, Feb. 1995, vol. 2417, pp. 167-176. Baum et al., "A Multimedia Chipset for Consumer Audio-Visual Applications," *IEEE Transactions on Consumer Electronics*, Aug. 1997, vol. 43, No. 3, pp. 646-648.

Bhaskaran et al., "Multimedia Architectures: From Desktop Systems to Portable Appliances," *Multimedia Hardware Architectures 1997*, Feb. 12-13, 1997, vol. 3021, pp. 14-25.

Bhed et al., "A High-Performance Cross-Platform MPEG Decoder," Digital Video Compression on Personal Computers: Algorithms and Technologies, SPIE Proceedings, Feb. 7-8, 1994, vol. 2187, pp. 241-

Bonannon et al., "The Architecture of the Dali Main-Memory Storage Manager," *Multimedia Tools and Applications*, 1997, vol. 4, pp. 115-151.

Bouville et al., "DVFLEX: A Flexible MPEG Real Time Video CODEC," *International Conference on Image Processing*, Sep. 16-19, 1996, vol. II of III, pp. 829-832.

Bove, Jr., "The Impact of New Multimedia Representations on Hardware and Software Systems," *Multimedia Hardware Architectures* 1997, Feb. 12-13, 1997, vol. 3021, pp. 34-39.

Brahmbatt, "A VLSI Architecture for Real Time Code Book Generator and Encoder of a Vector Quantizer," *International Conference on Image Processing*, IEEE Signal Processing Society, vol. 2, Sep. 16-19, 1996, pp. 991-994.

Bursky, "Codec Compresses Images in Real Time: Real-Time Motion Video or Still Images Can be Compressed with Single-Chip Multistandard Core," *Electronic Design*, Oct. 3, 1993.

Bursky, "Highly Integrated Controller Eases MPEG-2 Adoption," *Electronic Design*, vol. 43, No. 17, pp. 141-142, Aug. 21, 1995.

Bursky, "Performing Over 8 BOPS, A Two Chip Set Can Compress or Expand Video in Real Time Image Processing Chip Set Handles Full Motion Video," *Electronic Design*, May 3, 1993.

Butler et al., "The Great Leap Forward," *PC Magazine*, pp. 241-244, 246, 248, 250, 253-254, 256, 260-261, 264, 266-268, 273-275, 278, Oct. 11, 1994.

C-Cube CL450 MPEG Video Decoder ("CL450") as described in the "CL450 MPEG Decoder User's Manual," C-Cube Microsystems, Milpitas, CA 1992 (MOT-S 721789-721874). Chaddha et al., "A Real-Time Scalable Color Quantizer Trainer/

#### (56) References Cited

#### OTHER PUBLICATIONS

Chang et al., "Columbia's VoD and Multimedia Research Testbed with Heterogeneous Network Support," *Multimedia Tools and Applications*, 1997, vol. 5, pp. 171-184.

Chaudhry et al., "A Framework for Analysis of Guaranteed QOS Systems," *Video Techniques and Software for Full-Service Networks*, Nov. 21, 1996, vol. 2915, pp. 25-38.

Chen et al., "Video Encoder Architecture for MPEG2 Real Time Encoding," *IEEE Transactions Consumer Electronics*, Aug. 1996, vol. 42, No. 3, pp. 290-299.

Cheng et al., "Disk Management for a Hard Real-Time File System," *Multimedia Systems*, vol. 4, No. 2, 1996, pp. 255-260.

Chiariglione, "MPEG: A Technological Basis for Multimedia Applications," *Multimedia*, Spring 1995, vol. 2, No. 1.

Choe et al., "ATM-Based Multi-Party Conferencing System," *IEEE Global Telecommunications Conference*, Nov. 1995, vol. 1 of 3, pp. 592-596.

Colaitis, "Opening Up Multimedia Object Exchange with MHEG," *Multimedia*, Summer 1994, vol. 2, No. 2.

Coulson et al., "The Design of a QoS-Controlled ATM-Based Communications System in Chorus," *IEEE Journal on Selected Areas in Communications*, May 1995, vol. 13, No. 4, pp. 686-699.

Deka, "A Comprehensive Study of Digital Signal Processing Devices," *Microprocessors and Microsystems*, May 1995, vol. 19, No. 4, pp. 209-221.

Demairy et al., "On the Correctness of Multimedia Applications," *The 11<sup>th</sup> Euromicro Conference on Real-Time Systems*, IEEE Computer Society, Jun. 9-11, 1999, pp. 226-233.

Doquilo "Symmetric Multiprocessing Servers: Scaling the Performance Wall," *Infoworld*, pp. 82-85, 88-92, Mar. 27, 1995.

Dusen et al., "From Concept to an Implementation," *International Broadcasting Convention*, Sep. 12-16, 1996.

Dutta et al., "VLSI Issues in Memory-System Design for Video Signal Processors," *IEEE* 1995, pp. 498-503.

Furht, "Multimedia Systems: An Overview," *Multimedia*, Sprin 1994, vol. 1, No. 1, pp. 47-59.

Furht, "Processor Architectures for Multimedia: A Survey," *Multimedia Modeling*, Nov. 17-20, 1997, pp. 89-109.

Galbi et al., "An MPEG-1 Audio/Video Decoder with Run-Length Compressed Antialiased Video Overlays," *IEEE International Solid State Circuits Conference*, pp. 286-287, 381, 1995.

Ganesan, "A Dual-DSP Microprocessor System for Real-Time Digital Correlation," *Microprocessors and Microsystems*, Sep. 1991, vol. 15, No. 7, pp. 29-37.

Ganesan, "A Dual-DSP Microprocessor System for Real-Time Digital Correlation," *Microprocessors and Microsystems*, vol. 15, No. 7, Sep. 1991, pp. 379-384.

Gass, "Architecture Trends of MPEG Decoders for Set-Top Box," *Multimedia Hardware Architectures 1997*, Feb. 12-13, 1997, vol. 3021, pp. 162-169.

Giorgis, "SMP Network Operating Systems," Computer Dealer News, vol. 12, No. 16, Aug. 8, 1996.

Goodenough et al., "A General Purpose, Single Chip Video Signal Processing (VSP) Architecture for Image Processing, Coding and Computer Vision," *IEEE* 1994, pp. 1-4.

Goodenough et al., "A Single Chip Video Signal Processing Architecture for Image Processing, Coding and Computer Vision," *IEEE Transaction on Circuits and Systems for Video Technology*, Oct. 1995, vol. 5, No. 5, pp. 436-445.

Gove et al., "Image Computing Requirements for the 1990s: From Multimedia to Medicine," *The International Society for Optical Engineering, Medical Imaging V: Image Capture, Formatting and Display*, Feb. 1991, vol. 1444, pp. 318-333.

Gove, "The MVP: A Highly-Integrated Video Compression Chip," DCC '94, Data Compression Conference, Mar. 29-31, 1994, pp. 215-224

Gruger et al., "MPEG-1 Low-Cost Encoder Solution," Europe Series, Advanced Image and Video Communications and Storage Technologies, Mar. 20-23, 1995, vol. 2451, pp. 41-51.

Guediri et al., "An Affordable Solution to Real-Time Video Compression," *Technical Conference, Session 10 Imaging & HDTV*, Mar. 8, 1995, pp. 261-265.

Guttag et al., "A Single-Chip Multiprocessor for Multimedia: The MVP," *IEEE Computer Graphics and Applications*, Nov. 1992, pp. 53-64.

Hoffner et al., "Communication between two microprocessors through common memory," *Microprocessors and Microsystems*, Jul./ Aug. 1982, vol. 6, No. 6, pp. 303-308.

Huang et al., "On Supporting Mission-Critical Multimedia Applications," *International Conference on Multimedia Computing and Systems*, Jun. 17-23, 1996, pp. 46-53.

Huang et al., "Resource Management for Continuous Multimedia Database Applications," *Real-Time Systems Symposium*, Dec. 7-9, 1994, pp. 46-54.

Huynh et al., "Performance Analysis of Advanced I/O Architectures for PC-based Video Servers," *Multimedia Systems*, vol. 2, No. 1, 1994, pp. 36-50.

Irvin et al., "A New Generation of MPEG-2 Video Encoder ASIC & ITS Application to New Technology Markets," *International Broadcasting Convention*, Sep. 12-16, 1996, Pub. No. 428.

Jain et al., "An Integrated Circuit Design for Pruned Tree Search Vector Quantization Encoding with an Off-Chip Controller," *IEEE Transactions on Circuit and Systems for Video Technology*, Jun. 1992, vol. 2, No. 2, pp. 147-158.

Kassim et al., "A DSP-Based Video Compression Test-Bed," *Micro-processors and Microsystems*, vol. 20, 1997, pp. 541-551.

Kanellopoulos et al., "The Comprehensive Approach of QOS and the Evolution of ACSE Protocols in Multimedia Communications," *Proceedings of the Third IEEE International Conference on Electronics, Circuits, and Systems*, Oct. 13-16, 1996, vol. 1, pp. 323-326.

Kettler et al., "Scheduling Analysis of the Micro Channel Architecture for Multimedia Applications," *International Conference on Multimedia Computing and Systems*, May 14-19, 1994, pp. 403-414.

Khayat et al., "A Proposed Bus Arbitration Scheme for Multimedia Workstations," *International Conference on Multimedia Computing and Systems*, May 14-19, 1994, pp. 415-423.

Kim et al., "A Real-Time MPEG Encoder Using a Programmable Processor," *IEEE*, 1994, pp. 161-170.

King, *Inside Windows 95*, Microsoft Press, Redmond Washington, pp. 85-90, 1994.

Kinugasa et al., "A Video Pre/Post-processing LSI for Video Capture," 1996 Digest of Technical Papers, Jun. 5-7, 1996, pp. 396-397. Kohiyama et al., "Architecture of MPEG-2 Digital Set-Top-Box for CATV Vod System," IEEE, 1996, pp. 667-672.

Koinuma et al., "ATM in B-ISDN Communication Systems and VLSI Realization," *IEEE Journal of Solid-State Circuits*, Apr. 1995, vol. 30, No. 4, pp. 341-347.

Kondo et al., "Two-Chip MPEG-2 Video Encoder," *IEEE Micro*, Apr. 1996, vol. 16, No. 2, pp. 51-58.

Lau et al., "A Novel Video-On-Demand Storage Architecture for Supporting Constant Frame Rate with Variable Bit Rate Retrieval," *Network and Operating Systems Support for Digital Audio and Video*, Apr. 19-21, 1995, pp. 294-305.

Lee et al., "MediaStation 5000: Integrating Video and Audio," *Multimedia*, Summer 1994, vol. 1, No. 2, pp. 50-61.

Lee et al., "Real-Time MPEG Video Compression Using the MVP," Data Compression Conference '94, Mar. 29-31, 1994.

Lin et al., "Low Power Design for MPEG-2 Video Decoder," *IEEE Transactions on Consumer Electronics*, Aug. 1996, vol. 42, No. 3, pp. 513-521.

Lin and Chein-WeiJen, "On the Bus Arbitration for MPEG2 Video Decoder," VLSI Tech, Systems and Appl. 1995 Symposium, pp. 201-205

Lin et al., "DMA-based Communications between PC and DSP,"

#### (56) References Cited

#### OTHER PUBLICATIONS

Lisa et al., "A Reconfigurable Coprocessor for a PCI-based Real Time Computer Vision System," *Field-Programmable Logic and Applications*, 7<sup>th</sup> International Workshop, FPL 1997, London, UK, Sep. 1-3, 1997, pp. 392-399.

Liu, "MPEG Decoder Architecture for Embedded Applications," *IEEE Transactions on Consumer Electronics*, Nov. 1996, vol. 42, No. 4, pp. 1021-1028.

Majeed, "Dual Processor Automotive Controller," *IEEE*, 1988, pp. 39-44

Maturi, "Single Chip MPEG Audio Decoder," *IEEE Transactions on Consumer Electronics*, vol. 38, No. 3, pp. 348-356, Aug. 1992.

Matsuo et al., "A Programmable Video Codec System for Low-Bit-Rate Communication," *IEEE Transactions on Consumer Electronics*, Aug. 1997, vol. 43, No. 3, pp. 903-910.

Miura et al., "A 600 mW Single Chip MPEG2 Video Decoder," *IEICE Trans. Electrono*, Dec. 1995, vol. E78-C, No. 12, pp. 1691-1696.

Morton, "A236 Parallel DSP Chip Provides Real-Time Video Processing Economically and Efficiently," *Electro '96 Professional Program Proceedings*, Apr. 30-May 2, 1996, pp. 261-268.

"MPEG Video Överview," SGS-Thomson Microelectronics Technical Note, pp. 1-4, 1992.

Ng et al., "An analysis of buffer sharing and prefetching techniques for multimedia systems," *Multimedia Systems*, vol. 4, No. 2, 1996, pp. 55-69.

Ngai et al., "A Scalable Chip Set for MPEG2 Real-Time Encoding," *CompCon*, 1996, pp. 193-198.

Ngoh et al., "On Storage Server Issues for Multimedia-on-Demand System," *Multimedia Modeling*, Nov. 1995, pp. 393-409.

Oliver et al., "Distributed Connection Management for Real-Time Multimedia Services," From Multimedia Services to Network Services, Dec. 1997, pp. 59-74.

Ooi et al., "A PC-Based MPEG Compressed Data Decoder," *IEEE Transactions on Consumer Electronics*, Nov. 1995, vol. 41, No. 4, pp. 1169-1173.

Ooi et al., "An MPEG-2 Encoder Architecture Based on a Single Chip Dedicated LSI with a Control MPU," *IEEE*, 1997, pp. 599-602.

Ozden et al., "On the Design of a Low-Cost Video-on-Demand Storage System," *IEEE Journal of Solid State Circuits*, Apr. 1994, vol. 29, No. 4, pp. 40-54.

Shah, "Multimedia on the Internet," *The Twentieth Annual International Computer Software & Applications Conference*, Aug. 21-23, 1996, p. 150.

Pancha et al., "Bandwidth-Allocation Schemes for Variable-Bit-Rate MPEG Sources in ATM Networks," *IEEE Transactions on Circuits and Systems for Video Technology*, Jun. 1993, vol. 3, No. 3, pp. 190-198.

Pillai, "Multimedia Over the Internet," *The Twentieth Annual International Computer Software & Applications Conference*, Aug. 21, 23, 1996, p. 149.

Pirsch et al., "Architectural Approaches for Multimedia Processors," *Multimedia Hardware Architectures 1997*, Feb. 12-13, 1997, vol. 3021, pp. 2-13.

Pirsch et al., "VLSI Architectures for Video Compression—A Survey," *Proceedings of the IEEE*, Feb. 1995, vol. 83, No. 2, pp. 220-246. Pirsch et al., "VLSI Architectures for Video Signal Processing," *Image Processing and its Applications*, Jul. 4-6, 1995, Conference Publication No. 410, pp. 6-10.

Plansky, "Variable Block-Size Vector Quantization in the Transform Domain," *Signal Processing VI Theories and Applications*, vol. III, 1992, pp. 1243-1246.

Rangan et al., "Designing an On-Demand Multimedia Service," *IEEE Communications Magazine*, Jul. 1992, vol. 30, No. 7, pp. 56-64.

Reddaway, "Fractal Graphics and Image Compression on a DAP," *The Design and Application of Parallel Digital Processors*, Apr. 11-15, 1988, p. 201.

Richard et al., "The Washington University Broadband Terminal,"

Richard et al., "The Washington University Multimedia System," *Multimedia Systems*, vol. 1, No. 3, 1993, pp. 120-131.

Rooholamini et al., "ATM-Based Multimedia Servers," *Multimedia*, Spring 1995, vol. 2, No. 1, pp. 39-52.

Russell, "The Challenge of VLSI Technology to Low-bit-rate Video," *International Symposium on VLSI Technology Systems and Applications*, IEEE, Taipei, Taiwan, May 17-19, 1989, 164-168.

Sabaa et al., "Design and Modelling of a Nonblocking Input Buffer ATM Switch," Can. J. Elect. & Comp. Eng., vol. 22, Nov. 3, 1997, pp. 87-93

Seed et al., "An Enhanced Transputer Module for Real-Time Image Processing," *Third International Conference on Image Processing*, 1989, pp. 131-135.

Shah, "Multimedia on the Internet," *The Twentieth Annual International Computer Software & Applications Conferences*, COMPSAC '96, Aug. 21-23, 1996, p. 150.

Shepherd et al., "Quality-of-Service Support for Multimedia Applications," *Multimedia*, Fall 1996, vol. 3, No. 3, pp. 78-82.

Sriskanthan et al., "A Real-Time PC-Based Video Phone System on ISDN/Lan," *IEEE Transactions on Consumer Electronics*, May 1995, vol. 41, No. 2, pp. 332-342.

Stirpe et al., "Application Migration to Reserved Bandwidth Networks," *Multimedia Computing and Networking 1995*, Feb. 1995, vol. 2417, pp. 428-434.

Tamitani et al., "An Encoder/Decoder Chip Set for the MPEG Video Standard," *IEEE International Conference on Acoustics, Speech and Signal Processing*, Mar. 23-26, 1992, pp. 661-664.

The Motorola MCD212 Video Decoder and System Controller ("MCD212")(as described in the Advance Information manual, published in the U.S. Aug. 1995, at MOT-S 723153-723240).

Tiwari et al., "A Parallel MPEG-2 Video Encoder with Look-Ahead Rate Control," *The 1996 IEEE International Conference on Acoustics, Speech, and signal Processing Conference*, May 7-10, 1996, pp. 1994-1997.

Tobagi et al., "Streaming RAID—A Disk Array Management System for Video Files," ACM Multimedia 93, Aug. 1-6, 1993, pp. 393-400. Tsang et al., "A VLSI Architecture for a Real-Time Code Book Generator and Encoder of a Vector Quantizer," IEEE Transactions on a Joint Publication of IEEE Circuits and Systems Society, the IEEE Computer Society, the IEEE Solid-State Circuits Council, Sep. 1994, vol. 2, No. 3, pp. 360-364.

Undy et al., "A low-cost graphics and multimedia workstation chip set," *IEEE Micro*, vol. 14, No. 2, Apr. 1994, pp. 10-22.

Uramoto et al., "An MPEG2 Video Decoder LSI with Hierarchical Control Mechanism," *IEEE 1997 Custom Integrated Circuits Conference*, Apr. 26, 1995, pp. 1697-1708.

U.S. District Court, Eastern District of Texas Live (Sherman), Civil Docket for Case #: 4:03-cv-00276-LED, STMicroelectronics, Inc., Plaintiff v. Motorola, Inc., and Freescale Semiconductor, Inc., Defendants, Counterclaim Plaintiffs v. STMicroelectronics N.V., and STMicroelectronics, Inc., Counterclaim Defendants, date filed Jul. 18, 2003, 47 pages.

Verscheure et al., "Perceptual Video Quality and Activity Metrics: Optimization of Video Service Based on MPEG-2 Encoding," *Multimedia Telecommunications and Applications*, Nov. 1996, pp. 249-265

Video Electronics Standards Association, "VESA Unified Memory Architecture Hardware Specifications Proposal," Version: 1.0p, pp. 1-38, Oct. 31, 1995.

Video Electronics Standards Association, VESA Unified Memory Architecture VESA BIOS Extensions (VUMA-SBE Proposal), Version 1.0p, pp. 1-26, Nov. 1, 1995.

Vogel et al., "Distributed Multimedia and QOS: A Survey," *Multimedia*, Summer 1995, vol. 2, No. 2, pp. 10-19.

Williams et al., "A Programmable Solution for Standard Video Compression," in *IEEE Computer Society Press*, Thirty-Seventh IEEE Computer Society International Conference, San Francisco, CA, Feb. 24-28, 1992, pp. 47-50.

Winzker et al., "Architecture and Memory Requirements for Stand-Alone and Hierarchical MPEG2 HDTV-Decoders with Synchronous

#### (56) References Cited

#### OTHER PUBLICATIONS

Wolfe et al., "Design Methodology for Programmable Video Signal Processors," *Multimedia Hardware Architectures 1997*, Feb. 12-13, 1997, vol. 3021, pp. 26-31.

Wolfe et al., "Concepts for Resource Reservation in Advance," *Multimedia Tools and Applications*, 1997, pp. 255-278.

Wong et al., "The H-Bus: A Media Acquisition Bus Optimized for Multiple Streams," *Multimedia Hardware Architectures 1997*, Feb. 12-13, 1997, vol. 3021, pp. 40-50.

Wrege et al., "Video Traffic Characterization for Multimedia Networks with a Deterministic Service," *IEEE Inforcom* '96, Mar. 1996, vol. 2, pp. 537-544.

Wu et al., "A Function-Pipelined Architecture and VLSI Chip for MPEG Video Image Coding," *IEEE Transactions on Consumer Electronics*, Nov. 1995, vol. 41, No. 4, pp. 1127-1137.

Yamada et al., "Real-time MPEG2 Encoding and Decoding with a Dual-Issue RISC Processor," *Proceedings of the IEEE 1997 Custom Integrated Circuits Conference*, May 5-8, 1997, pp. 225-228.

Yamazaki et al., "ATM Networking and Video-Coding Techniques for QOS Control in B-ISDN," *IEEE Transactions on Circuits and Systems for Video Technology*, Jun. 1993, vol. 3, No. 3, pp. 175-181. Yoshimoto et al., "ULSI Realization of MPEG2 Realtime Video Encoder and Decoder—An Overview," *IEICE Trans. Electron*, May 23, 1995, vol. E78-C, No. 12, pp. 1668-1681.

Yu et al., "Resource Management Issues of a Video Server," *Multimedia Storage and Archiving Systems*, Nov. 18-19, 1996, vol. 2916, pp. 290-300.

Zahir et al., "VBR MPEG-2 Encoded Video Over Broadband Network," *Proceedings of SPIE*, Nov. 3-5, 1997, vol. 3231, pp. 372-381. Zhang et al., "Red-VBR: A New Approach to Support Delay-Sensitive VBR Video in Packet-Switched Networks," *Network and Operating System Support for Digital Audio and Video*, Apr. 19-21, 1995, pp. 258-272.

Hsing, "The Challenge of VLSI Technology to Low-Bit Rate Video," VLSI Technology, Systems and Applications, 1989. Proceedings of Technical Papers. 1989 International Symposium on May 17-19, 1989, pp. 164-168.

\* cited by examiner

# DOCKET

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

### **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.