VUMA Proposed Stanc 1

ESA Confidential

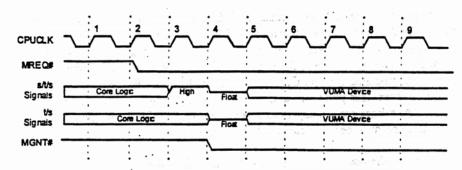

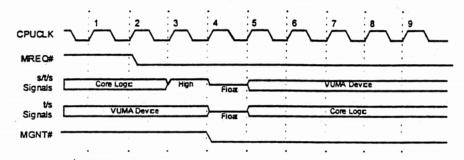

MREQ# is driven low from clock edge 2. Core logic samples it active on clock edge 3. Arbiter can give the bus right away, so core logic drives all s/t/s signals high from the same clock edge. Core logic tri-states all the shared signals (s/t/s and t/s) and drives MGNT# active from clock edge 4. VUMA device samples MGNT# active at clock edge 5 and starts driving the bus from the same edge.

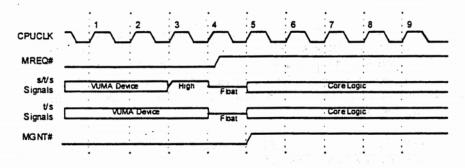

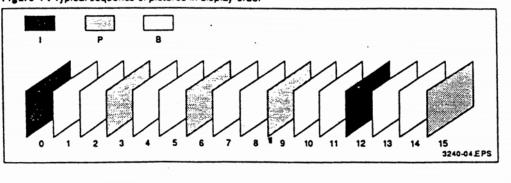

The shared DRAM signals are driven by VUMA device when it is the owner of the physical system memory bus. VUMA device relinquishes the physical system memory bus by de-asserting MREQ#. Bus Arbiter gives the bus back to core logic by de-asserting MGNT#. Also, as mentioned above, before core logic starts driving the bus, VUMA device should drive the s/t/s signals high for one CPUCLK clock and tri-state them. VUMA device should also tri-state all the shared t/s signals. The float condition on the bus should be for one CPUCLK clock, before core logic starts driving the bus. These activities are overlapped to improve performance as shown in Figure 5-6.

Figure 5-6 Bus hand off from VUMA device to core logic

VUMA device drives all s/t/s signals high from clock edge 3. VUMA device tri-states all shared signals (s/t/s and t/s) and de-asserts MREQ# from clock edge 4. Core logic samples MREQ# inactive on clock edge 5. Core logic drives all shared signals and deasserts MGNT# from clock edge 5.

### 5.3.2 DRAM Precharge

25

When the physical system memory bus is handed off from core logic to VUMA device or vice a versa, the DRAM needs to be precharged before the new master starts driving it. Part of this precharge can be hidden by overlapping with the arbitration protocol. As shown in Figure 5-5 and 5-6, all the DRAM control signals (including RAS# lines) are driven high for and tri-stated for one CPUCLK clock each. When RAS# lines are tri-stated, pull ups on those lines pull them to a logical high. Thus when a new master gets the control, the RAS# lines are already been precharged for two CPUCLK clocks. The rest of the precharge needs to be taken care by the new master.

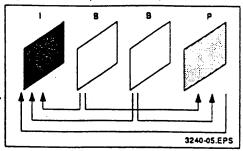

1. VUMA device gets the bus from core logic - As shown in Figure 5-5, when VUMA device gets the physical system memory bus at clock edge 5, the DRAM has been precharged for two CPUCLK clocks. VUMA device needs to take care of the rest of the DRAM precharge. This precharge can be overlapped by VUMA device over some of its activity e.g. VUMA device may be running at a different clock than the CPUCLK clock and the precharge can be overlapped with the synchronization of MGNT# signal. VUMA device can calculate the number of clocks it needs to precharge the DRAM with the following formula:

No. of VUMA device clocks for DRAM precharge = {RAS# Precharge Time (tRP) - (2 \* CPUCLK Clock Time Period)}/ VUMA device Clock Time Period

Example: CPU running at 66.66 MHz, VUMA device running at 50 MHz. 70ns Fast Page DRAM used.

No. of VUMA device clocks for DRAM precharge = {50ns - (2\* 15ns)}/ 20ns

= {20ns}/ 20ns = 1 clock

2. Core logic gets the bus from VUMA device - As shown in Figure 5-6, when core logic gets the physical system memory bus at clock edge 5, the DRAM has been precharged for two CPUCLK clocks. core logic needs to take care of the rest of the DRAM precharge. This precharge can be overlapped by core logic over some of its activity e.g. driving of new row address. Core logic can calculate the number of clocks it needs to precharge the DRAM with the following formula:

No. of CPU clocks for DRAM precharge = {RAS# Precharge Time (tRP) - (2 \* CPUCLK Clock Time Period)}/ CPUCLK Clock Time Period

Example: CPU running at 66.66 MHz, VUMA device running at 50 MHz. 70ns Fast Page DRAM used.

No. of CPU clocks for DRAM precharge = {50ns - (2\* 15ns)}/ 15ns

= {20ns}/15ns = 2 clock

26

#### VUMA Proposed Stanc J

#### /ESA Confidential

#### 5.4 Synchronous DRAM

Synchronous DRAM support is optional for both core logic and VUMA device. Various Synchronous DRAM support scenarios are as follows:

- Core logic does not support Synchronous DRAM Since core logic does not support. Synchronous DRAM, there would not be any Synchronous DRAM as the physical system memory and hence whether VUMA device supports Synchronous DRAM or not is irrelevant.

- 2. Core logic supports Synchronous DRAM When core logic supports Synchronous DRAM, VUMA device may or may not be supporting it. Whether core logic and VUMA device support Synchronous DRAM or not should be transparent to the operating system and application programs. To achieve the transparency, system BIOS needs to find out if both core logic and VUMA device support this feature and set the system appropriately at boot. The following algorithm explains how it can be achieved. The algorithm is only included to explain the feature. Refer to the latest VUMA VESA BIOS Extensions for the most updated BIOS calls:

a. Read <VUMA BIOS signature string (refer to VUMA VESA BIOS Extensions)>. Check if VUMA device supports Synchronous DRAM.

b. If VUMA device does not support Synchronous DRAM, do not assign Synchronous DRAM banks for Main VUMA Memory. Assign Main VUMA Memory to Fast Page Mode or EDO bank. Also, if Auxiliary VUMA Memory is assigned by operating system to Synchronous DRAM banks, do not use it. Either repeat the request for Auxiliary VUMA Memory till it is assigned to Fast Page Mode or EDO bank or use some alternate method.

c. If VUMA device supports Synchronous DRAM, read < VUMA BIOS signature string (refer to VUMA VESA BIOS Extensions)> to find out if VUMA device supports multiple banks access.

d. If only single bank access supported on VUMA device, exit, as the Main VUMA Memory and Auxiliary VUMA Memory bank is fixed.

e. If multiple banks access is supported and if the CS# for Synchronous DRAM bank is supported on VUMA device, assign the Main VUMA Memory to obtain the best possible system performance and exit.

#### **5.4.1 Programmable Parameters**

Synchronous DRAMs have various programmable parameters. Core logic programs Synchronous DRAM parameters to obtain the best possible results. The most efficient way for VUMA device to program its DRAM controller is to make a BIOS call to find

27

#### VUMA Proposed Sta ard

# **VESA Confidential**

out the parameters core logic has decided and program its DRAM controller with the same parameters. Alternately, VUMA device could program its DRAM controller with one or all different parameters. If VUMA device programs its DRAM controller with any different parameters, it is VUMA device's responsibility to reprogram Synchronous DRAM back with the original parameters, before the physical system memory bus is handed off to core logic. In other words, VUMA device is free to change any or all of the parameters, but the change should be transparent to core logic.

How core logic programs various parameters and how VUMA device could inquire them is as follows:

.1. Burst Length - Burst Length can be programmed as 1, 2 or 4. VUMA device needs to make a BIOS call <Return Memory Speed Type (refer to VUMA VESA BIOS Extensions)> to find out the Burst Length.

2. CAS Latency - As CAS latency depends on the speed of Synchronous DRAM used and the clock speed, this standard does not want to fix this parameter. Core logic programs this parameter to an appropriate value. VUMA device needs to make a BIOS call <Return Memory Speed Type (refer to VUMA VESA BIOS Extensions)> to find out the CAS latency.

3. Burst Ordering - Most efficient Burst Ordering depends upon the type of CPU used. VUMA device needs to make a BIOS call <Return Memory Speed Type (refer to VUMA VESA BIOS Extensions)> to find out the Burst Order.

#### 5.4.2 Protocol Description and Timing

All the DRAM signals are shared by core logic and VUMA device. They are driven by current bus master. When core logic and VUMA device hand over the bus to each other, they must drive all the shared s/t/s signals high for one CPUCLK clock and then tri-state them. Also, they should tri-state all the shared t/s signals.

Synchronous DRAMs are precharged by precharge command. When the physical system memory bus is handed off from core logic to VUMA device or vice a versa, the DRAM precharge has two options:

- 1. Precharge both the internal banks before hand-off This is a simple case where both the internal banks of the active synchronous DRAM bank are precharged and then the bus is handed off.

- 2. Requesting Master snoops the physical system memory bus and synchronous DRAM internal banks need not be precharged In this case the requesting master snoops the DRAM address and control signals to track the open pages in the internal banks of the active synchronous DRAM bank. The internal banks of the active synchronous DRAM

28

### VUMA Proposed Stanu

### /ESA Confidential

are not precharged when the physical system memory bus is handed-off to the requesting master. If needed, the requesting master takes care of precharge after getting the physical system memory bus.

Both core logic and VUMA device have an option of either implementing or not implementing DRAM snoop feature. Whether core logic and VUMA device support DRAM snoop or not should be transparent to the operating system and application programs. To achieve the transparency, system BIOS and VUMA BIOS need to find out if both core logic and VUMA device support this feature and set the system appropriately at boot. The following algorithm explains how it can be achieved. The algorithm is only included to explain the feature. Refer to the latest VUMA VESA BIOS Extensions for the most updated BIOS calls:

1. System BIOS reads <VUMA BIOS signature string (refer to VUMA VESA BIOS Extensions)>, to find out if VUMA device can snoop the physical system memory bus.

2. If no, System BIOS programs core logic to precharge synchronous DRAM before bus hand-off.

3. If yes, System BIOS programs core logic not to precharge synchronous DRAM before bus hand-off.

4. VUMA BIOS makes a call, <Report VUMA - core logic capabilities (refer to VUMA VESA BIOS Extensions)>, to find out if core logic can snoop the physical system memory bus.

5. If no, VUMA BIOS programs VUMA device to precharge synchronous DRAM before bus hand-off.

6. If yes, VUMA BIOS programs VUMA device not to precharge synchronous DRAM before bus hand-off.

None, only one, or both of core logic and VUMA device can support this feature. When only one of them supports this feature memory precharge will be asymmetrical i.e. there will be precharge before hand-off one way and no precharge the other way.

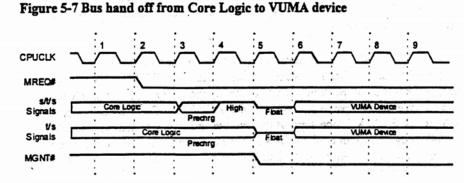

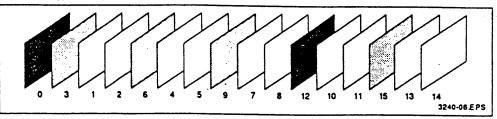

#### 5.4.2.1 Non-Snoop Cases

The shared DRAM signals are driven by core logic when it is the owner of the physical system memory bus. VUMA device requests the physical system memory bus by asserting MREQ#. Bus Arbiter grants the bus by asserting MGNT#. Also, before VUMA device starts driving the bus, core logic should drive all the shared s/t/s signals high for one CPUCLK clock and tri-state them. Core logic should also tri-state all the shared t/s signals. The tri-state condition on the bus should be for one CPUCLK clock, before VUMA device starts driving the bus. These activities are overlapped to improve performance as shown in Figure 5-7. Since VUMA device does not support DRAM snoop feature, DRAM is precharged before handing off the physical system memory bus as shown in Figure 5-7.

29

Version. 1.0p, Rev. 0.4p

Page 215 of 280

### VUMA Proposed Sta ard

#### **VESA Confidential**

MREQ# is driven low from clock edge 2. Core logic samples it active on clock edge 3. Arbiter can give the bus right away, so core logic gives precharge command to DRAM from the same clock edge. Core logic drives all the shared s/t/s signals high from clock edge 4. Core logic tri-states all the shared signals (s/t/s and t/s) and drives MGNT# active from clock edge 5. VUMA device samples MGNT# active at clock edge 6 and starts driving the bus from the same edge.

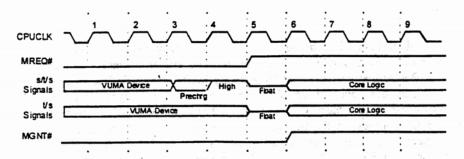

The shared DRAM signals are driven by VUMA device when it is the owner of the physical system memory bus. VUMA device relinquishes the physical system memory bus by de-asserting MREQ#. Bus Arbiter gives the bus back to core logic by de-asserting MGNT#. Also, as mentioned above, before core logic starts driving the bus, VUMA device should drive all the shared s/t/s signals high for one CPUCLK clock and tri-state them. VUMA device should also tri-state all the shared t/s signals. The float condition on the bus should be for one CPUCLK clock, before core logic starts driving the bus. These activities are overlapped to improve performance as shown in Figure 5-8. Since core logic does not support DRAM snoop feature, DRAM is precharged before handing off the physical system memory bus as shown in Figure 5-8.

#### Figure 5-8 Bus hand off from VUMA device to Core Logic

VUMA device gives precharge command from clock edge 3. It drives all shared s/t/s signals high from clock edge 4. It tri-states all shared signals (s/t/s and t/s) and de-asserts

30

Version. 1.0p, Rev. 0.4p

# Petitioners HTC & LG - Exhibit 1002, 1.216

#### VUMA Proposed Standz-1

MREQ# from clock edge 5. Core logic samples MREQ# inactive on clock edge 6. Core logic drives all shared signals and deasserts MGNT# from clock edge 6.

#### 5.4.2.2 Snoop Cases

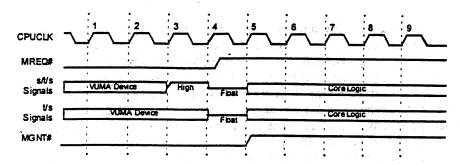

The shared DRAM signals are driven by core logic when it is the owner of the physical system memory bus. VUMA device requests the physical system memory bus by asserting MREQ#. Bus Arbiter grants the bus by asserting MGNT#. Also, before VUMA device starts driving the bus, core logic should drive all the shared s/t/s signals high for one CPUCLK clock and tri-state them. Core logic should also tri-state all the shared t/s signals. The tri-state condition on the bus should be for one CPUCLK clock, before VUMA device starts driving the bus. These activities are overlapped to improve performance as shown in Figure 5-9. Since VUMA device supports DRAM snoop feature, core logic does not precharge DRAM before handing off the physical system memory bus as shown in Figure 5-9.

#### Figure 5-9 Bus hand off from core logic to VUMA device

MREQ# is driven low from clock edge 2. Core logic samples it active on clock edge 3. Arbiter can give the bus right away and since VUMA device supports DRAM snoop feature, core logic drives all the shared s/t/s signals high from the same clock edge. Core logic tri-states all the shared signals (s/t/s and t/s) and drives MGNT# active from clock edge 4. VUMA device samples MGNT# active at clock edge 5 and starts driving the bus from the same edge.

The shared DRAM signals are driven by VUMA device when it is the owner of the physical system memory bus. VUMA device relinquishes the physical system memory bus by de-asserting MREQ#. Bus Arbiter gives the bus back to core logic by de-asserting MGNT#. Also, as mentioned above, before core logic starts driving the bus, VUMA device should drive all the shared s/t/s signals high for one CPUCLK clock and tri-state them. VUMA device should also tri-state all the shared t/s signals. The float condition on the bus should be for one CPUCLK clock, before core logic starts driving the bus. These activities are overlapped to improve performance as shown in Figure 5-10. Since core

31

Version. 1.0p, Rev. 0.4p

# Petitioners HTC & LG - Exhibit 1002, p. 217

### VUMA Proposed Stand

#### **VESA Confidential**

logic supports DRAM snoop feature, VUMA device does not precharge DRAM before handing off the physical system memory bus as shown in Figure 5-10.

Figure 5-10 Bus hand off from VUMA device to core logic

VUMA device drives all shared s/t/s signals high from clock edge 3. It tri-states all shared signals (s/t/s and t/s) and de-asserts MREQ# from clock edge 4. Core logic samples MREQ# inactive on clock edge 5. Core logic drives all shared signals and deasserts MGNT# from clock edge 5.

#### 5.5 Memory Parity support

Memory Parity support is optional on both core logic and VUMA device. If core logic supports parity it should be able to disable parity check for Main VUMA Memory and Auxiliary VUMA Memory areas while parity check on the rest of the physical system memory is enabled.

#### 5.6 Memory Controller Pin Multiplexing

The logical interfaces for Fast Page, EDO and BEDO DRAMs are very similar but are significantly different than that of Synchronous DRAM. If mother board designers want to mix different DRAM technologies on the same mother board, core logic will have to multiplex DRAM control signals. The meaning of a multiplexed signal will depend on the type of DRAM core logic is accessing at a given time. If a VUMA device supports multiple banks access and mix of different DRAM technologies, it will also have to multiplex DRAM control signals. Both core logic and VUMA devices will have to have same multiplexing scheme. The appropriate JEDEC standard should be followed for multiplexing scheme.

# 6.0 Boot Protocol

32

####

#### VESA Confidential

### 6.1 Main VUMA Memory Access at Boot

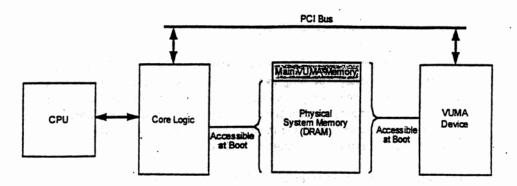

In unified memory architecture, part of the physical system memory is assigned to Main VUMA Memory. The existing operating systems are not aware of unified memory architecture. Also, some of the existing operating systems size memory themselves. This poses a problem as the operating systems after sizing the total physical system memory, will assume that they could use all of the memory and might overwrite Main VUMA Memory. The solution to this problem is explained below:

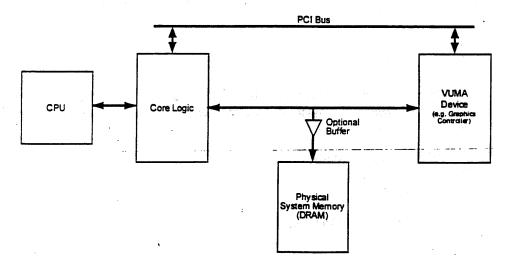

As shown in Figure 6-1, the solution to this problem is to disable core logic access to Main VUMA Memory area at boot time. In that case even if operating system, sizes the memory, it will find only (total physical system memory - Main VUMA Memory) and will not be aware of the Main VUMA Memory existence. This will avoid operating system ever writing to the Main VUMA Memory area. If VUMA device supports multiple banks access, it can access total physical system memory all the time. If VUMA device supports single bank access, it can access the bank of Main VUMA Memory all the time.

If VUMA device is a graphics controller, it needs a special consideration. Video screen is required during boot and since core logic can not access the Main VUMA Memory, it can not write to it. The problem is solved by programming the graphics controller into a pseudo legacy mode. In this mode graphics controller treats Main VUMA Memory exactly the same way as in non unified memory architecture situations i.e. as if it has its own separate frame buffer. So now, the total system looks just like a non unified memory architecture system and this mode is called as pseudo legacy mode. Core logic performs accesses to video through legacy video memory address space of A000:0 and B000:0. These accesses go on the PCI bus. Graphics controller claims these cycles. Graphics controller still needs to arbitrate for the physical system memory bus. After getting the bus, graphics controller performs reads/writes to Main VUMA Memory (frame buffer). After the system boots, it is still in the pseudo legacy mode. When operating system calls display driver, the driver programs core logic to allow access to Main VUMA Memory and switches the system from pseudo legacy mode to unified memory architecture.

In the case of other type of VUMA devices, device driver needs to program core logic to allow access to Main VUMA Memory.

#### Figure 6-1 Pseudo Legacy Mode

33

The following algorithm sums up the boot process in the case of VUMA device being a graphics controller:

- 1. System BIOS sizes the physical system memory.

- System BIOS reads the size of Main VUMA Memory at previous boot (where this value is stored is System BIOS dependent, but needs to be in some sort of non volatile memory).

- 3. System BIOS programs its internal registers to reflect that total memory available is [total physical system memory(from step 1) Main VUMA Memory at previous boot (from step 2)].

- 4. System boots and operating system calls display driver.

- Display driver makes a System BIOS call, <Enable/Disable Main VUMA Memory (refer to VUMA VESA BIOS Extensions)>, to program core logic internal registers to reflect that it can access total physical system memory.

- 6. Display driver switches VUMA device to unified memory architecture mode.

Even though core logic can not access Main VUMA Memory till the time display driver enables it, core logic is responsible for Main VUMA Memory refresh.

VUMA device should claim PCI Master accesses to Main VUMA Memory till display driver enables core logic access to that area. Core logic should claim PCI Master accesses to Main VUMA Memory after display driver enables core logic access to that area.

#### 6.2 Reset State

On power on reset, both core logic and VUMA device have their unified memory architecture capabilities disabled. MREQ# is de-asserted by VUMA device and MGNT# is de-asserted by core logic. System BIOS can detect if VUMA device supports unified memory architecture capabilities by reading <VUMA BIOS signature string (refer to VUMA VESA BIOS Extensions)>.

34

# 7.0 Electrical Specification

# 7.1 Signal Levels

This section describes the electrical signal levels for the arbitration signals only. DRAM signal levels depend on the type of DRAM used and hence can not be specified by the standard.

| MREQ#  | output<br>input | 5v TTL or 3.3v LVTTL<br>5v TTL for 5v buffer, 5v tolerant LVTTL for 3.3v buffer |

|--------|-----------------|---------------------------------------------------------------------------------|

| MGNT#  | output<br>input | 5v TTL or 3.3v LVTTL<br>5v TTL for 5v buffer, 5v tolerant LVTTL for 3.3v buffer |

| CPUCLK | output<br>input | 5v TTL or 3.3v LVTTL<br>5v TTL for 5v buffer, 5v tolerant LVTTL for 3.3v buffer |

# 7.2 AC Timing

This section describes the AC timing parameters for the arbitration signals only. DRAM AC timing parameters depend on the type of DRAM used and hence can not be specified by the standard. Both MREQ# are MGNT# timing parameters are with respect to CPUCLK rising edge.

| MREQ#  | output       | tClk to Out (max) - 10 ns         |

|--------|--------------|-----------------------------------|

|        |              | tClk to Out (min) - 2 ns          |

|        | input        | Set up time tSU (min) - 3 ns      |

|        |              | Hold time tH (min) - 0 ns         |

| MGNT#  | output       | tClk to Out (max) - 10 ns         |

|        |              | tClk to Out (min) - 2 ns          |

|        | input        | Set up time tSU (min) - 3 ns      |

|        | 1997 - C. 19 | Hold time tH (min) - 0 ns         |

| CPUCLK | output       | clock frequency (max) - 66.66 MHz |

7.2.1 Timing Budget

A margin for signal flight time and clock skew is added to the timing parameters.  $\pm$  2ns is allowed for the total of CPUCLK skew and signal flight time. Worst case timing budget calculations for setup and hold time are as follows:

35

# VUMA Proposed Sta: ird

# **VESA Confidential**

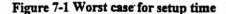

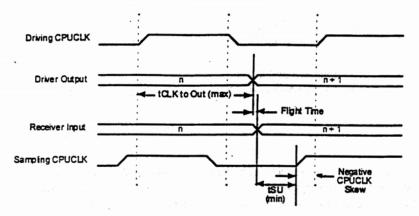

#### 7.2.1.1 Worst case for Setup time

Figure 7-1 shows the worst case for setup time. tClk to Out, flight time and clock skew have converged to reduce available setup time.

[tCLK to Out (max) + flight time + tSU (min) + negative CPUCLK skew]  $\leq$  CPUCLK period i.e. 15ns @ 66.66 MHz. [10ns + flight time + 3ns + negative CPUCLK skew]  $\leq$  15ns

[flight time + negative CPUCLK skew]  $\leq 2ns$

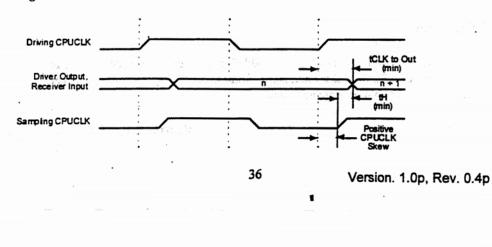

#### 7.2.1.2 Worst case for Hold time

Figure 7-2 shows the worst case for hold time. tClk to Out and clock skew have converged to reduce available hold time. Positive flight time number helps in this case and hence it is assumed to be zero.

## VUMA Proposed Star rd

# **VESA** Confidential

[positive CPUCLK skew + tH (min)] ≤ tCLK to Out (min) [positive CPUCLK skew + 0ns] ≤ 2ns positive CPUCLK skew ≤ 2ns

# 7.3 Pullups

All s/t/s signals need pullups to sustain the inactive state until another agent drives them. Core logic has to provide pullups for all the s/t/s signals. VUMA device has as option of providing pullups on some of the s/t/s signals. All t/s signals need pulldowns. Core logic has to provide pulldowns for all the t/s signals. VUMA device has as option of providing pulldowns on the t/s signals. Pullups and pulldowns could either be internal to the chips or external on board.

| DRAM Address -       | Core logic is responsible for pullups on DRAM Address lines.     |

|----------------------|------------------------------------------------------------------|

| DRAM control signals | - Core logic is responsible for pullups on DRAM control signals. |

|                      | VUMA device has as option of providing pullups on them.          |

| DRAM Data Bus -      | Core logic is responsible for pulldowns on DRAM data bus.        |

|                      | VUMA device has as option of providing pulldowns on them.        |

Pullups and pulldowns are used to sustain the inactive state until another agent drives the signals and hence need to be weak. Recommended value for pullups and pulldowns is between 50 kohm and 80 kohm.

### 7.4 Straps

As some VUMA devices and core logic chips use DRAM data bus for straps, DRAM data bus needs to be assigned for straps for different controllers. The assignment of DRAM Data Bus for straps is as follows:

| MD [0:19]  | VUMA device on Motherboard |

|------------|----------------------------|

| MD [20:55] | Reserved                   |

| MD [56:63] | Core Logic                 |

All the straps need to be pullups of 10 kohm.

#### 7.5 DRAM Driver characteristics

Loading plays a critical role in DRAM access timing. In case of PC motherboards end users can expand the existing memory of a system by adding extra SIMMs. Hence, typically the total DRAM signal loading is not constant and could vary significantly. Both Core Logic and VUMA device must be able to drive the maximum load that the

37

Version. 1.0p, Rev. 0.4p

Page 223 of 280

Petitioners HTC & LG - Exhibit 1002, p. 223

# VUMA Proposed Strand

#### VESA Confidential

system motherboard is designed to accommodate. In typical motherboard designs DRAM signal loading can be excessive (on the order of 1000pF for some signals) and hence care must be taken for DRAM driver selection. Some general guide lines for DRAM driver design are as follows:

Slew-rate controlled drivers are recommended. Drivers with selectable current drive (such as 8/16 mA drivers) may be used. This can reduce overshoot and undershoot associated with over-driving lightly loaded signals and can prevent excessive rise and fall time delay due to not providing enough current drive on heavily loaded signals.

As shown in Figure 7-3, buffers may be placed on the system motherboard to reduce the per signal loading and/or provide larger drive strength capabilities. DRAM Write Enable and DRAM Address signals are typically the most heavily loaded signals. Column Address Strobe signals may also become overloaded when more than two DRAM banks are designed into a system. TTL or CMOS buffers (typically 244 type) may be used to isolate and duplicate heavily loaded signals on a per bank basis. 244 type buffers typically have very good drive characteristics as well and can be used to drive all of the heavily loaded DRAM control signals if the Core Logic and/or VUMA device has relatively weak drive characteristics. If external buffers are used, the buffer delays should be taken in to timing considerations.

Wider DRAM devices offer reduced system loading on some of the control signals. x4 DRAMs require four times the physical connections on RAS, MA (Address), and write enables as x16 DRAMs. The reduction in loading can be significant. If the designer has control over the DRAMs which will be used in the system, the DRAM width should be chosen to provide the least loading.

38

**VESA**<sup>®</sup>

VUMA Proposal

(Draft) Video Electronics Standards Association

2150 North First Street, Suite 440 San Jose, CA 95131-2029 Phone: (408) 435-0333 FAX: (408) 435-8225

# VESA Unified Memory Architecture VESA BIOS Extensions (VUMA-SBE) Proposal

### Version: 1.0

# Document Revision: 2.2p November 1, 1995

Important Notice: This is a draft document from the Video Electronics Standards Association (VESA) Unified Memory Architecture Committee (VUMA). It is only for discussion purposes within the committee and with any other persons or organizations that the committee has determined should be invited to review or otherwise contribute to it. It has not been presented or ratified by the VESA general membership.

#### Purpose

To allow the video BIOS and other GUI specific software to control the VUMA hardware without specific knowledge or direct hardware access.

#### Summary

This document contains a specification for a system and video BIOS interface, VUMA-SVBE. The VUMA-SVBE interface will allow the video BIOS and other GUI specific software to control the VUMA hardware without specific knowledge or direct hardware access. The hardware protocol is described in VESA document VUMA 1.0.

### VUMA Proposed Sta. Jard

# **VESA** Confidential

#### Scope

Because this is a draft document, it cannot be considered complete or accurate in all respects although every effort has been made to minimize errors.

# Intellectual Property

© Copyright 1995 – Video Electronics Standards Association. Duplication of this document within VESA member companies for review purposes is permitted. All other rights are reserved.

# Trademarks

All trademarks used in this document are the property of their respective owners. VESA and VUMA are trademarks owned by the Video Electronics Standards Association.

# Patents

The proposals and standards developed and adopted by VESA are intended to promote uniformity and economies of scale in the video electronics industry. VESA strives for standards that will benefit both the industry and end users of video electronics products. VESA cannot ensure that the adoption of a standard; the use of a method described as a standard: or the making, using, or selling of a product in compliance with the standard does not infringe upon the intellectual property rights (including patents, trademarks, and copyrights) of others. VESA, therefore, makes no warranties, expressed or implied, that products conforming to a VESA standard do not infringe on the intellectual property rights of others. and accepts no liability direct, indirect or consequential, for any such infringement.

2

Version. 1.0p, Rev. 2.2p

# Petitioners HTC & LG - Exhibit 1002, p. 226

# VUMA Proposed Standaru

# **VESA Confidential**

# Support For This Specification

If you have a product that incorporates VUMA<sup>TM</sup>, you should ask the company that manufactured your product for assistance. If you are a manufacturer of the product, VESA can assist you with any clarification that you may require. All questions must be sent in writing to VESA via:

(The following list is the preferred order for contacting VESA.)

VESA World Wide Web Page: www.vesa.org

Fax:

(408) 435-8225

Mail:

VESA 2150 North First Street Suite 440 San Jose, California 95131-2029

# Acknowledgments

This document would not have been possible without the efforts of the members of the 1995 VESA Unified Memory Architecture Committee and the professional support of the VESA staff.

# Work Group Members

Any industry standard requires information from many sources. The following list recognizes members of the VUMA Committee, which was responsible for combining all of the industry input into this proposal.

### VUMA Chairperson

Rajesh Shakkarwar OPTi

#### Software work group Members

| Tim Crawford       | Work group leader, Cirrus Logic |

|--------------------|---------------------------------|

| Phil Mummah        | Phoenix Technologies            |

| Josh Grossman      | S3, Inc.                        |

| Christopher Rhodes | Award Software                  |

3

1

# VUMA Proposed Sta and

# **VESA Confidentia!**

# **Revision History**

| Initial Revision                                                                                                                                                                                                                                          | Aug 14 '95   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Rev.7                                                                                                                                                                                                                                                     | Aug 24 '95   |

| Rev.8                                                                                                                                                                                                                                                     | Aug 28 '95   |

| Removed segment registers, modified Boot sequence wording.                                                                                                                                                                                                |              |

| Rev.9                                                                                                                                                                                                                                                     | Aug 28 '95   |

| Added assumption F, modified issues and moved some to assumptions, remove refere<br>to main and aux VUMA memory, removed function for aux VUMA memory, modi<br>speed/type function                                                                        | nces<br>fied |

| Rev 1.0                                                                                                                                                                                                                                                   | Sept 8 '95   |

| Added VUMA device DRAM support, SDRAM parameters in function 6                                                                                                                                                                                            |              |

| Rev 1.1                                                                                                                                                                                                                                                   | Sept 11 '95  |

| Add items to Boot sequence                                                                                                                                                                                                                                | Sept II 95   |

| Remove a function call and cleaned up others                                                                                                                                                                                                              |              |

| Rev 1.2                                                                                                                                                                                                                                                   | Sept 22 '95  |

| Add changes suggested in previous VESA meeting                                                                                                                                                                                                            | Sept 22 95   |

| D1.2                                                                                                                                                                                                                                                      | -            |

| Rev 1.3                                                                                                                                                                                                                                                   | Sept 29 *95  |

| Added 32 bit I/F, added Aux functions, Added 16 bit protected mode I/F,<br>Modified several functions                                                                                                                                                     |              |

| Rev 1.4                                                                                                                                                                                                                                                   | Oct 6 '95    |

| Modified assumptions, issues, updated some functions.                                                                                                                                                                                                     |              |

| Rev 1.5                                                                                                                                                                                                                                                   | Oct 6 '95    |

| Modified the table of contents<br>Rev. 1.6                                                                                                                                                                                                                | 0-+ 10 105   |

| Minor modifications to assumptions                                                                                                                                                                                                                        | Oct 10 '95   |

| Rev 1.7                                                                                                                                                                                                                                                   | Oct 16 '95   |

| Changes to assumptions, & goals.                                                                                                                                                                                                                          |              |

| Made chages to some functions per discusion at last committee meeting.                                                                                                                                                                                    |              |

| Rev 1.8                                                                                                                                                                                                                                                   | Oct 18 '95   |

| Made changes to how memory is reported, funes 1 & 6. Modified ROM signature.                                                                                                                                                                              |              |

| Rev 1.9                                                                                                                                                                                                                                                   | Oct 18 '95   |

| Modified function 6 and assumptions. Other minor typos fixed.                                                                                                                                                                                             |              |

| Rev 2.0                                                                                                                                                                                                                                                   | 0-+ 22 105   |

| Modified assumptions C, J, L, N. Added assumptions O, P, Q, R. Removed issue 4.<br>Added error code 5, 6. Changed unit of memory in ROM signature from 1K to 64K.<br>Modified register definition in function 0, 1, 2, 6, and 7. Other minor typos fixed. | Oct 23 '95   |

| Rev 2.1                                                                                                                                                                                                                                                   | Oct 24 '95   |

| Added assumption "s".                                                                                                                                                                                                                                     |              |

| Per 2.2                                                                                                                                                                                                                                                   | •• • •       |

| Rev 2.2                                                                                                                                                                                                                                                   | Nov 1 '95    |

| Added requirement for 32 and 16 bit protected mode call stack selector and IO requirements. Removed issue section. Updated 32-bit and 16 bit interface section. Modified assumption 1, o. s. Rewrote sec. 3.1, 3.2 Modified sec.3.4, 3.5.0, 3.5.1, 3.5.6, |              |

|                                                                                                                                                                                                                                                           |              |

4

1

# VUMA Proposed Stan d

# VESA Confidential

:

# TABLE OF CONTENTS

| 1.0   | Introduction                                                      | 7               |

|-------|-------------------------------------------------------------------|-----------------|

| 2.0   | Goals & Assumptions                                               | 7               |

| 2.1   | Goals                                                             | 7               |

| 2.2   | Assumptions                                                       | 8               |

| 2.3   | Assumptions                                                       | 8               |

| 3.0   | VUMA VESA SYSTEM BIOS Extensions (VUMA-SBE)                       |                 |

| 3.1   | VUMA-SBE 32 bit interface                                         | 9               |

| 3.2   | VUMA-SBE 16 bit interface                                         | 11              |

| 3.3   | Status Information                                                | 12              |

| 3.4   | ROM signature                                                     | 12              |

| 3.5   | VUMA-SBE Functions                                                | 13              |

| 3.5.0 | 00h - Report VUMA -Core Logic Capabilities                        | 13              |

| 3.5.1 | 01h - Request Memory capabilities                                 | 15              |

| 3.5.2 | 02h - Set (Request) Memory Size for Next Boot                     | 16              |

| 3.5.3 | 03h - Get Memory Size for Next Boot for a Device                  | 17 <sup>.</sup> |

| 3.5.4 | 04h - Get Memory Size for Next Boot for all of VUMA Memory        | 18              |

| 3.5.5 | 05h - Get Current Memory Size for a Device or for all VUMA Memory | 19              |

| 3.5.6 | 06h - Return Memory Speed/Type                                    | 20              |

| 3.5.7 | 07h - Enable/disable memory                                       | 22              |

| 3.5.8 | 08h - Set (Request) VUMA Aux Memory                               |                 |

| 3.5.9 | 09h -Get VUMA Aux Memory Size                                     | 24              |

6

# VUMA Proposed Stand

# 1.0 Introduction

This document contains specifications for VESA unified memory architecture system and video BIOS interface. The system BIOS VUMA-SBE (System BIOS Extensions) will allow the video BIOS and other GUI specific software to control the VUMA hardware without specific knowledge or direct hardware access. The video BIOS VUMA-VBE (Video BIOS Extensions) will allow the system BIOS and other GUI specific software to access the VUMA hardware without specific knowledge or direct hardware access. The hardware access. The hardware protocol is described in VESA document VUMA 1.0.

Readers of this document should already be familiar with the VESA BIOS extensions and programming at the BIOS level.

# 2.0 Goals and Assumptions

VUMA-SBE provides a hardware independent means for operating system and configuration utility software to control and get status from the VUMA hardware.

VUMA-SBE services need to be provided as part of the system and video BIOS ROMs since the functions need to be used during system boot up.

#### 2.1 Goals

- a. Allow system memory access to non system controller devices. These devices, called VUMA devices will have their own memory controller and access system memory directly. All of system memory is potentially accessible by VUMA devices.

- b. Allow multiple devices. Although only one connector is allowed, multiple devices on the motherboard as well as multiple devices on the expansion board are allowed.

- c. If a VUMA device that previously has requested memory is taken out of the system, the memory will be returned to the O/S on the next boot.

- d. If a VUMA device is replaced by another VUMA device, the system will allocate the same amount of memory, if it meets the minimum requirements of the new board. Otherwise the memory allocated will be increased to the minimum required by the new board.

7

# VUMA Proposed Stallard

#### 2.2 Assumptions

- a. System BIOS will manage memory allocation requests from VUMA devices.

- b. Memory must be sized, typed and contiguous before control is turned over to a VUMA device.

- c. VUMA devices will test and initialize their own Main VUMA memory. (This is similar to the way they initialize and test their video memory on conventional VGA devices.)

- e. The lowest PCI PFA number will have priority if more than one VGA device is plugged in. The manufacture can decide if the VUMA slot has the highest, lowest or middle PFA number.

- f. The Video BIOS must be in shadow ram and writeable when control is passed to the video ROM as defined by the PCI SIG.

- g. The values that BIOS reports in function 6 for current, voltage, and speed will be determined at build/compile time.

- h. A device driver should insure that when requesting VUMA memory for the next boot that enough memory will be left for the O/S to boot.

- i. The device driver should take into consideration memory bandwidth when requesting memory.

- j. Memory is installed on the mother board in the bank or banks (RAS/CS) that the VUMA device can access. If a user moves memory to a bank (RAS/CS) that the VUMA controller can not access, the VUMA device will be disabled.

- k. On a warm boot the sytem will reallocate VUMA memory for each device.

- 1. For a multi-function plug in board, only function 0 on the board may require a minimum amount of memory for booting. See section 3.4, point A. Set next boot size call (VUMA-SBE function 2) can only be made using the PFA of function 0 on the board.

- m. If a plug in card has a bridge, only the first function of the first device behind the bridge may require a minimum amount of memory for booting. See section 3.4, point A.

- N. System BIOS will insure that PCI addresses will not conflict with Main VUMA memory that is placed above system memory. Main VUMA memory could have addresses that are not contiguous with system memory. (See h/w spec.)

- Main VUMA memory that is contiguous to system memory must be disabled before OS boots.

- p. VUMA device driver is responsible for enabling CPU access to Main VUMA memory. Note, all of Main VUMA memory access by the CPU is enabled when any part is enabled, i.e., all or nothing. Disabling CPU access is not allowed at run time.

- q. The Main VUMA memory must be contiguous, but it is not necessary to be contiguous with system memory.

- r. If Main VUMA memory is not contiguous with system memory, CPU access does not need to be disabled prior to INT 19h.

- s. When requesting Aux VUMA memory, if system memory is being cache by any type of cache, the cache must be cleared by an I/O instruction, not by reading memory. This is necessary since in protected mode a selector will not be available to the BIOS.

8

# VUMA Proposed Standard

**VESA** Confidential

Page 233 of 280

# Petitioners HTC & LG - Exhibit 1002, p. 233

#### 2.3 Boot Sequence

- 1. System BIOS sizes and configures (makes contiguous) all system memory.

- System BIOS scans ROM space for VUMA devices and determine if there are any devices present that were not present at the last boot. If yes, then add the minimum amount of memory required by that device for booting, to VUMA memory.

- 3. Allocate VUMA memory. At this point all memory, including VUMA memory is enabled. If this is not possible to allocate all requested memory (possibly memory has been removed between boots) then the system will scan all VUMA ROMs and allocate the minimum necessary to boot.

- 4. Next, call the entry point to the VGA device. The VGA device tests and initializes it's memory at this time.

- 5. After the VGA device has initialized itself, control is given back to the system BIOS.

- 6. System BIOS then continues POST. During POST the system gives control to the other PCI devices (including VUMA devices). They then initialize themselves.

7. When the OS starts it's boot process, it will then load and execute the video driver. If necessary the video driver will then enable the CPU access to memory allocated to the VUMA device.

8 Any changes to the size of the memory allocated to the VUMA device will be requested by the video driver, O/S, or utility/properity sheet. These requests will then be implemented on the next boot.

# VUMA Proposed Standard

# **VESA** Confidential

#### 3.0 VUMA VESA SYSTEM BIOS Extensions (VUMA-SBE)

The new system BIOS calls have that have been defined can be accessed via the following VUMA-SBE interfaces.

# 3.1 VUMA-SBE 32 bit interface.

Detecting the presence of the 32-bit interface for the VUMA-SBE functions is done using the BIOS32 Service Directory<sup>1</sup>. Use of the service directory involves 3 steps : locating the service directory, using the service directory to get the VUMA services entry point and finally calling the VUMA services to perform the desired function. The BIOS32 Service Directory is a contigous 16-byte data structure which begins on a 16-byte boundary somewhere in the physical address range 0E0000h - 0FFFFFh. It has the following format :

| Offset | Size    | Description                                                                                                                                                                                               |

|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h    | 4 bytes | ASCII Signature String _32_<br>This puts an underscore at offset 0, a '3' at offset 1, a '2' at offset 2 and<br>another underscore offset 3.                                                              |

| 04h    | 4 bytes | Entry point for BIOS32 Service directory<br>This is a 32-bit physical address through which the service directory can<br>be called.                                                                       |

| 08h    | l byte  | Revision level<br>The current revision level is 00h.                                                                                                                                                      |

| 09h    | l byte  | Length of data structure in paragraph (i.e., 16-byte) units.<br>The data structure in this revision is 16 bytes long so this field has a value of 01h.                                                    |

| 0Ah    | l byte  | Checksum<br>This field is a checksum of the complete data structure. It has a value<br>such that when all of the bytes in the data structure are added together in<br>a byte wide sum they add up to 00h. |

| 0Bh    | 5 bytes | Reserved<br>Must be 0                                                                                                                                                                                     |

To locate the service directory a caller must scan 0E0000h to 0FFFFFh on 16-byte boundaries looking for the ASCII signature "\_32\_" and a valid checksummed data structure. If the service directory is NOT found then 32-bit VUMA support is not present in the BIOS.

11

<sup>&</sup>lt;sup>1</sup> The BIOS32 Service Directory is an industry standard and is described by the document Standard BIOS 32-bit Service Directory Proposal, Revision 1.0 May24, 1993 available from Phoenix Technologies Ltd., Irvine, CA

# VUMA Proposed Sta ard

# VESA Confidential

To get the VUMA services entry point a CALL FAR to service directory is done using the value specified at offset 04h in the service directory data structure. The following is a list of the entry conditions and the return values when calling the service directory.

INPUT:

|      | EAX       | Service Identifier                                                      |

|------|-----------|-------------------------------------------------------------------------|

|      |           | This is a 4 character string used to identify which 32-bit BIOS service |

|      |           | is being sought. For VUMA is it "VUMA" where EAX =                      |

|      |           | 414D5556h (NOTE: This corresponds to mov eax, 'VUMA')                   |

| •    | EBX[31:8] | •                                                                       |

|      |           | Must be set to 00h                                                      |

|      | EBX[7:0]  | 00h                                                                     |

|      | CS        | Code selector set up to encompass the physical page holding the entry   |

|      | CO        | point as well as the immediately following physical page. It MUST       |

|      |           | have the same base. CS is execute only.                                 |

|      | DS        | Data selector set up to encompass the physical page holding the entry   |

|      |           | point as well as the immediately following physical page. It MUST       |

|      |           | have the same base. DS is read-only.                                    |

|      | SS        | Stack selector must provide at least 1K of stack space and be 32-bit.   |

|      | I/O       | I/O Permissions must be provided so that the BIOS can perform any       |

|      |           | I/O necessary.                                                          |

|      |           |                                                                         |

| OUTP | UT:       |                                                                         |

|      |           |                                                                         |

|      | AL        | Return Code                                                             |

|      |           |                                                                         |

|      |           | 00h - Requested service is present.                                     |

|      |           | 80h - Requested service is NOT present.                                 |

|      |           | 81h - Unimplemented function specified in BL.                           |

|      | EBX       | Physical address to use as the selector BASE for the service.           |

|      | ECX       | Value to use as the selector LIMIT for the service.                     |

|      | EDX       | Entry point for the service relative to the BASE returned in EBX.       |

|      |           |                                                                         |

|      |           |                                                                         |

Once the VUMA entry point has been found the caller should create an execute-only CODE and read-only DATA selectors based on the values in EBX and ECX. The VUMA entry point can now be invoked using a CALL FAR with the created CODE selector and the offset in EDX. The following additional conditions must exist when calling the VUMA entry point :

12

1

### VUMA Proposed Standard

# **VESA** Confidential

- I/O permissions are such that the service can perform any I/O necessary

- The stack is a 32-bit stack and provides at least 1K of stack space

- The appropriate privilege is provided so that the service can enable/disable interrupts are needed

All other register settings are specified to the function being called.

# 3.2 VUMA-SBE 16 bit interface.

The 16 bit Interface is function-based and all parameters are passed in registers. If a register is not specified as an output parameter for a function, then it will be preserved. All flags are preserved. Function values are passed as input parameters in register BL. Return status is passed back in register AL. A return status of 00h indicates that the function was successful.

Prior to calling into the 16-bit interface in protected mode using the PUSHF / CALL sequence the following requirements must be met :

- CS is an execute-only selector with a BASE of 0F0000h and a LIMIT of 64K.

- DS is a read-only selector with a BASE of 0F0000h and a LIMIT of 64K.

- I/O permissions are such that the service can perform any I/O necessary

- The stack is a 16-bit stack and provides at least 1K of stack space

- The appropriate privilege is provided so that the service can enable/disable interrupts are needed

Entry to the 16 bit interface may be done one of two ways:

Entry point to the 16 bit services is F000:F859. To call these services: Set up the registers as indicated in the function description. Status information is returned in AX.

PUSHF CALL FAR F000:F859 Check results

The 16 bit interface may also be accessed through the INT 15h instruction. The value F401h is passed in the AX register, with the subfunction passed in BL. Status information is returned in AX.

13

#### VUMA Proposed Star. rd

VESA Confidential

### 3.3 Status Information for the calls

Every function returns information in the AX register. The format of the status word is as follows:

|            | Function is supported.                                              |

|------------|---------------------------------------------------------------------|

| AL = FFh:  | No error, but function NOT supported.                               |

| AL = 00h:  | Function error or not completed yet, see error codes in AH.         |

| AH = 00h:  | Function call successful.                                           |

| AH != 00h: | Function call failed.                                               |

| = 01h:     | Unknown PFA. PFA does not match devices in system.                  |

| = 02h:     | Invalid Input Argument.                                             |

| = 03h:     | Too many banks (RAS/CS lines) requested.                            |

| = 04h:     | Requested bank(s) RAS/CS line(s) not supported.                     |

| = 05h:     | Aux Memory not supported.                                           |

| = 06h:     | Noncacheable/ write through cache area not available.               |

| = 80h:     | Function needs to be called again to return additional information. |

| = FFh:     | Other unknown error.                                                |

### 3.4 ROM Signature

VUMA devices must have a ROM signature, within the first 1K, "\_VUMA\_XXxx" where XX is major version and xx is minor version. Following the minor version number:

- A. 16 bit value with the minimum amount of memory necessary, in 64Kblocks, for booting. It is not a requirement to have all devices working to boot. Only devices essencial to bring up a system, such as VGA and a boot device (hard drive) are necessary. After booting, a device driver or utility may request additional memory for non-essential devices.

- B. 16 bit value with bit map of memory banks (RAS/CS lines) supported. Bit 0 corresponds to bank number 0 etc. If a bit is set then the bank (RAS/CS line) is supported by the VUMA device.

- C. 16 bit value for DRAM support. Bit set if supported.

- Bit 0 = Fast Page

- Bit 1 = EDOn

- Bit 2 = SDRAM

- Bit 3 = PN EDO (Burst EDO)

- All other bit are reserved.

- D. 8 bit value for features.

- Bit 0 = Snooping supported by VUMA device if set. (See h/w spec for definition of snooping.

#### 3.5 VUMA-SBE Functions

The following defined VUMA-SBE services are not included in the VBE standard documentation.

# 3.5.0 00h - Report VUMA Core Logic Capabilities

This function should be called before any other VUMA-SBE function is called to ensure that the VUMA system is present, and to inquire the core logic capabilities

Input: (AX is used only when being called by one of the two 16 bit interfaces.)

AH = F4hAL = 01h

BL = 00h

Output:

AX = Status (see section 3.3)

BL = Major BIOS revision = 01h

BH = Minor BIOS revision = 00h

CX = Banks (RAS/CS) that are supported, could have memory installed, by the core logic controller

Bit 0 = bank 0

- Bit 1 = bank 1

- etc.

DX[3:0] = Core logic capabilities

0 = No special features

Bit 0 = 1 -> Controller supports non-cacheable regions

- Bit 1 = 1 -> Controller supports write-thru cache regions

- Bit 2 = 0 -> Cannot change at run time from cached to non-cached and back

- 1 -> Can change at run time from cached to non-cached and back

- Bit 3 = 0 -> Cannot change at run time from non-write through to write through and back

- 1 -> Can change at run time from cached to non-write through and back

- DX[4] = Core logic supports snooping, this item is relevant only when synchrounous DRAM is supported

- 0 = Snooping is NOT supported

1 = Snooping is supported

SI = Bank (RAS/CS) numbers with memory. Bit set if has memory. Bit 0 = bank 0

15

# VUMA Proposed Sta. ard

## VESA Confidential

Bit 1 = bank 1 etc. DI = Bank (RAS/CS) numbers with memory and support VUMA. Bit 0 = bank 0 Bit 1 = bank 1

etc.

# VUMA Proposed Standard

# **VESA** Confidential

# 3.5.1 01h - Request VUMA Main Memory capabilities

This function returns system controller capabilities.

Input: (AX is used only when being called by one of the two 16 bit interfaces.)

- AH = F4h

- AL = 01h

- BL = 01h

Output:

AX = Status (see section 3.3)

- BX = Minimum size can allocate in 64 K increments

- CX = Maximum size can allocate in 64 K increments

- SI = System memory noncacheable or write through area granularity in 64 K blocks. Minimum block size region in system memory that can have L2 cacheable, non-cacheable, or write through cache. This is a basis provided for rounding up Aux memory size request.

0 = Not defined

- DI = VUMA main memory size increments from minimum size in 64K. When memory is disabled the CPU does not have access to it but refresh still occurs.

- 0 = Not defined

17

Version. 1.0p, Rev. 2.2p

# Petitioners HTC & LG - Exhibit 1002, p. 241

VESA Confidential

### 3.5.2 02h - Set (Request) VUMA Main Memory for Next Boot

This function sets the size of the Main VUMA memory for the next boot. An input parameter is the memory bank numbers (RAS/CS numbers) that can be accessed by the VUMA device. The banks supported (parameter passed in DX) **must** be the same as reported in the ROM signature as specified in section 3.4 of this document.

Input: (AX is used only when being called by one of the two 16 bit interfaces.)

18

AH = F4h AL = 01 BL = 02 CX = PFA number. CH = Bus Number (0 .. 255) CL[7:3] = Device number CL[2:0] = Function Number DX = Banks (RAS/CS) that are supported by the calling device. Bit 0 = bank 0 Bit 1 = bank 1 etc. SI = Size in 64 Kbytes (Will be rounded up by the system BIOS if necessary)

Output:

AX = Status (see section 3.3) DX = Actual size in 64 K bytes allocated.

# VUMA Proposed Standard

# **VESA** Confidential

# 3.5.3 03h - Get VUMA Main Memory Size for Next Boot for a Device

This function returns the size of Main VUMA memory to be set for the next boot for the selected controller.

Input: (AX is used only when being called by one of the two 16 bit interfaces.)

19

AH = F4h AL = 01h BL = 03h CX = PFA number CH = Bus Number (0 .. 255) CL[7:3] = Device number CL[2:0] = Function Number Output: AX = Status (see section 3.3)

DX = Size in 64 K bytes

# VUMA Proposed St. Jard

# **VESA Confidential**

# 3.5.4 04h - Get Memory Size for Next Boot for all MAIN VUMA Memory.

This function returns the size of Main VUMA memory to be set for the next boot.

:

Input: (AX is used only when being called by one of the two 16 bit interfaces.)

. ...

AH = F4hAL = 01hBL = 04hOutput: AX = Status (see section 3.3)

DX = Size in 64 K bytes

### VUMA Proposed Stanoard

#### **VESA** Confidential

### 3.5.5 05h - Get Current Memory Size for a Device or for all VUMA Memory

This function returns the size of Main VUMA memory for the selected controller. Note: Value returned in BH is for all of VUMA main memory since all main memory is either enabled or disabled. (Allows CPU access or does not allow CPU access.)

Input: (AX is used only when being called by one of the two 16 bit interfaces.)

AH = F4hAL = 01h

BL = 05h

CX = PFA number

CH = Bus Number (0 .. 255)

CL[7:3] = Device number

CL[2:0] = Function Number

If CX = FF then return for all devices

#### Output:

AX = Status (see section 3.3)

BH[0] = Memory access for all of Main VUMA memory.

0 -> Memory is not enabled, not visible to the CPU

1 -> Memory is enabled, visible to the CPU

CX = Bit map of bank (RAS/CS) numbers used. Bit set if bank is used.

Bit 0 = bank 0

Bit 1 = bank 1

etc.

DX = Size in 64 Kbytes

SI = upper 16 bits of physical start address

DI = lower 16 bits of physical start address

21

Version. 1.0p, Rev. 2.2p

Page 245 of 280

#### 3.5.6 06h - Return Memory Speed/Type/Location/Size

This function returns information about the type of memory installed for the selected bank (RAS/CS). Fractions greater than 0.5 are rounded up. Fractions 0.5 and lower are rounded down. If a bank is logically divided into more than one area, then the function needs to be called more than once. AX indicates whether the function is done or not. If more than 1 bit in CX is set then error code AH= 03H will be returned, therefore only one bit should be set in CX when calling this function. Note: If a bank has contigous memory, but part of the memory is system memory and part is VUMA memory, the information will also be returned in two steps. BX[14] will reflect the type of memory.

Input: (AX is used only when being called by one of the two 16 bit interfaces.)

AH = F4hAL = 01hBL = 06hCX = Bank (RAS/CS) number Bit 0 = bank 0Bit 1 = bank 1etc. DX = Serial calling number Output: AX = Status (see section 3.3, if equal to 80, must call for more info) BX[15] = Reserved. BX[14] = MAIN VUMA memory. 0 = not main VUMA memory, is system memory 1 = main VUMA memory. BX[13:7] = Speed of memory in nano-seconds 0 = undefined, else value. BX[6:0] = Core logic controller speed in nano-seconds 0 = undefined, else value. CX[3:0] = Type of memory 0000 = Undefined 0001 = Fast page mode 0010 = EDO0011 = SDRAM 0100 = PN EDO (Burst EDO) CX[5:4] = CAS latency CX[7:6] = Burst 0 = 11 = 22 = 43 = undefined

22

# VUMA Proposed Standard

# **VESA Confidential**

CX[8] = Burst order 0 = Linear1 = Sequential

CX[15:9] = Voltage of memory in tenths of a volt  $0 \Rightarrow$  undefined

DX[7:0] = Size in Mega-bytes

SI DI

ŀ

- upper 16 bits of physical start address

lower 16 bits of physical start address

23

1

Version. 1.0p, Rev. 2.2p

# VUMA Proposed SL dard

## VESA Confidential

## 3.5.7 07h - Enable/disable Main VUMA memory

The ability to enable/disable CPU access to Main VUMA memory is not required if Main VUMA memory is not contiguous with system memory. If supported, this function enables/disables CPU access to Main VUMA memory. When any device makes this call, all devices that have main VUMA memory will be affected. When CPU access to main VUMA memory is disabled, access to video memory may be done through the PCI bus. Note: During run time (after Int 19) CPU access can not be disabled.

Input: (AX is used only when being called by one of the two 16 bit interfaces.)

AH = F4h

AL = 01h

BL = 07h

BH[0] = Memory access

- 0 -> Enable CPU access to VUMA Main memory.

- 1 -> Disable CPU access to VUMA Main memory. (Can not be done at run time.)

Output:

AX = Status (see section 3.3)

24

Version. 1.0p, Rev. 2.2p

## VUMA Proposed Stanuard

# **VESA** Confidential

## 3.5.8 08h - Set (Request)/Free VUMA Aux Memory

This function sets (requests) the size of the aux memory for use at run time. See "How To Access Aux VUMA Memory" in the Appendix to be added at a later time. A physical starting address and size is passed in. This function will flush and then turn off caching for this area or change the area to write through cache.

Input: (AX is used only when being called by one of the two 16 bit interfaces.)

AH = F4h AL = 01 BL = 08 BH[1:0] = Type of cache Bit 0 set if non-cachable Bit 1 set if write-Thru CX = PFA number CH = Bus Number (0 .. 255) CL[7:3] = Device number CL[2:0] = Function Number DX = Size in K bytes, free VUMA Aux memory if set to 0 SI = upper 16 bits of physical address

DI = lower 16 bits of physical address

Output:

AX = Status (see section 3.3)

DX = Actual size in Kbytes allocated (rounded up by the system BIOS if necessary)

Version. 1.0p, Rev. 2.2p

# VUMA Proposed St. Jard

# **VESA Confidential**

# 3.5.9 09h - Get VUMA Aux Memory Size

This function returns the size of the aux memory being used by a VUMA device.

Input: (AX is used only when being called by one of the two 16 bit interfaces.)

:

AH = F4h AL = 01h BL = 09h CX = PFA number CH = Bus Number (0 .. 255) CL[7:3] = Device number CL[2:0] = Function Number

Output:

:

AX = Status (see section 3.3)

DX = Size in Kbytes

SI = upper 16 bits of physical address DI = lower 16 bits of physical address

26

۲

Version. 1.0p, Rev. 2.2p

PUBLISHED BY Microsoft Press A Division of Microsoft Corporation One Microsoft Way Redmond, Washington 98052-6399

Copyright © 1994 by Adrian King

All rights reserved. No part of the contents of this book may be reproduced or transmitted in any form or by any means without the written permission of the publisher.

Library of Congress Cataloging-in-Publication Data King, Adrian, 1953-

Inside Windows 95 / Adrian King. p. cm. Includes index. ISBN 1-55615-626-X 1. Windows (Computer programs) 2. Microsoft Windows (Computer file) I. Title. QA76.76.W56K56 1994 005.4'469--dc20 93-48485

Printed and bound in the United States of America.

123456789 QMQM 987654

Distributed to the book trade in Canada by Macmillan of Canada, a division of Canada Publishing Corporation.

A CIP catalogue record for this book is available from the British Library.

Microsoft Press books are available through booksellers and distributors worldwide. For further information about international editions, contact your local Microsoft Corporation office. Or contact Microsoft Press International directly at fax (206) 936-7329.

CIP

PageMaker is a registered trademark of Aldus Corporation. Apple, AppleTalk, LaserWriter, Mac, Macintosh, and TrueType are registered trademarks of Apple Computer, Inc. LANtastic is a registered trademark of Artisoft, Inc. Banyan and Vines are registered trademarks of Banyan Systems, Inc. Compaq is a registered trademark of Compaq Computer Corporation. CompuServe is a registered trademark of CompuServe, Inc. Alpha AXP, DEC, and Pathworks are trademarks of Digital Equipment Corporation. LANstep is a trademark of Compaq Computer Corporation. CompuServe is a registered trademark of Haves Microcomputer Products, Inc. HP and LaserJet are registered trademarks of Hewlett-Packard Company. Intel is a registered trademark and EtherExpress, Pentium, and SX are trademarks of Intel Corporation. COMDEX is a registered trademark of Interface Group-Nevada, Inc. AS/400, IBM, Micro Channel, OS/2, and PS/2 are registered trademarks and PC/ XT is a trademark of International Business Machines Corporation. Nicrosoft, MS, MS-DOS, and XENIX are registered trademarks of Lotter Development Corporation. Microsoft, MS, MS-DOS, and XENIX are registered trademarks of ODBC, Win32s, Windows, Windows NT, and the Windows operating system logo are trademarks of Microsoft Corporation. MIPS is a registered trademark of Novell, Inc. Soft-Ice/W is a registered trademark of Nu-Mega Technologies, Inc. DESQview is a registered trademark and Qemm is a trademark of Quarterdeck Office Systems. OpenGL is a trademark of Silicon Graphics, Inc. PC-NFS, Sun, and Sun Microsystems are registered trademarks of Sun Microsystems, Inc. TOPS is a registered trademark of TOPS, a Sun Microsystems company. UNIX is a registered trademark of UNIX Systems Laboratories.

Acquisitions Editor: Mike Halvorson Project Editor: Erin O'Connor Technical Editors: Seth McEvoy and Dail Magee, Jr.

THREE: A Tour of Chicago

was originally designed as a standardized format for 32-bit protected mode code modules. There is an API, internal to the base system, that VxDs can use.<sup>11</sup> Obviously, the scope of these functions is at a much lower level than the scope of the services called on directly by applications.

# **Memory Management**

Memory management in Windows takes place at two different levels: a level seen by the application programmer and an entirely different view seen by the operating system. Over the course of different releases of Windows, the application programmer has seen little change in the available memory management APIs. Within the system, however, the memory management changes have been dramatic. Originally, Windows was severely constrained by real mode and 1 megabyte of memory. Then expanded memory provided a little breathing room, and currently the use of enhanced mode and extended memory relieves many of the original constraints. Windows 95 goes further yet and essentially removes all the remaining memory constraints.

Windows 95 continues to support all the API functions present in Windows 3.1, and you can still build and run applications that use the segmented addressing scheme of the 286 processor. However, if you look at the detailed documentation for the Windows 95 memory management API, you'll see that all of the API functions originally designed to allow careful management of a segmented address space are now marked "obsolete." The "obsolete" list includes, for example, all the functions related to selector management. The reason, of course, is the Windows 95 support for 32-bit linear memory and the planned obsolescence of the segmented memory functions—yet another unsubtle hint that the Win32 API is the API you should be using to write Windows applications.

Although use of the 32-bit flat memory model simplifies a lot of Windows programming issues, it would be misleading to say that Windows memory management has suddenly gotten easy.<sup>12</sup> Windows 95 actually has a number of new application-level memory management

12. The Windows 95 documentation lists 45 API functions under the heading "Memory Management." The "obsolete" list numbers 28 API functions.

ctions referesolve

LLs. It

; of the open a ge fault es from ystem is

stem in-Vindows ivileged e details which it ger with :r can be

VxDs. Alsed intere device. g at the deal with nality that thitecture

<sup>11.</sup> The Windows Device Driver Kit is the best reference for detailed information on VxDs and the associated API functions.

### INSIDE WINDOWS 95

capabilities. All of the functions relate to the management of memory within the application's *address space*, the private virtual memory allocated to the process. The systemwide management of memory is the responsibility of the base system, and the Windows API aims to hide many of the details of the system's lower-level functions.

「ないとう

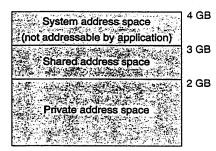

## **Application Virtual Memory**