512K x 16Bit x 2 Bank Synchronous DRAM

#### **FEATURES**

- · JEDEC standard 3.3V Power Supply.

- LVTTL compatible with multiplexed address.

- Dual Bank.

- · MRS cycle with address key programs.

- -. CAS Latency (1, 2, 3)

- -. Burst Length (1, 2, 4, 8 & Full page)

- -. Burst Type (Sequential & Interleave)

- All inputs are sampled at the positive going edge of the system clock.

- Burst Read Single Bit Write Operation.

- · L(U)DQM for byte masking.

- · Auto & Self Refresh.

- · 32ms Refresh Period. (2K cycle)

#### **GENERAL DESCRIPTION**

The KM416S1120A is 16,777,216 bits synchronous high data rate Dynamic RAM organized as 2 x 524,288 words by 16 bits, fabricated with SAMSUNG's high performance CMOS technology.

Synchronous design allows precise cycle control with the use of system clock. I/O transactions are possible on every clock cycle.

Range of operating frequencies, programmable burst length, and programmable latencies allows the same device to be useful for a variety of high bandwidth, high performance memory system applications.

#### **ORDERING INFORMATION**

| Part NO.           | Max Freq. | Package   |

|--------------------|-----------|-----------|

| KM416S1120AT-G/F10 | 100 MHz   | TSOP (II) |

| KM416S1120AT-G/F12 | 83 MHz    | TSOP (II) |

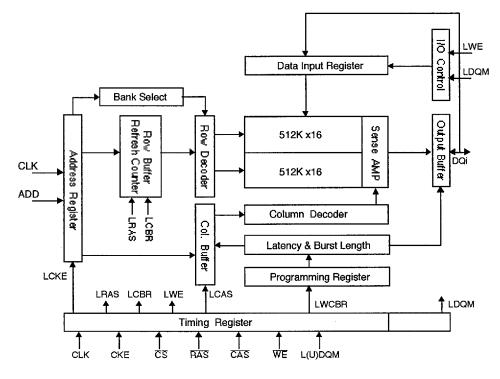

#### FUNCTIONAL BLOCK DIAGRAM

CD-ROM(Edition 3.0) This Data Sheet is subject to change without notice.

(C) 1996 Samsung Electronics Printed in Korea.

Find authenticated court documents without watermarks at docketalarm.com.

KM416S1120AT SDRAM

#### PIN CONFIGURATION (Top View)

| 1      |    |    |                        |

|--------|----|----|------------------------|

| VDDC   | 10 | 50 | Vss                    |

| DQ0 t  | 2  | 49 | DQ15                   |

| DQ1 c  | 3  | 48 | DQ14                   |

| Vssq c | 4  | 47 | Vssq                   |

| DQ2 d  | 5  | 46 | DQ13                   |

| DQ3 c  | 6  | 45 | DQ12                   |

| VDDQE  | 7  | 44 | VDDQ                   |

| DQ4 c  | 8  | 43 | DQ11                   |

| DQ5 d  | 9  | 42 | DQ10                   |

| Vssq 🛛 | 10 | 41 | Vssq                   |

| DQ6 c  | 11 | 40 | DQ9                    |

| DQ7 c  | 12 | 39 | DQ8                    |

| VDDQC  | 13 | 38 | VDDQ                   |

| LDQM d |    | 37 | ₽N.C                   |

| WEd    |    | 36 | UDQM                   |

| CAS    |    | 35 | ¢ CLK                  |

| RAS c  |    | 34 | D CKE                  |

| CS d   | 18 | 33 | ÞN.C                   |

| A11 C  | 19 | 32 | Þ A9                   |

| A10 E  | 20 | 31 | P A8                   |

| Aod    | 21 | 30 | Þ A7                   |

| A1 C   | 22 | 29 | P A6                   |

| A2 C   |    |    | A5 50 PIN TSOP (11)    |

| Азс    |    |    | A4 (400mil x 825mil)   |

| VDDC   | 25 | 26 | Vss (0.8 mm PIN PITCH) |

|        |    |    |                        |

#### **PIN FUNCTION DESCRIPTION**

| PIN       | NAME                     | INPUT FUNCTION                                                                                                                                                                                                                                 |

|-----------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK       | System Clock             | Active on the positive going edge to sample all inputs.                                                                                                                                                                                        |

| ខទ        | Chip Select              | Disables or enables device operation by masking or enabling all inputs except CLK, CKE, and L(U)DQM                                                                                                                                            |

| CKE       | Clock Enable             | Masks system clock to freeze operation from the next clock cycle.<br>CKE should be enabled at least one cycle prior to new command.<br>Disables input buffers for power down in standby.<br>CKE should be enabled tPDE prior to valid command. |

| A0~A10    | Address                  | Row / column addresses are multiplexed on the same pins.<br>Row address : RAo ~ RA1o, Column address : CAo ~ CA7                                                                                                                               |

| A11       | Bank Select Address      | Selects bank to be activated during row address latch time.<br>Selects bank for read/write during column address latch time.                                                                                                                   |

| RAS       | Row Address Strobe       | Latches row addresses on the positive going edge of the CLK with $\overline{\text{RAS}}$ low. Enables row access & precharge.                                                                                                                  |

| CAS       | Column Address Strobe    | Latches column addresses on the positive going edge of the CLK with $\overline{\text{CAS}}$ low. Enables column access.                                                                                                                        |

| WE        | Write Enable             | Enables write operation and row precharge.                                                                                                                                                                                                     |

| L(U)DQM   | Data Input/Output Mask   | Makes data output Hi-Z, tsHz after the clock and masks the output.<br>Blocks data input when DQM active. (Byte Masking)                                                                                                                        |

| DQ0 ~ 15  | Data Input/Output        | Data inputs/outputs are multiplexed on the same pins.                                                                                                                                                                                          |

| VDD/Vss   | Power Supply/Ground      |                                                                                                                                                                                                                                                |

| VDDQ/VSSQ | Data Output Power/Ground |                                                                                                                                                                                                                                                |

CD-ROM(Edition 3.0) This Data Sheet is subject to change without notice.

DOCKE

Δ

RM

Δ

(C) 1996 Samsung Electronics Printed in Korea.

Find authenticated court documents without watermarks at docketalarm.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                             | Symbol    | Value      | Unit      |

|---------------------------------------|-----------|------------|-----------|

| Voltage on any pin relative to Vss    | VIN, VOUT | -1.0 ~ 4.6 | V         |

| Voltage on VDD supply relative to Vss | VDD, VDDQ | -1.0 ~ 4.6 | v         |

| Storage temperature                   | Tstg      | -55 ~ +150 | <b>0°</b> |

| Power dissipation                     | PD        | 1          | W         |

| Short circuit current                 | los       | 50         | mA        |

Note : Permanent device damage may occur if 'ABSOLUTE MAXIMUM RATINGS' are exceeded. Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

#### DC OPERATING CONDITIONS

Recommended operating conditions (Voltages referenced to Vss = 0V, TA=0°C to 70°C)

| Parameter              | Symbol   | Min. | Тур | Max.    | Unit | Note      |

|------------------------|----------|------|-----|---------|------|-----------|

| Supply voltage         | VDD,VDDQ | 3.0  | 3.3 | 3.6     | ν    |           |

| Input high voltage     | Vін      | 2.0  | 3.0 | VDD+0.3 | v    |           |

| Input low voltage      | VIL      | -0.3 | 0   | 0.8     | V    | Note 1    |

| Output high voltage    | Vон      | 2.4  | -   | -       | V    | юн=-2mA   |

| Output low voltage     | Vol      | -    | -   | 0.4     | V    | IOL = 2mA |

| Input leakage current  | lır.     | -5   | -   | 5       | uA   | Note 2    |

| Output leakage current | IOL      | -5   | -   | 5       | uA   | Note 3    |

Note: 1. VIL(min.) = -1.5V AC (pulse width  $\leq$  5 ns)

2. Any input  $0 \le V \ge 0.3V$ , all other pins are not under test = 0V.

3. Dout is disabled, 0V≤VOUT≤VDD.

#### CAPACITANCE (VDD= 3.3V, TA= 25°C, f= 1MHz)

| Parameter                                               | Symbol | Min | Max | Unit |

|---------------------------------------------------------|--------|-----|-----|------|

| Input capacitance (Ao ~ A11)                            | CIN1   | -   | 5   | pF   |

| Input capacitance<br>(CLK,CKE,CS, RAS,CAS,WE & L(U)DQM) | CIN2   | -   | 5   | pF   |

| Data input/output capacitance<br>(DQo ~ DQ15)           | Соит   | -   | 6   | pF   |

#### DECOUPLING CAPACITANCE GUIDE LINE

Recommended decoupling capacitors are added to power line on PCB.

| Parameter                                    | Symbol | Value   | Unit |

|----------------------------------------------|--------|---------|------|

| Decoupling Capacitance between VDD and VSS   | CDC1   | 0.1 * 3 | uF   |

| Decoupling Capacitance between VDDQ and VSSQ | CDC2   | 0.1 * 3 | υF   |

Note: 1. VDD and VDDQ pins are separated each other.

All VDD pins are connected inside the chip. All VDDQ pins are connected inside the chip.

Vss and VssQ pins are separated each other. All Vss pins are connected inside the chip.

CD-ROM(Edition 3.0) This Data Sheet is subject to change without notice.

DOCKE

RM

(C) 1996 Samsung Electronics Printed in Korea.

KM416S1120AT SDRAM

#### **DC CHARACTERISTICS**

(Recommended Operating Conditions Unless Otherwise Noted, TA = 0 to 70 °C)

| Parameter                                        | Symbol | Test Condition CAS                                                          |               |     | sion | Unit | Note |

|--------------------------------------------------|--------|-----------------------------------------------------------------------------|---------------|-----|------|------|------|

|                                                  |        |                                                                             | Latency       | -10 | -12  |      |      |

|                                                  |        | Burst Length =1                                                             | 3             | 105 | 100  | mA   |      |

| Operating Current                                | ICC1   | tRC ≥ tRC(min)                                                              | 2             | 95  | 90   |      | 1    |

|                                                  |        | IOL = 0 mA                                                                  | 1             | 90  | 85   |      |      |

| Precharge Standby Current                        | Icc2P  | CKE≤VIL(max), tcc=15ns                                                      |               | :   | 3    | mA   |      |

| in Power-down mode                               | Icc2PS | CKE & CLK≤ViL(max), tcc= ∞                                                  |               | :   | 2    |      |      |

| Precharge Standby Current                        | Icc2N  | CKE≥VIH(min), CS≥VIH(min), tcc=15n<br>Input signals are changed one time du |               | 2   | 25   | mA   |      |

| in Non power-down mode                           | lcc2NS | CKE≥VIH(min), CLK≤VIL(max), tcc=∞<br>Input signals are stable               |               | 1   | 8    |      |      |

| Active Standby Current                           | ІссзР  | CKE≤VIL(max), tcc=15ns 3                                                    |               |     |      |      |      |

| in power-down mode                               | Icc3PS | CKE & CLK≤Vi∟(max), tcc= ∞                                                  |               | 2   |      | mA   |      |

| Active Standby Current<br>in Non power-down mode | ICC3N  | CKE≥VIH(min), CS≥VIH(min), tcc=15n<br>Input signals are changed one time du | 30            |     | mt   |      |      |

| (One Bank Active)                                | Icc3NS | CKE≥V⊮(min), CLK≤V৷L(max), tcc=∞<br>Input signals are stable                | 15            |     | mA   |      |      |

|                                                  |        | lo∟≕ 0 mA                                                                   | 3             | 145 | 125  | mA   |      |

| Operating Current<br>(Burst Mode)                | Icc4   | Page Burst<br>All Banks activated                                           | 2             | 105 | 90   |      | 1, 2 |

|                                                  | Ì      | tccD=tccD(min)                                                              | 1             | 65  | 60   |      |      |

|                                                  |        |                                                                             | 3             | 95  | 90   | mA   |      |

| Refresh Current                                  | ICC5   | tRC ≥ tRC(min)                                                              | 2             | 90  | 85   |      | 3    |

|                                                  |        |                                                                             | 1             | 85  | 80   | ]    |      |

| Oalf Dafaada Ourrant                             | 1      |                                                                             |               | 2   |      | mA   | 4    |

| Self Refresh Current                             | ICC6   | CKE ≤ 0.2V                                                                  | (E ≤ 0.2V 250 |     | 50   | uA   | 5    |

Note: 1. Measured with outputs open.

2. Assumes minimum column address update cycle tCCD(min)

3. Refresh period is 32ms.

4. KM416S1120AT-G\*\*

5. KM416S1120AT-F\*\*

CD-ROM(Edition 3.0) This Data Sheet is subject to change without notice.

DOCKE

Δ

RM

Δ

(C) 1996 Samsung Electronics Printed in Korea.

Find authenticated court documents without watermarks at docketalarm.com.

KM416S1120AT SDRAM

#### AC OPERATING TEST CONDITIONS (VDD = 3.3V±0.3V, TA = 0 to 70 °C)

| Parameter                                | Value                 |

|------------------------------------------|-----------------------|

| AC input levels                          | VIH/ VIL= 2.4V / 0.4V |

| Input timing measurement reference level | 1.4V                  |

| Input rise and fall time                 | tr / tf = 1ns / 1ns   |

| Output measurement reference level       | 1.4V                  |

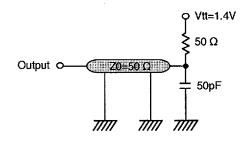

| Output load condition                    | See Fig. 2            |

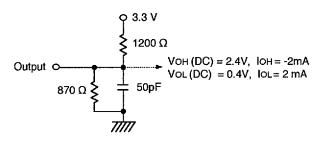

(Fig. 1) DC Output Load Circuit

(Fig. 2) AC Output Load Circuit

#### **OPERATING AC PARAMETER**

(AC operating conditions unless otherwise noted)

| Parameter                        |                        |           | Vera |              |      |      |

|----------------------------------|------------------------|-----------|------|--------------|------|------|

|                                  |                        | Symbol    | - 10 | sion<br>- 12 | Unit | Note |

| Row active to Row active delay   |                        | tRRD(min) | 20   | 24           | ns   | 1    |

| RAS to CAS delay                 |                        | tRCD(min) | 26   | 30           | ns   | 1    |

| Row precharge time               |                        | tRP(min)  | 26   | 30           | ns   | 1    |

|                                  |                        | tRAS(min) | 60   | 66           | ns   | 1    |

|                                  | Row active time        |           | 200  | 200          | us   |      |

| Row cycle time                   | ow cycle time tRC(min) |           | 96   | 100          | ns   | 1    |

| Last data in to new col. address | delay                  | tCDL(min) | 1    |              | CLK  | 2    |

| Last data in to Row precharge    |                        | tRDL(min) | 1    |              | CLK  | 2    |

| Last data in to burst stop       |                        | tBDL(min) | 0    |              | CLK  | 2    |

| Col. address to col. address de  | ay                     | tCCD(min) | 1    |              | CLK  | 3    |

| CASI                             |                        | tency= 3  | 2    |              |      |      |

| Number of valid output data      | CAS La                 | tency= 2  | 1    |              | ea   | 4    |

|                                  | CAS La                 | tency= 1  | (    | )            | Ţ    |      |

Note: 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time,

- and then rounding off to the next higher integer.

- 2. Minimum delay is required to complete write.

- 3. All parts allow every cycle column address change.

- 4. In case of Row precharge interrupt, Auto precharge and Read burst stop.

CD-ROM(Edition 3.0) This Data Sheet is subject to change without notice.

(C) 1996 Samsung Electronics Printed in Korea.

## DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

#### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.