#### 12.9 Timing

12.9.1 Overview. The successful interconnection of multivendor system components mandates that delay and bit loss be allocated fairly and realistically among the various system elements. The balance of this section defines the upper limits of delay and bit loss allocated to each component. These values allow proper operation with the worst-case system configuration of five levels of hubs, special links, maximum-length cable segments throughout the network, and colliding DTEs at extremes of the network.

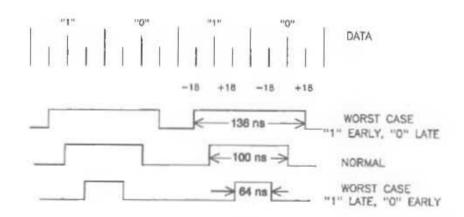

12.9.2 DTE Timing. DTE Initial Transmit Delay is the time from the first full transition (due to the first OUTPUT\_UNIT of preamble) from the MAC to the first full transition (after startup bit loss, if any) at the MDI. This delay shall not exceed 3BT. The start bit loss shall not exceed 1 bit.

DTEs shall correctly receive frames that are preceded by 13 or more bits of preamble plus 8 bits of <sfd>. There is a delay between the reception of signal at the PMA input of a DTE and operation of the deferral process in the MAC. Therefore, there is a window in which a DTE may fail to defer to a transmission even after it has arrived at the input. The DTE Deference Delay is the time from the receipt of the first transition of the preamble at the MDI until the last moment that the DTE might start transmitting at the MDI. This delay includes the following components:

- (1) The delay from the first input transition at the MDI to CARRIER\_ON at the PLS-MAC interface

- (2) The delay through the MAC processes from CARRIER\_ON to the last moment that a new transmission would miss being deferred

- (3) The delay from the first OUTPUT\_UNIT at the MAC-PLS interface to the first output transition at the MDI

The DTE Deference Delay shall be no more than 21BT.

The DTE Collision Shutdown Delay is the time from the first CVL or CVH arriving at the MDI of a transmitting DTE until that DTE transmits IDL at that interface. This time shall be no more than 26BT + jamSize=58BT. This limit shall not start until after the <sfd> has been transmitted.

12.9.3 Medium Timing. The Medium Transit Delay is the time from when a signal enters the medium until that signal leaves the medium. This delay shall not exceed 4BT.

12.9.4 Special Link Timing. The Special Link Transit Delay is the time from when a signal enters a special link until that signal leaves the special link. This delay shall not, exceed 15BT. The preamble leaving a special link shall be no more than 2 bit cells longer than the preamble sent to that special link and no more than 1 bit cell shorter than the preamble sent to that special link. For the purposes of these limits only, the first bit transmitted shall be considered part of the silence of the preceding IDL unless it meets the requirements for the succeeding bits specified in 12.5.3.1.1 and 12.5.3.1.2.

12.9.5 Hub Timing. Hub Startup Delay is the time from when the first bit cell of the preamble arrives at a hub until the first bit cell (also preamble) leaves that hub. This time shall be no greater than 12BT. The preamble sent by a hub shall be no more than 1 bit cell longer than the preamble sent to that hub or more than 4 bit cells shorter than the preamble sent to that hub. For the purposes of these limits only, the first bit transmitted shall be considered part of the silence of the preceding IDL unless it meets the requirements for the succeeding bits specified in 12.5.3.1,1 and 12.5.3.1,2.

Hub Idle Collision Startup Delay applies to any case in which CP arrives preceded by fewer (or no) bit times of preamble than the Hub Startup Delay. The time from arrival of the first bit cell (either preamble or CP) until the first bit cell leaves the hub shall be no greater than 12BT.

Hub Transit Delay is the time from the arrival of any bit cell at a hub to the transmission of the corresponding bit cell from the hub. This delay shall not exceed 9BT, excluding the cumulative effects of clock tolerance.

The transit (propagation) delay between the upward and downward sides of the Header Hub shall be negligible.

Hub Delay Stretch/Shrink is the increase or decrease in a hub's transit delay due to the effects of differing clock rates. The clock rate tolerance of 0.01% specified in 12.3.2.4.1 and the maximum frame size of 1518 octets specified in 4.4.2.2 yield a maximum stretch or shrink of  $(56 + 8 + 1518 \cdot 8) \cdot 0.01\% \cdot 2 < 3BT$ , both at any given hub and through an entire network.

Hub Collision Detect Delay is the time required for a hub to detect multiple incoming signals and initiate transmission of CP. The time until transmission of the first CVH or CVL shall be no greater than 21BT.

Hub Active Collision Startup Delay is the time from the arrival of the first CVH or CVL of a CP pattern at a hub that is repeating bit cells until transmission of the first CVH or CVL from the hub. This delay shall be no greater than 12BT in either the upward or downward direction.

Hub Collision Shutdown Delay is the time from IDL arriving at a hub that is passing on or generating CP until that hub starts transmitting IDL. This delay shall be limited to 9BT. The limit is relaxed to 25BT, however, for the upward side of a hub that is generating CP. This extra allowance is made to avoid requiring implementation of a separate <etd> detection mechanism in each port of the hub.

12.10 Safety. Implementors are urged to consult the relevant local, national, and international safety regulations to ensure compliance with the appropriate standards. EIA CB8-1981 (see Annex [12]) provides additional guidance concerning many relevant regulatory requirements.

Sound installation practice, as defined by applicable codes and regulations, shall be followed. ECMA-97 (see Annex [11]) describes safety requirements for local area networks.

12.10.1 Isolation. Each PMA/MDI interface lead shall be isolated from frame ground. This electrical separation shall withstand at least one of the following electrical strength tests:

- (1) 1500 V (rms) at 50 to 60 Hz for 60 s, applied as specified in Section 5.3.2 of IEC Publication 950 [8].

- (2) 2250 V (dc) for 60 s, applied as specified in Section 5.3.2 of IEC Publication 950 (see Reference [8]).

- (3) A sequence of ten 2400 V impulses of alternating polarity, applied at intervals of not less than 1 s. The shape of the impulses shall be 1.2/50 μs (1.2 μs virtual front time, 50 μs virtual time of half value), as defined in IEC Publication 60 (see Reference [11]).

There shall be no insulation breakdown, as defined in Section 5.3.2 of IEC Publication 950 (see Reference [8]), during the test. The resistance after the test shall be at least 2 M $\Omega$ , measured at 500 V (dc).

12.10.2 Telephony Voltages. The use of building wiring brings with it the possibility of wiring errors that may connect telephony voltages to 1BASE5 equipment. Other than voice signals (which are very low voltage), the primary voltages that may be encountered are the "battery" and ringing voltages. Although there is no universal standard that constrains them, the following maximums generally apply:

- (1) Battery voltage to an on-hook telephone line is about -56 V (dc) applied to the line through a balanced 400 Ω source impedance. This voltage is used to power the telephone instrument and detect the off-hook condition. Source inductance can cause large spikes on disconnect.

- (2) Battery voltage to an off-hook telephone line is also about -56 V (dc) applied to the line through a balanced 400 Ω source impedance, but most of the voltage appears across the source impedance because the telephone instrument's impedance is relatively much lower.

- (3) Ringing voltage is a composite signal. The first portion can be up to 175 V peak at 20 to 66 Hz, limited by a 100 Ω source resistance or a 400 to 600 Ω source inductive impedance. The second portion is -56 V (dc) limited by a 300 to 600 Ω source impedance. Large spikes can occur at the start and end of each ring.

Although 1BASE5 equipment is not required to survive such wiring hazards without damage, application of any of the above voltages shall not result in any safety hazard.

NOTE: Wiring errors may impose telephony voltages differentially across the 1BASES transmitters or receivers. Because the termination resistance likely to be present across a receiver's input is of substantially lower impedance than an off-hook telephone instrument, however, receivers will generally appear to the telephone system as off-hook telephones. Full ring voltages, therefore, will be applied for only short periods of time. Transmitters that are coupled using transformers will similarly appear like off-hook telephones (though perhaps a bit more slowly) due to low resistance of the transformer coil.

## 13. System Considerations for Multisegment 10 Mb/s Baseband Networks

13.1 Overview. This section provides information on building multisegment 10 Mb/s baseband networks within a single collision domain. The proper operation of a CSMA/CD network requires network size to be limited to control round-trip propagation delay to meet the requirements of 4.2.3.2.3 and 4.4.2.1, and the number of repeaters between any two Data Terminal Equipments (DTEs) to be limited in order to limit the shrinkage of the interpacket gap as it travels through the network. This section applies only to networks that contain 10BASE-T segments.

NOTE: Information on 10BASE-T is included to begin the process of developing this section. It is intended that 3.6.1 and 10.7.1 be merged into this section in the future and that any new 10BASE segments be added to this section.

## 13.2 Definitions. Terminology used in Section 13 is defined here:

collision domain. A single CSMA/CD network. If two or more Media Access Control (MAC) sublayers are within the same collision domain and both transmit at the same time, a collision will occur. MAC sublayers separated by a repeater are within the same collision domain. MAC sublayers separated by a bridge are within different collision domains.

link segment. The point-to-point full duplex medium connection between two and only two Medium-Dependent Interfaces (MDIs).

segment. The medium connection, including connectors, between MDIs in a CSMA/CD LAN.

13.3 Transmission System Model. The physical size of a 10BASE-T network, or mixed-media network containing 10BASE-T link segments, is constrained by the limits of individual network components. These limits include the following:

- (1) Cable length and its associated propagation time delay.

- (2) Delay of repeater units (start-up and steady-state).

- (3) Delay of MAUs (start-up and steady-state).

- (4) Interpacket gap shrinkage.

- (5) Delays within the DTE associated with the CSMA/CD access method.

Table 13-1 summarizes the delays for the various network media segments:

Table 13-1 Delays for Network Media Segments

| Media<br>Segment<br>Type | Maximum<br>Number of<br>MAUs per<br>Segment | Maximum<br>Segment<br>Length<br>(m) | Minimum<br>Medium<br>Propagation<br>Velocity* | Maximum<br>Medium<br>Dalay per<br>Segment<br>(ns) |

|--------------------------|---------------------------------------------|-------------------------------------|-----------------------------------------------|---------------------------------------------------|

| Coaxisi                  |                                             |                                     |                                               |                                                   |

| 10BASE5                  | 100                                         | 500                                 | 0.77 c                                        | 2165                                              |

| 10BASE2                  | 30                                          | 185                                 | 0.65 c                                        | 950                                               |

| Link                     |                                             |                                     |                                               |                                                   |

| FOIRL                    | 2                                           | 1000                                | 0.66 c                                        | 5000                                              |

| 10BASE-T                 | 2                                           | 100 <sup>†</sup>                    | 0.59 c                                        | 1000                                              |

| AUI‡                     | 1 DTF/1 MAU                                 | 50                                  | 0.65 c                                        | 257                                               |

$c = 3 \times 10^8 \text{ m/s}$

<sup>‡</sup>AUI is not a segment,

<sup>&</sup>lt;sup>†</sup>Actual maximum segment length depends on cable characteristics; see 14.1.1.3.

In addition, Table 14-1 summarizes the delays for the 10BASE-T MAU; Section 8, the delays for the 10BASE5 MAU; Section 10, the delays for the 10BASE2 MAU; and Section 9, the delays of the fiber optic inter-repeater link (FOIRL) and the repeater.

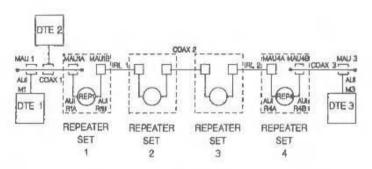

The following network topology constraints apply for 10BASE-T networks as well as mixed-media networks containing 10BASE-T link segments:

- (1) Repeater sets are required for all segment interconnection.

- (2) MAUs that are part of repeater sets count toward the maximum number of MAUs on a segment.

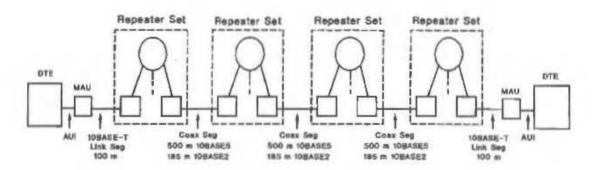

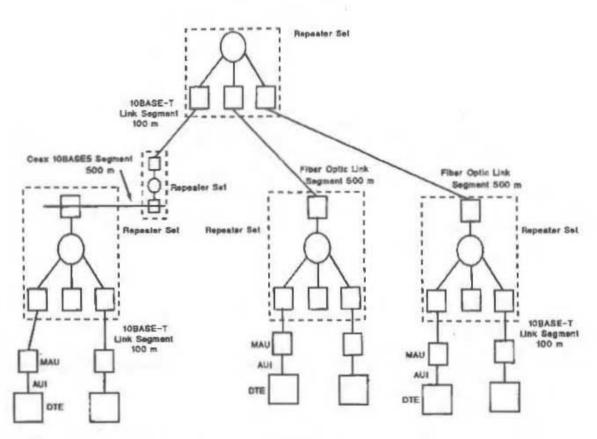

- (3) The transmission path permitted between any two DTEs may consist of up to five segments, four repeater sets (including optional AUIs), two MAUs, and two AUIs.

- (4) When a network path consists of four repeater sets and five segments, up to three of the segments may be coaxial and the remainder must be link segments (Figs 13-1 and 13-2). When five segments are present, each FOIRL link segment should not exceed 500 m.

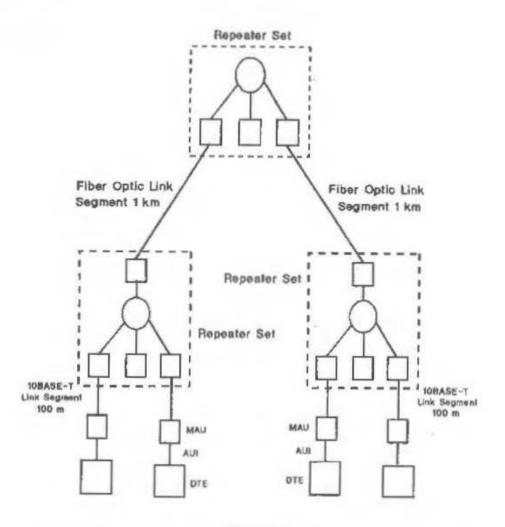

- (5) When a network path consists of three repeater sets and four segments, the maximum allowable length of the FOIRL segments is 1000 m each, as specified in 9.9 (Fig 13-3).

Fig 13-1 Maximum Transmission Path with Three Coaxial Cable Segments

Fig 13-2

Example of Maximum Transmission Path Using Coaxial Cable Segments,

10BASE-T Link Segments, and Fiber Optic Link Segments

Fig 13-3

Example of Maximum Transmission Path with Three Repeater Sets,

Four Link Segments (Two are 100 m 10BASE-T and Two are 1 km Fiber)

# 14. Twisted-Pair Medium Attachment Unit (MAU) and Baseband Medium, Type 10BASE-T

#### 14,1 Scope

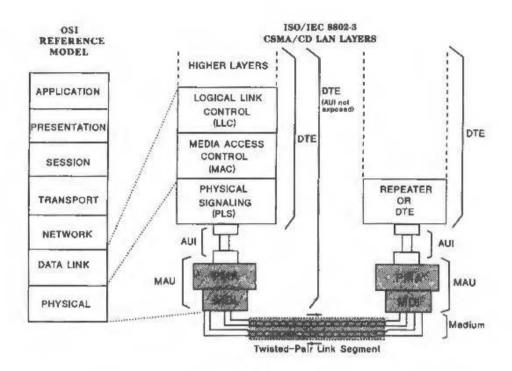

14.1.1 Overview. Section 14 defines the functional, electrical, and mechanical characteristics of the Type 10BASE-T MAU and one specific medium for use with that MAU. The relationship of this specification to the entire ISO/IEC 8802-3 CSMA/CD Local Area Network Specification is shown in Fig 14.1. The purpose of the MAU is to provide a simple, inexpensive, and flexible means of attaching devices to the medium.

This MAU and medium specification is aimed primarily at office applications where twisted-pair cable is often installed. Installation and reconfiguration simplicity is allowed by the type of cable and connectors used.

The 10BASE-T specification builds upon Sections 1 through 7 and Section 9 of this standard.

#### 14.1.1.1 Medium Attachment Unit (MAU). The MAU has the following general characteristics:

- Enables coupling the Physical Signaling (PLS) sublayer by way of the Attachment Unit Interface (AUI) to the baseband twisted-pair link defined in Section 14.

- (2) Supports message traffic at a data rate of 10 Mb/s.

- (3) Provides for operating over 0 m to at least 100 m (328 ft) of twisted pair without the use of a repeater.

- (4) Permits the Data Terminal Equipment (DTE) or repeater to confirm operation of the MAU and availability of the medium,

- (5) Supports network configurations using the CSMA/CD access method defined in ISO/IEC 8802-3:1993 with baseband signaling.

- (6) Supports a point-to-point interconnection between MAUs and, when used with repeaters having multiple ports, supports a star wiring topology.

- (7) Allows incorporation of the MAU within the physical bounds of a DTE or repeater.

- 14.1.1.2 Repeater Unit. The repeater unit is used to extend the physical system topology and provides for coupling two or more segments. Repeaters are an integral part of all 10BASE-T networks with more than two DTEs (see Figs 13-1 and 13-2). The repeater unit is defined in Section 9. Multiple repeater units are permitted within a single collision domain to provide the maximum connection path length specified in Section 13. The repeater unit is not a DTE and therefore has slightly different requirements for its attached MAUs, as defined in 9.4.1. Repeater sets with 10BASE-T MAUs are required to provide the autopartition/reconnection algorithm on those ports, as specified in 9.6.6.2.

- 14.1.1.3 Twisted-Pair Media. The medium for 10BASE-T is twisted-pair wire. The performance specifications of the simplex link segment are contained in 14.4. This wiring normally consists of 0.4 mm to 0.6 mm diameter [26 AWG to 22 AWG] unshielded wire in a multipair cable. The performance specifications are generally met by 100 m of 0.5 mm telephone twisted pair. Longer lengths are permitted providing the simplex link segment meets the requirements of 14.4. A length of 100 m, the design objective, will be used when referring to the length of a twisted-pair link segment.

- 14.1.2 Definitions. This section defines the terminology specific to Type 10BASE-T MAUs and their application to repeater units.

bit time (BT). The duration of one bit symbol (1/BR).

collision. A condition that results from concurrent transmissions from multiple signal sources.

common-mode voltage. The instantaneous algebraic average of two signals applied to a balanced circuit, both signals referred to a common reference. Also called longitudinal voltage.

Fig 14-1

10BASE-T Relationship to the ISO Open Systems Interconnection (OSI)

Reference Model and the IEEE 802.3 CSMA/CD LAN Model

cross connect. A group of connection points often wall- or rack-mounted in a wiring closet, used to mechanically terminate and interconnect twisted-pair building wiring.

differential-mode voltage. The instantaneous algebraic difference between two signals applied to a balanced circuit, both signals referred to a common reference. Also called metallic voltage.

Medium-Dependent Interface (MDI). The mechanical and electrical interface between the twisted-pair link segment and the MAU.

Physical Medium Attachment (PMA) sublayer. The portion of the MAU that contains the functional circuitry.

Physical Signaling (PLS) sublayer. The portion of the Physical Layer, contained within the DTE, that provides the logical and functional coupling between the MAU and the Data Link Layer.

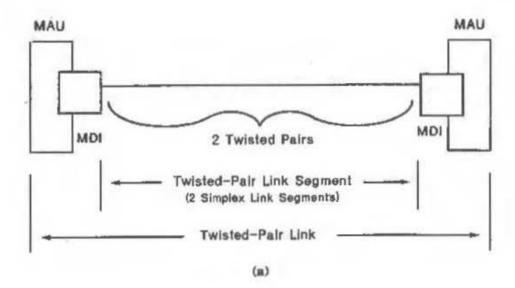

simplex link segment. A two-wire path between two MAUs including the terminating connectors, consisting of one or more twisted pairs joined serially with appropriate connection devices, for example, patch fields and wall plates (see Fig 14-2).

twisted pair. Two continuous insulated conductors helically twisted around one another (see Fig 14-2).

twisted-pair cable. A group of twisted pairs within a single protective sheath.

twisted-pair cable binder group. A group of twisted pairs within a cable that are bound together. Large telephone cables have multiple binder groups with high interbinder group near-end crosstalk loss.

twisted-pair link. A twisted-pair link segment and its two attached MAUs (see Fig 14-2).

Fig 14-2 Twisted-Pair Link

twisted-pair link segment (duplex link segment). Two simplex link segments for connecting two MAUs (see Fig 14-2).

14.1.3 Application Perspective. This section states the broad objectives and assumptions underlying the specifications defined throughout Section 14.

#### 14.1.3.1 Objectives

- (1) Provide the physical means for communication between LAN Data Link Layer Entities.

- (2) Ensure compatibility of independently developed physical and electrical interfaces.

- (3) Provide a communication channel with a mean bit error rate, at the physical layer service interface of less than one part in 10<sup>8</sup>.

- (4) Provide for ease of installation and service.

- (5) Ensure that fairness of DTE access is not compromised.

- (6) Provide for low-cost networks, as related to both equipment and cabling.

- (7) Make use of telephone twisted-pair building wiring and telephony wiring practices.

14.1.3.2 Compatibility Considerations. All implementations of the twisted-pair link shall be compatible at the MDI. The MAU and the medium are defined to provide compatibility among devices designed by different manufacturers. Designers are free to implement circuitry within the MAU in an application-dependent manner provided the MDI and AUI (when implemented) specifications are met.

14.1.3.3 Mode of Operation. The 10BASE-T MAU is capable of operating in *normal* mode only (see 7.1.4). The MAU shall not operate in *monitor* mode.

When normal mode is in operation, the MAU functions as a direct connection between the medium and the DTE or repeater. Data from the DTE or repeater is output to one of the simplex link segments of the link segment, and data received on the other simplex link segment is input to the DTE or repeater.

14.1.4 Relationship to PLS and AUI. A close relationship exists between Section 14 and Section 7. Section 14 specifies the physical medium parameters and the PMA logical functions residing in the physical MAU. The MAU provides services to the PLS defined in Section 7 by means of the AUI. 10BASE-T MAUs support a subset of the AUI services specified in Section 7. 10BASE-T MAUs do not support the optional isolate function, the optional CO circuit, or the optional CS1 signal on the CI circuit.

The design of an external MAU component requires the use of both Section 14 and Section 7 for the PLS and AUI specifications.

The figures and numerous textual references throughout Section 14 refer to terminology associated with the AUI (that is, DO, DI, and CI). Since an embodiment of the 10BASE-T MAU does not require the implementation of an AUI, the DO, DI, and CI circuits may not physically exist. However, they are logically present and MAU operation is defined in terms of them.

14.2 MAU Functional Specifications. The MAU provides the means by which signals on the three AUI signal circuits to and from the DTE or repeater and their associated interlayer messages are coupled to the twisted-pair link segment. The MAU provides the following functional capabilities to handle message flow between the DTE or repeater and the twisted-pair link segment:

- (1) Transmit function, Provides the ability to transfer Manchester-encoded data from the DO circuit to the TD circuit. While not sending Manchester-encoded data on the TD circuit, the MAU sends an idle signal, TP\_IDL, on the TD circuit.

- (2) Receive function. Provides the ability to transfer Manchester-encoded data from the RD circuit to the DI circuit. While not sending Manchester-encoded data on the DI circuit, the MAU sends an idle signal, IDL, on the DI circuit.

- (3) Loopback function. Provides the ability to transfer Manchester-encoded data from the DO to the DI circuit when the MAU is sending Manchester-encoded data to the TD circuit.

- (4) Collision Presence function. Provides the ability to detect simultaneous occurrence of Manchesterencoded data on the RD and DO circuits and to report such an occurrence as a collision.

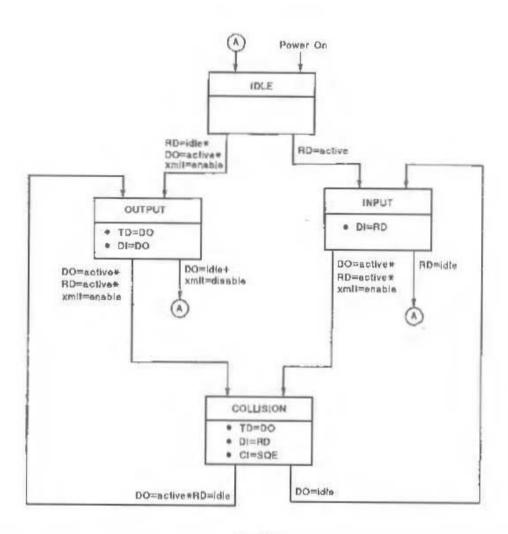

- (5) signal\_quality\_error Message (SQE) Test function. Provides the ability to indicate to the DTE that the Collision Presence function is operational and that the signal\_quality\_error message can be sent by the MAU.

- (6) Jabber function. Provides the ability to prevent abnormally long reception of Manchester-encoded data on the DO circuit from indefinitely disrupting transmission on the network. While such a condition is present, transfer of Manchester-encoded data by the Transmit and Loopback functions is disabled.

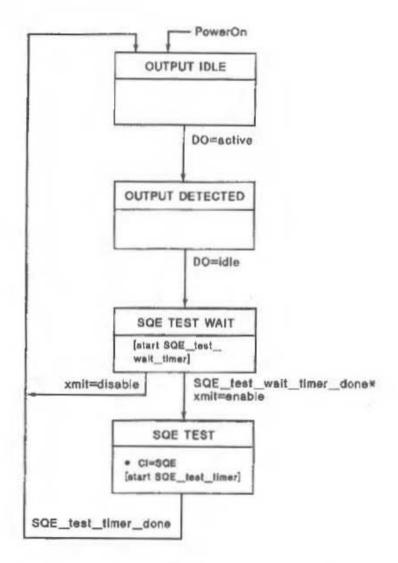

- (7) Link Integrity Test function. Provides the ability to protect the network from the consequences of failure of the simplex link attached to the RD circuit. While such a failure is present, transfer of Manchester-encoded data by the Transmit, Receive, and Loopback functions is disabled.

- 14.2.1 MAU Functions. The MAU shall provide the Transmit, Receive, Loopback, Collision Presence, Jabber, and Link Integrity Test functions. The SQE Test function shall be performed by MAUs that are connected to DTEs and shall not be performed by MAUs that are connected to repeaters. A capability may be provided in the MAU to activate or inhibit the SQE Test function. It is not required that a MAU determine that it is connected to either a DTE or a repeater and automatically activate or inhibit the SQE Test function.

- 14.2.1.1 Transmit Function Requirements. The MAU shall receive the signals on the DO circuit and send them to the TD circuit of the MDI. A positive signal on the A lead relative to the B lead of the DO circuit shall result in a positive signal on the TD+ (Transmit Data +) lead of the MDI with respect to the TD-lead.

At the start of a packet transmission, no more than 2 bits may be received from the DO circuit and not transmitted on the TD circuit. In addition, it is permissible for the first bit sent to contain phase violations or invalid amplitude. All subsequent bits of the packet shall be reproduced with the differential voltage specified in 14.3.1.2.1 and with no more jitter than is specified in 14.3.1.2.3. The second bit transmitted on the TD circuit shall be transmitted with the correct timing and signal levels. The steady-state propagation delay between the DO circuit input and the TD circuit shall not exceed 2 BT.

For any two packets that are separated by  $9.6~\mu s$  or less, the start-up delay (bit loss plus steady-state propagation delay) of the first packet shall not exceed that of the second packet by more than 2~BT.

Whenever data is not being transmitted on the TD circuit, an idle signal, TP\_IDL, shall be transmitted on the TD circuit. TP\_IDL is a start of idle, as defined in 14.3.1.2.1, followed by a repeating sequence of a 16 ms ± 8 ms period of silence (the time where the differential voltage remains at 0 mV ± 50 mV) and a link test pulse (see 14.3.1.2.1). Following a packet and start of idle, the repeating sequence shall start with a period of silence.

Transmission of TP\_IDL may be terminated at any time with respect to the link test pulse. It shall be terminated such that no more than the first transmitted bit of a packet is corrupted, and with no more delay than is specified for bit loss and steady-state propagation.

14,2.1.2 Receive Function Requirements. The MAU shall receive the signals on the RD circuit of the MDI and send them to the DI circuit. A positive signal on the RD+ (Receive Data+) lead relative to the RD- lead of the MDI shall result in a positive signal on the A lead with respect to the B lead of the DI circuit.

At the start of a packet reception from the RD circuit, no more than 5 bits may be received on the RD circuit and not transmitted onto the DI circuit. In addition, it is permissible for the first bit sent on the DI circuit to contain phase violations or invalid data; however, all successive bits of the packet shall be sent with no more than the amount of jitter specified in 14.3.1.3.1. The steady-state propagation delay between the RD circuit and the DI circuit shall not exceed 2 BT.

For any two packets that are separated by 9.6 µs or less, the start-up delay of the first packet shall not exceed that of the second packet by more than 2 BT.

- 14.2.1.3 Loopback Function Requirements. When the MAU is transmitting on the TD circuit and is not receiving RD\_input messages (14.2.2.4) on the RD circuit, the MAU shall transmit on the DI circuit the signals received on the DO circuit in order to provide loopback of the transmitted signal. At the start of packet transmission on the TD circuit, no more than 5 bits of information may be received from the DO circuit and not transmitted to the DI circuit. In addition, it is permissible for the first bit sent on the DI circuit to contain phase violations or invalid data; however, all successive bits of the packet shall meet the jitter specified in 14.3.1.3.1 (that is, 13.5 ns plus 1.5 ns). The steady-state propagation delay between the DO circuit and the DI circuit shall not exceed 1 BT.

- 14.2.1.4 Collision Presence Function Requirements. The MAU shall detect as a collision the simultaneous occurrence of activity on the DO circuit and the RD circuit while in the Link Test Pass state. While a collision is detected, a CSO signal (see 7.3.1.2) shall be sent on the CI circuit. The signal shall be

presented to the CI circuit no more than 9 BT after the occurrence of a collision. The signal shall be deasserted within 9 BT after the DO circuit or the RD circuit changes from active to idle.

When CS0 is asserted on the CI circuit due to a collision, the data on the RD circuit shall be sent to the DI circuit within 9 BT.

When the RD circuit changes from active to idle and data is present on the DO circuit, the data on the DO circuit shall be sent to the DI circuit within 9 BT.

The signal presented on the CI circuit in the absence of collision, SQE test, or Jabber shall be the IDL signal.

14.2.1.5 signal\_quality\_error Message (SQE) Test Function Requirements. The SQE Test function shall be performed by MAUs that are connected to DTEs and shall not be performed by MAUs that are connected to repeaters. When the SQE test is performed, the MAU shall send CSO on the CI circuit for a time 'SQE\_test' beginning a time 'SQE\_test\_wait' after the last positive transition of a packet on the DO circuit. The value of 'SQE\_test' shall be 10 BT ± 5 BT and the value of 'SQE\_test\_wait' shall be between 0. µs and 1.6 µs. This function should use as much of the normal collision detection and signaling circuitry as possible without introducing extraneous signals on the TD circuit or the DI circuit.

The CSO signal shall not be sent by the SQE Test function while in any of the Link Test Fail states.

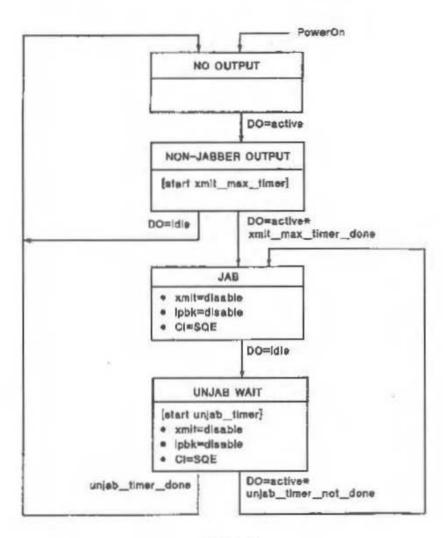

14.2.1.6 Jabber Function Requirements. The MAU shall contain a self-interrupt capability to prevent an illegally long transmission by a DTE from permanently disrupting transmission on the network and to disable loopback to the DI circuit (Fig 14-5). The MAU shall provide a window 'xmit\_max' during which time the Transmit function may continuously transmit TD\_output messages to the TD circuit. The value of 'xmit\_max' shall be between 20 ms and 150 ms. If a transmission exceeds this duration, the Jabber function shall inhibit the Loopback function and the transmission of TD\_output messages by the Transmit function, and shall send the CS0 signal on the CI circuit. This shall continue until output\_idle has been continuously present on the DO circuit for a time 'unjab'. The value of 'unjab' shall be 0.5 ms ± 0.25 s.

It is permissible to activate the Jabber function when the TD circuit transmitter is sending TD\_output messages for longer than 'xmit\_max'.

The MAU shall not activate its Jabber function when the repeater's MAU Jabber Lockup Protection function operates at its longest permitted time as specified in 9.6.5.

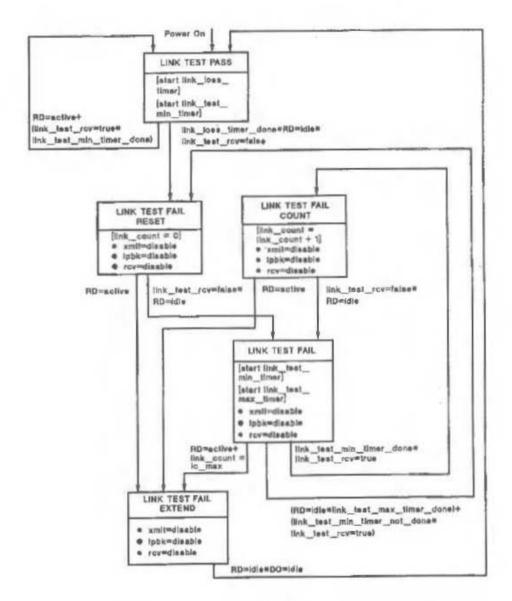

14.2.1.7 Link Integrity Test Function Requirements. In order to protect the network from the consequences of a simplex link segment failure, the MAU shall monitor the RD circuit for RD\_input and link test pulse activity. If neither RD\_input nor a link test pulse is received for a time 'link\_loss', the MAU shall enter the Link Test Fail state and cause the input\_idle message to be sent on the DI circuit and the TD\_idle message to be sent on the TD circuit (Fig 14-6). The value of 'link\_loss' shall be between 50 ms and 150 ms. When RD\_input or a number 'lc\_max' of consecutive link test pulses is received on the RD circuit, the MAU shall exit the Link Test Fail state. The value of 'lc\_max' shall be between 2 and 10 inclusive.

Only link test pulses that occur within time link test max' of each other shall be considered consecutive. The value of link test max' shall be between 25 ms and 150 ms. In addition, detected pulses that occur within a time link test min' of a previous pulse or packet shall be ignored while in the Link Test Pass state. In the Link Test Fail state, such pulses shall reset the counted number of consecutive link test pulses to zero. The value of link test min' shall be between 2 ms and 7 ms. Re-enabling shall be deferred until the signals on the RD and DO circuits become idle. The MAU shall not detect a link test pulse as RD\_input. Additionally, a MAU may exit the Link Test Fail Extend state and enter the Link Test Pass state when the RD circuit becomes idle and the Jabber function has disabled transmission on the TD circuit.

While the MAU is not in the Link Test Pass state, the Link Integrity Test function shall disable the bit transfer of the Transmit, Receive, and Loopback functions, and the Collision Presence and SQE Test functions.

At PowerOn, in place of entering the Link Test Pass state as shown in Fig 14-6, a MAU may optionally enter the Link Test Fail Reset state.

If a visible indicator is provided on the MAU to indicate the link status, it is recommended that the color be green and that the indicator be labeled appropriately. It is further recommended that the indicator be on when the MAU is in the Link Test Pass state and off otherwise.

14.2.2 PMA Interface Messages. The messages between the PLS in the DTE and the PMA in the MAU shall comply with the PMA interface messages described in 7.2.1. These messages also are used in repeater

unit to PMA communication. These and the messages between the PMAs over the MDI are summarized below.

14.2.2.1 PLS to PMA Messages. The following messages are sent by the PLS in the DTE or repeater to the PMA in the MAU:

| Message     | Circuit | Signal  | Meaning              |

|-------------|---------|---------|----------------------|

| output      | DO      | CD1,CD0 | Output information   |

| output_idle | DO      | IDL     | No data to be cutput |

14.2.2.2 PMA to PLS Messages. The following messages are sent by the MAU to the PLS in the DTE or repeater:

| Message              | Circuit | Signal  | Meaning                     |

|----------------------|---------|---------|-----------------------------|

| input                | DI      | CD1,CD0 | Input information           |

| input_idle           | DI      | IDL     | No information to input     |

| mau_available        | CI      | IDL     | MAU is available for output |

| signal_quality_error | CI      | CS0     | Error detected by MAU       |

Retiming of CD1 and CD0 signals within the MAU is neither prohibited nor required. Considerable jitter may be present (see 14.3.1.3.1).

### 14.2.2.3 PMA to Twisted-Pair Link Segment Messages

| Message   | Circuit | Signal  | Meaning                  |

|-----------|---------|---------|--------------------------|

| TD_output | TD      | CD1,CD0 | Output information       |

| TD_idle   | TD      | TP_IDL  | No information to output |

The encoding for TP\_IDL is defined in 14.2.1.1. The encoding for CD1 and CD0 is the same as that used on the AUI. Retiming of CD1 and CD0 signals within the MAU is neither prohibited nor required.

#### 14.2.2.4 Twisted-Pair Link Segment to PMA Messages

| Message  | Circuit | Signal  | Meaning                 |

|----------|---------|---------|-------------------------|

| RD_input | RD      | CD1,CD0 | Input information       |

| RD idle  | RD      | TP IDL  | No information to input |

The encoding for TP\_IDL is defined in 14.2.1.1. The encoding for CD1 and CD0 is the same as that used on the AUI.

14.2.2.5 Interface Message Time References. Delay and bit loss specifications are measured from the occurrence of messages at the MDI and MAU AUI. The following describes the point where each message starts:

| Message              | Reference                                                 |

|----------------------|-----------------------------------------------------------|

| output               | leading bit cell boundary (BCB) of first valid CD1 or CD0 |

| output_idle          | last positive-going transition prior to start of IDL      |

| input                | leading BCB of first valid CD1 or CD0                     |

| input_idle           | last positive-going transition prior to start of IDL      |

| signal_quality_error | first transition of valid amplitude                       |

| mau_available        | last positive-going transition prior to start of IDL      |

| TD_output            | leading BCB of first valid CD1 or CD0                     |

| $TD_idle$            | last positive-going transition prior to start of TP_IDL   |

| RD_output            | leading BCB of first valid CD1 or CD0                     |

| RD_idle              | last positive-going transition prior to start of TP_IDL   |

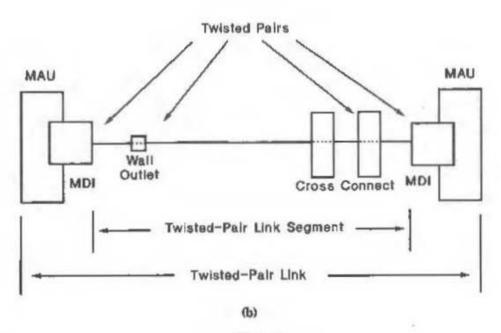

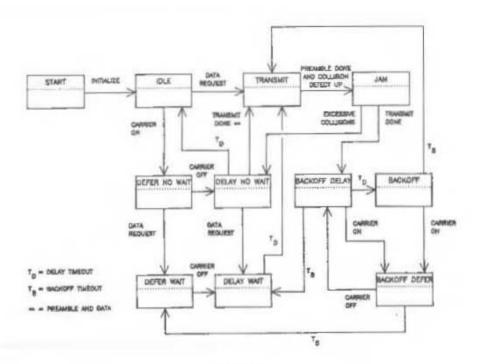

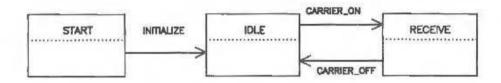

14.2.3 MAU State Diagrams. The state diagrams of Figs 14-3, 14-4, 14-5, and 14-6 depict the full set of allowed MAU state functions relative to the circuits of the AUI and MDI.

The notation used in the state diagrams follows the conventions in 1.2.1. The variables and timers used in the state diagrams are defined in the following sections.

14.2.3.1 State Diagram Variables. Variables are used in the state diagrams to indicate the status of MAU inputs and outputs, to control MAU operation, and to pass state information between functions.

In the variable definitions, the name of the variable is followed by a brief description of the variable and a list of values the variable may take. For those variables that are state diagram outputs, one value will be identified as the default. The variable has the default value when no active state contains a term assigning a different value.

For example, the variable 'xmit' has the value 'disable' whenever the Jabber function or the Link Integrity Test function is in a state that asserts 'xmit=disable'. The variable has the default value 'enable' all other times.

The variables used in the state diagrams are defined as follows:

DI. Controls the signal sent by the MAU on the DI circuit.

Values: idle; MAU is sending input\_idle, IDL (default).

DO; MAU sends the signal received on the DO circuit.

lpbk = disable overrides this and causes input\_idle to be sent.

RD; MAU sends the signal received on the RD circuit.

rcv = disable overrides this and causes input\_idle to be sent.

CI. Controls the signal sent by the MAU on the CI circuit.

Values: idle; MAU sends mau\_available, IDL (default).

SQE; MAU sends signal quality error, CS0.

DO. Status of the signal received by the MAU on the DO circuit.

Values: idle; MAU is receiving output\_idle, IDL.

active; MAU is receiving output, CD0 or CD1.

TD. Controls the signal sent by the MAU on the TD circuit.

Values: idle; MAU sends TD\_idle, TP\_IDL (default).

DO; MAU sends the signal received on the DO circuit.

xmit = disable overrides this and causes TD\_idle to be sent.

RD. Status of the signal received by the MAU on the RD circuit.

Values: idle; MAU is receiving silence or a link test pulse.

active; MAU is detecting signals which most the requirements of 14.3.1.3.2.

link\_test\_rcv. Status of the link test signal received by the MAU on the RD circuit.

Values:

false, MAU is not detecting a link test pulse.

true; MAU is detecting a link test pulse.

link\_count. Count of the number of consecutive link test pulses received while in the Link Fail state.

Values: non-negative integers.

lc\_max. The number of consecutive link test pulses required before exit from the Link Fail state.

Values: positive integer between 2 and 10 inclusive.

rcv. Controls the path from the RD circuit to the DI circuit.

Values: enable; receive.

enable; receive is enabled (default).

disable; the output to the DI circuit is input\_idle when DI=RD.

lpbk. Controls the path from the DO circuit to the DI circuit.

Values:

enable; loopback is enabled (default).

disable; the output to the DI circuit is input\_idle when DI=DO.

xmit. Controls the path from the DO circuit to the TD circuit.

Values:

enable; transmit is enabled (default).

disable; transmit is disabled and the signal sent on the TD circuit is TP\_IDL,

Fig 14-3

MAU Transmit, Receive, Loopback, and Collision Presence Functions State Diagram

Fig 14-4

signal\_quality\_error Message Test Function State Diagram

14.2.3.2 State Diagram Timers. All timers operate in the same fashion. A timer is reset and starts counting upon entering a state where 'start x\_timer' is asserted. Time 'x' after the timer has been started, 'x\_timer\_done' is asserted and remains asserted until the timer is reset. At all other times, 'x\_timer\_not\_done' is asserted.

When entering a state where 'start x\_timer' is asserted, the timer is reset and restarted even if the entered state is the same as the exited state; for example, when in the Link Test Pass state of the Link Integrity Test function state diagram, the 'link\_loss\_timer' and the 'link\_test\_min\_timer' are reset each time the term 'RD = active + (link\_test\_rcv=true \* link\_test\_min\_timer\_done)' is satisfied.

link\_loss\_timer. Timer for longest time input activity can be missing before the MAU determines that a link fail condition exists (14.2.1.7).

Fig 14-5 Jabber Function State Diagram

link\_test\_min\_timer. Timer for the minimum time between valid link test pulses (14.2.1.7).

link\_test\_max\_timer. Timer for maximum time input activity can be missing before Link Fail state is exited (14.2.1.7).

SQE\_test\_timer. Timer for the duration of the CSO signal used for the SQE Test function (14.2.1.5).

SQE\_test\_wait\_timer. Timer for the delay from end of packet to the start of the CSO signal used for the SQE Test function (14.2.1.5).

xmit\_max\_timer. Timer for excessively long transmit time (14,2,1,6).

unjab\_timer. Timer for the length of time the DO circuit must be continuously idle to allow transmission to be re-enabled (14.2.1.6).

Fig 14-6 Link Integrity Test Function State Diagram

14.3 MAU Electrical Specifications. This section defines the electrical characteristics of the MAU at the MDI and the AUI. The MAU shall also meet the AUI requirements specified in Section 7 when the AUI is implemented.

Additional information relative to conformance testing is given in A4.3.

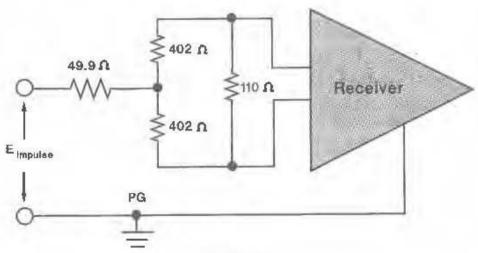

The ground for all common-mode tests is circuit PG, Protective Ground of the AUI. In implementations without an AUI, chassis ground is used as circuit PG. All components in test circuits shall be  $\pm 1\%$  unless otherwise stated.

#### 14.3.1 MAU-to-MDI Interface Characteristics

14.3.1.1 Isolation Requirement. The MAU shall provide isolation between the DTE Physical Layer circuits including frame ground and all MDI leads including those not used by 10BASE-T. This electrical separation shall withstand at least one of the following electrical strength tests.

- (1) 1500 V rms at 50 Hz to 60 Hz for 60 s, applied as specified in Section 5.3.2 of IEC Publication 950 [8].

- (2) 2250 Vdc for 60 s, applied as specified in Section 5.3.2 of IEC Publication 950 [8].

- (3) A sequence of ten 2400 V impulses of alternating polarity, applied at intervals of not less than 1 s. The shape of the impulses shall be 1.2/50 μs (1.2 μs virtual front time, 50 μs virtual time of half value), as defined in IEC Publication 60 [11].

There shall be no insulation breakdown, as defined in Section 5.3.2 of IEC Publication 950 [8], during the test. The resistance after the test shall be at least  $2 M\Omega$ , measured at 500 Vdc.

14.3.1.2 Transmitter Specifications. The MAU shall provide the Transmit function specified in 14.2.1.1 in accordance with the electrical specifications of this section.

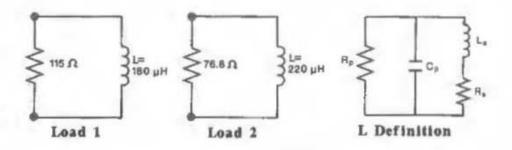

Where a load is not specified, the transmitter shall meet requirements of this section when connected to a 100  $\Omega$  resistive load. The use of 100  $\Omega$  terminations simplifies the measurement process when using 50  $\Omega$  measurement equipment as 50  $\Omega$  to 100  $\Omega$  impedance matching transformers are readily available.

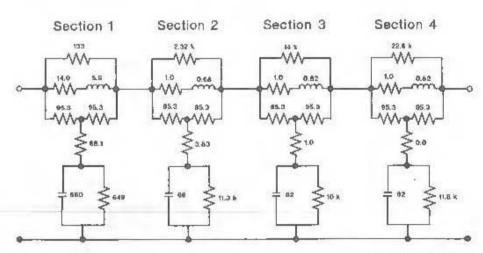

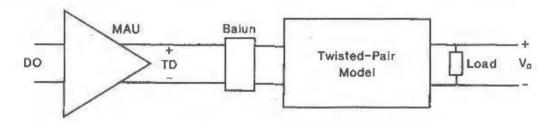

Some tests in this section require the use of an equivalent circuit that models the distortion introduced by a simplex link segment. This twisted-pair model shall be constructed according to Fig 14-7 with component tolerances as follows: Resistors,  $\pm 1\%$ ; capacitors,  $\pm 5\%$ ; inductors,  $\pm 10\%$ . Component tolerance specifications shall be met from 5.0 MHz to 15 MHz. For all measurements, the TD circuit shall be connected through a balun to Section 1 and the signal measured across a load connected to Section 4 of the model. The balun shall not affect the peak differential output voltage specified in 14.3.1.2.1 by more than 1% when inserted between the 100  $\Omega$  resistive load and the TD circuit.

The insertion loss of the twisted-pair model when measured with a 100  $\Omega$  source and 100  $\Omega$  load shall be between 9.70 dB and 10.45 dB at 10 MHz, and between 6.50 dB and 7.05 dB at 5 MHz.

NOTE: Care must be taken that layout and parasitics do not exceed R, C, and L tolerance values.

Resistances are in  $\Omega$ Capacitances are in pF Inductances are in  $\mu$ H

Fig 14-7 Twisted-Pair Model

14.3.1.2.1 Differential Output Voltage. Some of the text and figures of this section describe the differential voltage in terms of magnitudes. These requirements apply to negative as well as positive pulses.

The peak differential voltage on the TD circuit when terminated with a 100  $\Omega$  resistive load shall be between 2.2 V and 2.8 V for all data sequences. When the DO circuit is driven by an all-ones Manchester-encoded signal, any harmonic measured on the TD circuit shall be at least 27 dB below the fundamental.

NOTE: The specification on maximum spectral components is not intended to ensure compliance with regulations concerning RF emissions. The implementor should consider any applicable local, national, or international regulations. Additional filtering of spectral components may therefore be necessary.

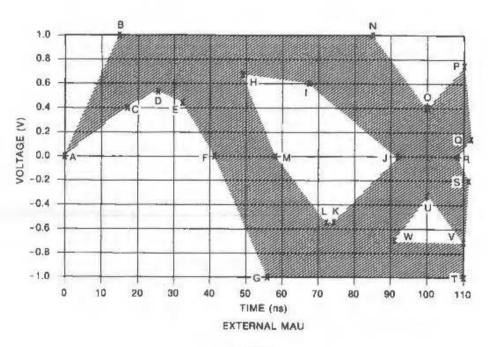

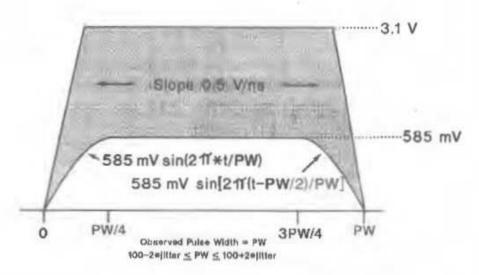

The output signal  $V_0$ , is defined at the output of the twisted-pair model as shown in Fig 14-8. The TD transmitter shall provide equalization such that the output waveform shall fall within the template shown in Fig 14-9 for all data sequences. Voltage and time coordinates for inflection points on Fig 14-9 are given in Table 14-1. (Zero crossing points are different for external and internal MAUs. The zero crossings depicted in Fig 14-9 apply to an external MAU.) The template voltage may be scaled by a factor of 0.9 to 1.1 but any scaling below 0.9 or above 1.1 shall not be allowed. The recommended measurement procedure is described in A4.3.1. Time t=0 on the template represents a zero crossing, with positive slope, of the output waveform. During this test the twisted-pair model shall be terminated in 100  $\Omega$  and driven by a transmitter with a Manchester-encoded pseudo-random sequence with a minimum repetition period of 511 bits.

Fig 14-8 Differential Output Voltage Test

Fig 14-9 Voltage Template

Table 14-1 Voltage Template Values for Fig 14-9

| Time (ns) |              |              |             |  |  |

|-----------|--------------|--------------|-------------|--|--|

| Reference | External MAU | Internal MAU | Voltage (V) |  |  |

| A         | 0            | 0            | 0           |  |  |

| В         | 15           | 15           | 1.0         |  |  |

| C         | 15           | 15           | 0.4         |  |  |

| D         | 25           | 25           | 0.55        |  |  |

| E         | 32           | 32           | 0.45        |  |  |

| F         | 42           | 39           | 0           |  |  |

| G         | 57           | 57           | -1.0        |  |  |

| H         | 48           | 48           | 0.7         |  |  |

| 1         | 67           | 67           | 0,6         |  |  |

| J         | 92           | 89           | 0           |  |  |

| K         | 74           | 74           | -0.55       |  |  |

| L         | 73           | 73           | -0,55       |  |  |

| M         | 58           | 61           | 0           |  |  |

| N         | 86           | 85           | 1.0         |  |  |

| 0         | 100          | 100          | 0.4         |  |  |

| P         | 110          | 110          | 0.75        |  |  |

| Q         | 111          | 111          | 0.15        |  |  |

| R         | 108          | 111          | ۵           |  |  |

| S         | 111          | 111          | -0.15       |  |  |

| T         | 110          | 110          | -1,0        |  |  |

| υ         | 100          | 100          | -0.3        |  |  |

| V         | 110          | 110          | -0.7        |  |  |

| w         | 90           | 90           | -0.7        |  |  |

This test shall be repeated with the template inverted about the time axis. In that case, t=0 on the template represents a zero crossing, with negative slope, of the output waveform. When testing an external MAU the input waveform to the DO circuit of the MAU shall contribute no more than 0.5 ns of jitter. Adherence to this template does not verify that the requirements of 14.3.1.2.3 are met. (See A4.3.3 for modification of the template to test jitter.)

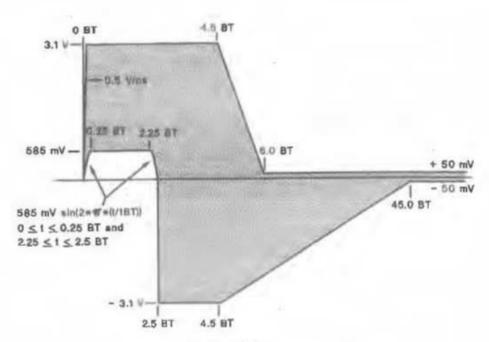

The TP\_IDL shall always start with a positive waveform when a waveform conforming to Fig 7-12 is applied to the DO circuit. If the last bit transmitted was a CD1, the last transition will be at the bit cell center of the CD1. If the last bit transmitted was a CD0, the PLS will generate an additional transition at the bit cell boundary following the CD0. After the zero crossing of the last transition, the differential voltage shall remain within the shaded area of Fig 14-10. Once the differential voltage has gone more negative than -50 mV, it shall not exceed +50 mV. The template requirements of Fig 14-10 shall be met when measured across each of the test loads defined in Fig 14-11, both with the load connected directly to the TD circuit and with the load connected through the twisted-pair model as defined in Figs 14-7 and 14-8.

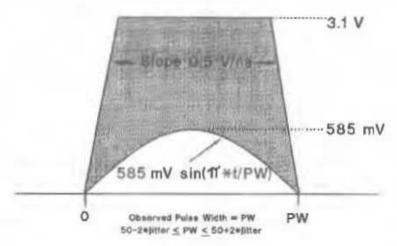

The link test pulse shall be a single positive (TD+ lead positive with respect to TD- lead) pulse, which falls within the shaded area of Fig 14-12. Once the differential output voltage has become more negative than -50 mV, it shall remain less than +50 mV. The template requirements of Fig 14-12 shall be met when measured across each of the test loads defined in Fig 14-11; both with the load connected directly to the TD circuit and with the load connected through the twisted-pair model as defined in Figs 14-7 and 14-8.

Fig 14-10 Transmitter Waveform for Start of TP\_IDL

All parameters are defined over the frequency range of 250 kHz to 6 MHz.

$L_{h} = L \pm 1\%$   $R_{p} \ge 2 \text{ k}\Omega$  $C_{p} = 12 \text{ pF} \pm 20\%$   $R_{a} \le 0.5 \Omega$

Fig 14-11 Start-of-TP\_IDL Test Load

14.3.1.2.2 Transmitter Differential Output Impedance. The differential output impedance as measured on the TD circuit shall be such that any reflection, due to differential signals incident upon the TD circuit from a simplex link segment having any impedance within the range specified in 14.4.2.2, shall be at least 15 dB below the incident, over the frequency range of 5.0 MHz to 10 MHz. This return loss shall be maintained at all times when the MAU is powered, including when the TD circuit is sending TP\_IDL.

14.3.1.2.3 Output Timing Jitter. The transmitter output jitter is measured at the output of the twisted-pair model terminated in a 100  $\Omega$  load, as shown in Fig 14-8. The jitter added to the signal on the DO circuit as it propagates through the MAU and the twisted-pair model shall be no more than  $\pm 3.5$  ns.

Fig 14-12 Transmitter Waveform for Link Test Pulse

Additionally, the MAU shall add no more than  $\pm 8$  ns of jitter to the signal received on the DO circuit when the TD circuit is directly driving a 100  $\Omega$  resistive load.

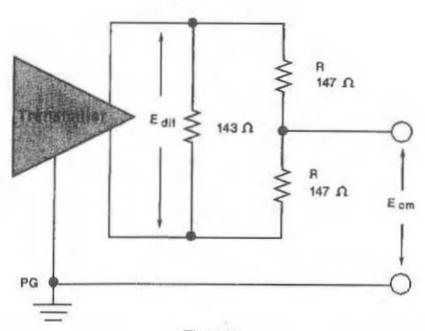

14.3.1.2.4 Transmitter Impedance Balance. The common-mode to differential-mode impedance balance of the TD circuit shall exceed  $29-17\log_{10}(f/10)$  dB (where f is the frequency in MHz) over the frequency range 1.0 MHz to 20 MHz. This balance is defined as  $20\log_{10}(E_{cm}/E_{dif})$ , where  $E_{cm}$  is an externally applied sine wave voltage as shown in Fig 14-13.

NOTE: The balance of the test equipment (such as the matching of the 147  $\Omega$  resistors) must exceed that required of the transmitter.

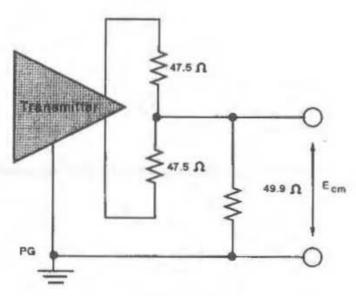

14.3.1.2.5 Common-Mode Output Voltage. The magnitude of the total common-mode output voltage of the transmitter,  $E_{\rm cm}$ , measured as shown in Fig 14-14, shall be less than 50 mV peak.

NOTE: This specification is not intended to ensure compliance with regulations concerning RF emissions. The implementor should consider any applicable local, national, or international regulations. Driving unshielded twisted pairs with high-frequency, commonmode voltages may result in interference to other equipment.

14.3.1.2.6 Transmitter Common-Mode Rejection. The application of  $E_{nm}$ , as shown in Fig 14-13, shall not change the differential voltage at the TD circuit,  $E_{dif}$ , by more than 100 mV for all data sequences. Additionally, the edge jitter added by the application of  $E_{nm}$  shall be no more than 1.0 ns.  $E_{cm}$  shall be a 15 V peak 10.1 MHz sine wave.

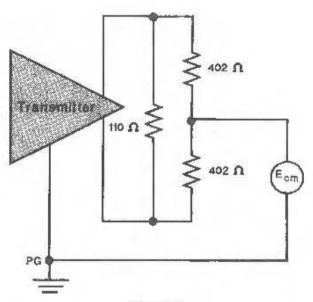

14.3.1.2.7 Transmitter Fault Tolerance. Transmitters, when either idle or non-idle, shall withstand without damage the application of short circuits across the TD circuit for an indefinite period of time and shall resume normal operation after such faults are removed. The magnitude of the current through such a short circuit shall not exceed 300 mA. Transmitters, when either idle or non-idle, shall withstand without damage a 1000 V common-mode impulse applied at  $E_{\rm cm}$  of either polarity (as indicated in Fig 14-15). The shape of the impulse shall be 0.3/50  $\mu s$  (300 ns virtual front time, 50  $\mu s$  virtual time of half value), as defined in IEC Publication 60 [11].

Fig 14-13

Transmitter Impedance Balance and Common-Mode Rejection Test Circuit

Fig 14-14 Common-Mode Output Voltage Test Circuit

Fig 14-15 Transmitter Fault Tolerance Test Circuit

- 14.3.1.3 Receiver Specifications. The MAU shall provide the Receive function specified in 14.2.1.2 in accordance with the electrical specifications of this section.

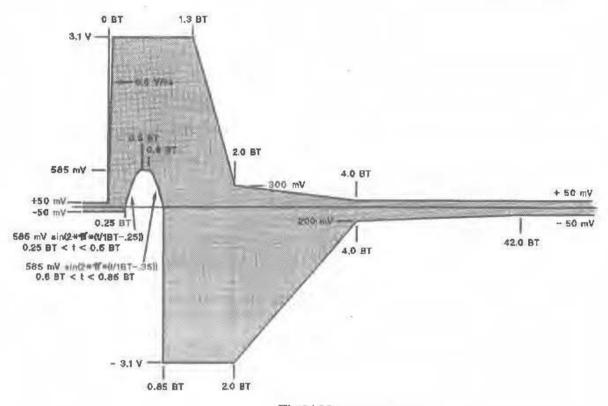

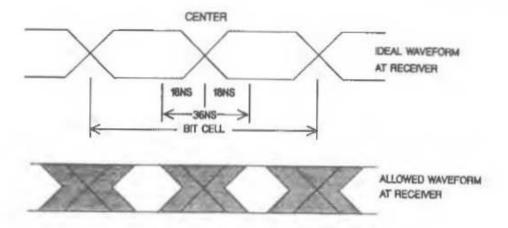

- 14.3.1.3.1 Receiver Differential Input Signals. Differential signals received on the RD circuit that are within the envelope of Fig 14-16 and 14-17, and have a maximum zero crossing jitter up to  $\pm 13.5$  ns from the ideal shall be sent to the DI circuit. The 13.5 ns includes jitter caused by an encoder, AUI cable and transmitting MAU, the twisted pair, and noise. Additionally, the MAU receiver shall add no more than  $\pm 1.5$  ns jitter to the receive signal before sending the signal to the DI circuit.

- 14.3.1.3.2 Receiver Differential Noise Immunity. The receiver, when presented with Manchester-encoded data meeting the requirements of 14.3.1.3.1, shall send this data to the DI circuit with a bit loss of no more than that specified in 14.2.1.2. In addition, the receiver, when presented with a signal meeting the requirements of 14.2.1.1 and within the envelope of Fig 14-12, shall accept it as a link test pulse.

The receiver, while in the Idle state, shall reject as RD\_input the following signals:

- All signals that when measured at the output of the following filter would produce a peak magnitude less than 300 mV. The filter is a 3-pole low-pass Butterworth with a 3 dB cutoff at 15 MHz (refer to A4.2).

- (2) All continuous sinusoidal signals of amplitude less than 6.2 V peak-to-peak and frequency less than 2 MHz.

- (3) All sine waves of single cycle duration, starting with phase 0 or 180 degrees, and of amplitude less than 6.2 V peak-to-peak where the frequency is between 2 MHz and 15 MHz. For a period of 4 BT before and after this single cycle, the signal shall be less than 300 mV when measured through the filter specified in (1) above.

- 14.3.1.3.3 Idle Input Behavior. The idle condition shall be detected within 2.3 BT of the last low-to-high transition at the receiver. The receiver shall take precautions to ensure that the high-to-silence transition of the start of idle is not falsely interpreted as a silence-to-non-idle-transition, even in the presence of signal droop, overshoot, ringing, slow voltage decay, or a combination thereof due to capacitive and inductive effects in the transmitter, link segment, and receiver.

Fig 14-16 Receive Differential Input Voltage—Narrow Pulse

Fig 14-17 Receiver Differential Input Voltage—Wide Pulse

14.3.1.3.4 Receiver Differential Input Impedance. The differential input impedance shall be such that any reflection, due to differential signals incident upon the RD circuit from a twisted pair having any impedance within the range specified in 14.4.2.2 shall be at least 15 dB below the incident over the frequency range of 5.0 MHz to 10 MHz. The return loss shall be maintained when the MAU is powered.

14.3.1.3.5 Common-Mode Rejection. Receivers shall assume the proper state on DI for any differential input signal E<sub>g</sub> that results in a signal E<sub>dif</sub> that meets 14.3.1.3.1 even in the presence of common-mode voltages E<sub>cm</sub> (applied as shown in Fig 14-18). E<sub>cm</sub> shall be a 25 V peak-to-peak square wave, 500 kHz or lower in frequency, with edges no slower than 4 ns (20%–80%). Additionally, E<sub>cm</sub> shall contribute no more than 2.5 ns of edge jitter to the signal transmitted on the DI circuit. The combination of the receiver timing jitter of 14.3.1.3.1 and the common-mode induced jitter are such that the MAU shall add no more than 4.0 ns of edge jitter to E<sub>g</sub> before sending the signal on the DI circuit.

Fig 14-18 Receiver Common-Mode Rejection Test Circuit

Fig 14-19 Common-Mode Impulse Test Circuit

14.3.1.3.6 Receiver Fault Tolerance. The receiver shall tolerate the application of short circuits between the leads of the RD circuit for an indefinite period of time without damage and shall resume normal operation after such faults are removed. Receivers shall withstand without damage a 1000 V common-mode impulse of either polarity ( $E_{\rm impulse}$  as indicated in Fig 14-19). The shape of the impulse shall be 0.3/50  $\mu s$  (300 ns virtual front time, 50  $\mu s$  virtual time of half value), as defined in IEC Publication 60 [11].

14.3.2 MAU-to-AUI Specification. When a MAU contains a physical AUI connector, the following specifications shall be met.

14.3.2.1 MAU-AUI Electrical Characteristics. The electrical characteristics for the driver and receiver components within the MAU that are connected to the AUI shall be identical to those specified in

7.4 and 7.5. Additionally, the AUI DO receiver, while in the Idle state, shall reject an input waveform of less than ±160 mV differential.

14.3.2.2 MAU-AUI Mechanical Connection. The MAU shall be provided with a 15-pin male connector as specified in 7.6.

14.3.2.3 Power Consumption. Following PowerOn, the surge current drawn by the MAU shall be such that  $I_p \times T_w$  is less than or equal to  $2 \times 10^{-3}$  ampere-seconds, where  $I_p$  is the peak surge current and  $T_w$  is the time during which the current exceeds the larger of 0.5 Å or 0.5  $\times$   $I_p$ . After the 100 ms following PowerOn, the current drawn by the MAU shall not exceed 0.5 Å when powered by the AUI.

The MAU shall be capable of operating from all possible voltage sources, including those current limited to 0.5 A, as supplied by the DTE or repeater through the resistance of all permissible AUI cables.

The MAU shall not introduce extraneous signals on the TD, CI, or DI circuits during normal power-up and power-down.

14.4 Characteristics of the Simplex Link Segment. Except where otherwise stated, the simplex link segment shall be tested with source and load impedances of  $100 \Omega$ .

14.4.1 Overview. The medium for 10BASE-T is twisted-pair wiring. Since a significant number of 10BASE-T networks are expected to be installed utilizing in-place unshielded telephone wiring and typical telephony installation practices, the end-to-end path including different types of wiring, cable connectors, and cross connects must be considered. Typically, a DTE connects to a wall outlet using a twisted-pair patch cord. Wall outlets connect through building wiring and a cross connect to the repeater MAU in a wiring closet.

NOTE: EIA/TIA 568 (1991) [A19] provides specifications for media and installation practices suitable for use with this standard.

14.4.2 Transmission Parameters. Each simplex link segment shall have the following characteristics. All characteristics specified apply to the total simplex link segment unless otherwise noted. These characteristics are generally met by 100 m of unshielded twisted-pair cable composed of 0.5 mm [24 AWG] twisted pairs.

14.4.2.1 Insertion Loss. The insertion loss of a simplex link segment shall be no more than 11.5 dB at all frequencies between 5.0 and 10 MHz. This consists of the attenuation of the twisted pairs, connector losses, and reflection losses due to impedance mismatches between the various components of the simplex link segment. The insertion loss specification shall be met when the simplex link segment is terminated in source and load impedances that satisfy 14.3.1.2.2 and 14.3.1.3.4.

NOTE: Multipair PVC-insulated 0.5 mm [24 AWG] cable typically exhibits an attenuation of 8 dB to 10 dB/100 m at 20 °C. The loss of PVC-insulated cable exhibits significant temperature dependence. At temperatures greater than 40 °C, it may be necessary to use a less temperature-dependent cable, such as most plenum-rated cables.

14.4.2.2 Differential Characteristic Impedance. The magnitude of the differential characteristic impedance of a 3 m length of twisted pair used in a simplex link segment shall be between 85  $\Omega$  and 111  $\Omega$  for all frequencies between 5.0 MHz and 10 MHz. Since characteristic impedance tends to decrease with increasing frequency, the above requirement is generally implied by the condition that the magnitude of the characteristic impedance over the frequency band 1 MHz to 16 MHz is  $100~\Omega\pm15~\Omega$ . Also, the magnitude of the input impedance averaged over the 5.0 MHz to 10 MHz frequency band of a simplex link segment terminated in  $100~\Omega$  shall be between  $85~\Omega$  and  $111~\Omega$ .

14.4.2.3 Medium Timing Jitter. Intersymbol interference and reflections due to impedance mismatches between tandem twisted pairs of a twisted-pair link segment and effects of connection devices can introduce jitter to the CD1 and CD0 signals received on the RD circuit. No more than  $\pm 5.0$  ns of jitter shall be introduced to a test signal by a simplex link segment. The test signal shall have a peak amplitude of 3.0 V and 10% to 90% rise and fall times of 12 ns. The content of the test signal shall be a Manchester-encoded pseudo-random sequence with a minimum repetition period of 511 bits.

NOTE: Branches off a twisted pair (often referred to as "bridged taps" or "stubs") will generally cause excessive jitter and so should be avoided.

- 14.4.2.4 Delay. The maximum propagation delay of twisted pair shall be 5.7 ns/m (minimum velocity of  $0.585 \times c$ ). The maximum propagation delay of a link segment shall not exceed 1000 ns.

- 14.4.3 Coupling Parameters. To avoid excessive coupling of signals between twisted pairs of a twisted-pair cable, the crosstalk must be limited. Crosstalk loss is specified for the twisted pairs in a twisted-pair cable or twisted-pair cable binder group that are used as 10BASE-T twisted-pair links. Crosstalk loss is specified with the far ends of both the disturbed and the disturbing pairs and the near end of the disturbed pair terminated in  $100~\Omega$ . Drivers of disturbing pairs shall have a source impedance of  $100~\Omega$ .

- 14.4.3.1 Differential Near-End Crosstalk (NEXT) Loss. The NEXT loss between any two twisted pairs of a twisted-pair cable is dependent upon the geometry of the twisted-pair cable. Since the proximity of any two twisted pairs is influenced by the size of the twisted-pair cable, the NEXT loss is affected by twisted-pair cable size.

- 14.4.3.1.1 Twenty-Five-Pair Cable and Twenty-Five-Pair Binder Groups. The NEXT loss between any two twisted pairs in a twenty-five-pair twisted-pair cable or binder group used for 10BASE-T applications shall be at least  $30-15\log_{10}(f/10)$  dB (where f is the frequency in MHz) over the frequency range 5.0 MHz and 10 MHz.

- 14.4.3.1.2 Four-Pair Cable. The NEXT loss between any two twisted pairs in a four-pair twisted-pair cable used for 10BASE-T applications shall be at least  $26 15 \log_{10}(f/10)$  dB (where f is the frequency in MHz) over the frequency range 5.0 MHz and 10 MHz.

- 14.4.3.1.3 Other Cables. The NEXT loss requirement for all other twisted-pair cables shall be the multiple-disturber NEXT loss of 14.4.3.2.

- 14.4.3.2 Multiple-Disturber NEXT (MDNEXT) Loss. When a twisted-pair cable or twisted-pair cable binder group contains twisted pairs from multiple 10BASE-T twisted-pair link segments, the multiple-disturber crosstalk loss is dependent upon the specific selection of disturbing and disturbed pairs. For each 10BASE-T receive pair, MDNEXT is measured by having the remaining near-end transmit pairs (excluding the transmit pair associated with the receive pair under test) driven with identical and synchronized sine wave signals. MDNEXT may then be determined from the signal level observed on the receive pair under test. By examining all pair combinations with a fixed number of disturbers, a cumulative distribution of MDNEXT is obtained at each frequency of interest. The one percentile of this cumulative distribution shall be at least 23 15 log<sub>10</sub>(f/10) (where f is the frequency in MHz) at 5.0 MHz, 7.5 MHz, and 10 MHz. When the number of possible combinations allowed by a cable is fewer than 100, the MDNEXT loss for all combinations shall be at least 23 15 log<sub>10</sub>(f/10) (where f is the frequency in MHz) at 5.0 MHz, 7.5 MHz, and 10 MHz. Refer to 12.7.3.2 and Appendix A3 for a tutorial and method for estimating the MDNEXT loss for a complete n-pair cable.

- 14.4.4 Noise Environment. The noise level on the link segments shall be such that the objective error rate is met. The noise environment consists generally of two primary contributors: crosstalk from other 10BASE-T circuits; and externally induced impulse noise, typically from telephone ringing and dialing signals, and other office and building equipment.

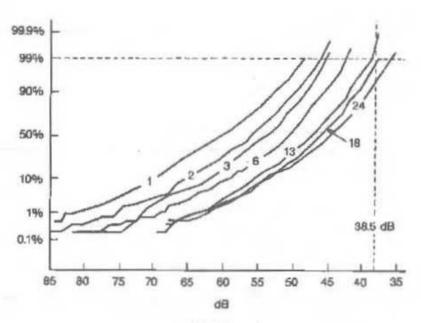

- 14.4.4.1 Impulse Noise. The average rate of occurrence of impulses greater than 264 mV shall be less than or equal to 0.2/s as measured at the output of the following specified filter. Following the start of any particular impulse that is counted, any additional impulse shall be ignored for a period of 1  $\mu$ s. The simplex link segment shall be terminated at the far end in 100  $\Omega$ . The filter is a 3-pole Butterworth low-pass with a 3 dB cutoff at 15 MHz (refer to A4.2).

NOTE: Typically, the impulse noise occurrence rate changes inversely by one decade for each 5 dB to 9 dB change in the threshold voltage. If a count rate of N counts/s is measured on a specific twisted pair and filter at the specified voltage threshold, the media noise margin is approximately 7 log<sub>10</sub>(0.2/N) dB. Impulse noise may be a burst phenomenon and should be measured over an extended period of time.

14.4.4.2 Crosstalk Noise. The level of crosstalk noise on a simplex link segment depends on the level of the disturbing signal(s) and the crosstalk loss between the pair(s) carrying the signal(s) and the dis-

turbed pair. With the maximum transmit level (14.3.1.2), the sinusoidal crosstalk loss (14.4.3.2), and multiple, random Manchester-encoded disturbers, the peak self-crosstalk noise levels as measured at the output of the following specified filter shall be less than or equal to 264 mV. The filter is a 3-pole Butterworth low-pass with a 3 dB cutoff at 15 MHz (refer to A4.2).

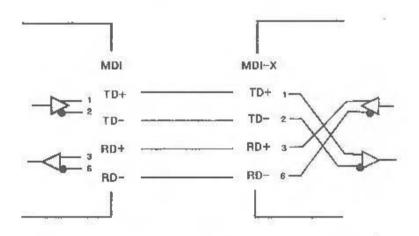

14.5 MDI Specification. This section defines the MDI for the twisted-pair link segment. The link topology requires a crossover function between PMAs. Implementation and location of this crossover is also defined in this section.

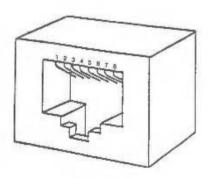

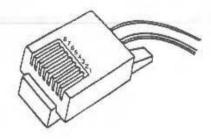

14.5.1 MDI Connectors. Eight-pin connectors meeting the requirements of Section 3 and Figures 1–5 of ISO 8877 [20] shall be used as the mechanical interface to the twisted-pair link segment. The plug connector shall be used on the twisted-pair link segment and the jack on the MAU. These connectors are depicted (for informational use only) in Figs 14-20 and 14-21. The following table shows the assignment of signals to connector contacts.

| CONTACT | MDI SIGNAL           |

|---------|----------------------|

| 1       | TD+                  |

| 2       | TD-                  |

| 3       | RD+                  |

| 4       | Not used by 10BASE-T |

| 5       | Not used by 10BASE-T |

| 6       | RD-                  |

| 7       | Not used by 10BASE-T |

| 8       | Not used by 10BASE-T |

Fig 14-20 MAU MDI Connect

Fig 14-21 Twisted-Pair Link Segment Connector

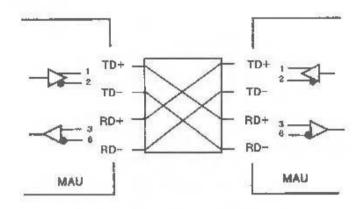

14.5.2 Crossover Function. A crossover function shall be implemented in every twisted-pair link. The crossover function connects the transmitter of one MAU to the receiver of the MAU at the other end of the twisted-pair link. Crossover functions may be implemented internally to a MAU or elsewhere in the twisted-pair link. For MAUs that do not implement the crossover function, the signal names of 14.5.1 refer to their own internal circuits. For MAUs that do implement the crossover function, the signal names refer to the remote MAU of the twisted-pair link. Additionally, the MDI connector for a MAU that implements the crossover function shall be marked with the graphical symbol "X". Internal and external crossover functions are shown in Fig 14-22.

(a) External Crossover Function

(b) MAU-Embedded Crossover Function

Fig 14-22 Crossover Function

When a twisted-pair link connects a DTE to a repeater, it is recommended that the crossover be implemented in the MAU local to the repeater. If both MAUs of a twisted-pair link contain internal crossover functions, an additional external crossover is necessary. It is recommended that the crossover be visible to an installer from one of the MAUs. When both MAUs contain internal crossovers, it is further recommended in networks in which the topology identifies either a central backbone segment or a central hub that the MAU furthest from the central element be assigned the external crossover to maintain consistency.

Implicit implementation of the crossover function within a twisted-pair cable, or at a wiring panel, while not expressly forbidden, is beyond the scope of this standard.

14.6 System Considerations. The repeater unit specified in Section 9 forms the central unit for interconnecting 10BASE-T twisted-pair links in networks of more than two nodes. It also provides the means for connecting 10BASE-T twisted-pair links to other 10 Mb/s baseband segments. The proper operation of a CSMA/CD network requires network size to be limited to control round-trip propagation delay to meet the requirements of 4.2.3.2.3 and 4.4.2.1, and the number of repeaters between any two DTEs to be limited in order to limit the shrinkage of the interpacket gap as it travels through the network. Configuration rules, which ensure that these limits are not exceeded, are given in Section 13.

#### 14.7 Environmental Specifications

14.7.1 General Safety. All equipment meeting this standard shall conform to one of the following IEC Publications: 380 [5], 435 [6], or 950 [8].

NOTE: For ISO/IEC 8802-3: 1993, conformance shall be to IEC 950 [8].

14.7.2 Network Safety. This section sets forth a number of recommendations and guidelines related to safety concerns; the list is neither complete nor does it address all possible safety issues. The designer is urged to consult the relevant local, national, and international safety regulations to ensure compliance with the appropriate requirements.

LAN cable systems described in this section are subject to at least four direct electrical safety hazards

during their installation and use. These hazards are as follows:

- (1) Direct contact between LAN components and power, lighting, or communications circuits.

- (2) Static charge buildup on LAN cables and components.

- (3) High-energy transients coupled onto the LAN cable system.

- (4) Voltage potential differences between safety grounds to which various LAN components are connected.

Such electrical safety hazards must be avoided or appropriately protected against for proper network installation and performance. In addition to provisions for proper handling of these conditions in an operational system, special measures must be taken to ensure that the intended safety features are not negated during installation of a new network or during modification or maintenance of an existing network. Isolation requirements are defined in 14.3.1.1.

- 14.7.2.1 Installation. Sound installation practice, as defined by applicable local codes and regulations, shall be followed in every instance in which such practice is applicable.

- 14.7.2.2 Grounding. Any safety grounding path for the MAU shall be provided through the circuit PG of the AUI connection.

WARNING: It is assumed that the equipment to which the MAU is attached is properly earthed, and not left floating nor serviced by a "doubly insulated ac power distribution system." The use of floating or insulated equipment, and the consequent implications for safety are beyond the scope of this standard.

- 14.7.2.3 Installation and Maintenance Guidelines. During installation and maintenance of the cable plant, care shall be taken to ensure that uninsulated network cable conductors do not make electrical contact with unintended conductors or ground.

- 14.7.2.4 Telephony Voltages. The use of building wiring brings with it the possibility of wiring errors that may connect telephony voltages to 10BASE-T equipment. Other than voice signals (which are low voltage), the primary voltages that may be encountered are the "battery" and ringing voltages. Although there is no universal standard, the following maximums generally apply.

Battery voltage to a telephone line is generally 56 Vdc applied to the line through a balanced 400  $\Omega$  source impedance.

Ringing voltage is a composite signal consisting of an ac component and a dc component. The ac component is up to 175 V peak at 20 Hz to 60 Hz with a 100  $\Omega$  source resistance. The dc component is 56 Vdc with a 300  $\Omega$  to 600  $\Omega$  source resistance. Large reactive transients can occur at the start and end of each ring interval.

Although 10BASE-T equipment is not required to survive such wiring hazards without damage, application of any of the above voltages shall not result in any safety hazard.

NOTE: Wiring errors may impose telephony voltages differentially across 10BASE-T transmitters or receivers. Because the termination resistance likely to be present across a receiver's input is of substantially lower impedance than an off-hook telephone instrument, receivers will generally appear to the telephone system as off-hook telephones. Therefore, full-ring voltages will be applied for only short periods. Transmitters that are coupled using transformers will similarly appear like off-hook telephones (though perhaps a bit more slowly) due to the low resistance of the transformer coil.

#### 14.7.3 Environment

14.7.3.1 Electromagnetic Emission. The twisted-pair link shall comply with applicable local and national codes for the limitation of electromagnetic interference.

14.7.3.2 Temperature and Humidity. The twisted-pair link is expected to operate over a reasonable range of environmental conditions related to temperature, humidity, and physical handling (such as shock and vibration). Specific requirements and values for these parameters are considered to be beyond the scope of this standard.

It is recommended that manufacturers indicate in the literature associated with the MAU the operating

environmental conditions to facilitate selection, installation, and maintenance.

It is recommended that manufacturers indicate, in the literature associated with the components of the twisted-pair link segment, the distance and operating environmental conditions over which the specifications of 14.4 will be met.

14.8 MAU Labeling. It is recommended that each MAU (and supporting documentation) he labeled in a manner visible to the user with at least these parameters:

(1) Data rate capability in Mh/s,

Power level in terms of maximum current drain (for external MAUs),

(3) Any applicable safety warnings.

See also 14.5.2.

14.9 Timing Summary. Table 14-2 summarizes the timing requirements for the 10BASE-T twisted-pair link. This table is a summary; for complete descriptions of the timing requirements, refer to the referenced sections.

**Table 14-2** Maximum Timing Parameters

|        |                                                                 |           |                  | 141                                                   | Start-up Delay |                          |                 |