# SEMICONDUCTOR INTEGRATED CIRCUIT PROCESSING TECHNOLOGY

W. R. RUNYANRetired, formerly with Texas InstrumentsK. E. BEANTexas Instruments

INDUSTRIAL DESIGN CORPORATION LIBRARY 2020 S.W. 4th PORTLAND, OREGON 97201

Addison-Wesley Publishing Company

Reading, Massachusetts • Menlo Park, California • New York Don Mills, Ontario • Wokingham, England • Amsterdam • Bonn Sydney • Singapore • Tokyo • Madrid • San Juan

## This book is in the Addison-Wesley Series in Electrical and Computer Engineering

Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and Addison-Wesley was aware of a trademark claim, the designations have been printed in initial caps or all caps.

This publication is designed to provide accurate and reliable information in regard to the subject matter covered. However, responsibility is assumed neither for its use nor for any infringement of patterns or rights of others which may result from its use.

Cover photos (top to bottom): Courtesy of Bell Laboratories; Courtesy of Texas Instruments; Courtesy of Intel Corporation (®Registered trademark of Fairchild Semiconductor Corporation); Courtesy of Gordon Teal; Courtesy of Texas Instruments Incorporated.

### Library of Congress Cataloging-in-Publication Data

Runyan, W. R. Semiconductor integrated circuit processing technology / Walter R. Runyan, Kenneth E. Bean. p. cm. Bibliography: p. Includes index. ISBN 0-201-10831-3 1. Integrated circuits-Design and construction. 2. Semiconductors-Design and construction. 1. Bean, Kenneth E. II. Title. TK7874.R86 1990 89-320 621.381'73-dc19 CIP

Copyright © 1990 by Addison-Wesley Publishing Company, Inc.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America.

ABCDEFGHIJ-DO-89

## Foreword

Forty years ago the transistor was hailed as a model of the scientific process of invention. Although Shockley's work provided a basic understanding of junction transistor structure, little was really known about the fabrication processes used for semiconductors. Terms such as "deathnium" and "forming" were used to describe effects that were not understood. Most of the techniques used were crude adaptations of technology developed for other purposes, and much of the learning was empirical.

Today, after many thousands of man-years of effort, the situation has changed. New processes have been developed specifically for semiconductor use, and others have been carefully optimized. By the standards of the 1950s, all are now well understood.

The authors of this book, Walt Runyan and Ken Bean, have been key contributors to this new understanding. Both have been actively involved with semiconductors since the beginning; both, in the development of new processes and the application of processes to high-volume production.

Today, semiconductor manufacture is truly a science based industry. This book provides an excellent summary of the state-of-theart in modern semiconductor processing, both in terms of the scientific knowledge of the field and in its practical application to devices.

J. S. Kilby

iii

Elm Exhibit 2159, Page 5

## Preface

The field of semiconductor process engineering is now so broad that it is virtually impossible for a single individual to provide process engineering support or process development for the complete semiconductor manufacturing operation. Thus, subdivision and specialization are required. However, since each subdivision is intricately related to all others, it is absolutely necessary that each technology specialist (engineer) have a good understanding of all phases of the manufacturing process. This book is intended to provide a unified treatment of that portion of the semiconductor manufacturing process commonly referred to as "wafer fabrication."

The book is to be used as a text by university students and as a reference by practicing engineers. It provides background, theory, and practical discussions related to the wafer fabrication process. It is not, however, a compendium of all of the latest research activities, which are constantly changing and continually covered in various technical journals and review book series. The serious student, whether in industry or university, must keep up-to-date by following the current technical journals most closely allied with his or her chosen specialty.

The level of presentation in the book assumes that the student has had introductory physics, introductory inorganic chemistry, mathematics through differential equations, a first course in transistor device physics, and a course covering electronic material properties including crystal structure. All of these courses are generally available by the senior year so the text is suitable for either senioror graduate-level courses.

The book is organized into eleven chapters and three appendices. All chapters have an extensive list of references, and all but the first two chapters have problems and a list of key ideas. Since silicon remains the semiconductor used for 99 percent of the integrated circuits, it is naturally emphasized. However, where GaAs processing differs substantially from silicon, it is discussed separately.

The first chapter is an historical discussion of the development of the integrated circuit. The second chapter gives an overview of the processing steps required to manufacture an integrated circuit. Chapters 3 through 10 discuss the various technologies required for the steps, and each chapter has a section on safety. The chapter subjects are, respectively, silicon thermal oxidation, deposition of thin inorganic films, photolithography, etching, epitaxial

Elm Exhibit 2159, Page 6

۷

VI PREFACE

growth, solid state diffusion, ion implantation, and contacts and interconnects.

Chapter 11 is devoted to a discussion of yields, yield analysis, and yield economics. The latter is included because all too often the student (and in some cases, practicing engineers as well) lose sight of the fact that to be practical for industrial use, semiconductor processes must be economical as well as scientifically feasible. Emphasis is on defect density measurement and interpretation, on the use of I–V plots to determine the cause of faulty integrated circuit elements, and on how yield and an economical manufacturing operation are related.

The first of three appendices is a review of crystallography as it relates to silicon and gallium arsenide. The second is a review of phase diagrams, and the third is a compilation of numerical constants and conversions. Finally, an extensive list of semiconductorrelated acronyms is given inside the front and back covers of the book.

Acknowledgments: Over the course of time spent in preparing this book, many people have been very helpful, and in particular, we would like to acknowledge Hettie Smith, who typed the manuscript and took care of many of the details involved in its preparation, as well as Marion Johnson and John Powell, who provided many of the photographs. We also want to acknowledge the following people who read and commented on various portions of the manuscript: Neal Akridge. ATEQ Corp.: Frederick Strieter. Honeywell Corp.: Bruce Deal, Advantage Production Technology, Inc.; Howard Huff, Sematech: George Brown. Dwayne Carter, Rinn Cleavelin, Monte Douglas, P. B. Ghate, John Hatcher, William Keenan, Charlotte Tipton, Michael Tipton, Rick Wise, and Richard Yeakley, all of Texas Instruments Incorporated; and Isaac Trachtenberg, Chemical Engineering Department at the University of Texas. In addition, we want to thank the following people for their helpful reviews of the manuscript: D. K. Schroder, Arizona State University; John D. Shott, Stanford University: Dean P. Neikirk, University of Texas, Austin; Arthur B. Glaser, AT&T Bell Laboratories; and Richard C. Jaeger, Auburn University.

We would also like to thank our editor. Tom Robbins, and his staff for guidance during the various stages of manuscript preparation. Lastly, we wish to express our appreciation for the patience, encouragement, and indulgence of our wives. Delma Runyan and Helen Bean.

> W. R. Runyan K. E. Bean

# Contents in Brief

i

| CHAPTER 1        | Historical Overview 1                                    |

|------------------|----------------------------------------------------------|

| CHAPTER 2        | Processing Overview 22                                   |

| CHAPTER 3        | Thermal Oxidation of Silicon 53                          |

| <b>CHAPTER 4</b> | Definition of Inorganic Thin Films 121                   |

| CHAPTER 5        | Lithography 161                                          |

| CHAPTER 6        | Etching 242                                              |

| CHAPTER 7        | Epitaxy 294                                              |

| CHAPTER 8        | Impurity Diffusion 371                                   |

| CHAPTER 9        | Ion Implantation 476                                     |

| CHAPTER 10       | Ohmic Contacts, Schottky Barriers, and Interconnects 518 |

| CHAPTER 11       | Yields and Yield Analysis 579                            |

| APPENDIX A       | Crystallography 645                                      |

| APPENDIX B       | Phase Diagrams 661                                       |

| APPENDIX C       | Reference Tables 670                                     |

|                  | Index 673                                                |

|                  |                                                          |

vii

Elm Exhibit 2159, Page 9

# **Detailed Contents**

### **CHAPTER 1**

#### **Historical Overview** 1

- 1.1 Background

- 1.2 The Transistor 2

- 1.3 The Integrated Circuit 8

- 1.4 Semiconductor Processes 17 References 20

1

#### **Processing Overview** CHAPTER 2 22

- 2.1 Introduction

- 2.2 Wafer Fabrication Facility 31

- 2.3 Wafer Fabrication Operations 33

- 2.3.1 Surface Cleaning 34

- 2.3.2 Epitaxy 34

- 2.3.3 Thermal Oxidation of Silicon 35

22

- 2.3.4 Diffusion 35

- 2.3.5 Ion Implantation 36

- 2.3.6 Lithography 36

- 2.3.7 Etching 38

- 2.3.8 Chemical Vapor Deposition (CVD) 38

- 2.3.9 Metal Deposition 38

- 2.3.10 Metal (Contact) Sintering 39

- 2.3.11 Backgrinding 39 39

- 2.3.12 Multiprobing

- 2.4 Integrated Circuit Fabrication 40 2.4.1 Components and Component Construction 40 2.4.2 Steps in IC Fabrication 46

#### CHAPTER 3 **Thermal Oxidation of Silicon** 53

- 3.1 Introduction 53

- 3.2 Structure 55

- Nonelectrical Properties 3.3 57

- 3.3.1 Density 57

- 3.3.2 Expansion Coefficient 59

- 3.3.3 Optical Properties 60

- 3.3.4 Chemical Properties 61

- 3.4 Electrical Properties 63

- 3.4.1 Bulk Electrical Conduction 63

- 3.4.2 Surface Electrical Conductivity 65

- 3.4.3 Dielectric Breakdown Strength 67

ix

### x DETAILED CONTENTS

- 3.4.4 Mobile Ion Transport 69

- 3.4.5 Interface Charges 72

- 3.5 Kinetics of Oxidation 76

- 3.5.1 Deal-Grove Model

- 3.5.2 Initial Stage of Oxidation 79

- 3.5.3 Reaction Path 81

- 3.5.4 Determination of Rate Constants 81

- 3.5.5 Calculation of Oxide Thickness 83

- 3.5.6 Temperature Behavior of Rate Constants 83

- 3.5.7 Effect of Crystal Orientation on Rate 84

- 3.5.8 Polycrystalline Silicon Oxidation 88

- 3.5.9 Effect of Pressure on Oxidation 90

- 3.5.10 Effect of Ambient Impurities on Oxidation Rate 90

77

- 3.5.11 Effect of Silicon Doping on Oxidation Rate 91

- 3.5.12 Impurity Profile at the Oxide Interface 96

- 3.6 Oxide Thickness Charts 98

- 3.7 Preparation of Thermal Oxide 99

- 3.7.1 Preoxidation Surface Cleanup 99

- 3.7.2 Atmospheric Pressure Equipment 104

- 3.7.3 High-Pressure Oxidation Processing 107

- 3.7.4 High-Pressure Equipment 107

- 3.7.5 Selective Oxidation 108

- 3.7.6 Two- and Three-Dimensional Oxidation 110

- 3.7.7 Oxide Physical Defects

- 3.7.8 Defects Generated in Silicon During Oxidation 112

111

- Key Ideas 113

- Problems 113

- References 114

### CHAPTER 4 Deposition of Inorganic Thin Films 121

- 4.1 Introduction 121

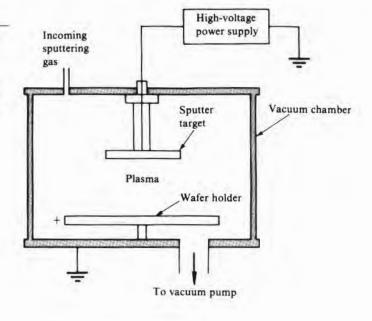

- 4.2 Sputter Deposition 124

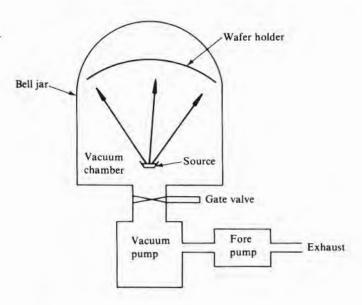

- 4.3 Evaporation 126

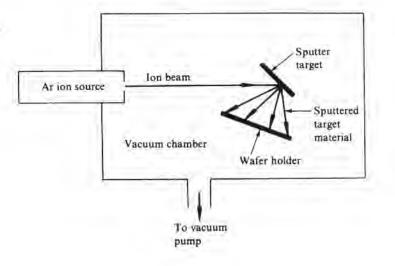

- 4.4 Ion Beam Deposition 128

- 4.5 Chemical Vapor Deposition 129

- 4.5.1 Atmospheric Pressure and Low-Pressure Depositions 130

137

- 4.5.2 Plasma-Enhanced CVD

- 4.5.3 Photon-Enhanced CVD 139

- 4.6 Deposition of Specific Materials 140

- 4.6.1 CVD Silicon Dioxide 140

- 4.6.2 Plasma Silicon Dioxide 142

- 4.6.3 Doped Silicon Oxide 143

- 4.6.4 CVD Silicon Nitride 145

- 4.6.5 Plasma Silicon Nitride 147

- 4.6.6 APCVD and LPCVD Polysilicon 148

- 4.6.7 Plasma Polysilicon 151

### DETAILED CONTENTS xi

- 4.7 Other CVD Film Materials 151

- 4.8 Spin-On Glasses 152

- 4.9 Glass Fritting 153 Safety 154 Key Ideas 156 Problems 156 References 157

### CHAPTER 5 Lithography 161

- 5.1Introduction1615.2Photomasks161

- 5.2.1 Masks for Optical Printing1615.2.2 X-Ray Masks164

- 5.2.3 Mask Protection 165

- 5.3 Mask Defects 166 5.3.1 Mask Inspection 167

- 5.3.2 Mask–Wafer Overlay Accuracy 169

- 5.3.3 Overlay Accuracy Measurements 171

- 5.4 Photoresists 172

- 5.4.1 UV Negative Resist Formulation 175

- 5.4.2 UV Positive Resist Formulation 175

- 5.4.3 E-Beam, X-Ray, and Ion Beam Resists 176

- 5.4.4 Inorganic Resists 177

- 5.4.5 Plasma-Developable Resists 177

- 5.4.6 Resist Contrast 178

- 5.4.7 Sensitivity 182

- 5.4.8 Reciprocity 183

- 5.4.9 Etch Resistance 184

- 5.5 Resist Processing Flow 184

- 5.5.1 Adhesion Promoters and Adhesion 184

- 5.5.2 Resist Application 186

- 5.5.3 Soft-, Postexpose-, and Hard-Bake 189

- 5.5.4 Developing 189

- 5.5.5 Resist Removal 189

- 5.6 Light Sources 190

- 5.6.1 Arc Sources 190

- 5.6.2 Excimer Lasers 192

- 5.7 Contact Printing 192

- 5.8 Optical Proximity Printing 193

- 5.9 Fundamental Optical Limitations of Projection Printing 195

- 5.9.1 Resolution 195

- 5.9.2 Depth of Focus 198

- 5.9.3 Variation in Position of Best Focus 198

- 5.10 Full-Wafer Projection Printing 200 5.10.1 Operation 201

### xii DETAILED CONTENTS

5.10.2 Focusing Accuracy 202 5.10.3 Registration 202 Stepper Printing 204 5.11 5.11.1 Focus 204 5.11.2 Alignment 206 5.11.3 Registration 207 5.11.4 Throughput 208 5.12 Electron Beam Printing 210 5.12.1 Pattern Generation 210 5.12.2 Resolution 210 5.12.3 Alignment 211 5.13 X-Ray Printing 211 5.13.1 Image Distortion 212 5.13.2 Resolution 212 5.13.3 X-Ray Sources 214 5.13.4 X-Ray Steppers 214 5.14 Ion Beam Printing 215 5.14.1 Focused Ion Beams 215 5.14.2 Masked Ion Beam Printing 215 5.15 Printer Selection 215 5.16 Line-Width Control 216 5.16.1 Process-Initiated Control Problems 217 5.16.2 Interference Effects 224 5.16.3 Minimizing Effect of Standing Waves 227 5.16.4 Resist over Steps 228 5.16.5 Multilayer Resist 228 5.17 Wafer Flatness 231 5.18 Lithography Process Modeling 234 Safety 235 236 Key Ideas Problems 237 References 237

### CHAPTER 6 Etching 242

- 6.1 Introduction 242

- 6.2 Wet Etching 245

- 6.2.1 Etch Formulation 247

- 6.2.2 Nonselective Silicon Etching 249

- 6.2.3 Polycrystalline Silicon Etching 251

- 6.2.4 Anisotropic Silicon Etching 252

- 6.2.5 Resistivity-Sensitive Silicon Etching 256

- 6.2.6 Electrolytic Silicon Etching 258

- 6.2.7 Silicon Staining 259

- 6.2.8 Gallium Arsenide Etching (General) 259

- 6.2.9 Gallium Arsenide Etching (Anisotropic) 261

- 6.2.10 Preferential Etches 263

#### DETAILED CONTENTS xiii

283

6.2.11 Silicon Dioxide Etching 264 6.2.12 Silicon Nitride Etching 267 6.2.13 Metal Etching 268 6.3 Plasma Etching 269 6.3.1 Etching Reactions 273 6.3.2 Plasma Etch Rates 278 6.3.3 Selectivity 280 6.3.4 End-Point Detection 282 6.3.5 Effect of Loading on Etch Rate 284 6.3.6 Effect of Electrode Material 6.3.7 Plasma-Induced Damage 284 6.3.8 Plasma Etching Equipment 285 6.4 Vapor Phase Etching 287 Safety 287 Key Ideas 288 Problems 289 References 289

#### **CHAPTER 7** Epitaxy

- 7.1 Introduction 294

- Vapor Phase Epitaxy 297 7.2

- 7.2.1 Nucleation 297

- 7.2.2 Surface Reactions 306

294

- 7.2.3 Material Transport 308

- 7.3 Vapor Phase Silicon Epitaxy 309

- 7.3.1 Surface Cleaning and Vapor Phase Etching 309

- 7.3.2 Deposition Reactions 313

- 7.3.3 Deposition Rates 315

- 321 7.3.4 Effect of Orientation on Deposition Rate

- 7.3.5 Layer Doping 323

- 7.3.6 Impurity Redistribution during Epitaxy 324

- 7.3.7 Pattern Shift and Distortion 328

- 7.3.8 Selective Epitaxial Growth (SEG) 332

- 7.3.9 Equipment for Silicon Vapor Phase Epitaxy 338

- 7.3.10 Molecular Beam Epitaxy (MBE) 342

- 7.3.11 Defects Introduced during Growth 344

- 7.4 Vapor Phase Gallium Arsenide Epitaxy 349 7.4.1 Halide Transport 349 7.4.2 Metalorganic Source CVD (MOCVD) 350

- 7.4.3 GaAs Molecular Beam Epitaxy 351

- 352

- 7.5 Liquid Phase Epitaxy 7.5.1 Silicon LPE 353 7.5.2 GaAs LPE 355

- 7.6 Epitaxial Crystal Growth from a Solid 356

- Crystal Growth over Insulating Substrates 357 7.7 Safety 360

### xiv DETAILED CONTENTS

| Key Ideas  | 360 |

|------------|-----|

| Problems   | 361 |

| References | 362 |

### **CHAPTER 8**

### Impurity Diffusion 371

8.1 Introduction 371

- 8.2 Atomic Diffusion Mechanisms 374

- 8.2.1 Diffusion by Vacancies 378

- 8.2.2 Diffusion by Interstitialcy 379

- 8.2.3 Interstitial Diffusion 380

- 8.2.4 Electric-Field-Aided Diffusion

- 8.2.5 Effect of Thermal Oxidation on the Diffusion Coefficient 383

381

- 8.2.6 Effect of Diffusing Direction (Orientation) 384

- 8.2.7 Effect of Heavy Doping 385

- 8.2.8 Effect of Temperature 386

- 8.2.9 Effect of Stress/Strain 386

- 8.2.10 Emitter Push, Pull, and Dip 388

- 8.3 Solutions to the Diffusion Equations 388

- 8.3.1 Diffusion from Infinite Source on Surface 390

- 8.3.2 Diffusion from Limited Source on Surface 392

- 8.3.3 Diffusion from Interior Limited Source 394

- 8.3.4 Diffusion from Layer of Finite Thickness 395

- 8.3.5 Diffusion from Concentration Step 397

- 8.3.6 Diffusion from Concentration Step into Moving Layer 398

- 8.3.7 Out-Diffusion with Rate Limiting at Surface 401

- 8.3.8 Diffusion from a Fixed Concentration into Moving Layer 401

- 8.3.9 Diffusion through Thin Layer 402

- 8.3.10 Diffusion during Thermal Oxidation 404

- 8.3.11 Diffusion from Infinite Source into Finite Thickness 406

- 8.3.12 Two-Dimensional Diffusion from High-Diffusivity Path 407

- 8.3.13 Two-Dimensional Solutions 409

- 8.3.14 Effect of Temperature Varying with Time 411

- 8.4 Diffusion Profile Calculations 412

- 8.4.1 Phosphorus Profile 414

- 8.4.2 Silicon Interstitial Diffusants 414

- 8.4.3 Gallium Arsenide Profile 416

- 8.4.4 Solid Solubility Data 416

- 8.5 Diffusion Characterization 418

- 8.5.1 Conversion from Dopant Concentration to Resistivity 418

- 8.5.2 Sheet Resistance Measurement 419

- 8.5.3 Determination of  $N_0$  420

- 8.5.4 Junction Depth Measurement 421

- 8.5.5 Profile Measurement 422

- 8.5.6 Determination of Diffusion Coefficient 424

- 8.6 Diffusion Processes 428

- 8.6.1 Depth 428

#### DETAILED CONTENTS XV

442

8.6.2 Surface Concentration 428 8.6.3 Lifetime Control 429 8.6.4 Gettering of Silicon 431 8.7 Diffusion-Induced Defects 440 8.7.1 Diffusion Flaws and Pipes 441 8.7.2 Lifetime-Reducing Impurities and Precipitates 8.7.3 Strain-Induced Dislocations 443 8.7.4 Permanent Wafer Warpage 446 8.8 Diffusion Equipment 451 8.8.1 Gas Flow Measurement and Control 452 8.8.2 Diffusion Tubes 453 8.8.3 Wafer Diffusion Boats 453 8.8.4 Wafer Insertion 454 8.8.5 Computer Control of Tube Functions 454 8.9 **Diffusion Sources** 456 8.9.1 Liquid Sources 458 8.9.2 Gaseous Sources 459 8.9.3 Planar Sources 460 8.9.4 Doped Oxide Sources 461 461 8.9.5 Closed-Tube Sources The Error Function 462 8.10 8.10.1 Error Function Algebra 462 462 8.10.2 Calculation of Error Function Values Safety 465 Key Ideas 466 Problems 467 References 468

#### **CHAPTER 9** Ion Implantation 476

9.1 Introduction 476

- Implant Depth (Range) 478 9.2

- 9.2.1 Range Calculations 478

- 9.2.2 Range Dispersion 481

- 9.2.3 Lateral Range Dispersion 486

- 9.2.4 Channeling 487

- 9.2.5 Implanting through Layers 491

- 9.3 Implant-Induced Defects 494 9.3.1 Lattice Damage 495

- 9.3.2 Annealing 497

- 9.4 Applications 499

- 9.4.1 MOS Threshold Adjust 501

- 9.4.2 Self-Aligned MOS Gate 502

- 9.4.3 Polysilicon Doping 503

- 9.4.4 Alternative to Diffusion Predep 504

- 9.4.5 Ion Beam Mixing and Ion Beam Damage 504

- 9.4.6 Formation of Buried Layers 505

### xvi DETAILED CONTENTS

9.5 Ion Implant Equipment 505 9.5.1 Ion Sources 507 509 9.5.2 Ion Analyzer 9.5.3 Wafer Handling 510 9.5.4 Wafer Contamination 511 512 9.5.5 Implant Uniformity Measurements 513 Safety 514 Key Ideas 514 Problems References 515

### CHAPTER 10 Ohmic Contacts, Schottky Barriers, and Interconnects 518

| 10.1  | Introduction 518                                   |

|-------|----------------------------------------------------|

| 10.2  | Ohmic Contacts 520                                 |

| 17.10 | 10.2.1 Spreading Resistance 520                    |

|       | 10.2.2 Contact Resistance 522                      |

|       | 10.2.3 Total Contact Resistance 527                |

|       | 10.2.4 The Aluminum–Silicon Ohmic Contact 528      |

|       | 10.2.5 The Silicide–Silicon Ohmic Contact 535      |

|       | 10.2.6 Alloyed GaAs Ohmic Contacts 538             |

|       | 10.2.7 Nonalloyed GaAs Ohmic Contacts 538          |

|       | 10.2.8 Measurement of Contact Resistance 539       |

| 10.3  | Schottky Diodes 541                                |

|       | 10.3.1 Rectifying Schottky Barriers 541            |

|       | 10.3.2 Choice of Metal for Schottky Barriers 544   |

| 10.4  | Leads (Interconnects) 544                          |

|       | 10.4.1 Lead Resistance 545                         |

|       | 10.4.2 Adhesion to SiO <sub>2</sub> 549            |

|       | 10.4.3 Diffusion Barrier 550                       |

|       | 10.4.4 Interconnect Material Contamination 552     |

|       | 10.4.5 Step Coverage 552                           |

|       | 10.4.6 Protective Overcoats 555                    |

| 10.5  | MOS Gate Materials 556                             |

| 10.6  | Multilevel Metallization 558                       |

|       | 10.6.1 Interlevel Shorts 558                       |

|       | 10.6.2 Planarization 559                           |

| 10.7  | Interconnect and Gate Metal Pattern Definition 560 |

| 10.8  | Failure Modes 560                                  |

|       | 10.8.1 Electromigration 561                        |

|       | 10.8.2 Corrosion 564                               |

|       | 10.8.3 Internal Stresses 565                       |

| 10.9  | Deposition Methods 565                             |

|       | 10.9.1 Surface Cleanup 566                         |

|       | 10.9.2 Metal Evaporation 566                       |

|       | 10.9.3 Sputtering 567                              |

|       | 10.9.4 Chemical Vapor Deposition 568               |

|       |                                                    |

### DETAILED CONTENTS xvii

10.10 Process Control 570 570 10.10.1 Resistivity Ratio 10.10.2 Current Capacity 571 10.10.3 Lead Adherence 571 10.10.4 Process Problems Requiring Test Patterns for Detection 572 Safety 572 Key Ideas 572 573 Problems 574 References

### CHAPTER 11 Yields and Yield Analysis 579

- 11.1 Introduction 579

- 11.2 Yield Definitions 579

- 11.3Methods of Yield Measurement58111.3.1The Curve Tracer58211.3.2Automatic Multiprobe Testing583

- 11.4 Yield Tracking 585

11.4.1 Process and Multiprobe Yield Tracking 585

11.4.2 Split Lot Testing 585

- 11.5 Defect Density 588

- 11.5.1 Theory 590

- 11.5.2 Defect Density Determination 596

- 11.6 Chip Yield Predictions Based on Defect Density 599 11.6.1 New Devices 599

- 11.6.2 New IC Designs with New Processes 601

- 11.6.3 Devices in Production 602

- 11.6.4 Work in Progress

- 11.6.5 When Yield is Low 603

- 11.7 Determining Causes of Chip Yield Loss 604

- 11.8 Junction Testing 605

- 11.8.1 Reverse-Biased pn Junctions 606

- 11.8.2 Reverse Current Curve Tracer Diagnostics 611

603

- 11.8.3 Reverse-Biased Schottky Junctions 616

- 11.8.4 Forward-Biased pn Junctions 617

- 11.9 MOS Transistor Testing 621

- 11.9.1 Threshold Voltage 621

- 11.9.2 Subthreshold Leakage Current 624

- 11.9.3 Pinchoff Voltage 624

- 11.9.4 Conduction Factors k and k' 624

- 11.9.5 Channel Mobility 626

- 11.9.6 Drain Breakdown Voltage 626

- 11.10 Bipolar Transistor Diagnostics 626

- 11.10.1 Current Gain 627

- 11.10.2 Reverse Breakdown Voltages 630

- 11.10.3 Reverse and Forward Currents 633

### xviii DETAILED CONTENTS

Yield Economics 634 11.11 11.11.1 Silicon Usage 635 11.11.2 Wafer Cost 636 11.11.3 Wafer Diameter 637 11.11.4 Effect of Chip Size on Yield and Cost 638 11.11.5 Revenue from Wafers 639 Factors Affecting Yield and Yield Improvement 640 11.12 Key Ideas 642 Problems 642 References 643

### APPENDIX A Crystallography 645

- A.1 Silicon and Gallium Arsenide Structure 645

- A.2 Crystallographic Defects 654 References 659

### APPENDIX B Phase Diagrams 661

- B.1 Binary Phase Diagrams 661

B.2 Ternary Phase Diagrams 667

References 669

- APPENDIX C Reference Tables 670

Index 673

## **Historical Overview**

## 1.1 BACKGROUND

The semiconductor technology that ultimately led to the integrated circuit (IC) was over 75 years in the making.<sup>1</sup> Around 1875, it was observed that selenium exhibited rectification and photoconductivity. A silicon diode of sorts for detecting radio waves was described in 1906 (1). By 1935, selenium rectifiers and photodetectors, silicon carbide varistors, and galena (naturally occurring lead sulfide) and silicon point contact diodes for radio detection were on the market (2). Also in 1935, a British patent was issued, but was never reduced to practice, for a thin-film field effect transistor (3).

The development of radar just prior to and during World War II placed a great deal of emphasis on the study of silicon (Si) and germanium (Ge) since they were singled out as the most appropriate materials for the mixer and detector diodes required in the radar detection circuitry. Because of this activity, commercial sources of high-purity silicon and germanium were developed. Professor Lark-Horovitz of Purdue University prevailed on Eagle-Pitcher Mining and Smelting Company to develop a high-purity germanium supply, which they did, based on extraction from the lead and zinc ores mined in the tri-state area of Kansas, Missouri, and Oklahoma. (This was the only known significant source of germanium ore in the Western Hemisphere.) During the same period, Professor Seitz of the University of Pennsylvania initiated a program at DuPont to produce high-purity silicon (4).

The few events and names mentioned in this section should neither be construed as representing the total semiconductor activity in that period nor as even necessarily being the most significant. They were chosen to give some idea of progress as a function of time, and in fact, a large number of people, both in industry and in the universities, contributed to the development. To single out a few names and places may seem unfair, but to do otherwise would turn a processing technology text into a volume of semiconductor history. (For more definitive information, see reference 2 and the first 85 references contained therein.)

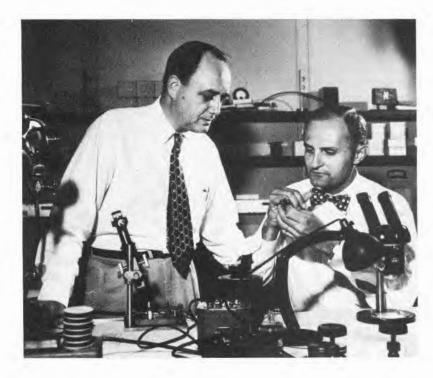

1.2 THE TRANSISTOR

William Shockley (seated at the microscope), John Bardeen (at left), and Walter Brattain, all of Bell Telephone Laboratories, are pictured here about the time of their discovery of the point contact transistor in 1947. This work resulted in their receiving the Nobel Prize for Physics in 1956. (Source: Photograph courtesy of AT&T Archives.)

John Bardeen, co-inventor of the point contact transistor, received a second Nobel Prize in physics in 1972 for his work on the theory of superconductivity. (Source Photograph courtesy of AT&T Archives.)

In December of 1947, the first transistor (a point contact structure) was constructed by John Bardeen and Walter Brattain of Bell Telephone Laboratories. For a discussion of the events leading up to that occasion and of the subsequent work that led to the junction transistor (and to the Nobel Prize in physics for Bardeen, Brattain, and Shockley), see Shockley's paper "The Path to the Conception of the Junction Transistor," *IEEE Trans. on Electron Dev. ED-23*.

The first point contact transistor used polycrystalline germanium for the semiconducting material. However, when the first paper describing the transistor was submitted for publication (June 25, 1948), the transistor effect had been demonstrated in silicon as well (5). By the end of 1949, single-crystalline rather than polycrystalline material was being used (2). This conversion from polycrystalline to single-crystal source material (spearheaded by Gordon Teal of Bell Telephone Laboratories) has been one of the most significant advances in semiconductor technology since the invention of the transistor itself. Without a source of large single crystals with uniform properties, the high-volume production of small devices would have been difficult and development of large-area integrated circuits impossible.

Efforts to build useful structures using polycrystalline or amorphous material thus far have had only spotty success. Amorphous silicon solar cells are now commercially feasible, and diodes utilized as fuses for programming are sometimes built into polycrystalline silicon integrated circuit leads. However, in all cases, single-crystal devices outperform comparable devices made in amorphous or polycrystalline material.

Although the point contact transistors were expensive and unreliable, they were, overall, superior in many respects to vacuum tubes.<sup>2</sup> Consequently, they went into production at Western Electric's Allentown plant in 1951 as replacements for vacuum tubes in some telephone exchange applications. However, by the time the transistor process was licensed to other manufacturers in 1952, William Shockley had invented the grown junction transistor, and Gordon Teal and Morgan Sparks had reduced it to practice (6). This transistor became the industry workhorse for several years. It differed from all subsequent transistor structures in that junction for-

<sup>&</sup>lt;sup>2</sup> Early guided missiles often used magnetic amplifiers instead of vacuum tubes in their control systems because of reliability considerations. The point contact transistor, which in retrospect appears to have been a very fragile and unreliable structure, was in fact good enough to replace the magnetic amplifiers and greatly improve the frequency response of the control systems.

### 1.2 THE TRANSISTOR 3

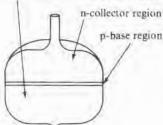

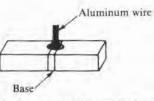

### FIGURE 1.1

Construction details of a silicon grown junction transistor. (Germanium transistors were pnp and used gold wire for the base contact.)

Walter Brattain was a co-inventor of the point contact transistor. (Source: Photograph courtesy of AT&T Archives.)

n-emitter region (heavily doped)

(a) Crystal cut in half for evaluation

(c) Section cut Into "bars" (size, varying with power rating of transistor, but typically 30× 30×150 mils)

(b) Section cut from mid-region of crystal that contains base layer and small section each of collector and emitter regions

(d) Base contact formed by fusing (alloying) aluminum wire to silicon so that wire made ohmic contact to base region and rectifying contacts to collector and emitter

William Shockley, co-inventor of the point contact transistor, was also the inventor of the junction transistor. (*Source:* Photograph courtesy of AT&T Archives.)

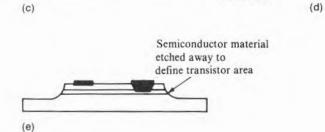

mation was completed during the crystal-growing operation. Fig. 1.1 shows the construction details of a silicon grown junction transistor. The remainder of the manufacturing steps were to affix leads, package, and test. Fig. 1.2 shows a transistor bar<sup>3</sup> mounted in a header. All that remained to be done here was to add a cover and final-test.

Even though both silicon and germanium were demonstrated at the beginning to be usable for transistors, germanium was much more tractable, and silicon transistors (desirable for their highertemperature capability) did not become commercially available until

<sup>&</sup>lt;sup>3</sup> As can be seen from Fig. 1.2, the bit of silicon used in each transistor really did look like a bar. For people and companies that worked extensively with grown junctions, the term *bar* became so deeply rooted that over 30 years later integrated circuits 1 cm on a side and 0.5 mm thick may still be called bars. Those whose experience started with alloyed or diffused units used the terms *chip* or *die*, which today are still common expressions.

### FIGURE 1.2

Grown junction transistor bar mounted in a header. (The collector and emitter connections support the bar; the fine wire is the base connection.)

1954 when grown junction silicon transistors were introduced by Texas Instruments Incorporated (7).

Alloyed junction germanium transistors were reported by Saby of General Electric in 1951 during the same meeting at which the grown junction transistor was first openly discussed (8). These transistors were made by alloying a dot of metal, usually indium, into each side of a chip of germanium, as shown in Fig. 1.3. A pn junction formed at each alloy–germanium interface and provided the collector–base and emitter–base junctions, respectively. Germanium alloyed transistors were very successful and became an alternative to the previously introduced germanium grown junction transistors. However, silicon alloyed transistors were difficult to construct and never commanded a very large market share.

The next important development was the use of gaseous diffusion at Bell Laboratories to make the necessary junctions from one side of a semiconductor slice (9). This activity gave rise to the diffused mesa transistors (10) that were commercially available in germanium in 1957 and in silicon in 1958. Fig. 1.4 shows the steps in their fabrication. There were actually several versions, only one of which is shown here. These mesa transistors had an advantage over either the grown junction or alloy transistors in that the diffusion process could give much narrower and more controlled base widths and thus allow higher-frequency operation. Since many transistors could be made at one time on each silicon or germanium slice, and since many slices could be cut from a single crystal, mesa transistors were less expensive to manufacture than grown junction transistors were. In the latter case, only one slice-or, if the crystal were rate grown (11), perhaps five or six—containing the grown junctions was available from each crystal. Diffused transistors were also less expensive than alloy transistors were since the alloy process required that each chip be processed individually rather than in slice form.

Gordon Teal pioneered the development of single-crystal growth of germanium and silicon and the use of high-purity single-crystal material for semiconductor applications. (*Source:* Photograph courtesy of Gordon K. Teal and AT&T Archives.)

### 1.2 THE TRANSISTOR 5

diffused in

Elm Exhibit 2159, Page 24

The point contact transistor went into production at Western Electric in 1951 and was licensed to other companies for manufacture. Although it was somewhat temperamental, this transistor was, in general, superior in performance to the vacuum tube. (*Source:* Photograph courtesy of AT&T Archives.)

Gordon Teal and Morgan Sparks made the first junction transistor, the construction of which eliminated many of the reliability problems of the point contact transistor. (*Source:* Photograph courtesy of AT & T Archives.)

### 1.2 THE TRANSISTOR 7

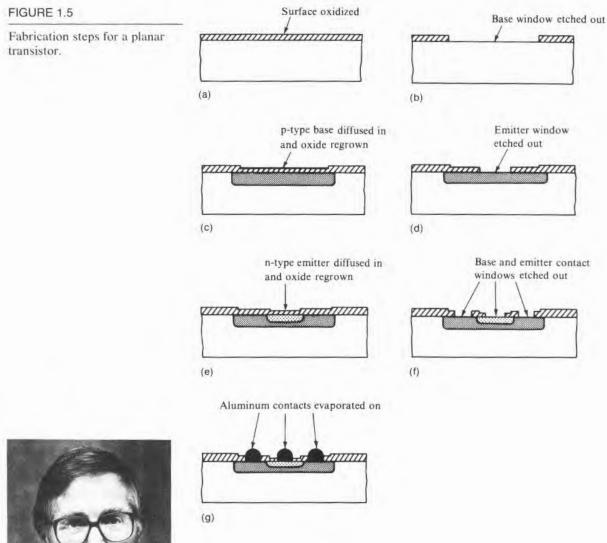

Jean Hoerni invented the planar process, which dramatically improved the reliability of silicon diodes and transistors. (Source: © Carolyn Caddes, 1986, from Portraits of Success.) Unfortunately, all three processes (grown junction, alloy, and mesa) continued to have one serious flaw, and that was the exposed junctions at the semiconductor surface. Various coatings were developed to minimize electrical leakage across those junctions, but they were never completely successful.

The silicon planar transistor, invented by Jean Hoerni of Fairchild Semiconductor, followed shortly thereafter (12) and was in production by 1961. As Fig. 1.5 shows, it very effectively solved the

| TA | RI | F | 11. | 1   |

|----|----|---|-----|-----|

| in | DL | - | 10  | ct: |

| Year | Germanium<br>Units | Silicon<br>Units |

|------|--------------------|------------------|

|      | 0.000              | onno             |

| 1954 | 1.3                | 0.02             |

| 1955 | 3.6                | 0.09             |

| 1956 | 12.4               | 0.42             |

| 1957 | 27.7               | 1.0              |

| 1958 | 45.0               | 2.1              |

| 1959 | 77.5               | 4.8              |

| 1960 | 119                | 8.8              |

| 1961 | 178                | 13.0             |

| 1962 | 214                | 26.6             |

| 1963 | 249                | 50.1             |

| 1964 | 289                | 117              |

| 1965 | 334                | 273              |

| 1966 | 369                | 481              |

Note: All units in millions.

Source: Electronic Industries Association Yearbook, 1967

1.3

THE INTEGRATED CIRCUIT junction protection problem for silicon by allowing the junctions to terminate under a silicon oxide thermally grown on the silicon surface. No other semiconductor has an oxide that can be grown in situ and that possesses the near ideal electrical characteristics of silicon dioxide. The introduction of the planar process, which increased reliability and improved yields, along with the inherently better hightemperature performance of silicon, marked the beginning of the decline of germanium devices. Thus, the four-year period between 1957 and 1961 included first the move to large-scale production with the introduction of the mesa process and then the beginning of the conversion from germanium to silicon with the advent of planar processing. Table 1.1 shows the growth of transistor production through those years, and while the yearly growth rate was no larger in those four years than in any other, it was because of those advances that the phenomenal rate could be sustained. This table also shows the dramatic manner in which silicon overtook germanium in the years following the introduction of the planar process.4 For a business view of the semiconductor world in this transition period between the times of the introduction of mesa and planar processing, see "Report on Semiconductors," Business Week, March 26, 1960.

Until the invention of the integrated circuit, complete circuits, whether they used transistors or vacuum tubes, were made by individually connecting the various components (tubes or transistors, diodes, capacitors, resistors, and inductors) together. Through the years, many improvements were introduced to increase packing density, simplify fabrication, and increase reliability of electronic circuits, but they all continued to depend on the wiring together of discrete and separately packaged devices. In an early effort to attack the problem from a fresh approach, G.W.A. Dummer of the Royal Radar Establishment of the United Kingdom suggested during the May 1952 Electronics Components Symposium in Washington, D.C., an integrated approach using a monolithic block comprising "layers of insulating, conducting, rectifying and amplifying mate-

Elm Exhibit 2159, Page 27

<sup>&</sup>lt;sup>6</sup> It should be appreciated that "production by" and "introduced in" dates are a bit difficult to pinpoint since these dates depend on the first time anyone made and reported such a device, the first time samples were shown to a potential customer, or the time at which reasonable quantities were available to customers. Similar problems arise in other areas, such as the year of introduction of larger crystal diameters.

### 1.3 THE INTEGRATED CIRCUIT 9

Jack Kilby is the inventor of the Solid Circuit® integrated circuit and a co-inventor of the pocket calculator. (Source: Photograph courtesy of Jack Kilby. ®Registered trademark of Texas Instruments Incorporated.)

rials, the electrical functions being connected directly by cutting out areas of the various layers." A metal model of how such a structure might be made was shown in 1957.

The figures included in a patent filed in May of 1953 by Harwick Johnson (U.S. Patent 2,816,228, issued December 10, 1957) bear a superficial resemblance to an integrated circuit. However, as expressed in the first sentence of the patent, both the discussion and claims relate only to a transistor phase-shift oscillator: "This invention pertains to semiconductor devices and particularly to semiconductor phase-shift oscillators and devices." Component isolation was not considered so that even if the concepts of the patent were extended to devices other than the phase-shift oscillator, the class of devices that could be made would be very limited.<sup>5</sup>

In February of 1959, Jack Kilby of Texas Instruments Incorporated filed a patent application describing a concept that allowed, using relatively simple steps, the fabrication of all of the necessary components of the desired circuit, both active and passive, in a single piece of semiconductor and their interconnection in situ. The patent states:

In contrast to the approaches to miniaturization that have been made in the past, the present invention has resulted from a new and totally different concept for miniaturization. . . In accordance with the principles of the invention, the ultimate in circuit miniaturization is attained using only one material for all circuit elements and a limited number of compatible processing steps for the production thereof. . . .

<sup>&</sup>lt;sup>3</sup> Considerable space is being devoted to a discussion of patents and subsequent patent litigation during the development of the integrated circuit. This discussion is provided because of the historical significance and to demonstrate several practical points of the patent world quite germane to the reader. One is that the fame and fortune of an inventor may depend on the precise wording of patent claims. Unfortunately, that wording is often considered to be the domain of the patent attorney and sometimes does not exactly reflect the inventor's intent. (See, for example, the discussion of the lack of a particularly specific figure in Kilby's patent.) Another is that in any new and developing technology, the key problems will be apparent to those active in the field, and they will be offering their individual solutions at about the same time. (Note the close grouping of the events of Table 1.2, which appears later in the chapter.) It is thus very important for the engineer or scientist to keep good records. Yet another point, perhaps not quite as obvious, is that the history of invention as depicted in the popular press, in the scientific literature, and in the issued patents may not be in agreement. To decide on the "true" inventor requires a careful study of all of the literature and also may depend on the particular definition of "inventor" that is chosen.

Up to this point, the goals are perhaps not much different from those expressed in 1952 by Dummer. However, to continue with the Kilby patent:

In a more specific conception of the invention, all components of an electric circuit are formed in or near one surface of a relatively thin semiconductor wafer characterized by a diffused p-n junction or junctions

It is a primary object of the invention to provide a miniaturized electronic circuit wherein the active and passive circuit components are integrated within a body of semiconductor material, the junctions of such components being near and/or extending to one face of the body, with components spaced or electrically separated from one another as necessary in the circuit . . . .

Figures 1–5a illustrate schematically various circuit components fabricated in accordance with the principles of the present invention in order that they may be integrated into, or as they constitute parts of, a single body of semiconductor material; . . .

The figures and text describe bulk resistors, diffused resistors, pn junction capacitors, MOS capacitors, transistors, and diodes. In the press coverage of the March 1959 announcement of the Kilby concept, this set of standard components was stressed (13). The patent text continues:

Because all of the circuit designs described above can be formed from a single material, a semiconductor, it is possible by physical and electrical shaping to integrate all of them into a single crystal semiconductor wafer containing a diffused p-n junction, or junctions, and to process the wafer to provide the proper circuit and the correct component values. . . .

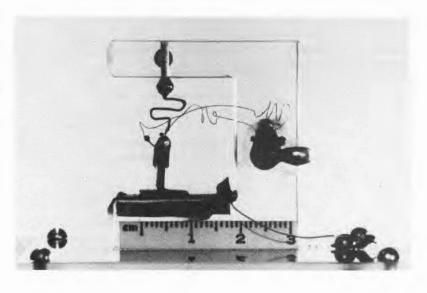

### FIGURE 1.6

One of the first working germanium integrated circuits constructed by Jack Kilby in the summer of 1958. (Source: Courtesy of Texas Instruments Incorporated.)

### FIGURE 1.7

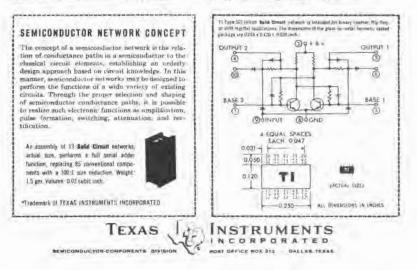

Advertisement for the first commercially available silicon integrated circuits appeared in the March 26, 1960 issue of *Business Week*: (Source: Courtesy of Texas Instruments Incorporated.)

### 1.3 THE INTEGRATED CIRCUIT 11

## AVAILABLE NOW FROM TI 100:1 miniaturization with SOLID CIRCUTT\*

semiconductor networks

Now-3 years ahead of industry's expectations- Only a Solid Circuit semiconductor networks from Texas instrution to ments for many of your high-reliability miniatorized systemations Solid

Solid Circuit networks are a major departure from conventional components because they integrate resistor, capacitor, diode, and transitor functions into a single figh-purity semiconductor water. Protection and packaging of discretic elements is eliminated, and contacts between dissimilar materials are minimized, reducing element interconnections as much as 80%. Fubricistion steps have been reduced to one-tenth those required for the same been reduced to non-tenth those required. Only a few process stops and time-proved T1 mass production tochniques permit a high degree of process control in Solid Circuit network fabrication. The result of these facts reliability is hailt into each Solid Circuit network.

If you need to reduce equipment size and weight—or to design a more complex system in the same size—invesingate Solid Circuit networks for your missile, satellitic, space vehicle, and other microelectronic programs. Ti equipments are ready to custom design this concept to your requirements. Contact your nearest TI Sales Engineer today. The TI Type 502 Solid Circuit network is immediately available for your evaluation,

The first working integrated circuit was built by Kilby in September of 1958 and was, for expediency, fabricated of germanium (Fig. 1.6). The first commercially available integrated circuits, announced in March of 1960 with the advertisement shown in Fig. 1.7, were made of silicon.

It was after the mesa process and before the planar process that Kilby's patent application was filed, and, because of the manner in

Robert Noyce is the inventor of the Microchip® Integrated circuit and a co-founder of both Fairchild Semiconductor Corporation and Intel Corporation. (Source: Photograph courtesy of Intel Corporation.) "Registered trademark of Fairchild Semiconductor Corporation. which the IC construction was described in the Kilby patent (14), when the planar process was introduced, a separate patent on an IC using planar technology and adherent leads was awarded to Robert Noyce of Fairchild Semiconductor (15). That award was the subject of a heated legal battle that arose over whether Kilby's patent statement as follows:

Instead of using the gold wires 70 in making electrical connections, connections may be provided in other ways. For example, an insulating and inert material such as silicon oxide may be evaporated onto the semiconductor circuit wafer through a mask either to cover the wafer completely except at the points where electrical contact is to be made thereto, or to cover only selected portions joining the points to be electrically connected. Electrically conducting material such as gold may then be laid down on the insulating material to make the necessary electrical connections.

covered the portion of the Noyce claims that described "... an electrical connection to one of said contacts comprising a conductor adherent to said layer ... " The disagreement centered around whether "laid down" was equivalent to "adherent to." The Board of Patent Interference, ruling in Kilby's favor, asserted that it was. However, a subsequent ruling by the Court of Customs and Patent Appeals (*Noyce v. Kilby*; *Kilby v. Noyce*, decided November 6, 1969) reversed the previous rulings and allowed the Noyce claims. (The Supreme Court then refused to review the case.) Contrary to assertions by some, the ruling did not depend on whether gold could or could not be made suitably adherent to silicon oxide. The Court specifically commented on that aspect. The ruling depended on the Court's assessment of whether or not someone reading Kilby's statement would be inevitably drawn to the conclusion that the lead should be adherent.

The Noyce patent application<sup>6</sup> was filed a few months after Kilby filed his, as well as after the Kilby concept was made public. However, it was issued April 25, 1961, three years before the Kilby patent. Perhaps because of this anomaly of issuing dates, and perhaps because of a mixing of the idea of a planar silicon integrated circuit with the already announced integrated circuit concept of Kilby, there has been considerable controversy in some circles over the true inventor of the integrated circuit. The sequence of events as portrayed in the patent and technical literature is shown in Table

<sup>&</sup>lt;sup>6</sup> His first notebook date was in January of 1959, before the public announcement of the integrated circuit concept by Texas Instruments, but well after Kilby's original notebook entry and after the Kilby approach had been described to various government agencies.

### 1.3 THE INTEGRATED CIRCUIT 13

1.2. Comments by some of the participants may be found in references 16–18. Additional comments are in references 19–20. Probably the most balanced assessment of Kilby's and Noyce's relative contributions is contained in the citations of the Franklin Institute's 1966 Ballantine Medal award, which they shared. Kilby was credited for "conceiving and constructing the first working monolithic circuit in 1958," and Noyce for "his sophistication of the monolithic circuit for more specialized use, particularly in industry."

One interesting aspect of the sequence shown in Table 1.2 is the issuance of the K. Lehovec patent for the use of a plurality of pn junctions for isolating integrated circuit components. It has been considered by some as being key to integrated circuit development in that it provided the necessary component isolation (21). Histori-

### TABLE 1.2

Key Events in Development of the Integrated Circuit

| Date             | Event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Responsible<br>Party                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| February 6, 1959 | File date of U.S. Patent 3,138,743, which stated: "This invention<br>relates to miniature electronic circuits, and more particularly to<br>unique integrated electronic circuits fabricated from<br>semiconductor material."                                                                                                                                                                                                                                                                                                                                 | J.S. Kilby                                |

| March 6, 1959    | Public announcement of concept described in Kilby patent<br>application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Texas Instruments<br>Incorporated         |

| April 22, 1959   | File date of U.S. Patent 3,029,366, which covered electrical<br>isolation through the use of at least two pn junctions between<br>each component and described conductive ink interconnections<br>over deposited oxide.                                                                                                                                                                                                                                                                                                                                      | K. Lehovec                                |

| May 1, 1959      | File date of U.S. Patent 3,025,580, which covered the planar process for making planar transistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | J.A. Hoerni                               |

| July 3, 1959     | File date of U.S. Patent 2,981,877, which stated: "Its principal<br>objects are these: to provide improved device-and-lead structures<br>for making electrical connections to various semiconductor<br>regions; to make unitary circuit structures more compact and<br>more easily fabricated in small sizes than has heretofore been<br>feasible; and to facilitate the inclusion of numerous<br>semiconductor devices within a single body of material." This<br>patent covered the use of planar transistors and metallization<br>running over the oxide. | R.N. Noyce                                |

| August 1959      | Public announcement of transistors built by planar process,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Fairchild<br>Semiconductor<br>Corporation |

| March 26, 1960   | Public announcement of availability of solid circuit silicon<br>multivibrator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Texas Instruments<br>Incorporated         |

| October 1960     | Technical meeting at which planar process was described.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | J.A. Hoerni                               |

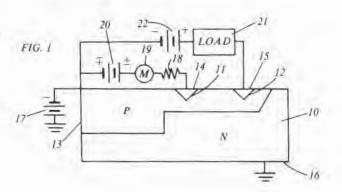

cally, pn junction isolation of a single discrete device was mentioned in a 1954 Shockley patent describing the use of ion implantation in transistor fabrication (22). Fig. 1.8 is a circuit diagram taken from that patent. Shockley's discussion relating to the pn junction was as follows: "It will be noted that the junction between the N body and the P layer is biased in the reverse direction. Hence the body serves essentially as a passive support for the layer." Then, before the Lehovec patent, the Kilby patent had already addressed the general problem of isolation when several components were present in one wafer and suggested various ways of providing it. One was by the use of high-resistivity material (used in gallium arsenide circuits), and one was by the use of pn junction isolation. The pertinent Kilby patent text is as follows:

Of importance to this invention is the concept of shaping. This shaping concept makes it possible in a circuit to obtain the necessary isolation between components and to define the components or, stated differently, to limit the area which is utilized for a given component. Shaping may be accomplished in a given circuit in one or more of several different ways. These various ways include actual removal of portions of the semiconductor material, specialized configurations of the semiconductor material such as long and narrow, L-shaped, U-shaped, etc., selective conversion of intrinsic semiconductor material by diffusion of impurities thereinto to provide low resistivity paths for current flow, and selective conversion of semiconductor material of one conductivity type to conductivity of the opposite type wherein the p-n junction thereby formed acts as a barrier to current flow [italics added].

The Lehovec patent was filed after the filing of the Kilby patent and later was the subject of an interference proceeding by Kilby. Since the Kilby discussion supports pn junction isolation, if one of his figures had included *two* diffused resistor components instead of just one, the Lehovec patent probably would never have been is-

### FIGURE 1.8

Fig. 1 from U.S. Patent 2,666,814 (filed April 27, 1949; issued January 19, 1954) showing use of a reverse-biased pn junction for electrical isolation.

### 1.3 THE INTEGRATED CIRCUIT 15

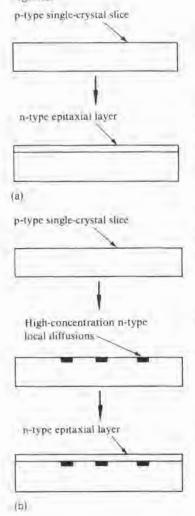

### FIGURE 1.9

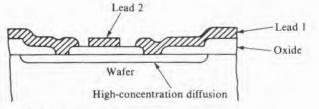

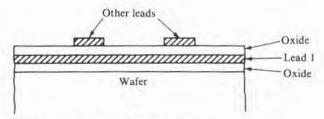

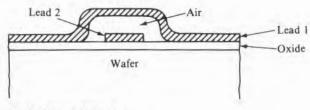

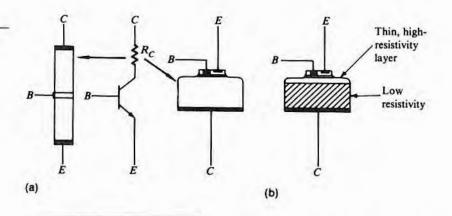

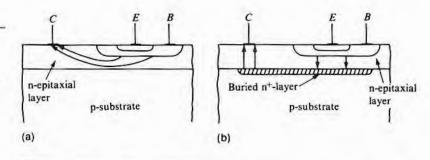

(a) Use of an epitaxially grown thin layer of n-type silicon on a p-type slice to provide part of the required electrical isolation. (b) Use of that layer combined with localized n-type diffusions to improve performance of transistors built in the layer over the diffused regions.

sued. The Board of Patent Interference ruled that Kilby's patent did not cover the Lehovec claims. It did not, however, rule on whether the Lehovec patent covered the methods typically used for IC isolation. In fact, the claims do not appear to support the case of ordinary bipolar IC isolation, although that aspect has not been addressed by the courts. Lehovec's text describes the use of two or more junctions for isolation that extend from one face of the semiconductor body to the other but does not mention the typical IC isolation case in which all junctions terminate on the same side of the wafer. His claims typically state:

A multiple semiconductor assembly comprising a semiconductor slice having a plurality of regions of alternating p and n conductivity types to thereby provide a plurality of p-n junctions, two of said regions being separated by at least two of said p-n junctions, ....

The "two of said regions being separated by at least two of said p-n junctions, . . ." would apply to an IC, but "a semiconductor slice having a plurality of regions of alternating p and n conductivity types to thereby provide a plurality of p-n junctions . . ." does not appear to apply since isolation for a whole chip is normally provided by just one p-type region and multiple n-type regions.

Despite the fact that there were no interconnection claims. Lehovec described in the body of his patent an interconnection method that used conductive ink over an evaporated quartz insulating layer. Since conductive inks are adherent and since his patent was filed before Noyce's, one can speculate that had a related claim been included in his patent application, he would now have the patent on IC interconnections.

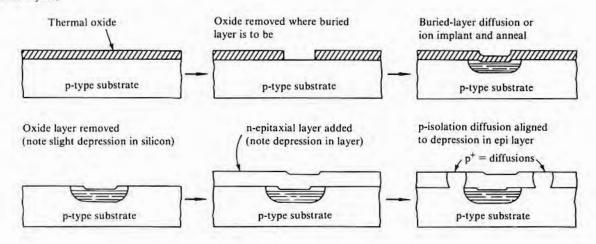

Two later developments, while not directly related to IC development, contributed greatly to bipolar IC manufacturing ability and performance. One was the use of epitaxial overgrowth (23), which in IC applications allowed a thin n-type layer to be overgrown on a high-resistivity p-type substrate, as shown in Fig. 1.9a. The other was the use of localized high-concentration diffusions before the growth of the epitaxial layer, as shown in Fig. 1.9b. in order to reduce transistor collector resistance (24).

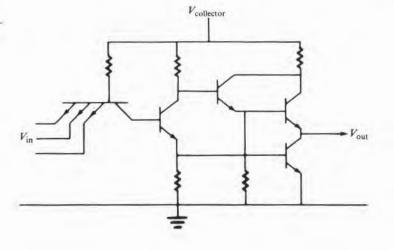

While early IC work was all bipolar, in 1960, a practical MOS transistor was announced (25, 26), and by 1962, a MOS IC consisting of 16 silicon n-channel transistors had been constructed (27). Efforts to use germanium, either by itself or overgrown onto semi-insulating gallium arsenide (GaAs), as a material for ICs continued for several years but never proved successful. GaAs was, however, by the mid-1980s being used for niche applications requiring very-high-frequency ICs.

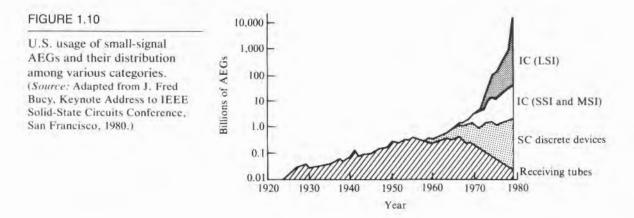

Silicon thus remains the mainstream material, and as shown in Fig. 1.10, the U.S. usage of silicon ICs had reached astronomical proportions by 1980. As represented in Fig. 1.10, this usage is given in terms of AEGs, or active element groups, which might, for example, consist of a single-stage amplifier, a single gate, or a single bit of memory. The term was apparently first applied in a limited manner to vacuum tube circuits and then by Patrick Haggerty (*IEEE Spectrum 1*, pp. 80–82, June 1964) to transistor circuits. Each AEG is made up of various combinations of the following:

- Bipolar transistors, with or without multiple emitters or collectors

- 2. pn junction diodes, which can also be used as capacitors

- 3. Conventional metal-plate capacitors

- 4. MOS transistors

- 5. MOS capacitors

- 6. MIS transistors

- 7. Schottky diodes

- 8. Diffused resistors

- 9. Thin-film resistors

- 10. Interconnecting leads

Conspicuously missing from this list of available components are inductors. It is true that small inductors can be made by spiraling a conductor and that at some frequencies there can be enough phase shift to make a transistor behave as though inductance is present. However, for all practical purposes, the IC world remains inductorless.

### 4 SEMICONDUCTOR PROCESSES 17

## 1.4 SEMICONDUCTOR PROCESSES

The major semiconductor wafer fabrication steps in the mesa process of 1958 were diffusion, metallization, silicon etching, and various cleanups. It was with these steps that the first ICs were made. The planar process of 1960 introduced three more steps: thermal oxidation of silicon (as a step separate from diffusion), lithographic printing of a pattern in a photoresist layer on top of the oxide, and the etching of that pattern in the oxide. Since 1960, there have been only four processing innovations that allow new kinds of structures or circuits to be fabricated, and they were all developed in the 1960s. They were as follows:

- The use of epitaxial layers in bipolar circuits to provide an easy method of device isolation. (Later, epitaxial layers were deposited over previously diffused areas of the circuit to reduce collector saturation resistance and time, thus providing high-speed circuitry.)

- The use (in 1963) of epitaxial overgrowth of silicon onto insulating substrates such as sapphire.

- The use of chemically vapor-deposited (CVD) materials, such as silicon nitride, first (in 1965) for protective overcoats and later as diffusion masking material.

- The use of ion implantation (first practical application in 1968 for MOS threshold adjusting) as an adjunct to diffusion.

This is not to imply that the industry has been stagnant, however. Tremendous strides have been taken in increasing the complexity of IC circuitry available and in decreasing the cost of each AEG. However, these advances have been accomplished primarily through the use of more sophisticated equipment and through process variants such as the use of plasma etching instead of wet etching and optical steppers and the use of electron beam writers or X-ray printing instead of contact printers or the original handpainted black wax for patterning. Table 1.3 illustrates the growth in capability and cost of printing technology during the past 30 years. The increasing complexity of patterning equipment is typical of the other processes as well.

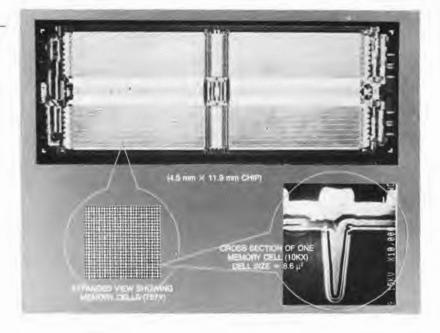

Besides the advances made in processing equipment, other parts of the industry have changed as well. The increase in circuit complexity can be judged by comparing the first commercially available ICs (like the one in the advertisement shown in Fig. 1.7, which consisted of a single flip-flop with two transistors, four diodes, four capacitors, and six resistors) with a large MOS memory such as the one megabit DRAM chip shown in Fig. 1.11, which contains a mil-

# 18 CHAPTER 1 HISTORICAL OVERVIEW

# TABLE 1.3

The Increasing Complexity of Patterning Equipment

| Year  | Size of Feature<br>Patterned | Steps in Operation                                                                                                                      | Equipment Cost<br>per Machine<br>in Year of<br>Purchase | Comments                                        |

|-------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------|

| 1957  | 10 mils*                     | Handpaint black wax on<br>area to be protected;<br>etch mesas                                                                           | \$0.10                                                  | Camel's hair brush                              |

| 1960  | 2 mils                       | Apply photosensitive layer<br>("resist"); use contact<br>printer and mask to<br>expose desired area;<br>develop resist; etch<br>feature | \$2,000                                                 | In-house constructed contact printer            |

| 1965  | 0.6 mils                     | Contact printer                                                                                                                         | \$5,000                                                 | Commercial contact printer                      |

| 1970  | 0.4 mils                     | Contact printer                                                                                                                         | \$15,000                                                | Commercial contact printer                      |

| 1975  | 0.15                         | Optical projection printing.                                                                                                            | \$80,000                                                | Optical projection printing                     |

| 1980  | 0.08                         | Optical projection printing                                                                                                             | \$120,000-500,000                                       | Optical projection printing                     |

| 1985  | 0.06 mils                    | Optical projection or<br>electron beam printing                                                                                         | \$500,000-3,000,000                                     | Optical projection or electron beam<br>printing |

| 1990† | 0.024                        | Optical projection,<br>electron beam, or X-ray<br>printing                                                                              | \$500,000-3,000,000                                     | Optical projection or electron beam<br>printing |

\*The semiconductor industry began by using mils, and that terminology is used for comparison throughout this table. †Projected.

Note: For a description of patterning equipment, see Chapters 2 and 5.

lion memory cells plus thousands of additional transistors for various other operations. In ICs of the 1960s, chip area was perhaps  $0.01 \text{ cm}^2$ ; it is now approaching  $1 \text{ cm}^2$ . Thus, while chip size has increased, it has by no means followed commensurately with circuit complexity. The  $100 \times$  increase in area has been accompanied by a millionfold increase in circuit elements.

The slice diameter has also steadily increased since the introduction of the IC, as shown in Table 1.4. In some cases, the impetus has been to improve yields; in some, to reduce equipment and facility costs; and in others, to reduce labor costs. Not shown by the table is the small dip in the slice diameter that occurred in 1960–1962 because of the difficulty in producing uniform epitaxial depositions on slices of diameters larger than 18–20 mm.

## 1.4 SEMICONDUCTOR PROCESSES 19

# FIGURE 1.11

One megabit CMOS DRAM chip. (Source: Courtesy of Texas Instruments Incorporated.)

Circuit design has become much more sophisticated and attuned to space-saving features since the first flip-flops were introduced. Two or three layers of interconnections between circuit elements are now used, and the number of active devices required to perform a given function has decreased. For example, some of the early DRAM memory cells required six transistors, whereas now one transistor and one capacitor suffice. Also, much more attention is given to designs that are more tolerant of the expected process variations. Simultaneously, process control has been continually tightened through better understanding of the processes and the introduction of microprocessor control of most of the equipment. With the recognition that most yield loss is associated with particulates on the slice, extensive effort has been expended to provide better cleanups, cleaner and purer chemicals, and a cleaner manufacturing environment.

Probably the most dramatic way of displaying the effect of all of the improvements on semiconductor manufacturing during the past three decades is to compare silicon usage with semiconductor output, as is done in Table 1.5. To dramatize the effect of the original inventions and the subsequent improvements on our daily lives can be done by mentally eliminating all of the things around us that depend on transistors for their successful operation.

# TABLE 1.4

| Year | Diameter (mm) |

|------|---------------|

| 1955 | 25*           |

| 1960 | 25            |

| 1965 | 37            |

| 1970 | 50            |

| 1975 | 75            |

| 1980 | 100           |

| 1985 | 150           |

1.1 01

# 20 CHAPTER 1 HISTORICAL OVERVIEW

| TABL | E 1 | 15   |

|------|-----|------|

| INDL | 100 | 0.00 |

Silicon Usage Compared with Semiconductor Output

| Year | Polycrystalline<br>Silicon (tons) | Silicon Transistors<br>(millions) | IC<br>AEGs<br>(billions) |

|------|-----------------------------------|-----------------------------------|--------------------------|

| 1955 | 5                                 | 0.09                              | -                        |

| 1960 | 30                                | 8.8                               | -                        |

| 1965 | 50                                | 273                               | -                        |

| 1970 | 500                               | -                                 | 2                        |

| 1975 | 1500                              |                                   | 200                      |

| 1980 | 3000                              | -                                 | 10,000                   |

Sources: Data on polycrystalline silicon from reference 2 and industry estimates. Data on silicon transistors from *Electronic Industries Association* Yearbook, 1967.

# REFERENCES 1

- G.W. Pickard, "Thermo-Electric Wave Detectors," *Electrical World* 4, p. 1003 (L), November 24, 1906.

- G.K. Teal et al., Chap. 6, "Semiconductor Materials," in James F. Young and Robert Shane, eds., *Material Processes*, Marcel Dekker, New York, 1985.

- Oskar Heil, "Improvement in or Relating to Electrical Amplifiers and Other Control Arrangements and Devices." British Patent 439,457, September. 26, 1939.

- Henry C. Torrey and Charles A. Whitmer, Crystal Rectifiers, McGraw-Hill Book Co., New York, 1948.

- J. Bardeen and W.H. Brattain, "The Transistor, A Semi-Conductor Triode," Phys. Rev. 74, pp. 130-231, 1948.

- W. Shockley, M. Sparks, and G.K. Teal, "p-n Junction Transistors," *Phys. Rev.* 83, pp. 151– 162, 1951.

- G.K. Teal, "Some Recent Developments in Silicon and Germanium Materials and Devices." paper presented at National IRE Conference, Dayton, May 10, 1954.

- J.S. Saby, "Fused Impurity p-n-p Junction Transistors," Proc. IRE 40, pp. 1358–1360, 1952.

- G.L. Pearson and C.S. Fuller, "Silicon p-n Junction Power Rectifiers and Lightning Protectors," *Proc. IRE* 42, p. 760 (L), 1954.

- M. Tanenbaum and D.E. Thomas, "Diffused Emitter and Base Silicon Transistors," *Bell* Syst. Tech. J. 35, pp. 1–22, 1956. Charles A. Lee, "A High-Frequency Diffused Base Germanium Transistor," *Bell Syst. Tech. J.* 35, pp. 23–24, 1956.

- R.N. Hall, "p-n Junctions Produced by Rate Growth Variations," *Phys. Rev.* 88, p. 139, 1952.

- Jean A. Hoerni, "Planar Silicon Transistors and Diodes," paper presented at IRE Electron Devices meeting, Washington, D.C., October 1960, J.A. Hoerni, "Method of Manufacturing Semiconductor Devices," U.S. Patent 3,025,589, March 20, 1962 (filed May 1, 1959).

- "Ultramicroscopic Circuits." Electronic Design, April 29, 1959.

- J.S. Kilby, "Miniaturized Electronic Circuits," U.S. Patent 3,138,743, June 23, 1964 (filed February 6, 1959).

- R.N. Noyce, "Semiconductor Device-and-Lead Structure," U.S. Patent 2,918,877, April 25, 1961 (filed July 30, 1959).

- Jack S. Kilby, "Invention of the Integrated Circuit," *IEEE Trans. on Electron Dev. ED-23*, pp. 648–654, 1976.

- Robert Noyce. "Microelectronics." Scientific American 237, pp. 63–69, 1977.

- 18. Kurt Lehovec, "Invention of p-n Junction Iso-

REFERENCES 21

lation in Integrated Circuits," *IEEE Trans. on Electron Dev. ED-25*, pp. 495–496, 1978.

- M.F. Wolff, "The Genesis of the Integrated Circuit," *IEEE Spectrum* 13, pp. 45–53, August 1976.

- C. Lester Hogan, "Reflections on the Past and Thoughts about the Future of Semiconductor Technology," *Interface Age 2*, pp. 24–36, March 1977.

- Sorab K. Ghandhi, *The Theory and Practice of* Microelectronics, John Wiley & Sons, New York, 1968.

- W. Shockley, "Semiconductor Translating Device," U.S. Patent 2,666,814, January 19, 1954 (filed April 27, 1949).

- 23. H.C. Theuerer et al., "Epitaxial Diffused Transistors," Proc. IRE 48, pp. 1642–1643, 1960.

- B.T. Murphy, "Monolithic Semiconductor Devices," U.S. Patent 3,237,062, February 22, 1966 (filed October 20, 1961).

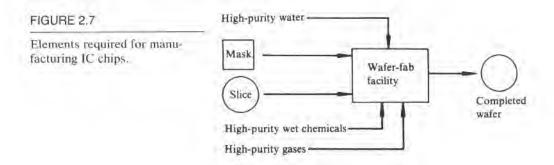

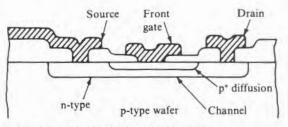

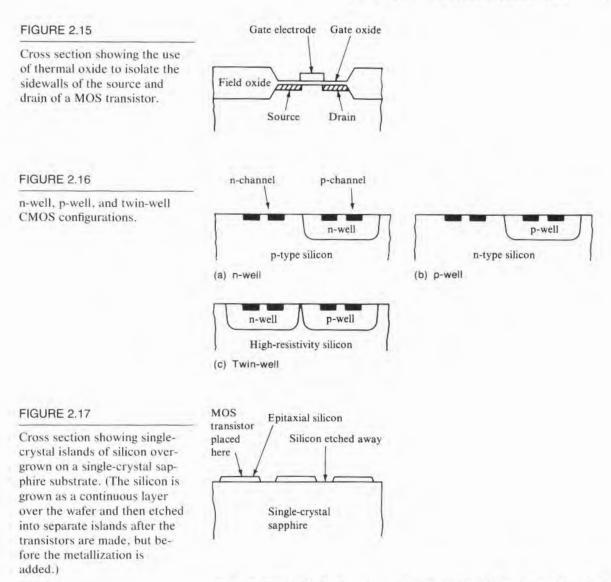

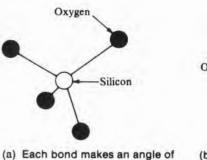

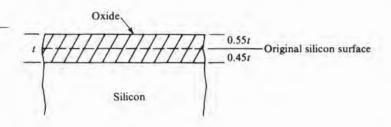

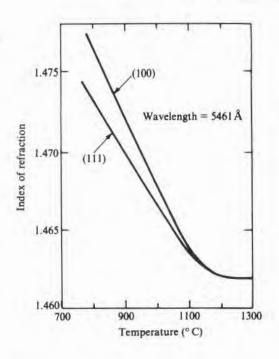

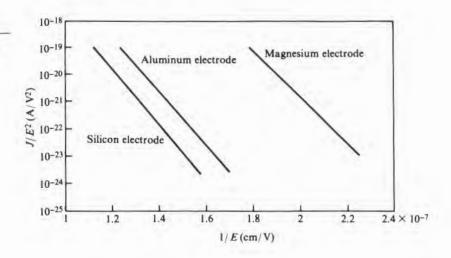

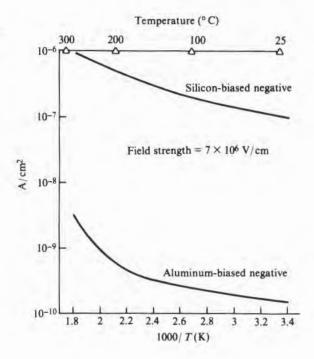

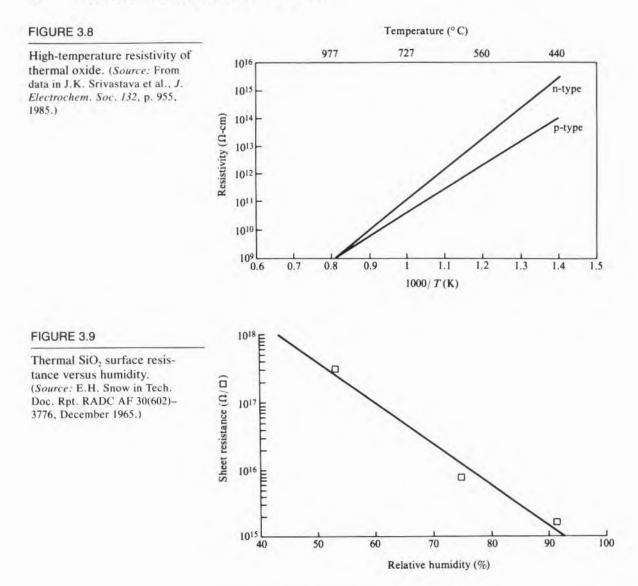

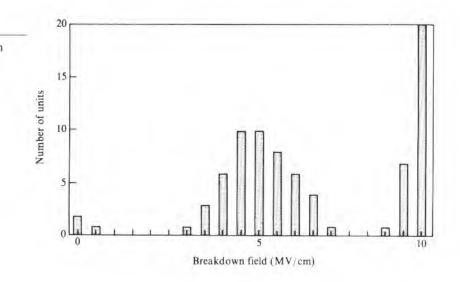

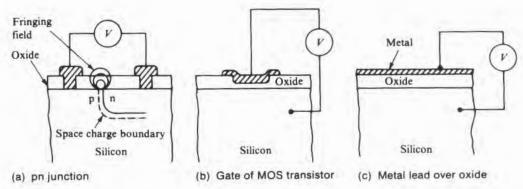

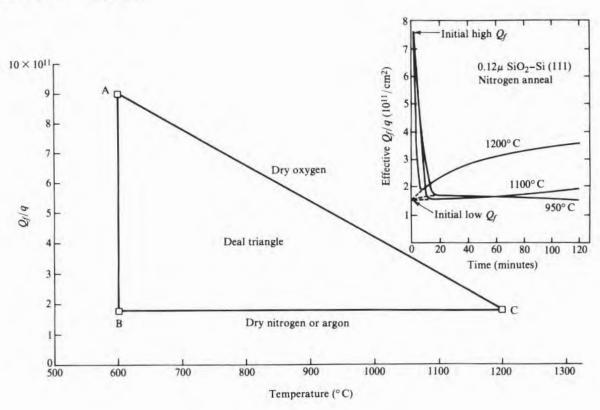

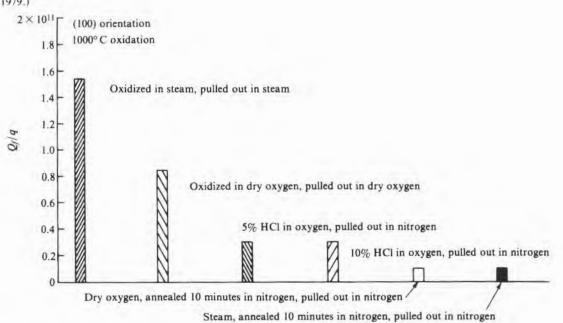

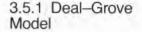

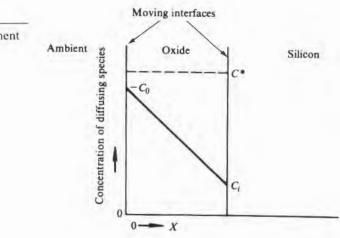

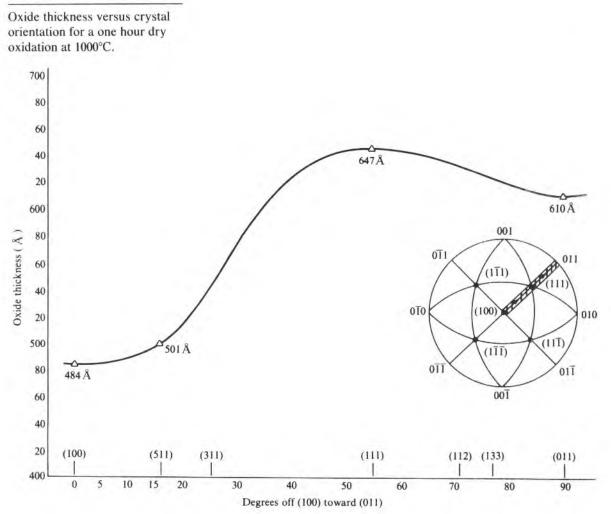

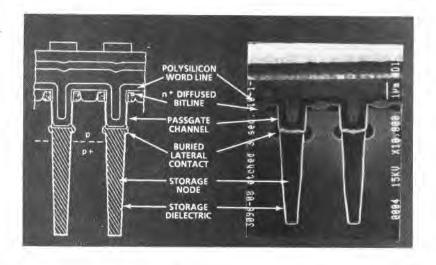

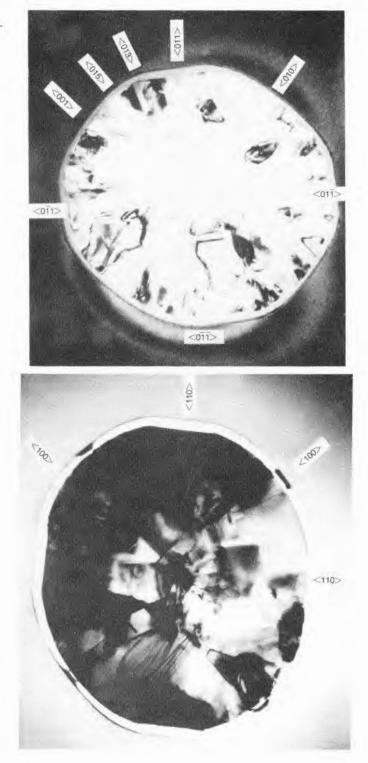

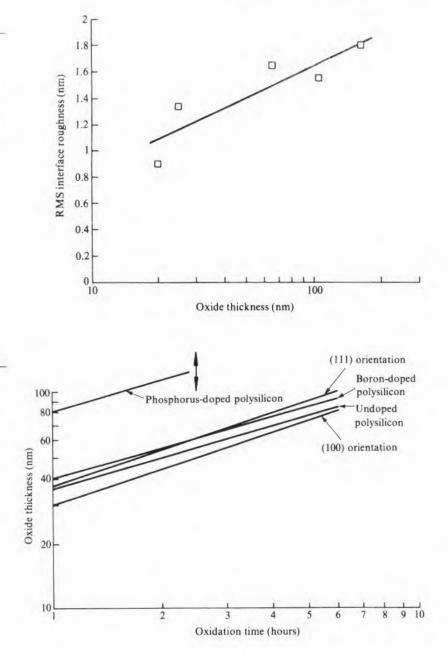

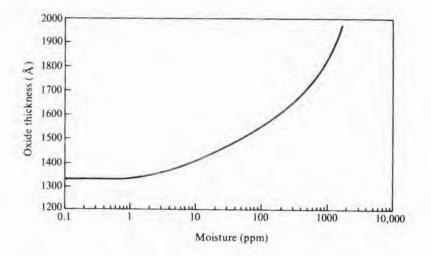

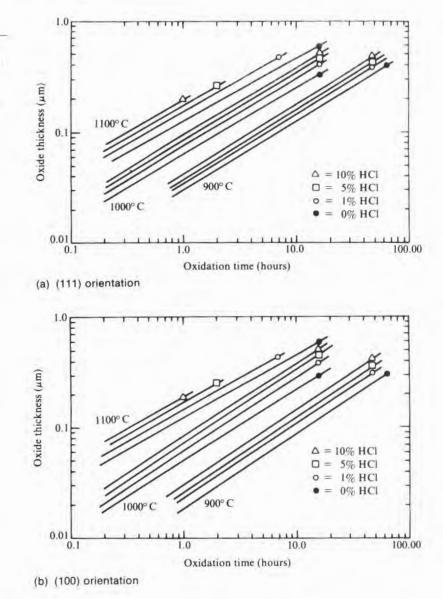

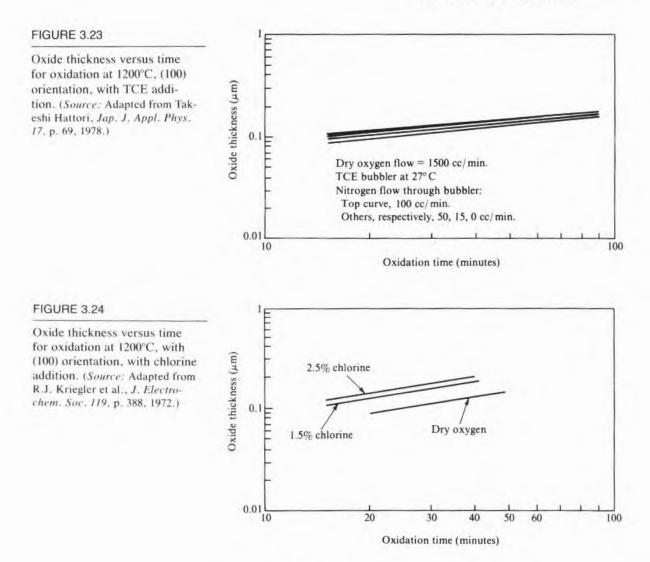

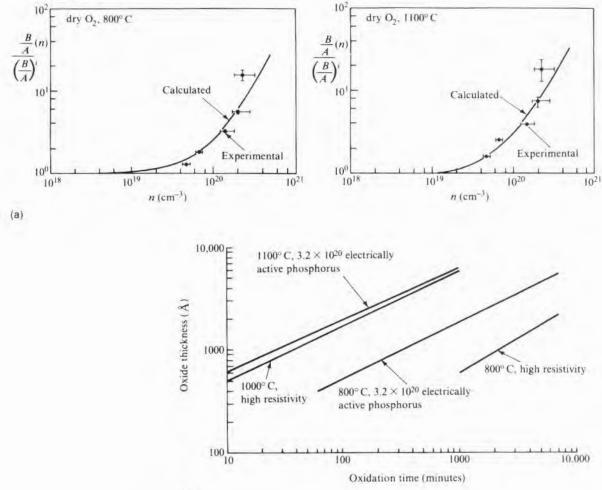

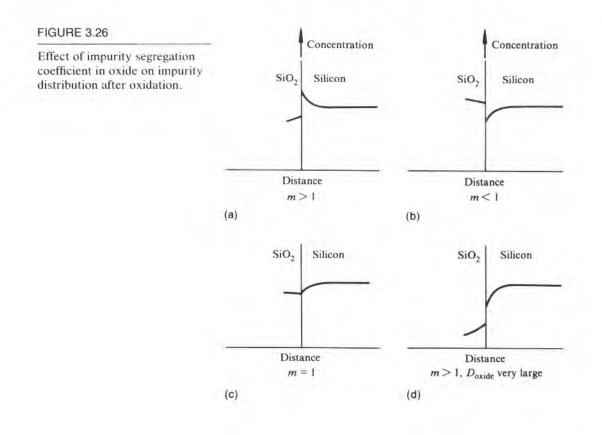

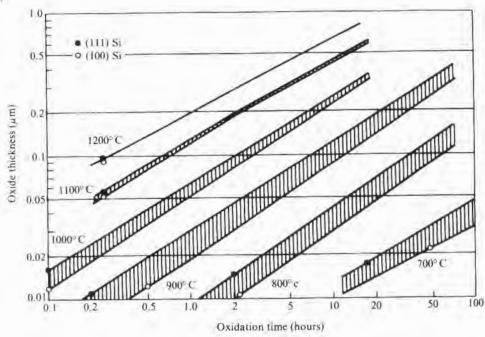

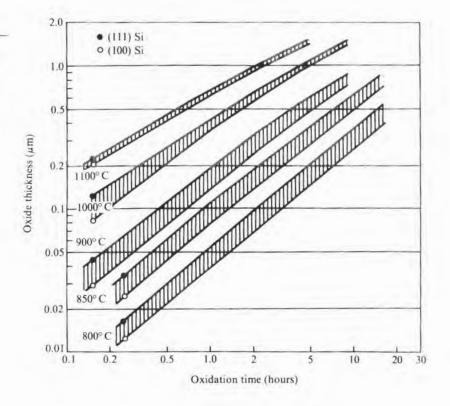

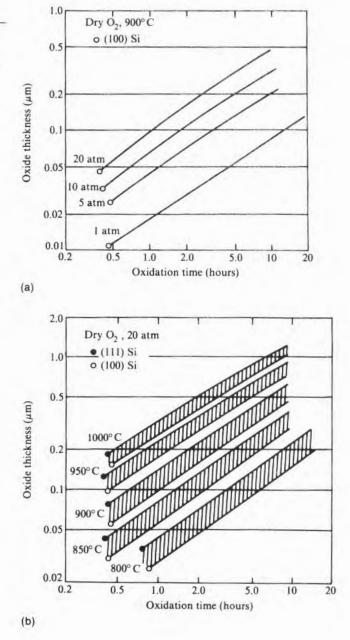

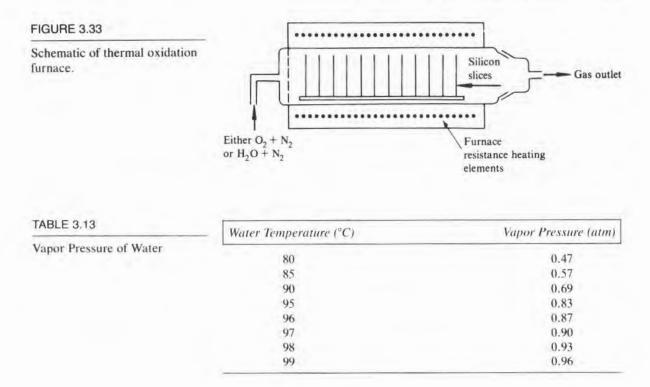

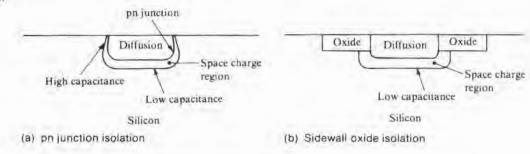

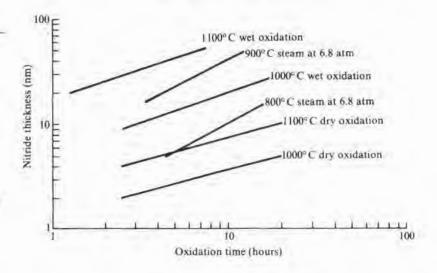

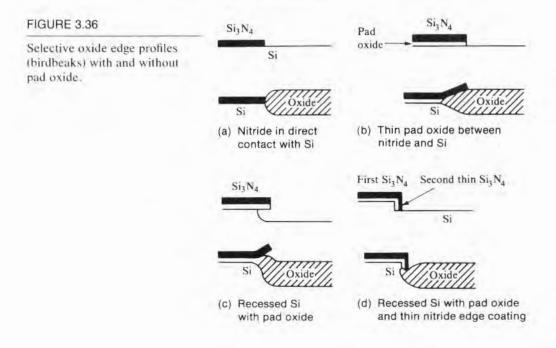

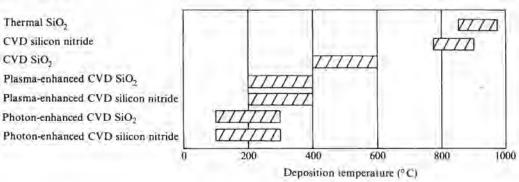

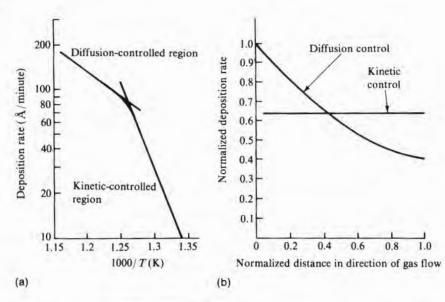

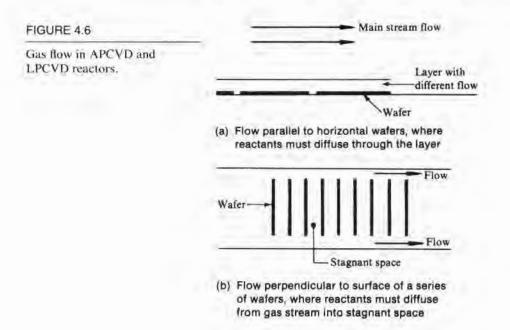

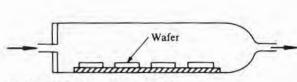

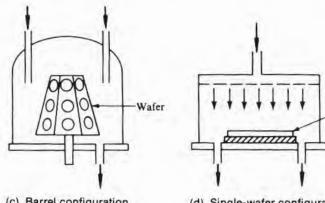

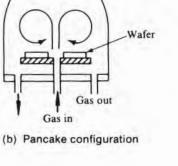

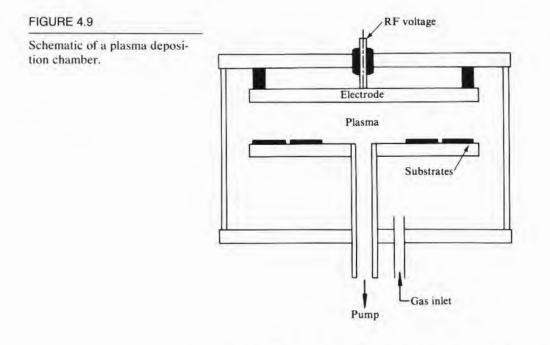

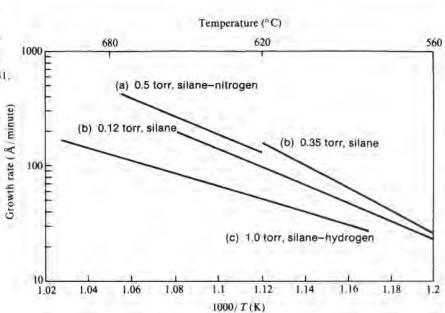

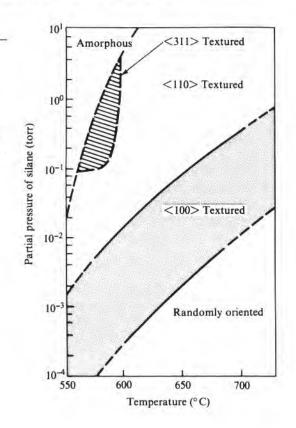

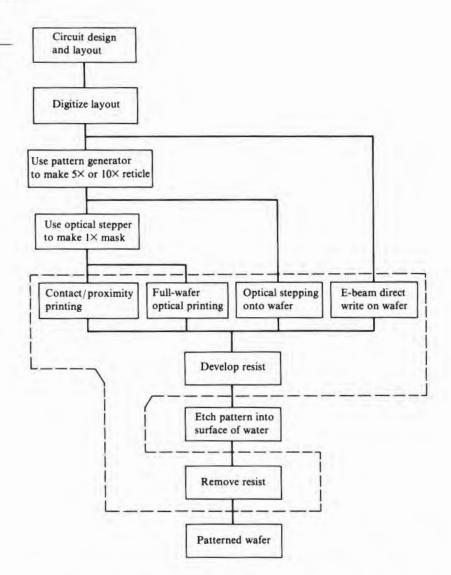

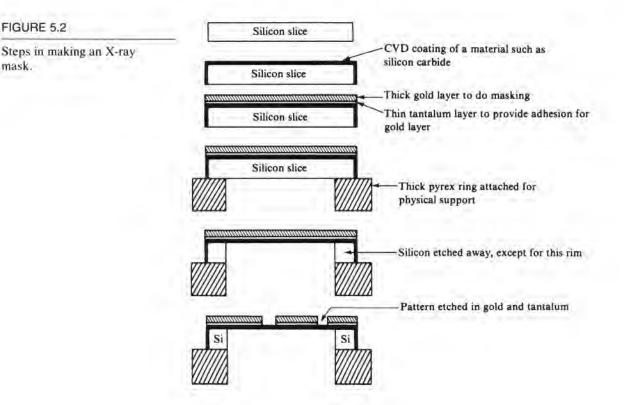

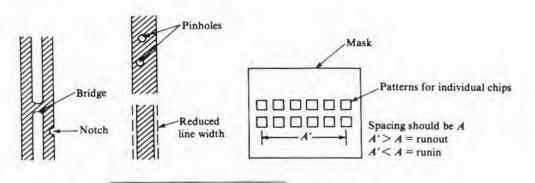

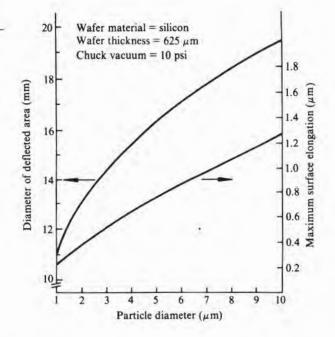

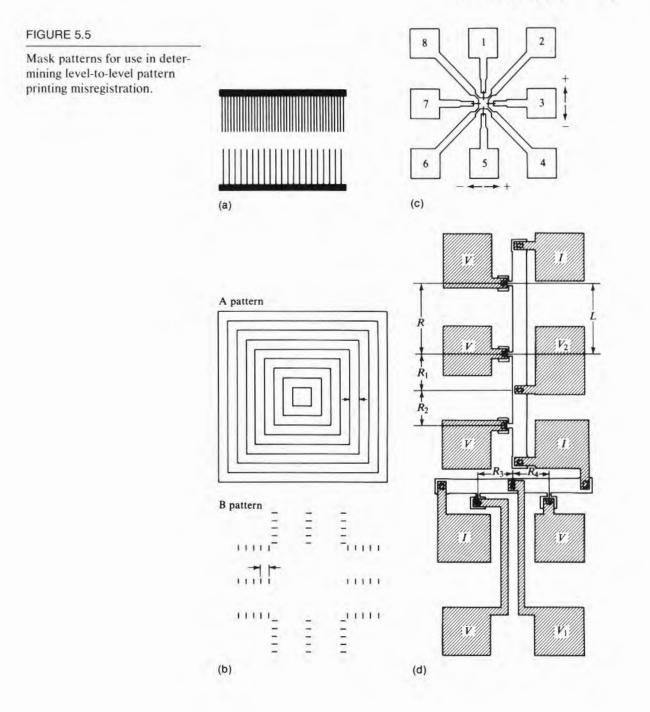

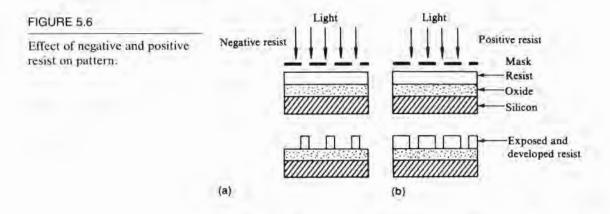

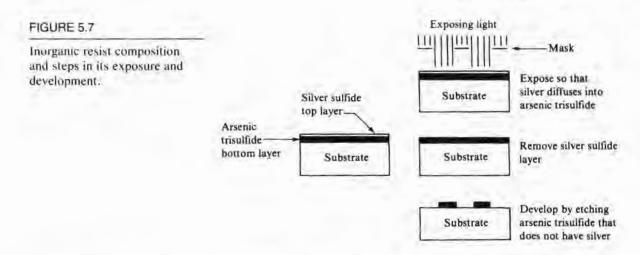

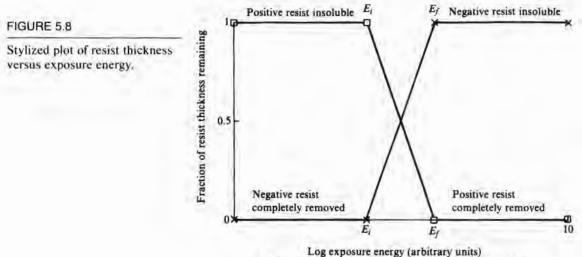

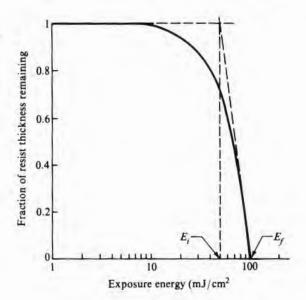

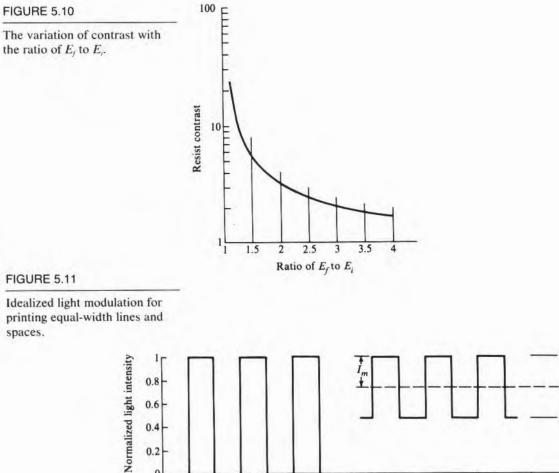

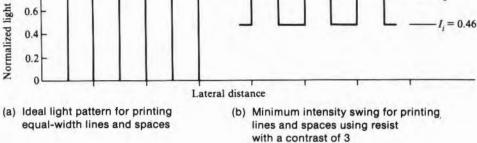

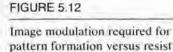

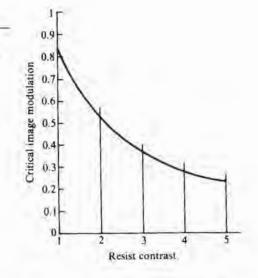

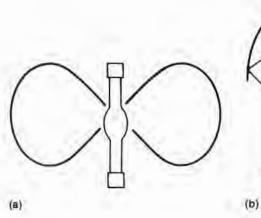

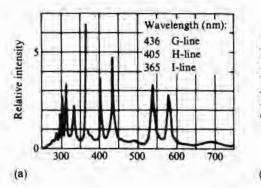

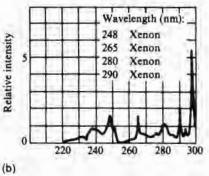

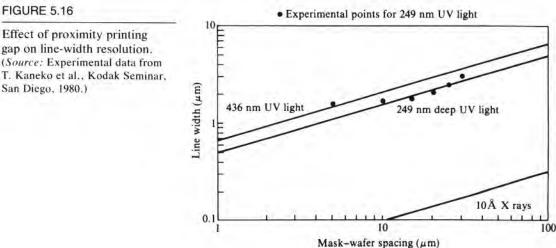

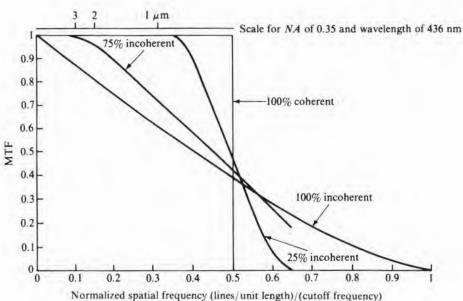

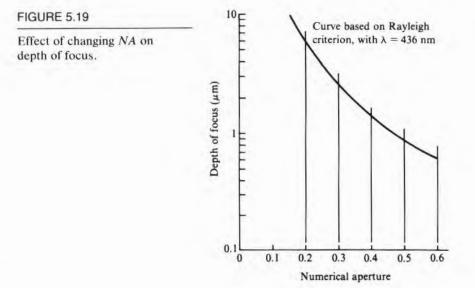

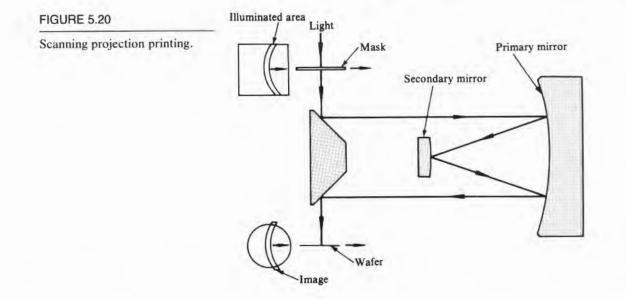

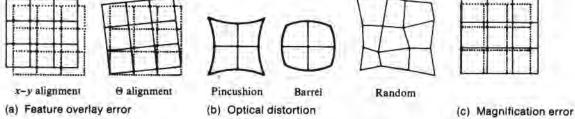

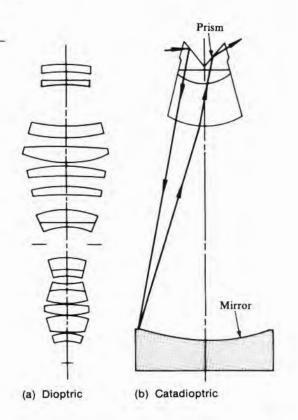

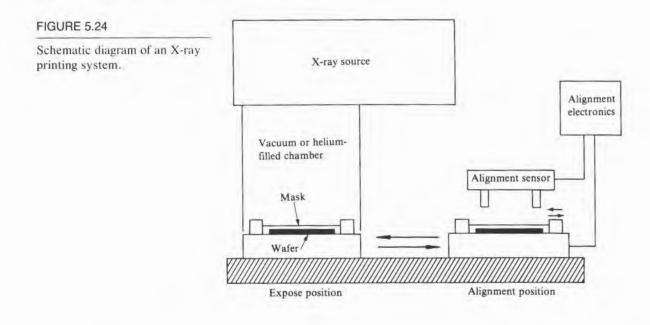

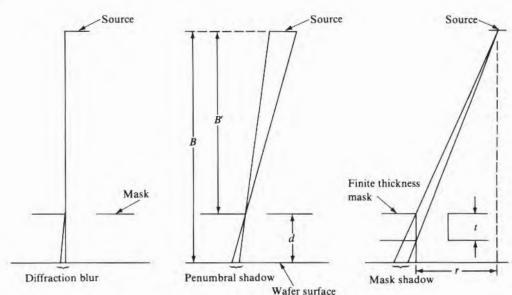

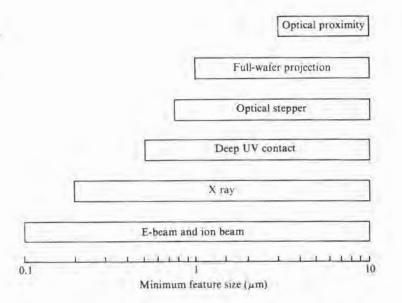

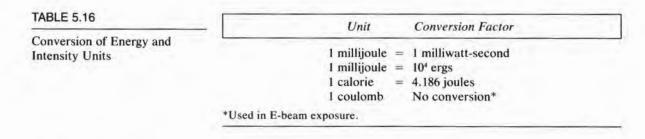

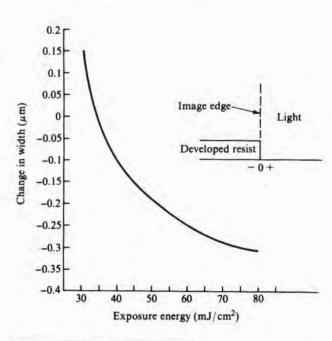

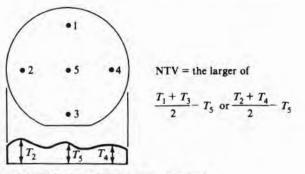

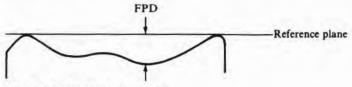

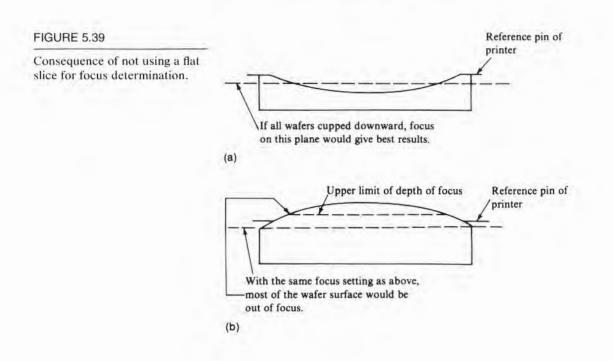

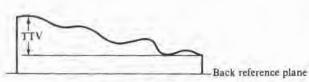

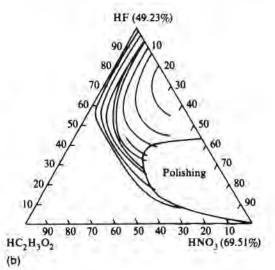

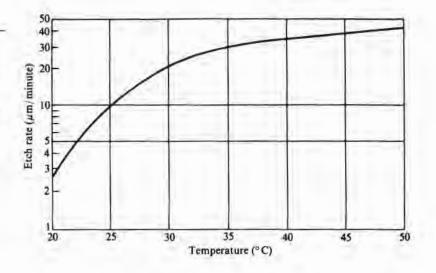

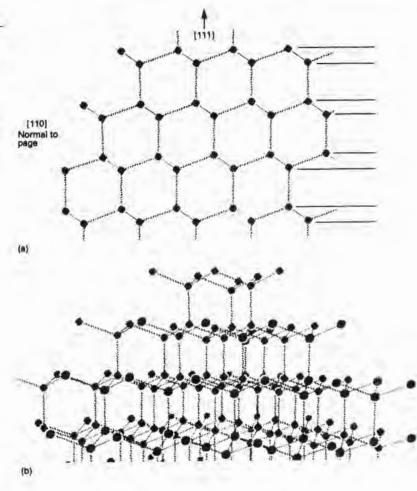

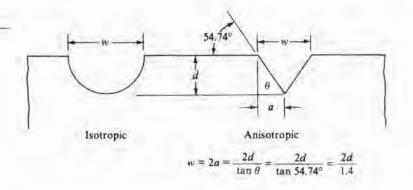

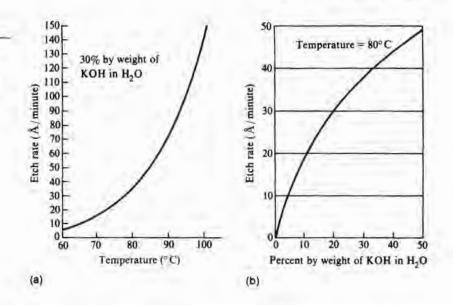

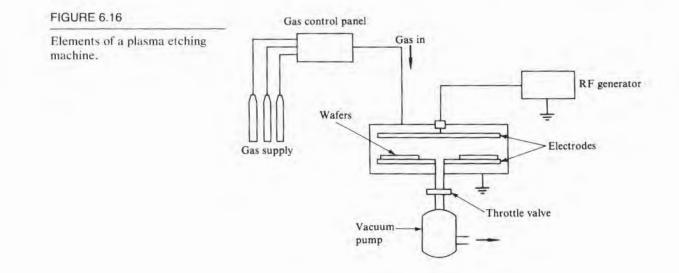

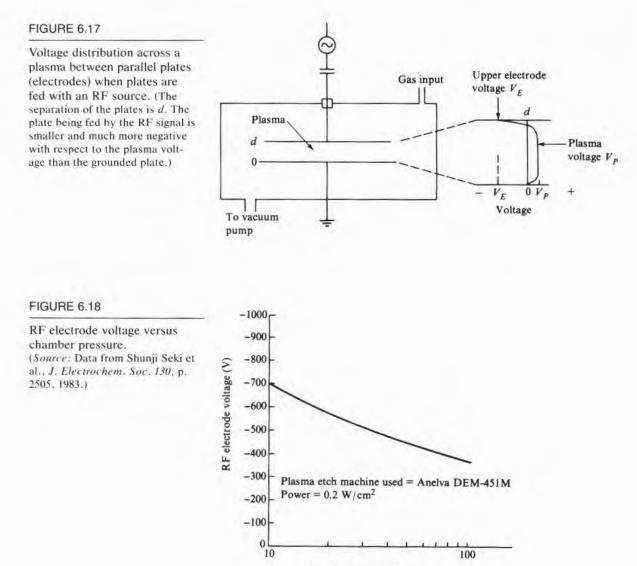

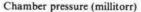

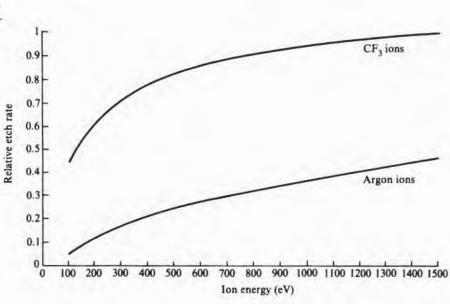

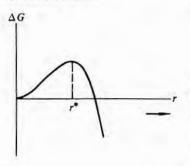

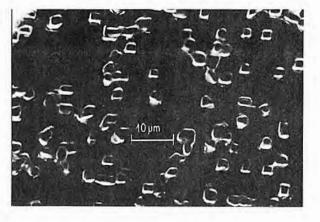

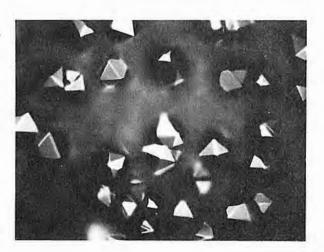

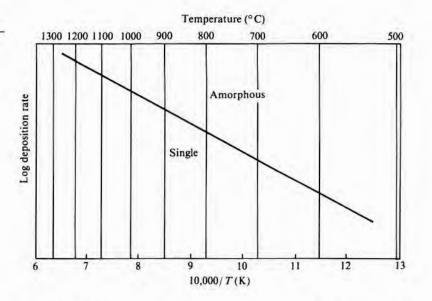

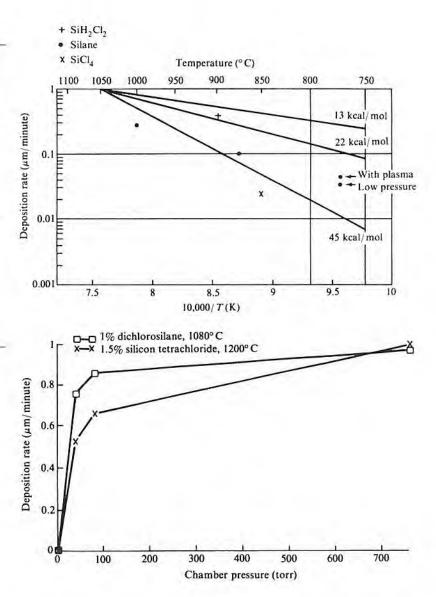

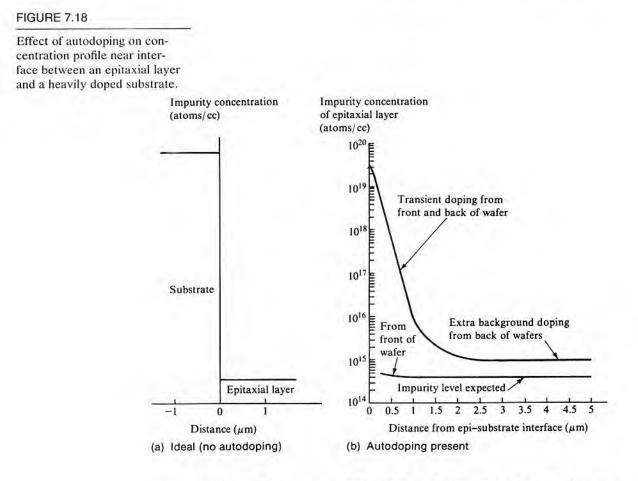

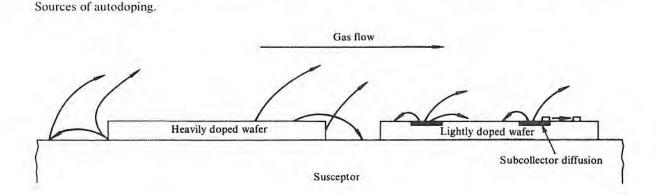

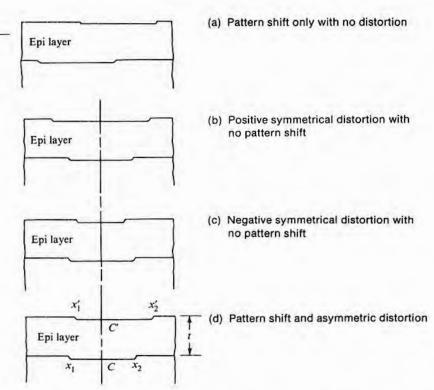

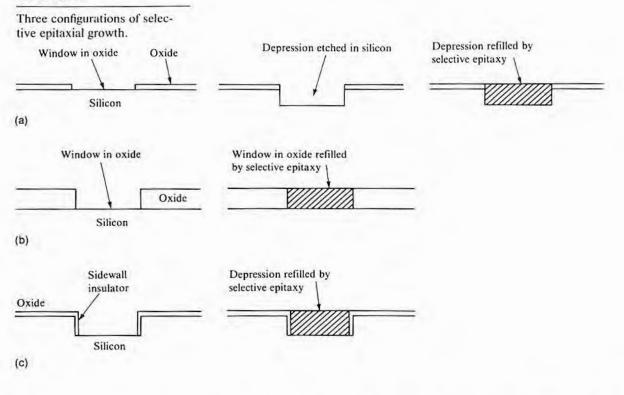

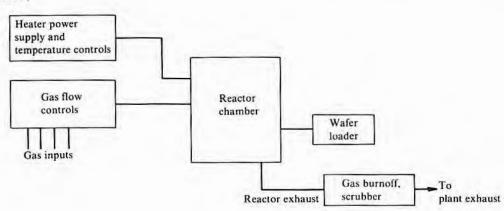

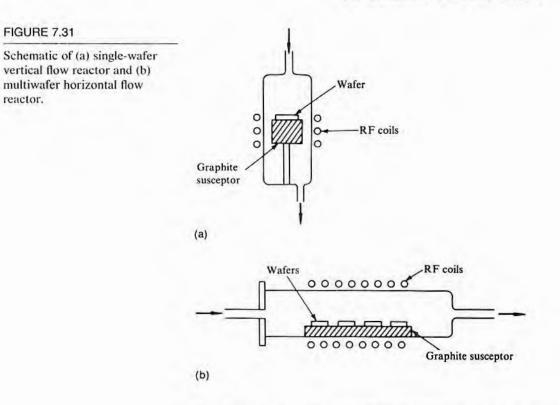

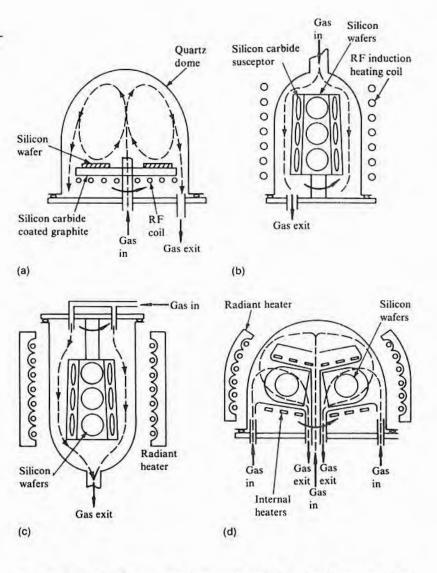

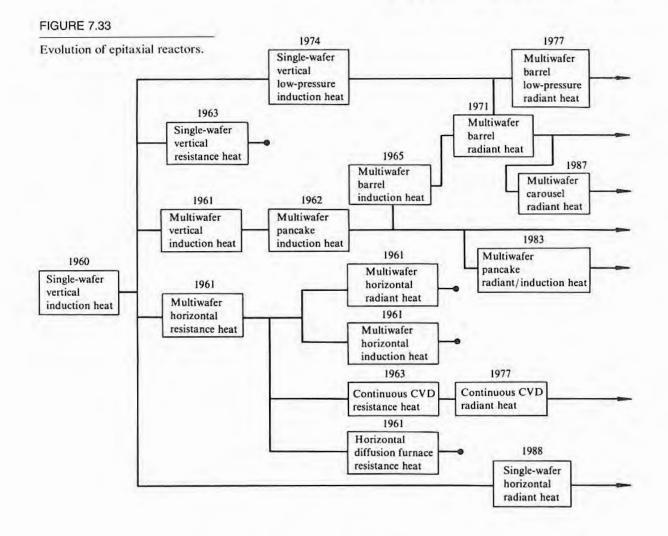

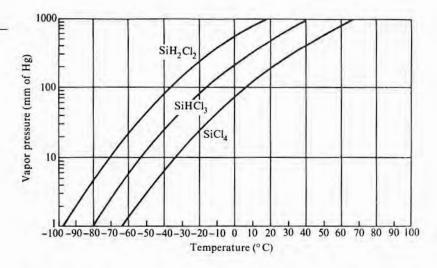

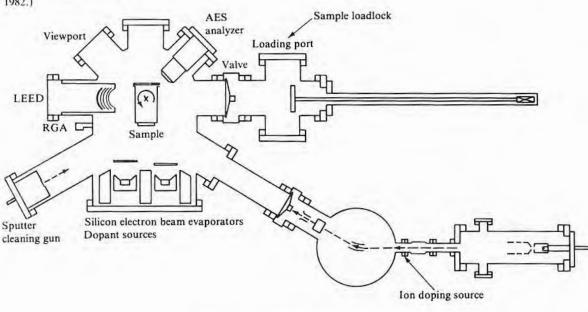

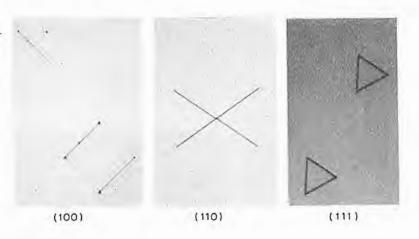

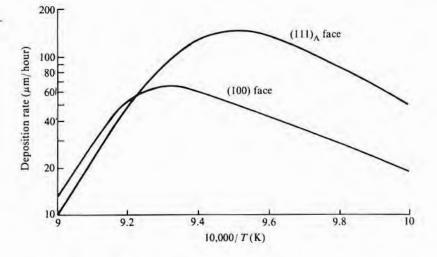

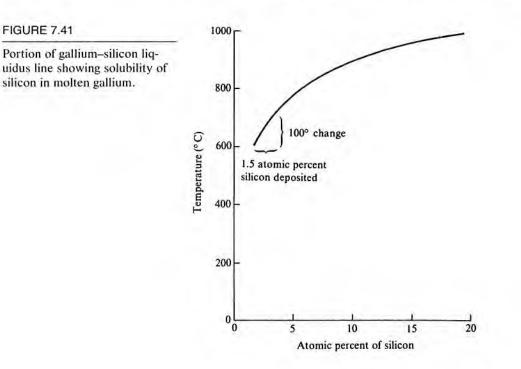

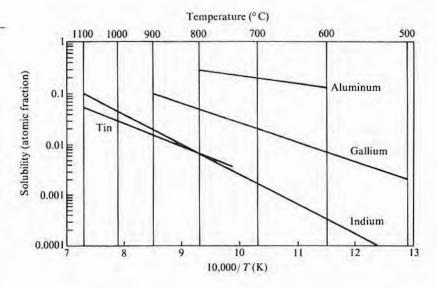

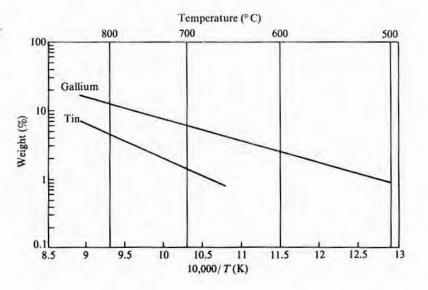

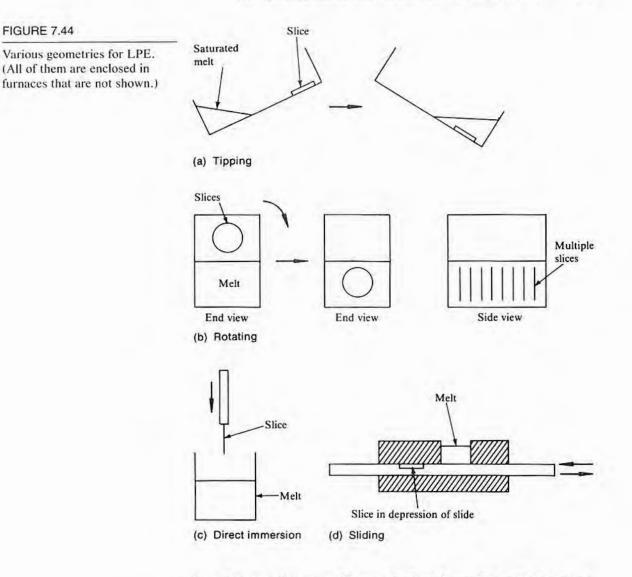

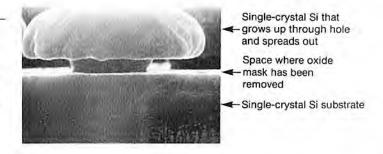

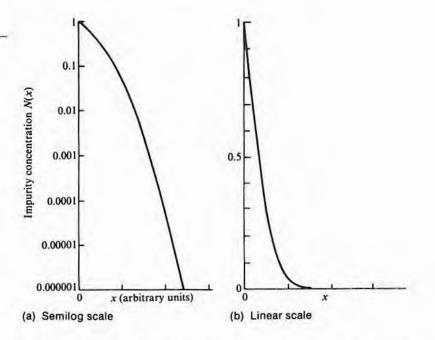

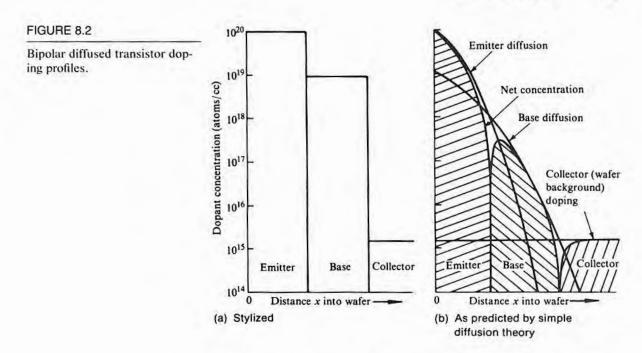

- D. Kahng and M.M. Atalla, "Silicon-Silicon Dioxide Field Induced Surface Devices," paper presented at IRE-AIEE Solid-State Device Conference, Pittsburg, 1960.