DOCKET NO.: 0107131-00351US2 Filed on behalf of Intel Corporation By: Grant K. Rowan, Reg. No. 41,278 Yung-Hoon Ha, Reg. No. 56,368 Wilmer Cutler Pickering Hale and Dorr LLP 1875 Pennsylvania Ave., NW Washington, DC 20006 Tel: (202) 663-6000 Email: Grant.Rowan@wilmerhale.com Yung-Hoon.Ha@wilmerhale.com

## UNITED STATES PATENT AND TRADEMARK OFFICE

## **BEFORE THE PATENT TRIAL AND APPEAL BOARD**

### INTEL CORPORATION Petitioner

v.

DSS Technology Management, Inc. Patent Owner

Case IPR2016-00290

## PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 5,965,924 CHALLENGING CLAIMS 7-12, 15 and 17 UNDER 35 U.S.C. § 312 AND 37 C.F.R. § 42.104

## **TABLE OF CONTENTS**

| I. Introduction                                    | 1  |

|----------------------------------------------------|----|

| II. Mandatory Notices                              | 5  |

| A. Real Party-in-Interest                          | 5  |

| B. Related Matters                                 | 5  |

| C. Counsel                                         | 5  |

| D. Service Information                             | 6  |

| III. Certification of Grounds for Standing         | 6  |

| IV. Overview of Challenge and Relief Requested     | 6  |

| A. Prior Art Patents                               | 6  |

| B. Grounds for Challenge                           | 7  |

| V. Brief Description of Technology                 | 7  |

| A. Overview of Transistor Fabrication              | 7  |

| 1. Basic Structure of Transistors                  | 7  |

| 2. Formation of Transistor Components              | 8  |

| 3. Local Interconnects                             | 10 |

| B. Overview of the '924 Patent                     | 11 |

| 1. Alleged Problem                                 | 12 |

| 2. Summary of Alleged Invention of the '924 Patent | 14 |

| 3. The Challenged Claims                           | 15 |

| 4. Prosecution History                             | 16 |

| VI. Overview of the Primary Prior Art References   | 19 |

| A. Overview of Sakamoto                            | 19 |

| B. Overview of Cederbaum                           | 21 |

| VII. Claim Construction                            | 23 |

| A. "diffusion region in a silicon substrate"       | 23 |

| VIII. Level of Ordinary Skill In The Art           | 27 |

| IX. Specific Grounds for Petition                  | 27 |

| A. Ground I: Claims 7-9, 15 and 17 are anticipated by Sakamoto27                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Independent Claim 7                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2. Claim 8: "A method according to claim 7, wherein said diffusion region is an N+ or a P+ region."                                                                                                                                                                                                                                                                                                                                   |

| 3. Claim 9: "A method according to claim 7, wherein said insulating material is selected from the group consisting of silicon oxide and silicon nitride."                                                                                                                                                                                                                                                                             |

| 4. Claim 15: "A method according to claim 7, wherein said gate is a polysilicon gate." / Claim 17: "The method according to claim 7, wherein said gate comprises polysilicon."                                                                                                                                                                                                                                                        |

| B. Ground II: Claims 10-12 are obvious in view of the combination of Sakamoto and Cederbaum                                                                                                                                                                                                                                                                                                                                           |

| 1. Claim 10: "a method according to claim 7, wherein said electrically conducting plug is a metal plug" / Claim 11: "a method according to claim 7, wherein said electrically conducting plug is preferably a refractory metal plug" / Claim 12: "a method according to claim 7, wherein said electrically conducting plug is formed of a material selected from the group consisting of titanium, tantalum, molybdenum and tungsten" |

| X. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                         |

Intel Corporation ("Intel") respectfully requests *Inter Partes* Review of claims 7-12, 15 and 17 of U.S. Patent No. 5,965,924 (the "924 patent") (Ex. 1101) pursuant to 35 U.S.C. §§ 311-19 and 37 C.F.R. § 42.1 *et seq*.

#### I. INTRODUCTION

The '924 patent claims a purportedly novel method for manufacturing transistors in semiconductors. But in fact, the claimed method merely duplicates a well-known technique disclosed by Osamu Sakamoto and others nearly three years before the alleged invention.

The '924 patent is directed to certain aspects of the structure and fabrication of transistors used in semiconductor and integrated circuit products such as microprocessors and memory. Transistors act as microscopic switches that turn on and off at extraordinarily high rates to enable aggregations of transistors (and other components) to process data. Transistors are made up of various structures including "contacts" that provide electrically conductive pathways into and out of certain structures within a transistor, and which thereby are used to connect transistors together. Declaration of Dr. John Bravman ("Decl.") ¶ 26 (Ex. 1102).

The '924 patent is concerned with electrically connecting different transistor parts to each other in a particular way. Transistors typically have three terminals through which electrical signals may pass: a "source," a "drain," and a "gate." The '924 patent is concerned with connecting the gate of one transistor to, for example, the source or drain of a neighboring transistor. Decl. ¶ 27 (Ex. 1102).

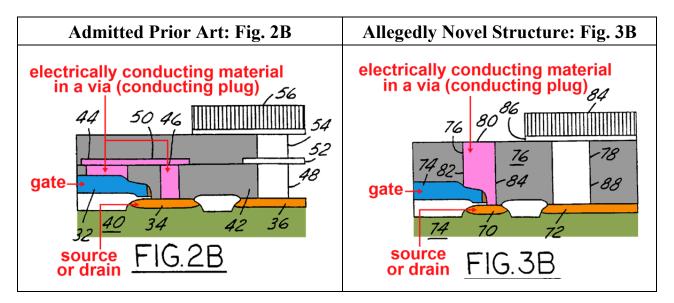

As the specification of the '924 patent admits, there were many well-known ways of making electrical connections between different transistor parts. As shown in Figure 2B (below), for instance, one of the admitted prior art ways of connecting the components of two transistors was by using two electrical connections called "plugs"—one connected to the gate of one transistor, and the other connected to the source or drain of the other—and then connecting those plugs together. As shown in Figure 3B (below), the purported invention of the '924 patent was to replace the two plugs with one plug. Decl. ¶ 28 (Ex. 1102).<sup>1</sup>

In both the admitted prior art (Figure 2B) and the allegedly novel structure of the '924 patent (Figure 3B), the gate is connected to a diffusion region (*i.e.*, a

<sup>&</sup>lt;sup>1</sup> All emphasis and annotations are added unless otherwise indicated.

## DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

#### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.