### US005475240A

### United States Patent [19]

### Sakamoto

**Patent Number:** [11]

5,475,240

**Date of Patent:** [45]

Dec. 12, 1995

| <b>AM</b> | 0204171<br>0186051<br>0006855<br>0040133 | 9/1985<br>1/1986<br>9/1986 | Japan 257/67   Japan 257/67   Japan Japan |

|-----------|------------------------------------------|----------------------------|-------------------------------------------|

| sha.      | 0132317<br>0015620<br>0073666<br>0271663 | 1/1990<br>3/1990           | Japan .<br>Japan .<br>Japan               |

| sna.      |                                          |                            |                                           |

#### OTHER PUBLICATIONS

"A Memory Cell with Polysilicon Thin Film Transistor (TFT) for a 4Mbit SRAM", Tsutsumi et al., Institute of Electronics and Communication Engineers of Japan Technical Report, vol. 90, No. 48, pp. 7-13.

"A New CMOS SRAM Cell with Fully Planarizing Technology", Narita et al., 1987 Symposium on VLSI Technol-

ogy Digest of Technical Papers, pp. 103–104. "Trench Self–Aligned EPROM Technology", Sekiya et al., 1986 Symposium on VLSI Technology Digest of Techical Papers, pp. 87-88.

"A High-Performance SRAM Memory Cell with LDD-TFT Loads", Tsutsumi et al., 1991 Symposium on VLSI Technology Digest of Technical Papers, pp. 23-24.

Primary Examiner-William Mintel Assistant Examiner—Peter Toby Brown Attorney, Agent, or Firm-Lowe, Price, LeBlanc & Becker

### **ABSTRACT**

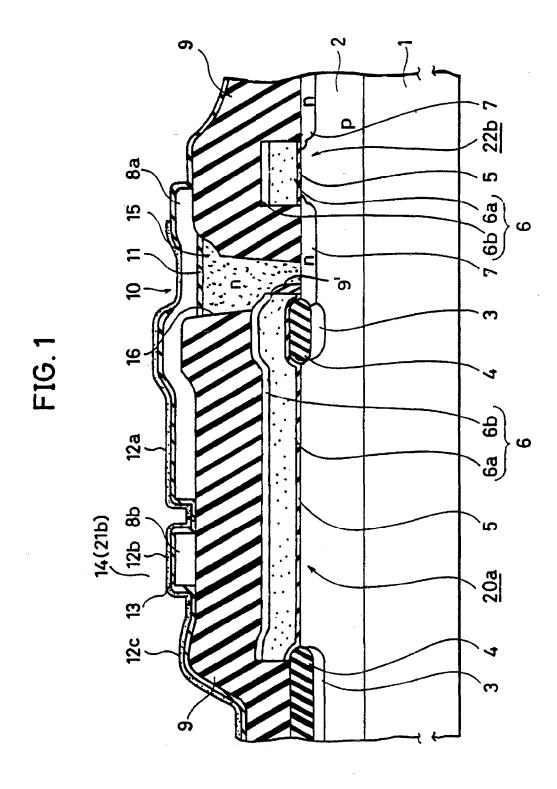

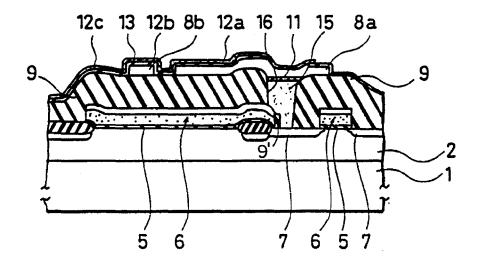

A silicon layer in a lower layer and an interconnection layer arranged in an upper layer are electrically connected through an opening for contact. A silicon plug layer having the same conductivity type as that of the silicon layer is embedded in the opening. The silicon plug layer is embedded in the opening by an etch back method after deposited using a CVD method. The interconnection layer in the upper layer has conductivity type different from that of the silicon plug layer. A refractory metal silicide layer is formed between the upper interconnection layer and the silicon plug layer.

The refractory metal silicide layer prevents pn junction from being formed between the upper interconnection layer and the silicon plug layer.

### 9 Claims, 23 Drawing Sheets

| 12c 1 | 14(21b)<br>3   12b 8b | 12a     | 16 10 11 | 15 8a              |  |

|-------|-----------------------|---------|----------|--------------------|--|

| 3 4   | 20a 5                 | 6a 6b 4 | 3 7 6b   | 6a, 5 <u>22b</u> 7 |  |

### [54] CONTACT STRUCTURE OF AN INTERCONNECTION LAYER FOR A SEMICONDUCTOR DEVICE AND A MULTILAYER INTERCONNECTION SRA [75] Inventor: Osamu Sakamoto, Hyogo, Japan [73] Assignee: Mitsubishi Denki Kabushiki Kaisha, Tokyo, Japan [21] Appl. No.: 293,771 [22] Filed: Aug. 19, 1994 Related U.S. Application Data [63] Continuation of Ser. No. 845,980, Mar. 4, 1992, abandoned. [30] Foreign Application Priority Data Mar. 15, 1991 [JP] Japan ...... 3-050954 Jan. 14, 1992 [JP] Japan ...... 4-005222 [51] Int. Cl.<sup>6</sup> ...... H01L 27/11; H01L 29/786; H01L 29/417; H01L 29/43 ......**257/67**; 257/69; 257/377; 257/384; 257/755; 257/756; 257/903 257/369, 377, 754-756, 903, 904, 752, 382-384, 385 [56] References Cited

### U.S. PATENT DOCUMENTS

| 4,785,341 | 11/1988 | Ning et al     | 257/755 |

|-----------|---------|----------------|---------|

| 4,786,954 | 11/1988 | Morie et al    | 257/303 |

| 4,829,018 | 5/1989  | Wahlstrom      | 437/51  |

| 4,884,121 | 11/1989 | Ishii          | 257/752 |

| 4,966,865 | 10/1990 | Welch et al    | 257/752 |

| 5,041,884 | 8/1991  | Kumamoto et al | 257/401 |

| 5,061,983 | 10/1991 | Egawa et al    | 257/756 |

| 5,198,683 | 3/1993  | Sivan          | 257/756 |

|           |         |                |         |

### FOREIGN PATENT DOCUMENTS

| 0163132 | 4/1985 | European Pat. Off |

|---------|--------|-------------------|

| 0281711 | 1/1987 | European Pat. Off |

| 0380327 | 1/1990 | European Pat. Off |

5,475,240

Dec. 12, 1995

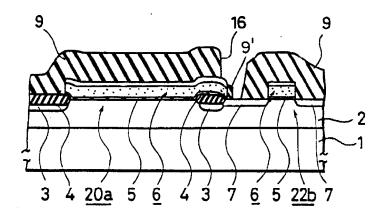

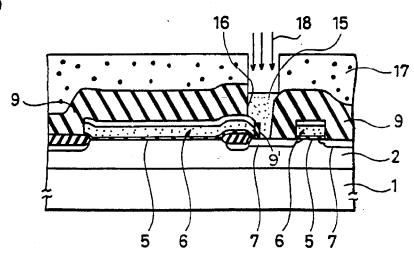

FIG. 2

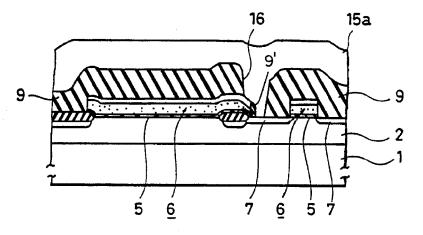

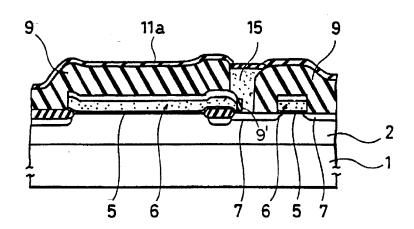

FIG. 3

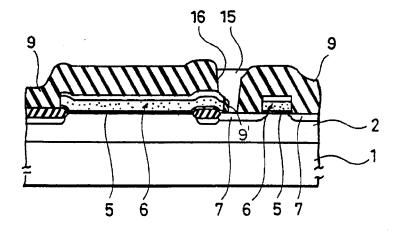

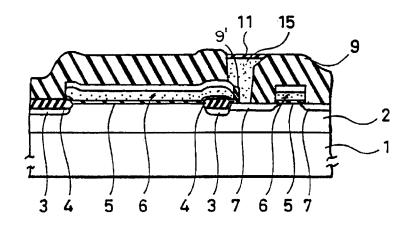

FİG. 4

5,475,240

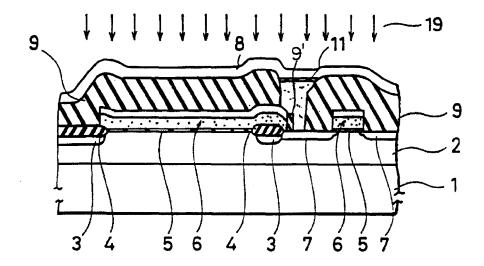

FIG. 5

FIG. 6

FIG. 7

5,475,240

FIG. 8

FIG. 9

# DOCKET A L A R M

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.