## United States Patent [19]

U.S. Cl. ...... 257/520; 257/903; 257/904;

References Cited

U.S. PATENT DOCUMENTS

4,960,726 10/1990 Lechaton et al. ...... 257/370 5,252,845 10/1993 Kim et al. ...... 257/304

257/377; 257/382; 257/384; 257/383; 257/515

257/734, 301, 304, 349, 360, 361, 370,

371, 394, 377, 382, 383, 384, 396, 397,

3/1985 Lund et al. ...... 257/520

6/1990 Harari ...... 257/904

510, 515, 520, 902

#### Kinoshita

[56]

4,503,451

4,933,739

#### [11] **Patent Number:**

5,453,640

[45] **Date of Patent:**  Sep. 26, 1995

| [54] | SEMICONDUCTOR INTEGRATED CIRCUIT<br>HAVING MOS MEMORY AND BIPOLAR<br>PERIPHERALS | 5,357,132 10/1994 Turner                                                                                                  |  |

|------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| [75] | Inventor: Yasushi Kinoshita, Tokyo, Japan                                        | 0172459 7/1988 Japan                                                                                                      |  |

| [73] | Assignce: NEC Corporation, Tokyo, Japan                                          | Primary Examiner—Mahshid D. Saadat Assistant Examiner—Alexander Oscar Williams                                            |  |

| [21] | Appl. No.: <b>359,996</b>                                                        | Attorney, Agent, or Firm—Sughrue, Mion, Zinn, Macpeak &                                                                   |  |

| [22] | Filed: <b>Dec. 20, 1994</b>                                                      | Seas                                                                                                                      |  |

| [30] | Foreign Application Priority Data                                                | [57] ABSTRACT                                                                                                             |  |

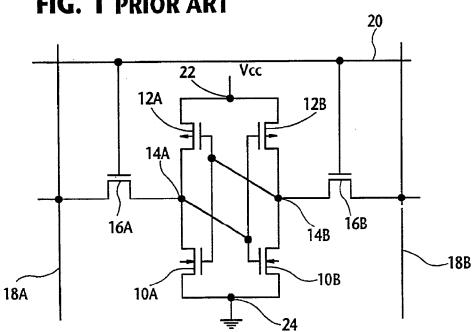

| Dec. | . 22, 1993 [JP] Japan 5-322996                                                   | In a semiconductor integrated circuit having a block of static<br>memory cells using CMOS transistors and peripheral com- |  |

| [51] | <b>Int. Cl.</b> <sup>6</sup> <b>H01L 29/06</b> ; H01L 27/11; H01L 27/04          | ponents using bipolar transistors, metal interconnections in<br>a layer over the CMOS transistors on the substrate are    |  |

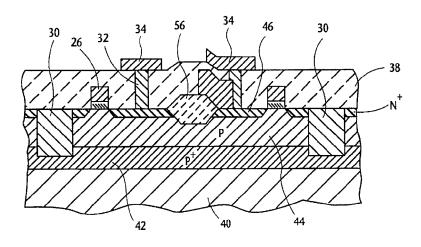

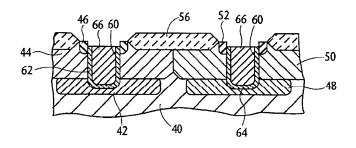

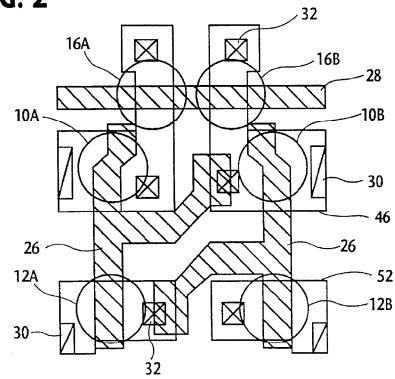

ic in simplified by using buried layers in the substrate as supply and ground lines for the CMOS transistors. This is accomplished by making buried contacts of a metal such as tungsten in each memory cell to make ohmic connection of the diffused layer of n-MOS transistors and the diffused layer of p-MOS transistors respectively to underlying buried layers of opposite conductivities and applying supply voltage or ground potential to each buried layer from the substrate surface by using additional buried contacts which are made at convenient locations outside the memory block. In the case of n-MOS memory cells using resistors or TFTs as load elements, ground potential is applied to the n-MOS transistors by the same method.

#### 8 Claims, 7 Drawing Sheets

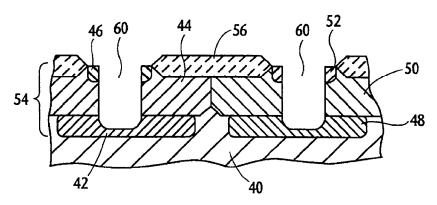

FIG. 1 PRIOR ART

Sep. 26, 1995

FIG. 2

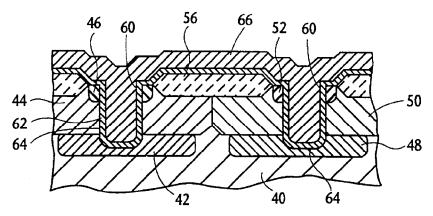

**FIG. 3**

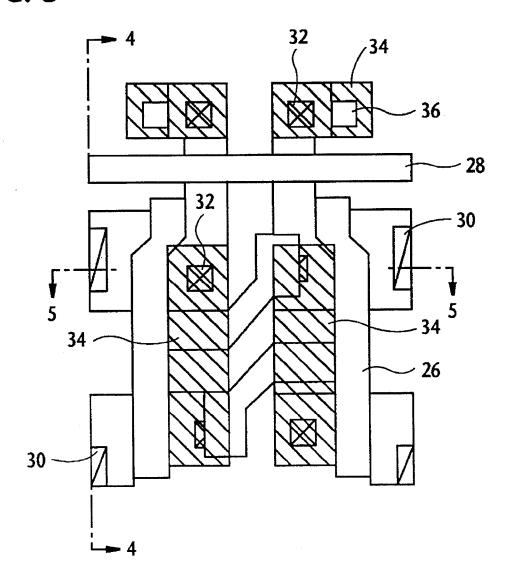

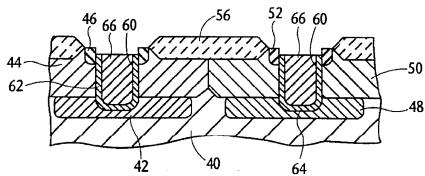

FIG. 4

Sep. 26, 1995

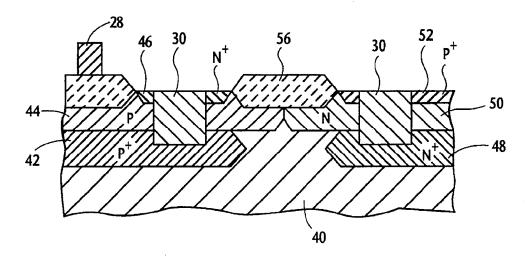

**FIG.** 5

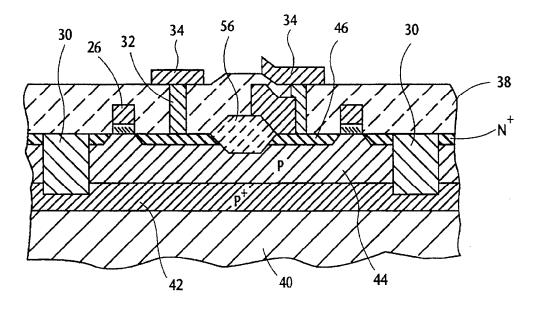

**FIG.** 6

**FIG.** 7

**FIG. 8**

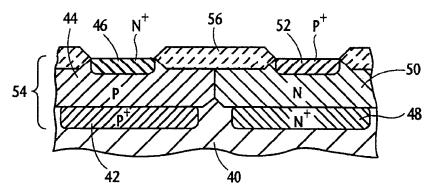

FIG. 9

# DOCKET A L A R M

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.