# United States Patent [19]

#### Raschke

[56]

- [54] METHOD OF JOINING SUBSTRATES FOR PLANAR ELECTRICAL INTERCONNECTIONS OF HYBRID CIRCUITS

- [75] Inventor: Curt R. Raschke, Dallas, Tex.

- [73] Assignce: Texas Instruments Incorporated, Dallas, Tex.

- [21] Appl. No.: 53,459

- [22] Filed: May 22, 1987

- [51]

Int. Cl.<sup>4</sup>

H05K 3/30

[52]

U.S. Cl.

29/832; 357/72;

- [58] Field of Search ...... 29/832, 833, 834, 836,

- 29/840; 357/72, 80; 437/209

#### **References Cited**

#### **U.S. PATENT DOCUMENTS**

| 3,466,741 | 9/1969 | Wiesner 357/72 X            |

|-----------|--------|-----------------------------|

| 3,501,832 | 3/1970 | Saburoiwats et al 437/209 X |

| 3,903,590 | 9/1975 | Yokogawa 357/72 X           |

| 4,466,181 | 8/1984 | Takishima 357/80 X          |

# FOREIGN PATENT DOCUMENTS

| 23565 | 3/1978 | Japan |  |

|-------|--------|-------|--|

| 47901 | 1/1979 | Japan |  |

# [11] Patent Number: 4,815,208

[45] Date of Patent: Mar. 28, 1989

| 47902 | 2/1979 | Japan 437/209 |

|-------|--------|---------------|

| 7677  | 1/1980 | Japan 357/80  |

| 32425 | 2/1983 | Japan 437/209 |

| 4351  | 1/1987 | Japan 437/209 |

Primary Examiner-Carl J. Arbes

Attorney, Agent, or Firm--Rene E. Grossman; James T. Comfort; Melvin Sharp

### [57] ABSTRACT

The disclosure relates to a method of forming a hybrid circuit wherein two substrates, preferably though not necessarily, of diverse materials, are aligned on and secured to a glass plate by layers of polymer which are selectively etchable as to each other. The portion of the topmost polymer layer which is between the substrates is removed and the space therebetween is filled with an electrically insulating material which adheres to the substrates to form a surface between the substrates which is coplanar with the circuit containing surfaces of the substrates. Interconnects are then formed on the electrically insulating surface which extend onto both of the substrates. The remaining polymer layers are removed and the hybrid circuit which has been formed is then placed on a support to provide rigidity and, if necessary, heat sinking properties.

#### 16 Claims, 1 Drawing Sheet

Mar. 28, 1989

**OCKEI LARM** Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

Α

#### METHOD OF JOINING SUBSTRATES FOR PLANAR ELECTRICAL INTERCONNECTIONS OF HYBRID CIRCUITS

## BACKGROUND OF THE INVENTION

1. Field of the Invention

This application relates to a method of interconnecting the pads of the diverse substrates or chips to form a hybrid circuit.

2. Brief Description of the Prior Art

A problem which has limited full exploitation of the advantages of hybrid circuits has been that of reliably making electrical interconnection between the chips on a scale consistent with the scale of circuit integration on <sup>15</sup> the chips themselves. A variety of methods exist for making planar interconnections on an appropriate scale. To use these methods, however, requires an adhesive bond between the chips which is uniform and flat to the scale of the interconnection geometry, level with the <sup>20</sup> chip surfaces and rigid and adherent over the planned temperature use range.

The ideal circuit will often be a hybrid with, for example, one part formed from gallium arsenide and the second part formed from lithium niobate, where a cir- 25 cuit design cannot be optimized on a single substrate. When such hybrid circuits are used, it is necessary to lithographically interconnect the two different types of substrates. The interconnection presents problems of a type not encountered in the formation of interconnects 30 on a single substrate. The two substrates must be sufficiently close together and sufficiently coplanar whereby standard lithographic techniques can be applied. The two substrates must be coplanar on the order of the line width of the interconnections. Therefore, if 35 the interconnection line widths are, for example, seven microns, the substrates must be coplanar on the order of at least seven microns for the entire length of joint therebetween.

The prior art attempted to solve this problem by 40 glueing the two substrates together in advance and then polishing down both substrates together including the adhesive therebetween whereby, by this polishing action, both substrate surfaces and the intervening adhesive are coplanar. The substrates are then operated upon 45 individually in standard manner to form the circuits therein. This system is economically ineffective, especially when substrates such as gallium arsenide are involved. This is because gallium arsenide processing is so complex and the yield thereof is so low that, statisti- 50 cally, the likelihood of obtaining a hybrid circuit wherein both the gallium arsenide circuit and the second circuit are simultaneously functioning is very small. Accordingly, it is desirable to seek a method for formation of hybrid circuits wherein the statistical likelihood 55 of obtaining such circuits in a completely functional manner is substantially increased.

#### SUMMARY OF THE INVENTION

In accordance with the present invention, there is 60 provided a method of making such hybrid circuits wherein the statistical likelihood of success is materially improved.

Briefly, in accordance with the present invention, the desired circuits are initially formed on the surfaces of 65 the substrates of both materials of the hybrid circuit. The individual circuits are then tested for operability individually with the inoperative circuits being dis-

DOCKE

carded. It is then necessary to interconnect the diverse substrates by running leads from the pads of one substrate to the pads of the other. This has caused a problem in that it is necessary that the circuit containing

<sup>5</sup> surfaces of the two diverse substrates being connected as well as the adhesive which holds the substrates together in close proximity to each other be absolutely planar on the order of the width of the photolithographic interconnect lines formed over the adhesive to interconnect the pads of the substrates. This has presented a major problem which is now solved by the present invention.

Accordingly, a glass slide is provided with markings thereon for accurate placement of the substrates. A first transparent polymer layer with a thickness of 1 to 10 microns and preferably 5 microns which adheres well to glass is then formed over the glass slide. Preferred polymers for this first layer are polymethylmethacrylate, polymethylsiloxane and polyimides of sufficiently low viscosity that they can be deposited uniformly to the desired thickness. A second transparent polymer layer with a thickness of 1 to 10 microns and preferably 5 microns which adheres to the first polymer layer and is moderately cross-linked is then formed over the first polymer. The polymers which have the desired properties for the first layer will generally be used for the second layer. In this case the first and second layer are deposited as one layer.

A third polymer layer, which is preferably a photoresist or an uncured polyimide, such as PL-1000 of Hitachi, with a thickness of less than 2 microns and preferably 1 micron is then formed over the second polymer layer which adheres to the second polymer layer and is etchable with an etchant which does not etch the first or second polymer layer. The third polymer layer is either sufficiently thin or sufficiently transparent so that the markings on the glass slide are, visible therethrough. The substrates or chips with circuits formed on a surface thereof are then placed on the third layer with the circuit containing surface contacting the third layer and aligned with the markings on the glass slide.

The third polymer layer is then removed in the region between the substrates down to the second polymer layer with an etchant selective to the third layer as opposed to the second and first layer. The etchants can be solvents such as butyl acetate or methyl alcohol or can be oxygen gas in an excited state such as formed in an RF plasma. A fourth polymer in the form of an epoxy, such as a well known casting compound such as Emerson Cumins Stycast 2651-40 which forms a smooth surface or cyanoacrylate or methylacrylic ester, is then introduced into the region between the substrates and cured. The entire assembly is then soaked in a solution which does not attack the fourth layer but removes or makes removable the first and second layers, such as N-butyl acetone, acetone, N-methyl pyrillidone, so that the two substrates joined together by the fourth layer remain. The circuit containing surfaces of the substrates and the intervening adhesive will be essentially coplanar since the glass acts as a planarizing surface therefore during fabrication.

The hybrid circuit thus formed is then placed on a metal support, such as brass, which also provides heat sinking properties thereto. The interconnect lines are then formed between the two substrates over the fourth layer, in standard manner using standard lithographic

Find authenticated court documents without watermarks at docketalarm.com.

10

techniques. The device is then packaged in standard manner.

#### BRIEF DESCRIPTION OF THE DRAWINGS

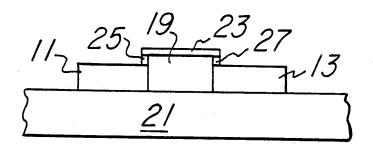

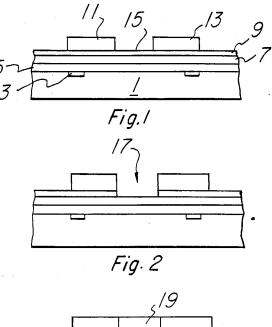

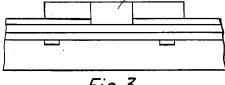

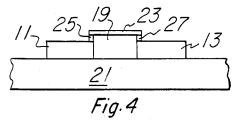

FIGS. 1 to 4 are schematic drawings which depict 5 the result obtained after different manufacturing steps in the process have been performed for formation of the hybrid circuit in accordance with the present invention; and

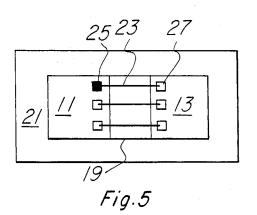

FIG. 5 is a top view of FIG. 4.

#### DESCRIPTION OF THE PREFERRED EMBODIMENT

Referring now to the FIGURES and specifically to FIG. 1, there is shown a transparent glass plate 1 having 15 markings 3 thereon for later alignment of chips or substrates. The glass plate defines the planar surface which the remainder of the process will be referenced against. A first transparent polymer layer 5 of polymethylsiloxane having a thickness of 5 microns is then deposited 20 over the plate 1 and a second transparent polymer layer 7 of polymethylmethacrylate having a thickness of 5 microns is deposited over the layer 5. A third thin layer 9 of a photoresist AZ1350B of American Hoechst having a thickness of one micron, which acts as a tempo- 25 rary glue for the chips to be placed on the plate 1, is then deposited over the layer 7 and the substrates 11 and 13 are aligned on the layer 9 in locations determined by the alignment markings 3 on the glass plate 1 which are visible through each of the layers 5, 7 and 9. At this time 30 in the procedure, the system will appear as shown in FIG. 1.

The entire device of FIG. 1 is then masked to permit etching of the portion of the layer 9 which exists in the region 15 between the substrates 11 and 13. The region 35 formed of different materials. 15 is then etched away using butyl acetate followed by an oxygen plasma to remove any residues to provide the arrangement as shown in FIG. 2. The space 17 which now exists between the substrates 11 and 13 is then filled with an epoxy 19, such as the casting compound Emer- 40 son and Cuming Stycast 2651-40 which forms a smooth surface and degassed to provide the arrangement as shown in FIG. 3 with the epoxy layer 19. The epoxy layer 19 secures the substrates 11 and 13 thereto and forms the surface over which the interconnects will 45 later be formed to form the structure as shown in FIGS. 4 and 5.

The structure as shown in FIG. 3 is then treated with acetone to dissolve the layers 5 and 7 and the remnant of layer 9 to provide the substrates 11 and 13 with circuits 50 formed in the downward facing faces thereof, the substrates being secured together by the epoxy 19 which provides a surface coplanar with the circuit containing surfaces of the substrates. This arrangement is glued with an epoxy to a brass support surface 21 which also 55 acts as a heat sink for the hybrid circuit being formed as shown in FIG. 4. It can be seen that the circuit carrying surface of each of the substrates 11 and 13 is facing away from the support 21. This structure is then patterned with a photoresist in standard manner and inter- 60 connect lines 23 are formed in standard manner which extend from pads 25 on substrate 11 to pads 27 on substrate 13 as shown in FIGS. 4 and 5 to form the completed hybrid circuit. The hybrid circuit can then be packaged in standard manner to provide the completed 65 adherable to said support. usable circuit.

It can be seen that there has been provided a method for making a hybrid circuit which utilizes few and rela-

DOCKE

tively simple processing steps and which utilizes all operable chips.

Though the invention has bee described with respect to active semiconductor substrates it should be understood that other types of substrates, both active and passive, can be substituted for one or both of the substrates herein.

Though the invention has been described with respect to a specific preferred embodiment thereof, many variations and modifications will immediately become apparent to those skilled in the art. It is therefore the intention that the appended claims be interpreted as broadly as possible in view of the prior art to include all such variations and modifications.

I claim:

1. A method of forming an electrical circuit comprising the steps of:

- (a) providing a planar support;

- (b) forming a layer of an adhesive on said support;

- (c) providing first and second substrates, each having

- a circuit formed on a surface thereof; (d) securing the circuit containing surface of each of said substrates to said adhesive layer;

- (e) removing the portion of said adhesive layer between said substrates;

- (f) filling the region between said substrates with a substrate adhering material to form an insulating surface between said circuit containing surfaces coplanar with said surfaces; and

- (g) forming interconnect lines on said insulating surface extending from said first to said second substrate.

2. The method of claim 1 wherein said substrates are

3. The method of claim 1 further including providing alignment marks on said support and, in step (d) further aligning said substrates with said alignment marks.

4. The method of claim 2 further including providing alignment marks on said support and, in step (d) further aligning said substrates with said alignment marks.

5. The method of claim 1 wherein step (b) includes, prior to formation of said adhesive layer, forming a transparent layer of a material adherable to said support and resistant to etching by an etchant for said adhesive laver.

6. The method of claim 2 wherein step (b) includes, prior to formation of said adhesive layer, forming a transparent layer of a material adherable to said support and resistant to etching by an etchant for said adhesive layer.

7. The method of claim 3 wherein step (b) includes, prior to formation of said adhesive layer, forming a transparent layer of a material adherable to said support and resistant to etching by an etchant for said adhesive layer.

8. The method of claim 4 wherein step (b) includes, prior to formation of said adhesive layer, forming a transparent layer of a material adherable to said support and resistant to etching by an etchant for said adhesive laver.

9. The method of claim 5 further including, before step (g), removing said transparent layer of a material

10. The method of claim 6 further including, before step (g), removing said transparent layer of a material adherable to said support.

5

10

15

20

25

30

35

40

45

50

55

60

65

5

11. The method of claim 7 further including, before step (g), removing said transparent layer of a material adherable to said support.

12. The method of claim 8 further including, before step (g), removing said transparent layer of a material adherable to said support. 13. The method of claim 9 further including then securing the substrates to a support.

14. The method of claim 10 further including then securing the substrates to a support.

15. The method of claim 11 further including then securing the substrates to a support.

16. The method of claim 12 further including then securing the substrates to a support.

\* \* \*

Find authenticated court documents without watermarks at <u>docketalarm.com</u>.