and Overhead Unit. To eliminate the possibility of a similar latent software error in the System Monitor and the Control Law Processor, a dissimilar set of algorithms are implemented in System Monitor software.

As a second function, the System Monitor assesses the approach progress and annunciates a caution to the crew if the approach exceeds limits which could cause a landing outside the desired touchdown footprint.

#### 3. System/Crew Interface and Crew Procedures

The ability of the pilot not flying (PNF) to monitor the progress of the approach through the initiation of flare while remaining head down was a primary consideration during system design. The following information provided to the PF on the HUD is also provided on the PNF instrument panel to ensure awareness of system status and approach progress.

- 1. An annunciator indicating system readiness to execute a CAT III approach (AIII status).

- An Approach Warn indicator which annunciates a system malfunction or an approach flown outside required limits.

- 3. An expanded localizer display at the bottom of the ADI with indicated limits equal to localizer limits on the HUD.

- 4. The vertical guidance command which the PF is following on the HUD is repeated head down for the PNF to enable him to evaluate pilot tracking performance below the altitude where glideslope information becomes unusable.

Two other duties of the PNF are 1) assisting in performing the approach checklist and 2) executing a go-around in case of a HUD system failure. Prior to approach initiation, the approach course, airspeed, field elevation and glideslope angle are entered through the Captain's panel instruments and HUD Control Panel. By initiating a system test, these values are displayed on the HUD, and then read in the PF and cross-checked to the approach plate by the PNF. Below 500' the PNF rides passively on the controls; one hand on the wheel and the second behind the throttles. A "go-around your controls" call by the PNF gives control of the aircraft to the PNF. He will take control without direction only on loss of response by the PF in a response exchange initiated prior to decision height.

#### 4. Aircraft Installation Drawing Package

To ensure consistency and repeatability of system installation a detailed drawing package was developed prior to intial aircraft installation and revised during installation on the two flight test aircraft. Achieving system separation on the aircraft in order to prevent loss of critical information to both the Captain and First Officer in the event of a wire bundle overheat or serious avionics malfunction required rework of existing aircraft wiring in the form of physical wire separation or sleeving where separation was not possible. A document describing the wire separation objectives and methods was prepared and approved by the FAA prior to system installation in the No. 2 aircraft. The drawing package also contains detailed installation instructions, an operational test procedure to ensure a proper interconnect to all avionics systems and a compatibility test to ensure non-interference with other aircraft systems.

#### 5. Safety and Failure Analyses

The ability of the system to meet the safety requirements for operation in CAT III conditions was established and verified by conducting three separate analyses each resulting in extensive supporting documentation.

The System Safety Analysis considered the ability of the system to ensure that the probability of undetected hazardous events were on the order of one part in  $10^{-8}$ . The following hazardous events were included in the analysis: long landing, short landing, landing laterally off the runway, hard landing, wing tip strike. and nose wheel strike. The conditions which could lead to these events were then examined. Once the causes of each hazardous event were identified, fault trees were constructed in accordance with guidelines set forth in "Fault Tree handbook"<sup>(6)</sup>. The known failure rates of sensors and the predicted failure rates of the HUD system were used along with predicted exposure times to determine, in accordance with the fault trees, the probability of occurrence of the hazardous events.

The System Failure Mode and Effect Analysis supported the Safety Analysis by establishing the failure rates and modes at the avionic unit level. The Detailed FMEA considered HUD System faults at the component level to support the system level analysis and to verify predicted built-in-test and monitoring effectiveness. In addition a failure test plan was prepared and tests were conducted to verify the detailed analysis.

#### 6. Simulation and Flight Test Plans

A three axis motion simulator with visual scene was employed to develop the pilot system interface, evaluate pilot control response and to determine the ability of the system with the pilot-in-the-loop to meet touchdown footprint requirements in the specified environment. Prior to evaluating the system on the motion simulator the HUD Guidance System, airborne sensors, target aircraft aerodynamics, ground based ILS and environmental conditions were modeled and installed on a SEL 32/27 computer system. A pilot model<sup>(3)</sup> was also developed to permit complete modeling of the ILS capture, approach, flare and touchdown. All the sensor models and the ILS model included bias, gain variation and noise contamination. The environmental conditions modeled included steady winds, wind shears, turbulence, runway slope, runway length, glideslope angle, pressure, and temperature variations. Probability distributions for the identified disturbances were developed and used to generate random environments for the model. Aircraft weight, center of gravity and approach speed, as well as the pilot model were adjusted in Monte Carlo fashion for statistical evaluation of the system design.

These sensor errors, environmental conditions, aircraft configurations and their probability distributions were then applied to the manned simulator to establish performance correlation between the pilot model and a large number of subject pilots. A manned simulation test program was established to demonstrate system performance in the CAT III environment. The pilot group consisted of airline pilots and FAA pilots. Pilot variability proved to be a large contributor to touchdown dispersions. The FAA demonstration program in the manned simulator required over 1000 flights to touchdown.

A flight test plan was then prepared to validate the fidelity of the simulation by demonstrating that the touchdown statistics from the simulation and the flight test were from the same population. The flight test plan required verifying performance in a subset of the environmental conditions used in the simulator demonstrations.

#### 7. Selection of Flight Test Crew

To conduct the extensive flight testing of this experimental system in a large turbojet aircraft with the special requirement that some of the testing be done in actual CAT III weather, we developed special criteria for the selection of the crew and especially the chief pilot. The following requirements were applied in this selection.

- 1. Previous experience in CAT III operations

- 2. Previous experience in CAT III weather

- 3. Previous R and D flight testing

- Ability to contribute to the development of operations procedures

- 5. Ability to act as a right seat safety pilot

We were fortunate to find an individual who could fill these roles well. We also received assistance from the FAA test pilots in a number of areas which helped make these tests successful.

#### 8. <u>Development and Installation of the Flight Data</u> Acquisition and Touchdown Verification Equipment

The performance of the system in flight and at touchdown was gathered by a data acquisition system which received all the sensor data used by the HUD System, and stored this information on a high speed magnetic tape. An extensive data reduction system was then developed for the SEL 32/27 which provided time histories of sensor data, parameter/parameter plots and histograms across the flight test program. The system proved invaluable in determining aircraft and system performance, developing the final control laws, and in establishing the simulator flight test correlation.

A belly mounted video camera was employed to verify aircraft touchdown position. With a wide angle lens and proper calibration, touchdown position could be established longitudinally within 20 feet and laterally within 2 feet.

HUD symbology was continuously recorded on a second video system and overlayed with video from a forward looking camera mounted just behind the windshield. This video system permitted the flight test engineers to view the approach as if they were sitting behind the HUD.

#### 9. Aircraft Operation

Due to the length of time involved from the beginning of CAT II flight tests to the completion of CAT III flights and the rising demand for 727 aircraft, two HUD system and data acquisition installations were required on two separate aircraft. Uninterrupted operation of the aircraft proved difficult as we were low in the priorities of the maintenance organizations willing to assist a one-ofa-kind aircraft traveling the Northwest in search of the winds and weather needed to satisfy the flight test plan requirements. Because all aircraft landing and take-off operations align for the best wind advantage, and our mission was to explore adverse winds, we were unable to take advantage of numerous opportunities at Type II airports since this would mean working against the traffic flow. Air Traffic Control did accommodate our operations whenever possible permitting the completion of the flight tests.

#### 10. Simulation and Flight Test Data Confirmed Proof of Concept Test Results:

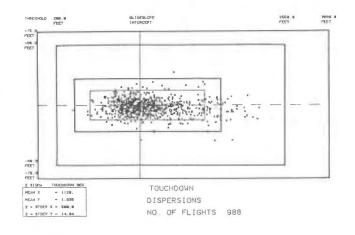

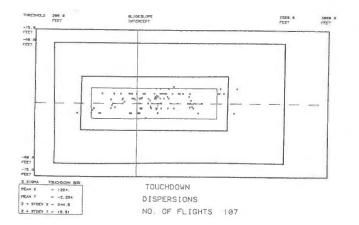

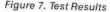

The simulation and flight test programs confirmed that a man-in-the-loop control system, subjected to the environmental requirements for CAT III operations can meet, and in this case, exceed the requirements for autoland systems. Data plots for the simulator and flight test results are presented in Figures 6 and 7. Most of the simulation and flight test landings were made with the pilots vision of the outside world obscured.

#### FIGURE 6 SIMULATION DISPERSIONS

Classical statistical hypothosis testing techniques were used to verify that the system performance dispersions met criteria set forth in AC 20-57A and AC 120-28C. Distribution fitting and extrapolation techniques combined with probability models of system monitor effectiveness were used for verification of low probability event statistics. Simulation statistics were shown to be reliable by showing statistical equality of flight test results and simulator results.

#### FIGURE 7 FLIGHT TEST DISPERSIONS

#### Conclusions

The ability of the HUD System to meet the requirements of CAT III operations has been examined: 1) in Proof-of-Concept testing where the effectiveness of single HUD pilot in-the-loop operations was demonstrated; 2) in simulation where performance and limit requirements were tested; 3) in the flight test aircraft where actual operations and correlation with simulation were demonstrated; and 4) in the engineering laboratory, simulation and aircraft where system failure modes have been analyzed, tested, and demonstrated. The issuance of the STC waits final review of reports and data and a test flight in actual weather conditions. This flight is scheduled for November of this year, 1984, when low visibility conditions occur on the U.S. West Coast.

The success of this program is credited to the assiduous design, development and test effort put forth by the staff at FDI, the assistance of our knowledgeable consultants and able flight crew, and the cooperation and support of the dedicated people of the FAA.

- "Criteria For Approval Of Category III Landing Weather Minima", FAA Advisory Circular Number: 120-28C

- (2) "Automatic Landing Systems (ALS)", FAA Advisory Circular Number: 20-57A

- (3) D.T. McRuer and E. S. Krendel, "Mathematical Models of Human Pilot Behavior", AGARD-AG-188: Jan., 1984

- (4) McRuer, Jex, Clement, Graham, "A Systems Analysis Theory for Displays in Manual Control", STI Tech Rpt No. 163: June 1968

- (5) McRuer, Ashkenas, Graham, "Aircraft Dynamics and Automatic Control", Princeton University Press: 1973

- (6) Roberts, Vesely, Haasl, Goldberg, "Fault Tree Handbook", NUREG-0492: Jan., 1981

## **SESSION 15**

## COMMUNICATION, NAVIGATION, AND IDENTIFICATION (CNI) TERMINALS

Chairmen:

Dr. Duncan B.Cox, Jr. Charles Stark Draper Lab, Inc.

Frank W. Smead ITT Avionics

This session is primarily concerned with technical descriptions of actual or planned on-aircraft CNI terminals and with the issues and benefits associated with integrating several CNI functions together in one terminal.

#### 15

BOEING Ex. 1031, p. 513

-

Pages 447-453 have been deleted intentionally.

#### Samuel Anderson

#### Technical Staff The MITRE Corporation 1820 Dolley Madison Boulevard McLean, Virginia 22102

#### Abstract

There is a need to improve communication and surveillance capabilities in oceanic airspace. In October 1982, The MITRE Corporation initiated a 3-year, internally-funded project to design, develop, and demonstrate an experimental aeronautical satellite data link system to provide data communications capability between the ground and aircraft flying in oceanic airspace.

This paper describes the approach used by MITRE in developing the system and presents technical details to support specific design decisions. The experimental aircraft data terminal is designed to provide low-capacity data transfer between the aircraft and an earth station via satellite. The low aircraft terminal data rate of 200 bits per second (bps) minimizes power requirements and thereby the costs. The link between the aircraft and satellite is at L-band (1.5/1.6 GHz), and the links between satellite and earth stations are at C-band (4/6 GHz).

The subsystems comprising the aircraft data terminal include the transceiver, modem, processor, frequency control, and power. Digital logic functions are designed using STD Bus technology. The antenna design takes into account performance and cost tradeoffs between antenna gain and signal power.

The system concept avoids the high cost of launching, operating, and maintaining dedicated satellites through sharing of existing commercially available satellite links (e.g., INMARSAT) with other mobile users (e.g., maritime). The diversity among aeronautical users relative to their operational requirements and financial resources is accommodated by adopting a modular design architecture for user equipment that allows for expansion of capabilities at user discretion.

#### Background

The use of satellite channels has been considered since the early 1960s as an effective means of providing communications to a large group of aeronautical users. For some applications, such as communicating to and from aircraft flying remote routes, out of the range of ground-based VHF stations, satellite communication represents an ideal solution. Three satellites, correctly positioned, could conceivably provide coverage for all of the world's major air routes. The aeronautical satellite system concepts that have been studied to date, despite their theoretical and practical advantages, have been regarded as too expensive to be supported by aviation users, and none have been implemented. The cost of a satellite system dedicated to aeronautical users would involve the design and launch of satellites, earth station construction, maintenance, and technical support.

The economic consensus regarding the high cost of dedicated satellite systems is clear, yet there remains a problem of inadequate aeronautical communications over oceanic routes. Although the sophistication of on-board aircraft navigation systems is increasing, there is as yet no reliable means of conveying the data produced by these systems to the ground (dependent surveillance) when the aircraft is beyond the range of radar and VHF radio links.

The MITRE Corporation has committed large resources to the demonstration of a low-cost aeronautical satellite data link, which will use a space segment of an already existing satellite system. The purpose is to show that aeronautical satellite communications need not be overwhelmingly expensive while being of great value to the aviation community.

The concept is based on analyses and conclusions contained in an FAA report titled: "Oceanic Area System Improvement Study (OASIS)."[1] An OASIS working group estimated that reduced minimum airspace requirements in the North Atlantic, made possible by an automatic dependent surveillance capability derived from the shared use of the International Maritime Satellite (INMARSAT) system, could generate an overall cost savings of from 90 to 164 million dollars in the time period between 1979 through 2005, depending on the specific implementation.[2] An attractive feature of an INMARSAT-based aeronautical data link system is that aviation usage of the service could expand in increments. Beginning with limited satellite capacity initially, enough to serve selected applications, the user investment need increase only as existing demand and requirements increase.

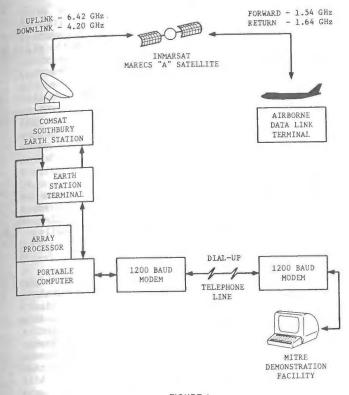

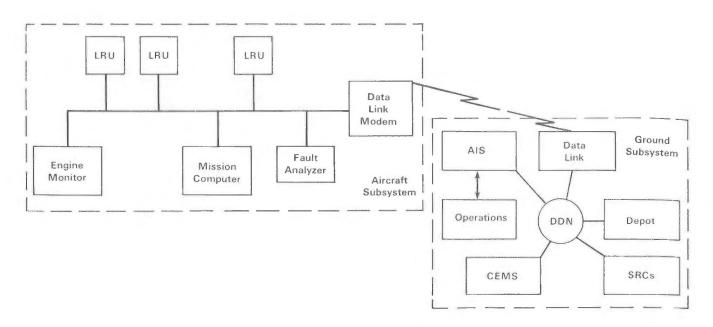

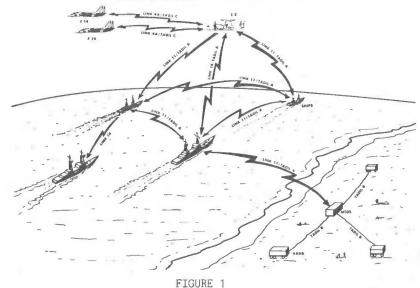

The MITRE experimental data link will consist of one aircraft terminal and one earth-station terminal, which will operate over a shared-space segment of the present INMARSAT system. The aircraft terminal has been designed to provide a two-way communications link between the aircraft and the satellite at the existing maritime L-band mobile satellite frequencies (1.5/1.6 GHz).\* (See Figure 1.) Both hardware and software have been developed to provide for multiple access, modulation and coding, and antenna switching.

#### Design Considerations

#### Cost Factors

It is not likely that an aeronautical satellite

Copyright © American Institute of Aeronautics and Astronautics, Inc., 1984. All rights reserved.

<sup>\*</sup>When the aeronautical mobile satellite frequencies are made available in the subsequent generations of the INMARSAT system, the aircraft terminal frequencies would also change correspondingly. The power budget given in Table 2 is based on the second generation INMARSAT spacecraft.

#### FIGURE 1 MITRE EXPERIMENTAL AERONAUTICAL SATELLITE DATA LINK

data link design will be accepted unless it can be shown to be cost effective. This fact, when considered in a design perspective, places inevitable constraints on system performance. The cost of an implemented service would depend primarily on two parameters, described below, both of which have a first-order effect on the overall cost.

1. Earth Station Power. The subscription rates charged to users of a satellite system such as INMARSAT are based on the effective isotropic radiated power (EIRP) required from the satellite. For a given user channel, the satellite EIRP depends on the earth station transmitter power levels allocated to the specified channel and the gain provided by the satellite transponder. The aeronautical data link satellite EIRP requirement depends on several design variables such as data rate, aircraft antenna gain, and coding gain. Expected link signal and power parameters for the proposed MITRE concept are given in Tables 1 and 2 generation INMARSAT spacefor the second craft.[3-5]

| MODULATION                              | DPSK                |

|-----------------------------------------|---------------------|

| $E_{b}/N_{o}$ (BER = 10 <sup>-5</sup> ) | 10.4 dB             |

| CONVOLUTIONAL CODING                    | 1/2 rate,           |

| 201                                     | Constraint length-6 |

| CODING IMPROVEMENT                      | 3.5 dB              |

| IMPLEMENTATION MARGIN                   | 2.5 dB              |

| DATA RATE                               | 200 bps             |

| REQUIRED CARRIER-TO-NOISE               |                     |

| DENSITY RATIO (C/N <sub>o</sub> )       | 32.4 dBHz           |

| TABLE 1: SIGNAL                         | PARAMETERS          |

|                                         |                     |

|                                                                                                                                                                                                                                                                                                                                | FORWARD                                                                                                                      |                                                                                               | URN<br>HGA OFF*                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| TO SATELLITE                                                                                                                                                                                                                                                                                                                   |                                                                                                                              | HGA UN                                                                                        | HGA UFF                                                                                       |

| FREQUENCY (GHz)<br>IRANSMIT EIRP (dBW)                                                                                                                                                                                                                                                                                         | 6.42                                                                                                                         | 1.                                                                                            | 64                                                                                            |

| TRANSMIT EIRP (dBW)                                                                                                                                                                                                                                                                                                            | 66.0**                                                                                                                       | 11.3                                                                                          | 17.7                                                                                          |

| FREE SPACE LOSS (dB)                                                                                                                                                                                                                                                                                                           | 200.9                                                                                                                        | 189.2                                                                                         | 189.2                                                                                         |

| PROPAGATION MARGIN (dB)                                                                                                                                                                                                                                                                                                        | 1.7                                                                                                                          | 5.0#                                                                                          | 5.0#                                                                                          |

| RECEIVE G/T (dB/K)                                                                                                                                                                                                                                                                                                             | -14.0                                                                                                                        | -12.5                                                                                         | -12.5                                                                                         |

| PROPAGATION MARGIN (dB)<br>RECEIVE G/T (dB/K)<br>C/N <sub>O</sub> UP (dBHz)                                                                                                                                                                                                                                                    | 78.0                                                                                                                         | 33.2                                                                                          | 39.6                                                                                          |

| FROM SATELLITE                                                                                                                                                                                                                                                                                                                 |                                                                                                                              |                                                                                               |                                                                                               |

| FREQUENCY (GHz)                                                                                                                                                                                                                                                                                                                | 1.54                                                                                                                         | 4.                                                                                            | 20                                                                                            |

| SATELLITE EIRP (dBW)                                                                                                                                                                                                                                                                                                           | 24.0**                                                                                                                       | -21.4                                                                                         | -28.0                                                                                         |

| FREE SPACE LOSS (dB)                                                                                                                                                                                                                                                                                                           | 188.5                                                                                                                        | 197.3                                                                                         | 197.3                                                                                         |

| PROPAGATION MARGIN (dB)                                                                                                                                                                                                                                                                                                        | 5.0#                                                                                                                         | 2.0                                                                                           | 2.0                                                                                           |

| RECEIVE G/T (dB/K)                                                                                                                                                                                                                                                                                                             | -26.0##                                                                                                                      | 32.0                                                                                          | 32.0                                                                                          |

| PROPAGATION MARGIN (dB)<br>RECEIVE G/T (dB/K)<br>C/N <sub>O</sub> DOWN (dBHz)                                                                                                                                                                                                                                                  | 33.1                                                                                                                         | 39.9                                                                                          | 33.3                                                                                          |

| C/N <sub>o</sub> INTERMOD (dBHz)<br>C/N <sub>o</sub> TOTAL (dBHz)                                                                                                                                                                                                                                                              | 66.5                                                                                                                         | 70.0                                                                                          | 70.0                                                                                          |

| C/N <sub>O</sub> TOTAL (dBHz)                                                                                                                                                                                                                                                                                                  | 33.1                                                                                                                         | 32.4                                                                                          | 32.4                                                                                          |

| * The present generat<br>equipped with a high<br>vided primarily for<br>applications. The<br>satellites will be<br>amplifier that will<br>aeronautical band as<br>**Equivalent power of f<br>vice voice channels.<br># Propagation margin<br>zation, and absorbtio<br>##Receive system nois<br>be 500° K and the an<br>1.0 dB. | a-gain amp<br>maritime<br>next gen<br>equipped<br>operate in<br>well.<br>four INMAR:<br>includes<br>in losses.<br>se tempera | plifier (<br>search a<br>neration<br>with a<br>n a porti<br>SAT marit<br>fading,<br>ture is a | HGA) pro<br>and rescu<br>INMARSA<br>high-gai<br>on of th<br>ime ser-<br>polariza<br>assumed t |

| TABLE 2: LINK PARAMET                                                                                                                                                                                                                                                                                                          | TEDC AT 50                                                                                                                   | FLEVATIO                                                                                      | N ANGLE                                                                                       |

2. Aircraft Terminal Cost. The single aircraftterminal cost should include hardware and software, installation, antenna(s), and maintenance costs.

#### Capability Tradeoffs

System Capability. The first compromise in the design of a low-cost data link is a restriction on channel capacity. The channel capacity of the system, or the achievable data rate, is a function of the satellite EIRP for both the ground-to-air (forward) and air-to-ground (return) links. Therefore, data rates must be restricted in order to (1) avoid high service charges for the forward link, (2) minimize the cost of the power amplifier in the aircraft terminal transmitter on the return link, and (3) minimize the cost and complexity of signal processing electronics. It is clear that unless there is a revolutionary breakthrough in digital voice encoding, the proposed data link will not have sufficient capacity to provide voice communications (1,200 to 32,000 bps).

The experimental data link has been designed to handle the data rates required for air traffic control (ATC) and automatic dependent surveillance functions as derived in the OASIS report. Automatic dependent surveillance of air traffic relies on navigational position data generated on board the aircraft and automatically communicated to ATC ground stations. Independent surveillance describes surveillance methods which do not require such aircraft-generated data (e.g., radar). The average network data throughput requirement for North Atlantic air traffic through the year 2005 (223 in-flight aircraft) has been projected to be 200 bits per second (bps) over the forward link and 700 bps over the return link.[1] The return link capacity can be divided between four channels, each having a 200 bps capacity.[2]

In addition to lowering required signal power levels, the use of low data rates takes advantage of the availability and low cost of microelectronics, i.e., microprocessors that can handle most signal processing and encoding tasks when the data-rate-to-microprocessor-clock-rate ratio is low enough. It so happens that 200 bps approaches the upper data rate limit (400 bps may be achievable, but certainly nothing higher) for the type of microprocessor-based demodulator and error correction decoder implementations used in the experimental aircraft terminal design. (The experimental system operates at a standard data rate of 200 bps using 1/2 rate error-correction coding--2 channel symbols per information bit, or 400 channel symbols per second--with 8-bit, 4 MHz clock-rate microprocessor technology.)

#### The Aircraft Antenna

The aircraft antenna is a critical design feature because it plays a pivotal role in the data link cost tradeoff considerations. If, for a typical link power budget calculation, we assume a simple aircraft antenna with a hemispherical gain of +1 dBiC, the satellite L-band power required in the satellite-to-aircraft link is equivalent to approximately four INMARSAT maritime service voice channels.[2] On the other hand, if the aircraft antenna gain can be assumed to be somewhat higher, on the order of +6 dBiC, then the equivalent power of slightly more than one INMARSAT channel is required. Another significant advantage of a higher gain antenna is that because the antenna's directional discrimination is greater, channel degradation due to multipath interference is reduced. Probably the most sophisticated and best antenna for this application is a highgain steerable phased array; however, a phased array does not represent an option in the aeronautical data link design being considered here because such antennas are not currently available for what would be considered an acceptable cost.

Under the imposed cost constraints, the optimum antenna configuration appears to consist of two microstrip antenna elements, flush-mounted on each side of the aircraft, approximately 40° down from top-center. Each antenna element provides a gain of at least +1 dBiC over a 130° spherically symmetrical angle, and much better gains at angles approaching vertical. Their optimum peak gain in the vertical direction, relative to the plane of the antenna element, is about +5 dBiC. For overocean communications in the North Atlantic, the dual, side-mounted antenna configuration should be able to exploit some of this directivity because the one antenna element in use at any given time will be pointed in the general direction of the INMARSAT satellite for typical aircraft orientations and flight paths in the North Atlantic flight track system.

#### The Aeronautical Multipath Channel

The Multipath Problem. The most complex technical problem confronting the system design is the signal degradation caused by the aeronautical channel's multipath characteristic. A simple description of multipath interference follows. When the direct-path satellite signal arrives at the aircraft antenna, it is accompanied by an assortment of reflected signals, varying in phase and intensity. Out-of-phase reflections add destructively to the direct-path signal and cause fades whose durations and magnitudes vary randomly. The resulting interference to the desired signal is referred to as multipath interference. It poses a difficult problem because it cannot be overcome entirely by increasing transmitter power levels since the intensities of the reflected path signals would also increase proportionally.

#### Overcoming Multipath Through Coding

Error Correction Codes. Aside from using a highgain antenna with good directional discrimina-tion, another way to contend with the multipath problem is by the use of error correction coding with interleaving. The theory of error correction codes is an extension of the well-known singleerror-detecting parity check coding techniques. One significant difference in error-correction coding is that the quantity of redundant bits transmitted with the encoded message may vary from a small to a quite large percentage of the total message depending on the code rate used. The redundancy is exploited by the decoding algorithm to recover the original message from a received noise-corrupted encoded message if the number of errors in the received message is less than some maximum defined by the code.

Interleaving. Most error-correction codes are efficient at correcting random errors; however, in a multipath environment, the errors caused by fading may extend over long groups of encoded symbols, called error bursts. To manage the decoding of a message with error bursts, interleaving is used. It is a technique that essentially randomizes the channel errors received by the error correction decoder. It is performed in the transmitter processor after the data has been encoded and prior to transmission over the channel. A block of encoded symbols are reordered such that symbols ordered consecutively before interleaving are interspersed in the channel symbol stream, separated by a number (equal to the interleaving depth) of similarly reordered symbols. At the receiver, after the deinterleaving process is completed, channel burst errors appear to the error correction decoder as random, uncorrelated errors.

#### Interleaved Convolutional Encoding/Viterbi

Decoding. The error-correction code selected for the experimental aeronautical data link is a constraint-length-6, convolutional code; the decoder is a software-implemented soft-decision Viterbi decoding algorithm. The interleaving/ deinterleaving system uses an interleaving depth of 16 symbols. This value was arrived at as a compromise between a sufficiently long interleaving depth to decorrelate channel interference and a reasonably short minimum message length. Using this interleaving depth and a block interleaver, the shortest allowable data link message is 128 bits. While for most applications this is quite short, air traffic service applications generally would not require messages longer than 40 bits.[1]

The complexity of the Viterbi algorithm increases exponentially with the constraint length. The error correction capability of the convolutional code also increases with constraint length; in a Gaussian noise channel, a constraint-length increment of one provides an additional link performance gain of approximately 0.5 dB.[6] The experimental data link's convolutional code uses a constraint length of 6, which is less than desired, but the best possible under the real-time constraints imposed by the microprocessor. Typically, convolutional codes, used with Viterbi decoders in satellite data links, have constraint lengths ranging from 7 to 10.

Soft-decision Decoding. One of the reasons the Viterbi decoding algorithm was selected is that it is capable of processing soft-decision data very easily. A demodulator which performs channel measurements with resolutions higher than just the common two-state, one/zero measurement is said to make soft decisions. If the demodulator performs 3-bit, 8-level A-to-D conversions, a performance improvement of up to 2 dB over typical 1-bit conversions can be provided when soft-decision decoding is used.[6]

#### Reliability Requirements

As yet, no reliability requirements have been established for the various potential aeronautical data link applications. For the experimental data link design, it has been assumed that the probability of a channel bit error should not exceed  $10^{-5}$ .

#### Modulation and Demodulation

The Selected Modulation Technique. The modulation technique chosen for the experimental data link is differentially coherent phase-shift-keying (DPSK). This selection was based on a variety of criteria. Three of these criteria were: (1) power efficiency, (2) robustness in multipath fading, and (3) simplicity.

Although bandwidth constraints do not present a serious design restriction since data rates are much lower than the available bandwidth, spreadspectrum modulation techniques were not considered appropriate for this application. Because of the ample bandwidth, there was no point in considering M-ary PSK techniques, common in commercial communication applications which require high bandwidth efficiency. Likewise, multiple frequency shift keying (MFSK), as well as other technically viable modulation techniques such as minimal-shift keying (MSK), also were not considered seriously mainly because their implementations are significantly more complex than that of DPSK. [7] The selection alternatives were restricted to binary modulation techniques.

In an additive white Gaussian noise (AWGN) channel, phase-shift keyed (PSK) signals can be demodulated with a power efficiency 3 dB greater than frequency-shift keyed (FSK) signals. Coherent modulation methods, such as coherent binary PSK (BPSK), under the same AWGN channel conditions, perform slightly better than DPSK, a noncoherent technique. However, for this application, modulation performances must be evaluated in the aeronautical channel subject to phase noise and multipath fading.

The Phase Noise Problem. The low-data-rate data link application presents a design problem not encountered in higher capacity systems. Phase noise generated by oscillators in the earth station and aircraft terminals, as well as in the satellite, seriously degrades the performance of PSK systems at low data rates. Coherent demodulation systems are more seriously affected by phase noise than are noncoherent systems, due to the degraded performance of the integral phase-tracking loop necessary in coherent systems. According to calculations performed using INMARSAT phase noise specifications and the assumption of a slow fading channel, the performance of BPSK becomes unacceptable at channel symbol rates below about 350 bps, whereas DPSK is shown to perform adequately for symbol rates down to about 100 bps.[8] FSK systems are the most resistant to phase noise, but this does not outweigh their power efficiency disadvantage in AWGN channels.

Modem Performance in Multipath Fading. FSK modulation performs better than DPSK when severe fading conditions are present. However, in a standard nonfading environment, it performs 3 dB worse; and when coding and interleaving are used, FSK loses all of its advantages.[9]

#### Multiple Access

In a full-scale data link design, the multiple access system must accommodate as many as 223 aircraft that may be using the data link system at any one time. In the ground-to-air direction, the total channel capacity requirement (200 bps) is small enough to allow all users to share a common time-division multiple access (TDMA) channel. A discrete, address-mode service would operate by including an aircraft address with each message transmission. Each aircraft terminal would have the capability of recognizing its own address, whereupon it would respond appropriately.

The complexity in multiple access design is concentrated in the air-to-ground link. First, it seems probable that the 700 bps total required air-to-ground channel capacity would be split between four separate 200 bps channels, to form a time/frequency division multiple access (TDMA/ FDMA) hybrid--essentially four separate TDMA channels. For a TDMA channel to operate in this multi-user aeronautical scenario, air-to-ground transmissions would either occur in response to ground-to-air polls or be very carefully timed. The earth station terminal must acquire the signal carrier (the frequency of which is unknown due to Doppler and oscillator uncertainties) for each air-to-ground message transmission. This carrier acquisition must proceed quickly for the system to achieve the necessary system throughput performance. The experimental data link will demonstrate the use of an array-processor fast Fourier transform technique to quickly estimate the carrier frequency for fast carrier acquisition on air-to-ground transmissions.

Additional complexity is associated with air-toground message timing and arbitration. Each aircraft terminal must be synchronized to the earth station terminal to ensure that: (1) more than one aircraft message does not crowd the channel at any point in time; and (2) that the earth station terminal is in its carrier acquisition mode during the time any aircraft terminal may be sending its carrier-burst message preamble to initiate carrier synchronization.

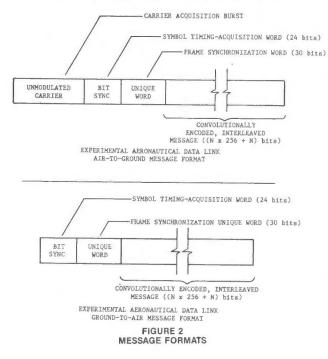

#### Message Format

Appropriate message format structures are required for the data link design. However, since at this time no specialized services have been proposed, it would be premature to try to define them. The message formats that will be used with the experimental aeronautical data link will closely resemble typical INMARSAT message formats.

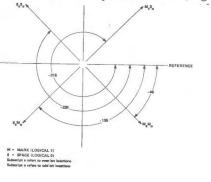

The message formats (illustrated in Figure 2) must contain: (1) a preamble consisting of a carrier recovery field (in return direction only), a bit timing field, and a "unique word" for frame synchronization; and (2) an information field which will contain the aircraft address, the message type, and the data field.

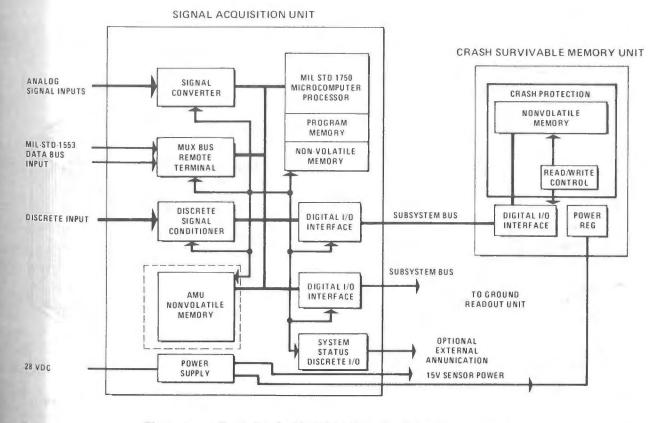

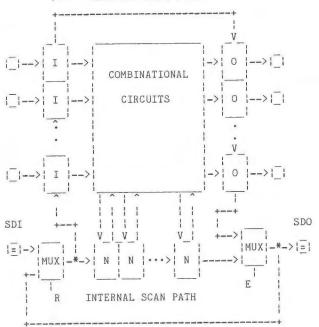

#### Aircraft Terminal Design Configuration

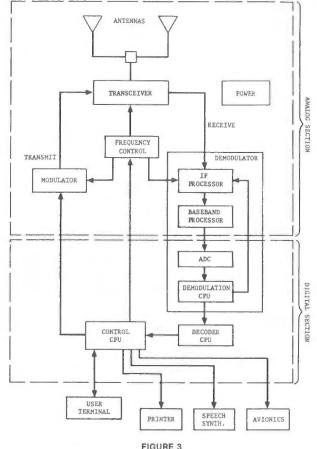

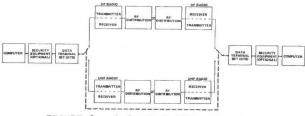

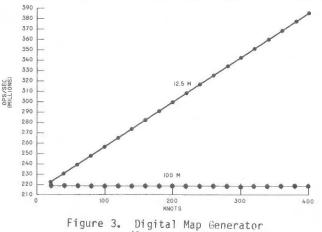

This section provides a description of the experimental aircraft terminal that will be used to demonstrate and test the aeronautical data link concept. The aircraft terminal design may be divided into two major parts—(1) the analog, RF section; and (2) the digital section. Figure 3 shows a schematic diagram of the principal aircraft terminal subsystems. The power subsystem is associated with both the RF and digital sections. A major design objective has been to develop a simple system that can be built from low-cost, off-the-shelf modules. The emphasis is on low-risk, commonly available technology, which minimizes the need for circuit-level hardware design.

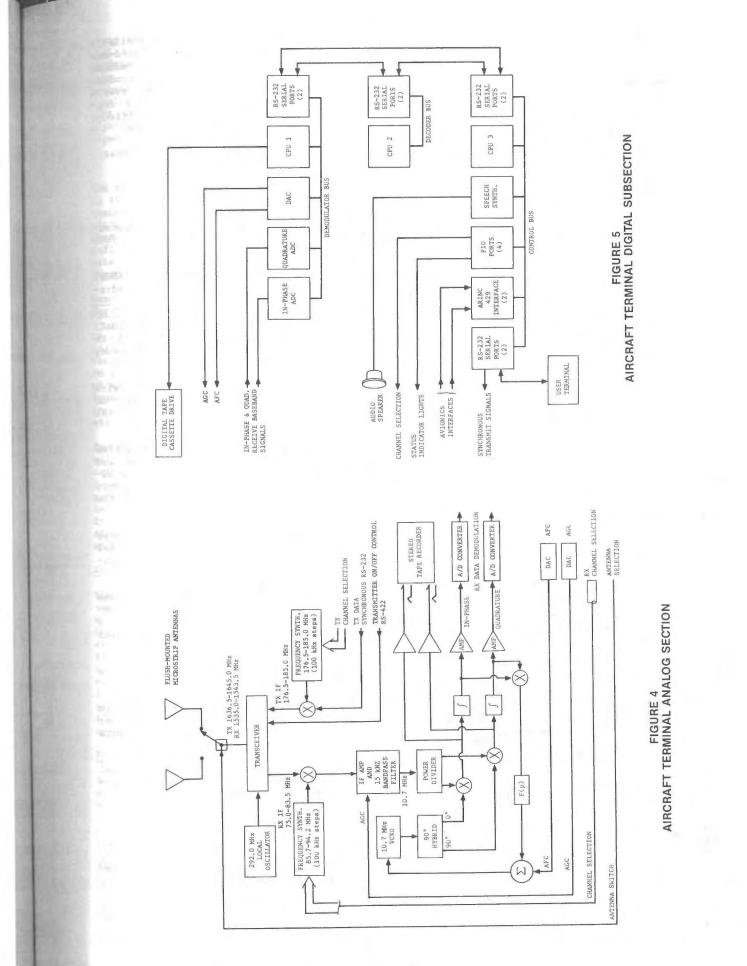

#### **RF** Section

The RF section (Figure 4) consists of four basic subsystems:

AIRCRAFT TERMINAL BLOCK DIAGRAM

- 1. Antenna Subsystem

- 2. Transceiver

- 3. Channel Selection Subsystem

- 4. IF Subsystem

Antenna Subsystem. The antenna subsystem consists of the following components:

- 1. Antennas

- 2. Coaxial cable

- 3. RF switch

The optimum antenna configuration, in terms of a compromise between cost and performance, is a pair of two side-mounted microstrip antennas, positioned 40 degrees down from vertical on each side of the aircraft. It is hoped that sidemounting two microstrip elements will optimize the antenna directivity relative to the satellite position for relatively low elevation angles so that coverage is available even during banks and turns.

The drag produced by antennas is a critical cost factor to high-performance aircraft. The microstrip elements are optimum in this respect since they are small and less than 0.10 inch thick; therefore, drag is minimized.

The length of coaxial cable required to connect the antenna to the aircraft terminal transceiver

terminal transceiver is another critical design issue. At L-band frequencies, low-loss coaxial cable causes an attenuation of approximately 3 dB per 100 ft. Because of this, it is desirable to mount the antennas as close as possible to the equipment bay, where the aircraft terminal would be located. Another alternative is to mount the L-band transceiver somewhere close to the antenna and connect the IF and signal processing electronics to the transceiver via coaxial cable. Attenuation losses are less severe at IF frequencies.

The signals from only one of the two microstrip antennas will be received at any time, depending on which antenna is pointed most directly toward the satellite. Under processor control, an electrically controlled RF coaxial switch will select the proper antenna.

Transceiver The transceiver used in the experimental aircraft terminal design is a standard INMARSAT transceiver. L-band transmit and receive frequencies are 1636.5-1645.0 MHz and 1535.0-1543.5 MHz respectively. The transmit IF input is 176.5-185.0 MHz; the receive IF output is 75.0-83.5 MHz. The specified noise figure of the receiver is 2.5 dB under all conditions. The maximum power output of the transmitter is 28 watts.

A diplexer allows the use of a single RF antenna port to support both the transmitter and receiver.

Channel Selection Subsystem. The channel selection subsystem consists of a pair of frequency synthesizers, digitally controlled, that operate in the transmit and receive IF frequency bands to enable transmit and receive channel selection. Frequency synthesizers with the high performance specifications for low phase and low spurious noise required by this design are generally not off-the-shelf items. Therefore, the synthesizers used to build the aircraft terminal have frequency steps of 100 kHz, larger than desired by a factor of four.

IF Subsystem. The receive channel frequency synthesizer will downconvert the receive channel transceiver IF output to 10.7 MHz. The demodulation processing of the received signal begins with a 15 kHz bandpass filter centered at 10.7 MHz. The 10.7 MHz band signal is passed through a power divider; the two outputs are then mixed with voltage controlled oscillator (VCXO) frequencies, 90 degrees out of phase, to produce in-phase and quadrature baseband outputs. The VCXO is centered at 10.7 MHz but is variable under processor control to facilitate the automatic frequency tracking function.

The in-phase and quadrature baseband signals pass through an analog signal processing section consisting of an integrator and an amplifier, after which the signals are sampled by an analog-todigital (A/D) converter for further processing in the digital section.

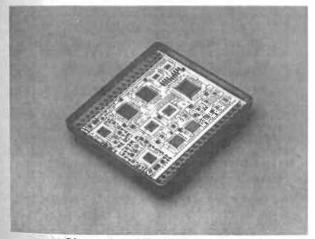

#### The Digital Section

The aircraft terminal digital hardware subsystem, illustrated in Figure 5, consists entirely of 8-bit Standard Bus (STD Bus) modules. Three processors (STD Bus CPU modules) operate on three separate busses; no bus arbitration is available with STD Bus technology to manage shared-bus systems. This arrangement is effective because the processors handle three almost independent tasks. The processing load is divided evenly between them, and interbus, interprocessor communications are handled with sufficient efficiency via asynchronous serial communications ports.

The three processors are referred to as follows:

- 1. Demodulation Processor

- 2. Decoder Processor

- 3. Control Processor

Demodulation Processor. The demodulation processor operates on a bus in conjunction with four other STD Bus modules:

- two analog-to-digital converters (ADCs) used to sample the in-phase and quadrature baseband signals;

- one digital-to-analog converter (DAC) module with multiple outputs used to control automatic gain and frequency tracking loops; and

- one serial communications module with two ports, i.e., one port for interbus communications and one for a digital tape cassette interface.

The demodulation processor handles the real-time sampling, bit synchronization, demodulation, and signal control functions for the aircraft terminal. When a DPSK demodulation decision is formed, the 3-bit soft-decision value is passed to the decoder processor.

Decoder Processor. The decoder processor operates on a bus with just one other module: a serial communications module to provide interbus communications to the other processors.

The functions of the decoder processor are frame synchronization; code-block formatting; and buffering, deinterleaving, and decoding. When a message has been completely decoded, it is passed to the control processor.

<u>Control Processor</u>. The control processor operates on a bus with four other modules:

- two serial communications modules to provide interbus communications, a user terminal interface, and synchronous data link transmit control;

- one ARINC 429 (airline industry digital bus standard) dual-port serial avionics interface module; and

- 3. one speech synthesis module.

The main control processor functions are (1) to provide a user terminal monitor with simple menu and editing features; (2) to perform all data link transmit functions, such as message formatting, interleaving, convolutional error-correction encoding, differential encoding, and synchronous manchester encoded transmission; (3) to provide software arbitration for all digital interfaces, such as those to avionics systems and test equipment; and (4) to act as a message processor which will operate on ground-to-aircraft messages and perform appropriate functions according to message type. Unlike the other processors, the control processor does not have a dedicated real-timesensitive function. It is flexible in the sense that much of its software may be written in a high-level language, and can therefore be easily augmented, updated, and modified.

#### Test and Demonstration Plans

The aeronautical data link will be flight tested in the summer of 1985 using an INMARSAT satellite channel. The objectives of the tests will be to prove the overall concept and to generate data that will be of use in developing engineering refinements for a potential future full-scale data link design. Some objectives of the demonstration program are as follows.

#### Demonstration of Remote Automatic Dependent Surveillance

As concluded in the OASIS final report, and stated earlier in this paper, the data link capacities required for automatic dependent surveillance are on the order of 200 bps per channel for the communication of navigational data generated by onboard navigation systems to air traffic control centers, so that position tracking of en route aircraft can be maintained.

For the flight tests, the MITRE aircraft terminal will be equipped with an avionics interface to receive data from a standard navigation unit; the data will be periodically transmitted to the ground segment. For demonstration purposes, the data may be communicated from the earth station in Southbury, Connecticut to a MITRE-based demonstration site where a computer graphics display will show the progress of the tracked aircraft.

#### Channel Verification Tests

The next order of priority will be the channel verification tests. Bit error rate (BER) tests will be performed at three transmit power levels. Channel propagation tests will also be performed at three power levels to measure the channel multipath characteristics as well as to measure carrier acquisition performance levels. The tests will be performed while flying at a geographical latitude that will ensure that the test results are representative of worst-case satellite elevation angles in the North Atlantic organized track system, but not necessarily the polar routes.

#### Demonstration of Message Transfer

Basic message transfer capabilities will be demonstrated. This capability forms the basis of a number of possible user services, such as company business data communications and telex.

#### Demonstration of Weather Data Transfer

Based on previous work done at MITRE, it should be possible to demonstrate the ground-to-aircraft transfer of simple weather map facsimiles.

#### Summary

The design of an experimental aeronautical satel-

lite data link has been accomplished using offthe-shelf components and a simple configuration of three microcomputers. The main objectives of this project are to determine the required level of satellite power necessary to operate a lowcapacity aeronautical data link and to demonstrate the feasibility of an air-ground communications system for aviation applications which uses a shared satellite system. After the project flight tests have been completed at the end of fiscal year 1985, sufficient data should be available to enable an efficient full-scale design. Further details concerning the aircraft and ground station terminal designs, as well as signal processing and multiple access strategies, will be made available in the final project report.

#### Acknowledgments

Acknowledgments are given to Walter C. Scales who conceived and initiated this project and performed the systems studies and high-level design, and to Lawrence Hogle and Yaroslav Kaminsky, who helped significantly in the preparation of the article.

#### References

- G. J. Couluris and B. Conrad, "Oceanic Area System Improvement Study," SRI Report No. FAA-EM-81-17, Vol. 1, September 1981.

- [2] OASIS Working Group B "Consideration of INMARSAT for an Aeronautical Data Link Only Service for the NAT," ARC 82/WP-5, WGB, November 1981.

- [3] "Revised Characteristics of INMARSAT Second Generation Satellite Transponders," CCIR, IWP 8/7 Sub-group, Document No. INMARSAT/15, 19 October 1983.

- [4] "Satellite EPIRB Coordinated Trials Programme Using the INMARSAT Geostatioary Space Segment Operating in the 1.6 GHz Band," CCIR, Interim Meeting of Study Group 8, Mobile Services, New Draft Report, Document 8/167, Table III; Geneva, May 1984.

- [5] "Link Power Budgets for a Maritime Mobile Satellite Service," CCIR, XVth Plenary Assembly, Mobile Services Vol. VIII, Report 760-1, pp. 541-551, Geneva, 1982.

- [6] J. A. Heller and I. M. Jacobs, "Viterbi Decoding for Satellite and Space Communication," IEEE Trans. Commun. Tech., Vol. COM-19 No. 5, October 1971.

- [7] J. J. Spilker, "Digital Communications by Satellite," Englewood Cliffs, New Jersey, Prentice-Hall, 1977.

- [8] S. Rhodes, W. Hagmann, P. Chang, and R. Fang, "Signal Design for INMARSAT Standard C Ship Earth Stations," Globecom '82, Vol. 3, Miami, November 29-December 2, 1982.

- [9] D. Chase, "Digital Signal Design Concepts for a Time-Varying Rician Channel," IEEE Trans. Commun. Tech., Vol. COM-24, February 1976.

Stephen R. Schmitt Naval Air Development Center Warminster, Pa. 18974

#### Abstract

A digital signal processing algorithm based on the Kalman filter is shown to be suitable for use in an airborne adaptive low frequency communications array. The Kalman filter is used to adjust the weights in a weighted sum of antenna element outputs in order to minimize the mean square error between this sum and a replica of the transmitted waveform. The algorithm uses decision aiding in which bit decisions indicate the correct replica waveform used in estimation of the optimal weights. An impulsive noise suppression subroutine is included as part of the algorithm to reduce the effects of atmospheric noise.

#### Introduction

An important frequency band used for radio communications at very long ranges is the region of the RF spectrum below 100kHz covering the Extremely Low, Very Low, and Low Frequency bands. Study of radio propagation and noise in these bands has continued for many decades (1-8). At frequencies below about 100kHz the region between the earth's surface and the ionosphere acts much like a waveguide. The dominant propogation modes are those with the electric field oriented vertically (TM mode). This fact makes possible signal reception with magnetic dipole antenna arrays in which the gain of an antenna element varies with azimuthal direction. The problem under study is that of applying adaptive array techniques to a magnetic dipole array in order to suppress interference. At frequencies below 100kHz it is impractical to make use of phase differences between antenna elements since the wavelengths at these frequencies are very long; however, the effects of varying the gain patterns of several antenna elements can be exploited for adaptive spatial filtering.

#### Communication System Simulation Description

The digital computer simulation used in this study includes mathematical models of an analog modulator, additive continuous wave (CW) interference, additive impulsive atmospheric noise, two loop antenna elements each connected to a frequency converter which converts to baseband, and a digital filter which optimally combines the baseband waveforms to recover the transmitted data.

A commonly used waveform for communication in the frequency band below 100kHz is the minimum shift keying (MSK) waveform. This waveform can be formed from the linear sum of two modulated phase-shift-keying (PSK) waveforms. The MSK waveform can be demodulated by a pair of PSK matched filters. In the simulations used in this study, a PSK waveform is assumed.

This paper is declared a work of the U.S. Government and therefore is in the public domain. The algorithms used in the digital filtering part of the simulation are, therefore, quite similar to those which would be employed for the MSK waveform.

The analog modulator which is simulated produces a binary PSK waveform at modulation rate 400/sec with a carrier at 6.4kHz. Two orthogonal 8-chip codewords are used to represent binary data resulting in a data rate of 50 bits/sec. The resulting waveform is a direct sequence spread spectrum signal. In a real system the codewords may be encrypted by mod-2 addition with a binary keystream at rate 400/sec.

The interfering waveform is a tone at the carrier frequency of 6.4kHz. The amplitude of the interfering waveform is set considerably larger than the amplitude of the signal. The Signal-to-Interference (SIR) power ratio is adjusted by changing the amplitude of the signal resulting in the simulation of a relatively constant power output from the frequency converters. The phase difference between the interfering waveform and the signal carrier is set randomly for each run of the computer simulation.

The method of simulating atmospheric noise is intended to represent the physical nature of the environment in order to study how the digital filtering algorithm would perform in the presence of this type of noise. It is not necessary to develope a highly accurate simulation of atmospheric noise for this purpose. The model of atmospheric noise assumes several discrete impulse sources distributed uniformly over the surface of a sphere. The strength of an impulse is reduced according to Pierce's formula (9) to simulate the effects of distance on attenuating electromagnetic waves propogating within the earth-ionosphere spherical waveguide. Each source generates impulses randomly. The loop antenna model, Pierce's formula, and the range and bearing of each source from the receiver are used to compute the output of each antenna element in order to simulate the reception of atmospheric noise.

Using Pierce's formula, the attenuation of a signal is proportional to:

$$exp[(-a \cdot d/R)/sin(d/R)]$$

in which:

d - distance along the spherical surface from the signal source to the receiver

R - radius of the sphere

462

#### a - attenuation constant (2.56 at 30kHz, 0.456 at 3kHz, 2 in the simulation)

Distribution of noise sources uniformly on the surface of a sphere can be easily accomplished by use of the fact that the area on a sphere between two parallel planes cutting the sphere in linarly proportional to the distance between them. Then:

#### $d = R \cdot \arccos[(R-h)/R]$

in which h is the distance on a line from the receiver through the center of the sphere. Letting h vary uniformly over [0,2R] and the azimuth angle vary uniformly over  $[0, 2\pi]$  allows the selection of pairs of points in terms of range and azimuth from a receiver which describe a uniform distribution of impulsive noise sources on the surface of a sphere representing the earth. The locations of noise sources can be set randomly for each run of the simulation. A statistical parameter,  $V_d$ , is used as a measure of atmospheric noise impulsivity (5). It is defined as the ratio of the root-meansquare to average voltage of the noise envelope at the output of a band pass filter. The atmospheric noise generation subroutine produces about 100 pulses per second from all sources which generally results in a value for  $v_d$  of about 10 dB in a bandwidth of 200 Hz.

The fact that the dominant signal propagation modes below 100kHz are those with the electric field vertical and the magnetic field horizontal is used in the mathematical model of a two element magnetic dipole antenna array. For a time varying magnetic field, B(t), the output of a single loop is:

$$v(t) = -A \cdot \cos(\theta) \cdot B(t)$$

in which:

- B(t) magnetic induction, volt-seconds/meter<sup>2</sup>

- A surface area of loop, meter<sup>2</sup>

- $\theta$  angle between <u>B(t)</u> and a line perpendicular to the loop plane

The antenna array model used in this study consists of two magnetic dipoles with both axes in a horizontal plane and with both axes at right angles. The horizontal plane moves with aircraft pitch, roll, and yaw so that the antenna element ouputs are given by:

$$V_1(t) = g_1s(t) \cdot sin(a) \cdot cos(b)$$

$v_2(t) = g_2s(t) \cdot cos(a) \cdot cos(c)$

where:

- gi antenna gain constants

- s(t) signal

- a angle of arrival of signal

- b aircraft pitch angle

#### c - aircraft roll angle

In simulating the antenna array, a sine wave signal is assumed and the antenna element ouputs are simplified to:

$$v_1 = s \cdot sin(a) \cdot cos(b)$$

$$v_2 = s \cdot \cos(a) \cdot \cos(c)$$

Each frequency converter simulated in this study produces inphase and quadrature components of the baseband waveform by a single stage conversion of the signal received from an antenna element followed by a low pass filter for each component. It is assumed that a highly stable reference signal is available at the receiver. This technique, when combined with adaptive digital filtering, would eliminate the need for a phase locked loop.

The low pass filter used in the computer simulation has the discrete transfer function:

$$G(z) = \frac{.11990976z}{z^2 - 1.7254245z + .75865088}$$

which results in a sampled data low pass filter of second order having a cutoff frequency of 796 Hz when the sampling rate is 25,600 samples per second (the sampling rate used in the simulation of the analog portion of the system).

Samples of the baseband waveform are obtained from each frequency converter at a rate of 1600/sec. The weight adjustment algorithm uses bit decisions to determine the correct reference waveform to be used in the weight adjustment process. For data synchronization, several correlators are run in parallel, each with a different timing hypothesis. The correlation result with the least error determines the estimate of the transmitted data and indicates the best estimate of waveform timing.

#### Digital Filter Algorithm

The digital filter (10) has the goal of minimizing the mean-square-error (MSE):

$$E e^2 = E[d(k) - w'x(k)]^2$$

which is defined as the average squared error between discrete samples of a reference waveform d(k) and the weighted sum of a set of signal samples  $\underline{x}(k)$  taken at the output of the analog portion of the array at time kT. Since the simulated system communicates with a series of binary data waveforms, the correct reference signal is then a replica of one of two possible transmitted signals:

$d_0(k)$ , k:1,...,N if 0 transmitted  $d_1(k)$ , k:1,...,N if 1 transmitted

Matched filtering, in which:

y(k) = w'x(k)

is compared with  $d_{O}(k)$  and  $d_{1}(k)$  is performed. The comparison having the least cumulative error indicates the correct reference signal and gives an estimate of the transmitted data. Once the correct reference signal is known, the algorithm can calculate updated sets of weights  $\underline{w}$ .

The mathematical model of the dynamic behavior of the optimal array weights can be represented by:

$$\underline{W}_{O}(k+1) = A(k+1,k) W_{O}(k) + u(k)$$

in which:

$$E u(k)u'(k) = Q(k)$$

and in which the weight transition matrix defines how the optimal weights  $\underline{w}_O$  change as the aircraft maneuvers. The noise vector  $\underline{u}(k)$  accounts for errors in the mathematical model of the system. The system measurements can be represented by a noise corrupted version of the optimal array output:

$$d(k) = \underline{x}'(k)\underline{w}_{O}(k) + v(k)$$

in which:

$$E v(k) \cdot v(k) = r^2(k)$$

A filtering algorithm for weight determination can be defined by use of the Kalman filtering equations in which  $\underline{w}$  is the state vector:

$$\underline{W}_{p}(k+1) = A(k+1,k)W_{f}(k)$$

$$P_{D}(k+1) = A(k+1,k)P_{f}(k)A'(k+1,k) + Q(k)$$

$$K(k) = \frac{P_{p}(k+1)\underline{x}(k)}{\underline{x}'(k)P_{p}(k+1)x(k) + r^{2}(k)}$$

$P_{f}(k+1) = P_{p}(k+1) - K(k)x'(k)P_{p}(k+1)$

$\frac{W}{f}(k+1) = \frac{W}{p}(k+1) + K(k)[d(k) - x'(k)W_{p}(k+1)]$

These equations constitute a Kalman filtering algorithm for determining the optimum values of the elements of  $\underline{w}$  in which:

- $\frac{W}{p}(k)$  predicted weight vector

- wf(k) filtered weight vector

A(k+1,k) - weight transition matrix

P<sub>D</sub>(k) - predicted covariance matrix

P<sub>f</sub>(k) - filtered covariance matrix

K(k) - Kalman gain matrix

The weight transition matrix may be derived for the case under study by making use of the optimal solution for the weight vector for the baseband waveform determined by four equations in four unknowns:

$2 \cos(Ps)/As = W_{1} \cdot g_{1} \cdot sin(a_{s}) \cdot cos(b) +$

+ w3.g2.cos(as).cos(c)

$2 \sin(P_s)/A_s = w_2 \cdot g_1 \cdot \sin(a_s) \cdot \cos(b) +$

+ w4.g2.cos(as).cos(c)

$0 = w_{1} \cdot g_{1} \cdot \sin(a_{j}) \cdot \cos(b) +$

+ w3.g2.cos(aj).cos(c)

$0 = W_2 \cdot g_1 \cdot \sin(a_j) \cdot \cos(b) +$

+ w4.g2.cos(a;).cos(c)

This can be written in the matrix form:

e = Sw

The incremental changes in the optimum weight vector are determined by a weight transition matrix so that:

$$w(k+1) = A(k+1,k)w(k)$$

Since the phase, amplitude, and locations of the signal and interference sources are approximately constant:

$$e = S(k)w(k) = S(k+1)w(k+1)$$

and,

$$w(k+1) = S^{-1}(k+1)e$$

then by substitution:

$$S^{-1}(k+1)e = A(k+1,k)S^{-1}(k)e$$

giving:

$$A(k+1,k) = S^{-1}(k+1)S(k)$$

The change in azimuth angle, roll, and pitch from time kT to (k+1)T are given by:

$a_{s}(k+1) = a_{s}(k) - da(k+1)$   $a_{j}(k+1) = a_{j}(k) - da(k+1)$  b(k+1) = b(k) + db(k+1) c(k+1) = c(k) + dc(k+1)

in which da, db, and dc are the incremental changes in heading, pitch, and roll of the aircraft. By performing many trigonometric and algebraic manipulations, the elements of the weight transistion matrix can be reduced to:

$a_1 = \cos(da) \cdot \cos(db) +$

+ cos(da).sin(db).sin(b)/cos(b)

$a_2 = -\sin(da) \cdot \cos(dc) \cdot \cos(c) / \cos(b) -$

- sin(da).sin(dc).sin(c)/cos(b)

$a_3 = \sin(da) \cdot \cos(db) \cdot \cos(b) / \cos(c) +$

+ sin(da).sin(db).sin(b)/cos(c)

$a_4 = \cos(da) \cdot \cos(dc) +$

+ cos(da).sin(dc).sin(c)/cos(c)

in which:

A(k+1,k) =

$$= \begin{bmatrix} a_{1}(k+1) & 0 & a_{2}(k+1) & 0 \\ 0 & a_{1}(k+1) & 0 & a_{2}(k+1) \\ a_{3}(k+1) & 0 & a_{4}(k+1) & 0 \\ 0 & a_{3}(k+1) & 0 & a_{4}(k+1) \end{bmatrix}$$

The terms of each trigonometrix expression are evaluated at time (k+1)T. It can be seen that the weight transition matrix may be computed using only measurements of aircraft heading, pitch, and roll.

The simulated algorithm updates the covariance matrix and the Kalman gains once each sample period. A pair of filtered and a pair of predicted weight vectors for each timing hypothesis is updated each sample period with each weight vector in a pair corresponding to one of two possible bit decisions. At the end of a bit period for each timing hypothesis a bit decision is made and stored. The associated filtered weight vector is retained as the starting filtered weight vectors for both possible bit decisions in the next cycle. After a complete set of timing hypothesis parameters have been updated, the bit decision corresponding to the best timing estimate is chosen as the filter output.

Impulsive atmospheric noise can affect an adaptive array algorithm adversely, causing momentary losses of the signal or preventing algorithm convergence in some cases. The effects of atmospheric noise can be mitigated to some extent if a "hole punching" subroutine is added to each adaptive array algorithm. Note that the adaptive process causes the average power of the array filter output to approach the average power of the reference waveform as the adaptive process continues period. This process is quite rapid. The hole punching subroutine performs the following algorithm:

This algorithm zeroes the current filter output and the input samples if a noise pulse is detected. A noise pulse is indicated in the hole punch subroutine if the instantaneous filter output power is two times or 3 dB greater than the estimated signal power. The hole puncher is designed to suppress large noise pulses which have the greatest adverse effects on the adaptive algorithms. In the Kalman filter, replacing each sample with zero prevents the update of the filtered weight vector and the filtered covariance matrix by causing the Kalman gain vector to be zero during the sample in which a noise impulse is removed. The bit decision correlators will also not be incremented for a large impulse to improve the bit decision error rate.

#### Simulation Results

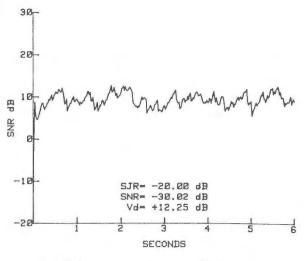

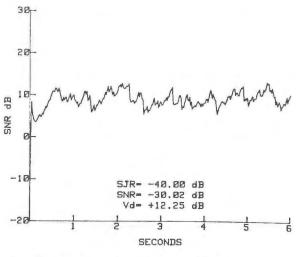

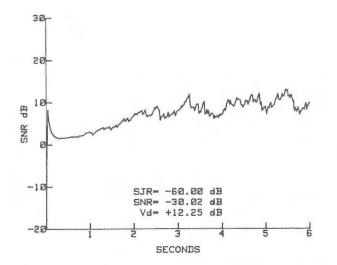

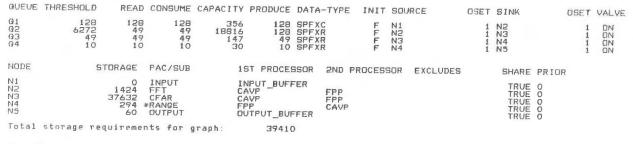

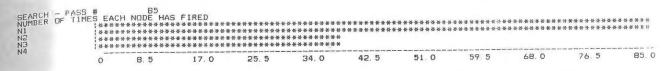

Computer simulations were run in which the signal-to-noise power ratio was set to -30 dB for signal-to-interference power ratios of -20, -40, and -60 dB. The SNR of the filters output for each case are graphed in figures 1 - 3. The simulation program included a subroutine which modeled the effect of a rapid aircraft maneuver on antenna attitude. Six seconds of real time were simulated with straight and level flight for the first second, a roll to a bank angle of 45 degrees during the next second, and a turn at 9 degrees per second during the remaining four seconds.

Fig. 2 Filter output SNR at -40 dB SIR

Fig. 3 Filter output SNR at -60 dB SIR

#### Conclusions

The result of the study suggest that relatively high data rate transmission can be maintained in low frequency communication systems in the presence of strong interference and high levels of atmospheric noise by using an adaptive array based on the Kalman filter. However, the computational burden imposed, assuming a 20 msec sync window for instantaneous data synchronization, is 4.7 million arithimetic operations per second. By using a search technique for data synchronizations the computational burden may be reduced to 557 thousand arithimetric operations per second. Practical implementation of this algorithm would require a compact processor capable of very high speed computation.

#### References

- Special Issue of the Proceedings of the IRE, Vol.45, No. 6, June 1957

- (2) I. J. Rothmuller, "Effect of the VLF Propagation Channel on Spread -Spectrum Communications Systems," Naval Electronics Laboratory Center, San Diego, CA, NELC Technical Report 1834, 4 August 1972

- (3) F. J. Kelly, J. P. Hauser, H. M. Beck, and F. J. Rhoads, "Multipath VLF Propagation Effects on Correlation Receivers," Naval Research Laboratory, Washington, DC, NRL Report 8521, 18 September 1981

- (4) E. L. Maxwell and D. L. Stone, "Natural Noise Fields from lcps to 100kc,"IEEE Transactions on Antennas and Propagation, pp.339-343, May 1963

- (5) International Radio Consultative Committee, "World distribution and characteristics of atmospheric radio noise," International Tele-communications Union, Geneva, Switzerland, Report 322, 1964

- J. K. Omura and P. D. Shaft, "Modem Performance in VLF Atmospheric Noise, "IEEE Transactions on Communications Technology, Vol. com-19, pp. 659-668, 1971

- (7) E. Bolton, "Simulating Atmospheric Radio Noise from Low Frequency Through High Frequency," The Review of Scientific Instruments, Vol. 42, No. 5, pp. 574-577, 1971