edited by Paulo Cappelletti Carla Golla Piero Olivo Enrico Zanoni

KLUWER ACADEMIC PUBLISHERS

Ву

Paulo Cappelletti

Carla Golla

Piero Olivo

Enrico Zanoni

KLUWER ACADEMIC PUBLISHERS

Boston/Dordrecht/London

### Distributors for North, Central and South America:

Kluwer Academic Publishers

101 Philip Drive

Assinippi Park

Norwell, Massachusetts 02061 USA

Telephone (781) 871-6600

Fax (781) 871-6528

E-Mail < kluwer@wkap.com>

## Distributors for all other countries:

Kluwer Academic Publishers Group

Distribution Centre

Post Office Box 322

3300 AH Dordrecht, THE NETHERLANDS

Telephone 31 78 6392 392

Fax 31 78 6546 474

E-Mail <orderdept@wkap.nl>

Electronic Services < http://www.wkap.nl>

# Library of Congress Cataloging-in-Publication Data

Flash memories / by Paulo Cappelletti ... (et al.).

p. cm

Includes bibliographical references.

ISBN 0-7923-8487-3

1. Flash memories (computers) I. Cappelletti, Paulo TK7895.M4F58 1999

004.5--dc21

99-25278

**CIP**

# Copyright <sup>©</sup> 1999 by Kluwer Academic Publishers

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher, Kluwer Academic Publishers, 101 Philip Drive, Assinippi Park, Norwell, Massachusetts 02061

Printed on acid-free paper.

Printed in the United States of America

# Contents

| LIASHI                          | MEMORIES: AN OVERVIEW                                                                    | 1        |  |

|---------------------------------|------------------------------------------------------------------------------------------|----------|--|

|                                 | E. Zanoni                                                                                | _        |  |

| 1.1                             | ·                                                                                        |          |  |

| 1.2                             | .2 Evolution of Non-volatile Memories                                                    |          |  |

| 1.3 The Floating Gate Device    |                                                                                          |          |  |

| 1.4 Charge Injection Mechanisms |                                                                                          |          |  |

| 1.5                             | Erasable Programmable Read Only Memories                                                 | 7        |  |

|                                 | 1.5.1 The Floating gate Avalanche-injection MOS transistor (FAMOS) Cell                  | 7        |  |

|                                 | 1.5.2 The basic Erasable Programmable Read Only Memory (EPROM)                           | 8        |  |

| 1.6                             | Electrically Erasable Programmable Read Only Memories                                    | 9        |  |

|                                 | 1.6.1 The FLOating gate Thin Oxide (FLOTOX) Memory Cell                                  | 9        |  |

|                                 | <ul><li>1.6.2 Textured Polysilicon Cells</li><li>1.6.3 The EEPROM Architecture</li></ul> | 10<br>12 |  |

|                                 | 1.6.4 Ferroelectric Memories                                                             | 13       |  |

| 1.7                             | Flash Memories: The Basic ETOX Cell. Programming and Erasing Mechanisms                  | 15       |  |

| <sub>V</sub> 1.8                |                                                                                          |          |  |

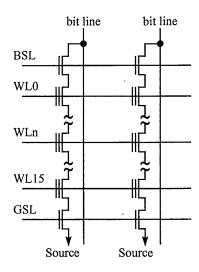

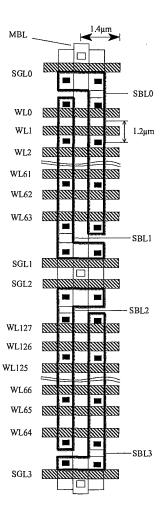

| V1.9                            | The NAND Flash Mass Storage Concept                                                      | 24       |  |

| 1.10                            | Embedded Flash Memories                                                                  | 26       |  |

| 1.11                            | The Future of Flash Memories                                                             | 27       |  |

|                                 | 1.11.1 Evolution of Flash Memory Technology                                              | 27       |  |

|                                 | 1.11.2 Non Volatile Memories Market Development                                          | 29       |  |

| Referenc                        | es                                                                                       | 33       |  |

|                                 | DUSTRY STANDARD FLASH MEMORY CELL<br>1, R. Bez                                           | 37       |  |

#### FLASH MEMORIES vi 2.1 Introduction 38 2.2 Basic Structure 42 2.3 Operating Conditions 46 2.3.1 Read 46 2.3.2 Program 47 2.3.3 Erase 53 2.4 Technology and Process 58 2.4.1 Isolation 60 2.4.2 Well and Channel Doping 61 2.4.3 Cell Structure Definition 64 Interlevel Dielectrics 2.4.4 68 2.4.5 Interconnections 70 2.4.6 Final Passivation 74 2.5 Yield and Reliability 74 2.5.1 Retention 75 2.5.2 Endurance 75 2.5.3 Reading Disturbs 76 2.5.4 Programming Disturbs 77 2.5.5 Erasing Disturbs 79 81 2.6 Scaling Issues References 83 BINARY AND MULTILEVEL FLASH CELLS 91 B. Eitan, A. Roy 3.1 Introduction to Flash Cell Design 91 3.2 Binary Flash Cells 93 3.2.1 Figures of Merit 93 Cell Design Complication Hierarchy from ROM to Flash 94 3.2.2 96 Basis for Flash Cells/Array Classification 3.2.3 98 3.2.4 Detailed Description of Flash Cells and Architectures 3.2.5 Scaling and Conclusions 131 3.3 Multilevel Flash Cells 137 3.3.1 Introduction to the Concept of Multilevel Flash 137 Multilevel Programming Mechanisms 3.3.2 138 Architectures for Multilevel Flash Memories 3.3.3 142 3.3.4 Scaling and Trade-Offs for Multilevel 146 147 References PHYSICAL ASPECTS OF CELL OPERATION AND RELIABILITY 153 L. Selmi, C. Fiegna 4.1 Introduction 153 155 4.2 Electronic Properties of Carriers and MOS Structures 4.2.1 Electrons in Crystals 155 4.2.2 Electrons as Classical Particles 156

|     |               | Contents                                                                                    | vii        |

|-----|---------------|---------------------------------------------------------------------------------------------|------------|

|     | 4.2.3         | Silicon                                                                                     | 157        |

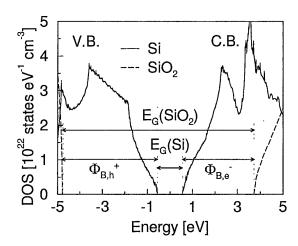

|     | 4.2.4         | Silicon Dioxide                                                                             | 157        |

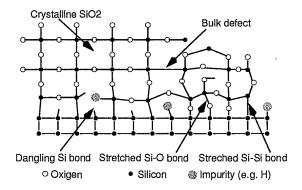

|     | 4.2.5         | Silicon - Silicon Dioxide Interface                                                         | 159        |

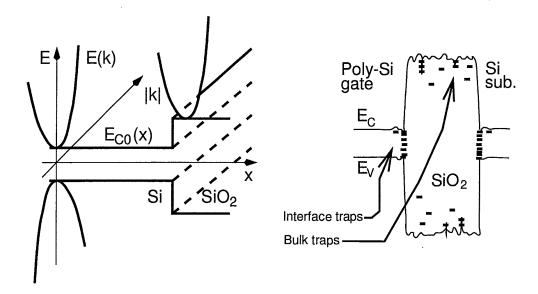

|     | 4.2.6         | Oxide and Interface Traps                                                                   | 159        |

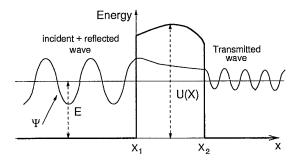

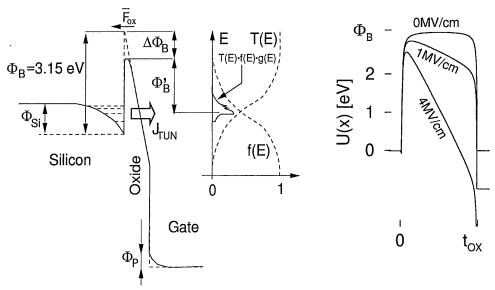

| 1.3 | Funda         | mentals of Tunneling Phenomena                                                              | 161        |

|     | 4.3.1         | Basic Concepts and the WKB Approximation                                                    | 161        |

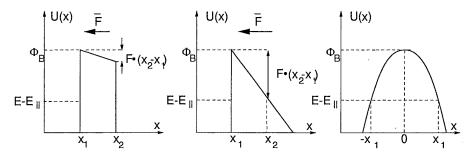

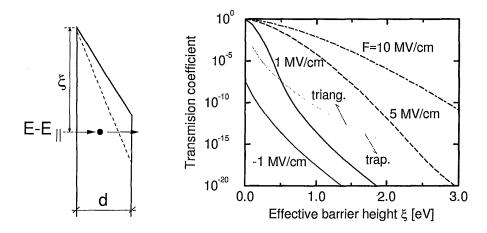

|     | 4.3.2         | Transmission Coefficient                                                                    | 162        |

|     | 4.3.3         | Tunneling Current                                                                           | 165        |

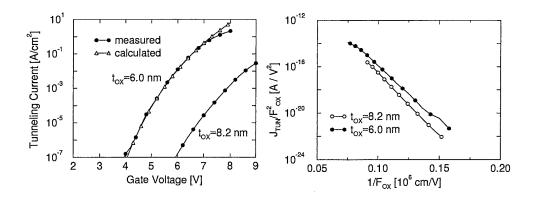

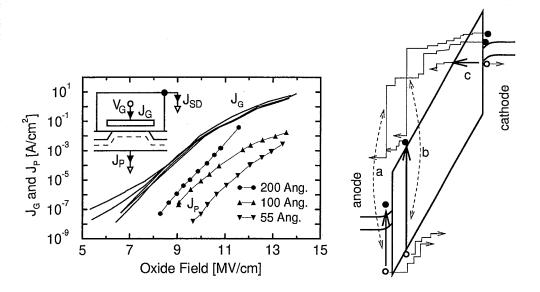

| 1.4 | Tunne         | ling Phenomena in MOSFETs                                                                   | 165        |

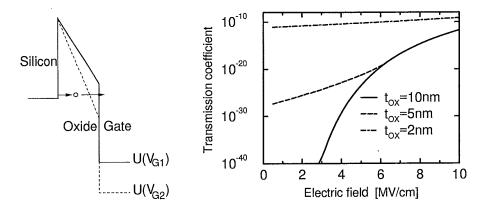

|     | 4.4.1         | Fowler-Nordheim and Direct Tunneling Through Gate Oxides                                    | 166        |

|     | 4.4.2         | Modeling the Tunnel Current of MOS Structures                                               | 167        |

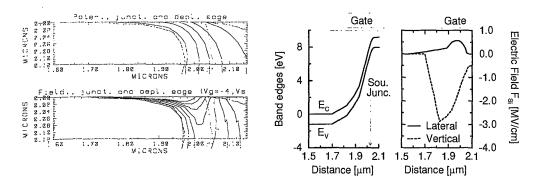

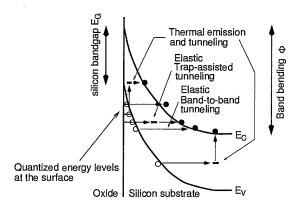

|     | 4.4.3         | Band-to-band and Trap-to-band Tunneling                                                     | 170        |

|     | 4.4.4         | Modeling the Band-to-band and Trap-to-band Tunneling Current                                | 174        |

| 1.5 | Funda         | mentals of Carrier Transport                                                                | 176        |

|     | 4.5.1         | •                                                                                           | 176        |

|     | 4.5.2         | The Boltzmann Transport Equation                                                            | 178        |

|     | 4.5.3         | Scattering                                                                                  | 180        |

|     | 4.5.4         | The Carrier Distribution in Thermal Equilibrium                                             | 181        |

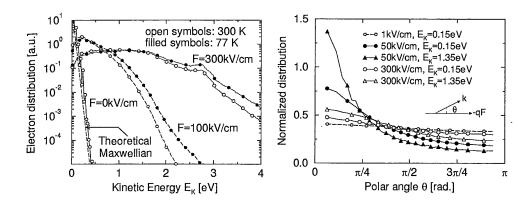

|     | 4.5.5         | Carrier Distributions in Homogeneous Electric Fields                                        | 182        |

|     | 4.5.6         | The Effective Temperature Model                                                             | 184        |

| 1.6 | Hot C         | arrier Effects in MOSFETs                                                                   | 185        |

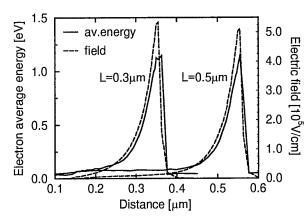

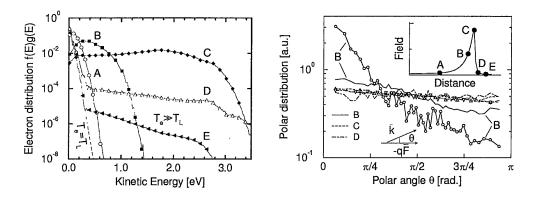

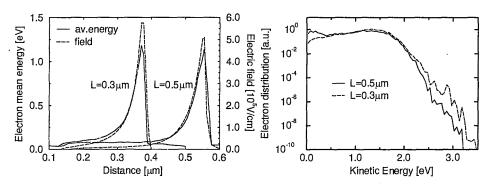

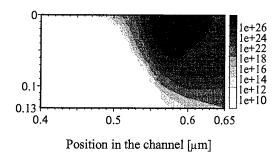

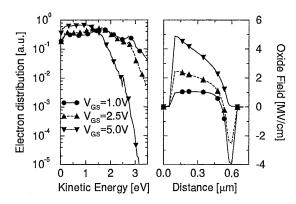

|     | 4.6.1         | Carrier Heating in MOSFETs and Flash Cells                                                  | 186        |

|     | 4.6.2         |                                                                                             | 189        |

|     | 4.6.3         | Simplified Models of Carrier Heating                                                        | 190        |

|     |               | 4.6.3.1 Average Energy                                                                      | 190        |

|     |               | 4.6.3.2 Carrier Distribution                                                                | 191        |

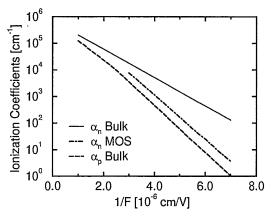

|     |               | Impact Ionization                                                                           | 192        |

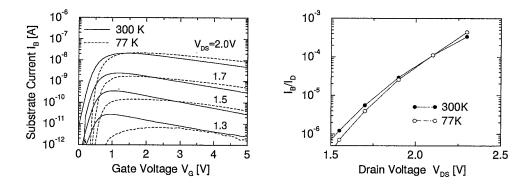

|     |               | Substrate Current                                                                           | 194        |

|     | 4.6.6         | J ==                                                                                        | 197        |

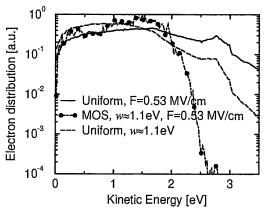

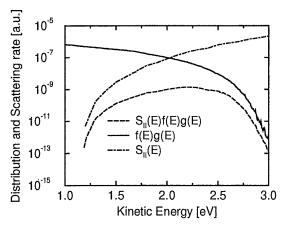

|     |               | 4.6.6.1 Distribution Function                                                               | 198        |

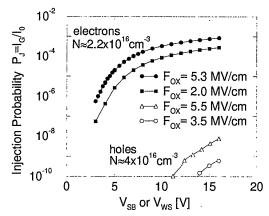

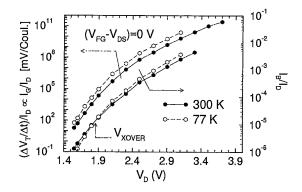

|     |               | 4.6.6.2 Injection Probability                                                               | 198        |

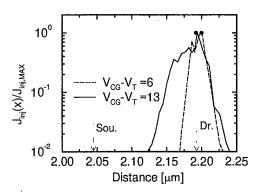

|     | 4.6.7         | Gate Current                                                                                | 199        |

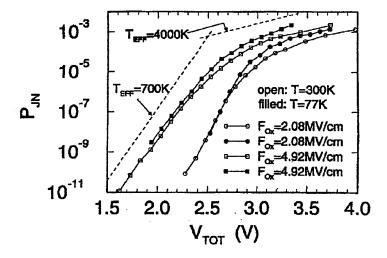

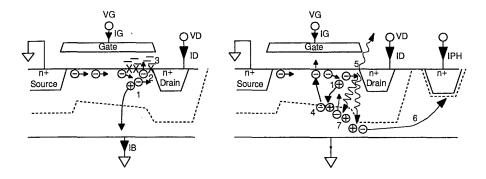

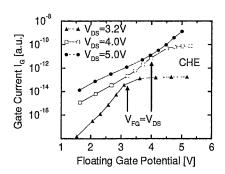

|     |               | 4.6.7.1 Channel Hot Electron Injection                                                      | 199        |

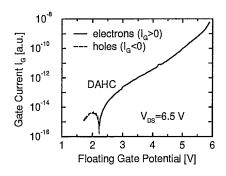

|     |               | 4.6.7.2 Drain Avalanche Hot Carrier Injection                                               | 201        |

|     |               | 4.6.7.3 Secondary Generated Hot Electron Injection 4.6.7.4 Substrate Hot Electron Injection | 202        |

|     |               |                                                                                             | 203<br>205 |

|     | 4.6.8         | 4.6.7.5 Implications for Device Operation  Hot Carrier Effects at Low Voltages              | 205        |

|     |               | <del>-</del>                                                                                |            |

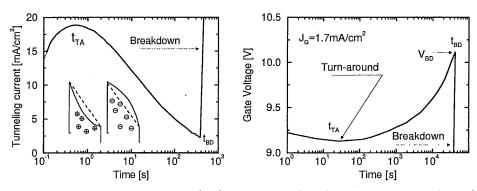

| 1.7 |               | Degradation due to High Field Stress                                                        | 207        |

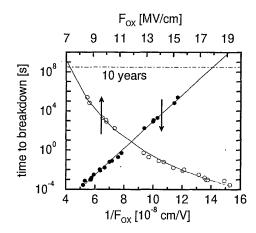

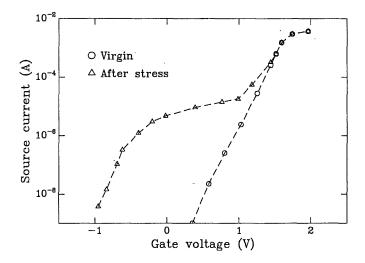

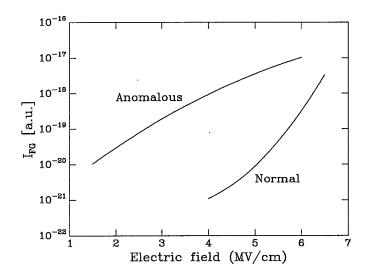

|     | 4.7.1         | Oxide Wear-out and SILC                                                                     | 207<br>210 |

|     | 4.7.2         | 4.7.1.1 Stress Induced Leakage Currents (SILC) Oxide Breakdown                              | 211        |

|     | 4.7.3         |                                                                                             | 213        |

|     | 4.1.3         | 4.7.3.1 SILC Lifetime Evaluation Model                                                      | 214        |

|     |               | 4.7.3.2 Breakdown Lifetime Evaluation Model                                                 | 215        |

| 1 0 | المناط -      |                                                                                             | 217        |

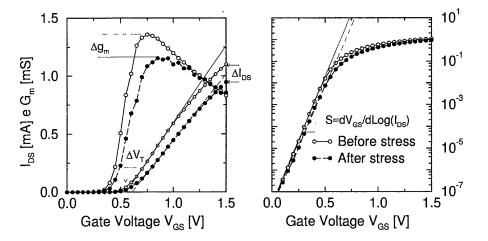

| ł.8 | 4.8.1         | and Interface Degradation due to Hot Carrier Injection Homogeneous Hot Carrier Degradation  | 217        |

|     | T,U, <u>1</u> | 4.8.1.1 n-channel Devices                                                                   | 217        |

|     | •             | noille in chainer before                                                                    | ~ 1        |

# viii FLASH MEMORIES

|         |                | 4.8.1.2 p-channel Devices                                                                                          | 218         |

|---------|----------------|--------------------------------------------------------------------------------------------------------------------|-------------|

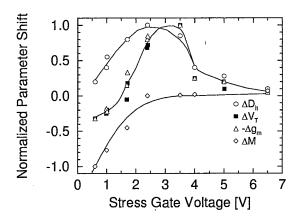

|         | 4.8.2          | Non-homogeneous Hot Carrier Degradation                                                                            | 218         |

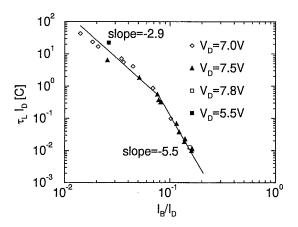

|         | 4.8.3          | Lifetime Evaluation Models                                                                                         | 221         |

| Referen | ces            |                                                                                                                    | 223         |

| 5       | DV ADA         | CHITECTURE AND RELATED ISSUES                                                                                      | 241         |

|         |                |                                                                                                                    |             |

|         |                | G. Campardo, S. Commodaro, S. Ghezzi, A. Ghilardelli, C. Golla, M. Micheloni, J. Mulatti, M. Zammattio, S. Zanardi | maccarrone, |

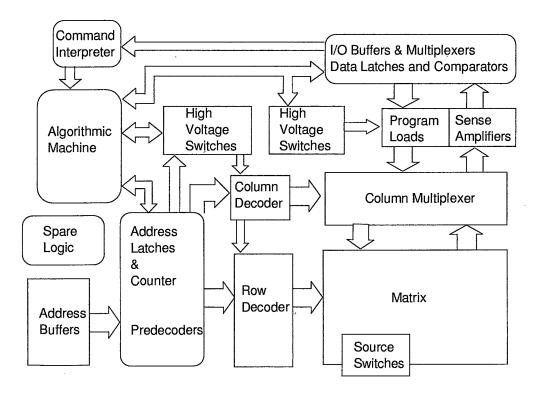

| 5.1     | Flash          | Architecture: General Overview                                                                                     | 241         |

|         | 5.1.1          | Flash Architecture Scenario                                                                                        | 242         |

| ^       | 5.1.2          | , , , , , , , , , , , , , , , , , , , ,                                                                            | 243         |

|         | 5.1.3          | · · · · · · · · · · · · · · · · · · ·                                                                              | 250         |

|         | 5.1.4          |                                                                                                                    | 253         |

|         |                | 5.1.4.1 Read Path Building Blocks Description                                                                      | 253         |

|         | **             | 5.1.4.2 Program Path Building Blocks Description                                                                   | 256         |

|         |                | 5.1.4.3 Erase Path Building Blocks Description                                                                     | 256         |

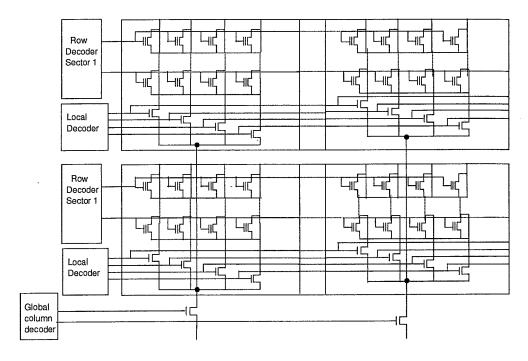

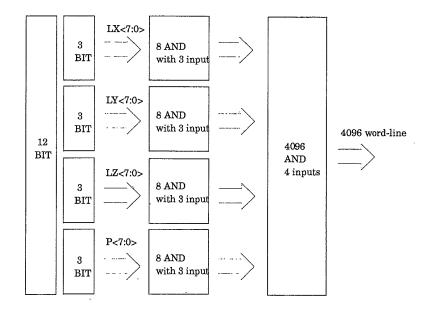

| 5.2     | Read           | Path: Decoding                                                                                                     | 257         |

|         | 5.2.1          | Predecoding                                                                                                        | 259         |

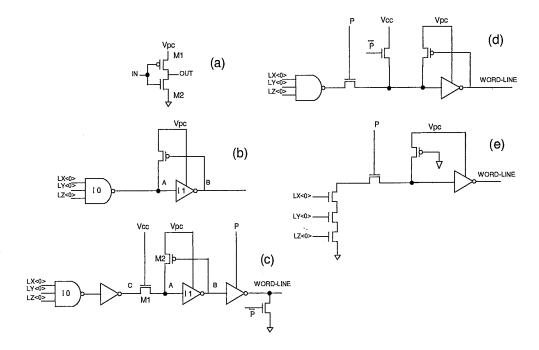

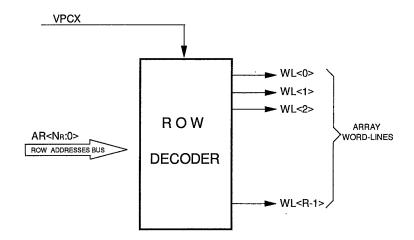

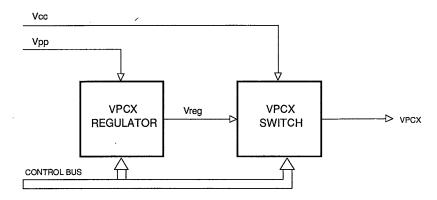

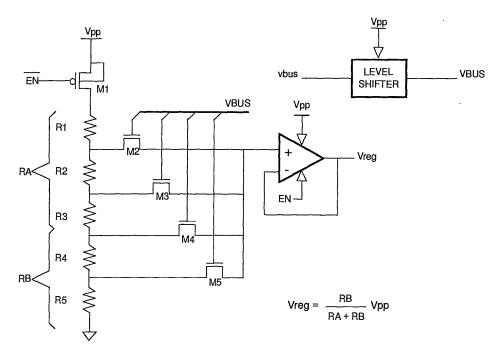

|         | 5.2.2          | Row Decoder                                                                                                        | 259         |

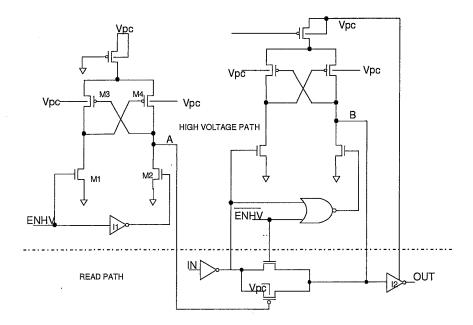

|         | 5.2.3          | •                                                                                                                  | 263         |

|         | 5.2.4          |                                                                                                                    | 264         |

|         |                | Low $V_{ m CC}$ Problems                                                                                           | 266         |

|         | 5.2.6          |                                                                                                                    | 267         |

|         | 5.2.7          | A New Boost Approach: Miniboost                                                                                    | 268         |

| 5.3     | Read           | Path: Input and Output Buffers                                                                                     | 270         |

|         | 5.3.1          |                                                                                                                    | 270         |

|         | 5.3.2          | Output Buffer                                                                                                      | 272         |

|         | 5.3.3          | Noise Issues                                                                                                       | 275         |

|         | 5.3.4          | High Voltage Tolerance                                                                                             | 277         |

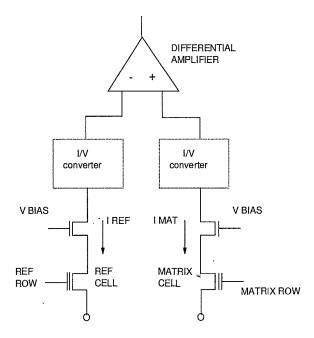

| 5.4     | Read           | Path: Sensing Techniques                                                                                           | 280         |

|         | 5.4.1          | Sensing Techniques: An Overview                                                                                    | 281         |

|         | 5.4.2          | Differential Sensing Technique                                                                                     | 285         |

|         | 5.4.3          | Differential Sensing Technique with Offset Current                                                                 | 289         |

|         | 5.4.4          | Differential Semi-Parallel Sensing Technique                                                                       | 293         |

|         | 5.4.5          | Reading Speed-up Techniques                                                                                        | 295         |

|         | 5.4.6          | From EPROM to Flash                                                                                                | 304         |

|         | 5.4.7          |                                                                                                                    | 305<br>308  |

|         | 5.4.8          | Low Voltage Flash Read<br>Reference Problems                                                                       | 312         |

|         | 5.4.9          |                                                                                                                    |             |

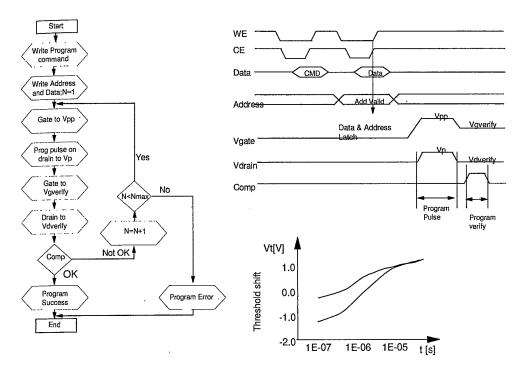

| 5.5     | _              | am Operation Circuitry                                                                                             | 314         |

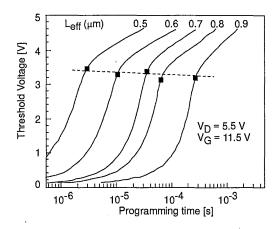

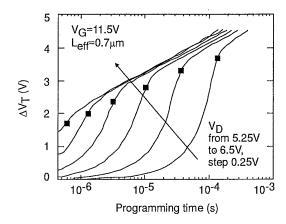

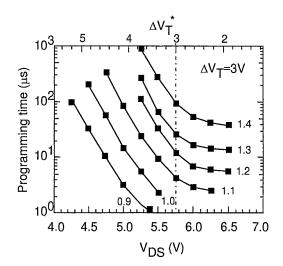

|         | 5.5.1          | Cell Programming Voltages: Optimum Choice                                                                          | 314<br>315  |

|         | 5.5.2<br>5.5.3 | Typical Program Path  Drain Voltage Regulation: Principles and Basic Circuits                                      | 315         |

|         |                | Drain Voltage Regulation: Principles and Basic Circuits Gate Voltage Regulation Fundamentals                       | 320         |

|         | 5.5.4          | •                                                                                                                  |             |

| 5.6     |                | Operation Circuitry                                                                                                | 327         |

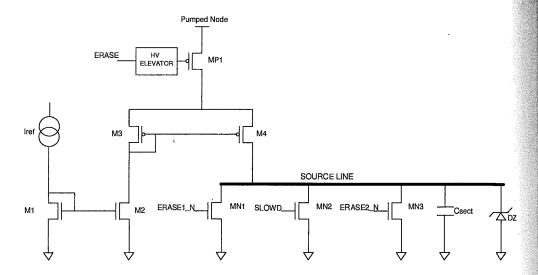

|         | 1.0.0          | Double Supply Voltage Approach                                                                                     | 329         |

|         |                                                                                                                                                                                      | Contents | 1X                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------|

|         | 5.6.1.1 Source Erase Circuitry 5.6.1.2 Slow Discharge of Critical Nodes 5.6.2 Single Supply Voltage Approach 5.6.2.1 Charge Pumping 5.6.2.2 Voltage Regulators 5.6.2.3 Source Switch |          | 329<br>330<br>331<br>332<br>335<br>336 |

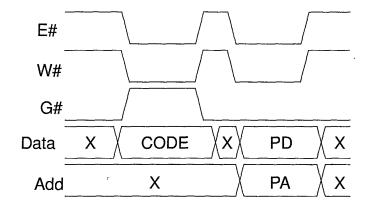

| 5.7     | Control Logic and Embedded Algorithms 5.7.1 Logic Architecture 5.7.2 Embedded Algorithms 5.7.2.1 Sequencer (Pseudo-Microcontroller) 5.7.2.2 Finite State Machine                     |          | 337<br>339<br>343<br>344<br>344        |

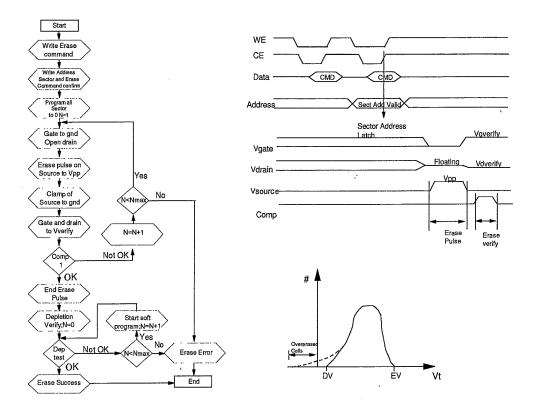

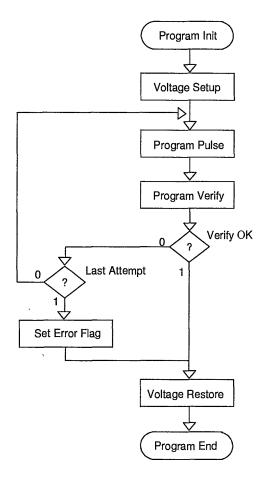

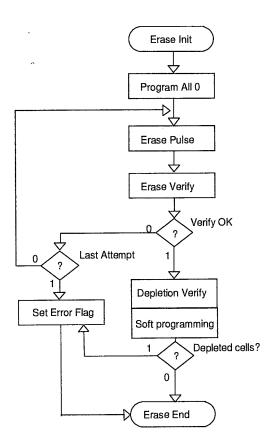

|         | <ul> <li>5.7.3 Program Flow</li> <li>5.7.4 Erase Flow</li> <li>5.7.5 Erase Suspend - Erase Resume</li> <li>5.7.6 Testability Issues</li> </ul>                                       |          | 344<br>346<br>348<br>348               |

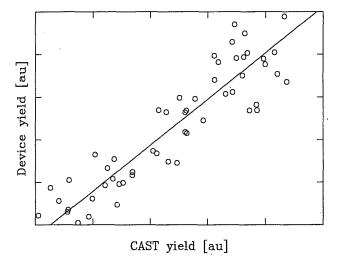

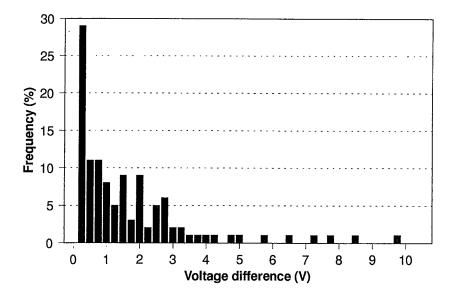

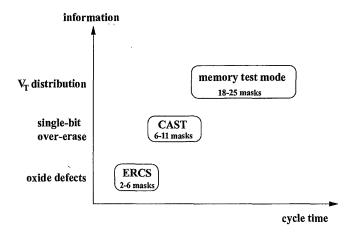

| 5.8     | Redundancy and Error Correction Codes 5.8.1 The Yield 5.8.2 Static Redundancy 5.8.3 Wafer Yield 5.8.4 A Real Case 5.8.5 Error Correction Codes                                       |          | 350<br>350<br>352<br>353<br>354<br>356 |

|         | LEVEL FLASH MEMORIES                                                                                                                                                                 |          | 361                                    |

|         | illi, M. Lanzoni. A. Manstretta, B. Riccò                                                                                                                                            |          | 200                                    |

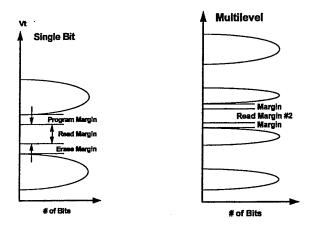

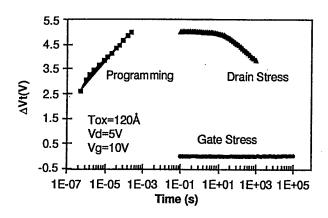

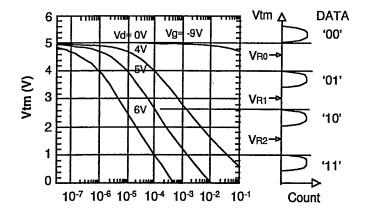

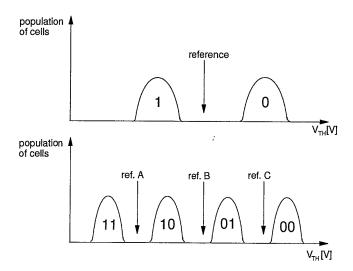

| 6.1     | Introduction 6.1.1 The Multilevel Approach 6.1.2 Basic Issues for ML Storage                                                                                                         |          | 362<br>362<br>364                      |

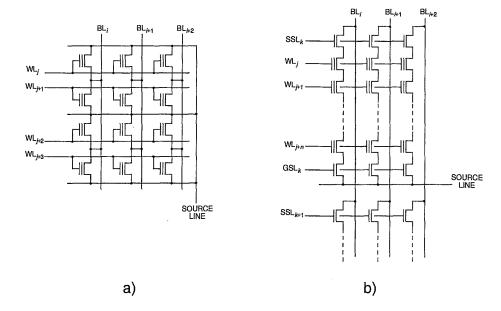

| 6.2     | Array Architectures for Multilevel Flash Memories 6.2.1 NOR Architecture with CHE Programming 6.2.2 NOR Architecture with FN Programming 6.2.3 NAND Architecture                     |          | 368<br>369<br>371<br>371               |

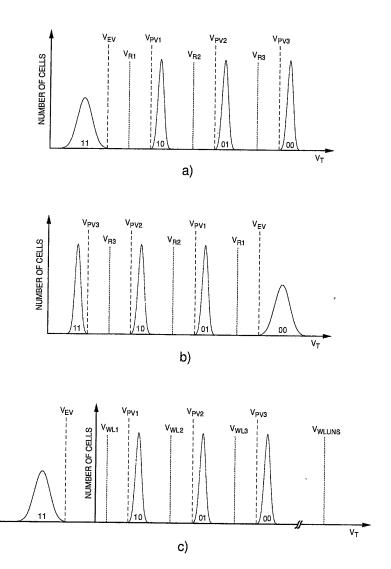

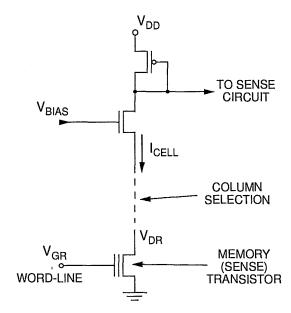

| 6.3     | Multilevel Sensing 6.3.1 Signal Production and Recognition 6.3.2 Sensing Schemes                                                                                                     |          | 373<br>374<br>376                      |

| 6.4     | Multilevel Programming 6.4.1 Program-and-Verify Approaches 6.4.2 Self-Controlled Approaches                                                                                          | -        | 382<br>384<br>387                      |

| 6.5     | Conclusions                                                                                                                                                                          |          | 389                                    |

| Referen | ices                                                                                                                                                                                 |          | 391                                    |

|         | MEMORY RELIABILITY  pelletti, A. Modelli                                                                                                                                             |          | 399                                    |

| 7.1     | Introduction                                                                                                                                                                         |          | 399                                    |

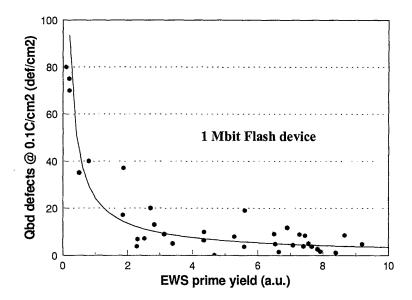

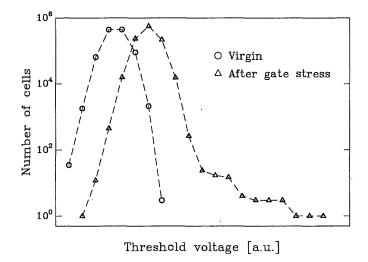

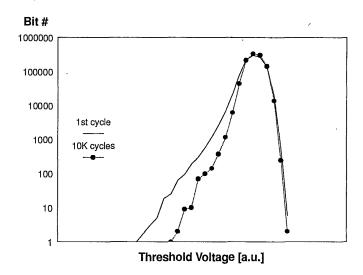

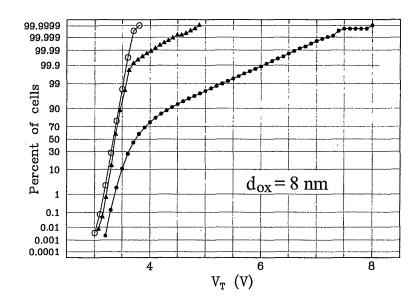

| 7.2     | Memory Array $V_t$ Distributions and Tunnel Oxide "Defects"                                                                                                                          |          | 401                                    |

| 7.3     | Main Yield and Reliability Issues                                                                                                                                                    |          | 409                                    |

|         |         | 7.3.1 Over-Erasing                                                                         | 409        |

|---------|---------|--------------------------------------------------------------------------------------------|------------|

|         |         | 7.3.2 Program Disturbs                                                                     | 411        |

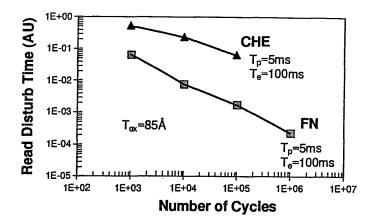

|         |         | 7.3.3 Read Disturb                                                                         | 414        |

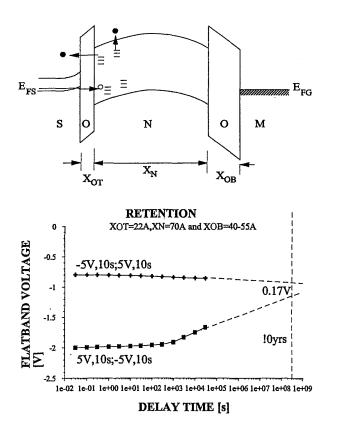

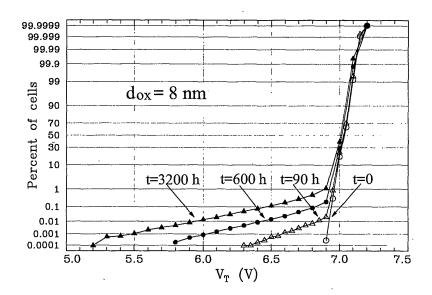

|         |         | 7.3.4 Program/Erase Endurance 7.3.5 Data Retention                                         | 415<br>416 |

|         | 7 1     | Testing for Reliability                                                                    | 417        |

|         |         | Failure Modes Induced by Program/Erase Cycling                                             | 418        |

|         | 7.5     | 7.5.1 Memory Cell Intrinsic Endurance                                                      | 418        |

|         |         | 7.5.2 The Behavior of Tail Bits                                                            | 422        |

|         |         | 7.5.3 Single Bit Failure Mechanisms                                                        | 422        |

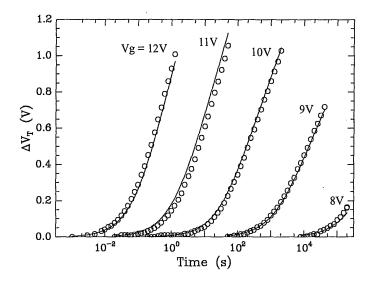

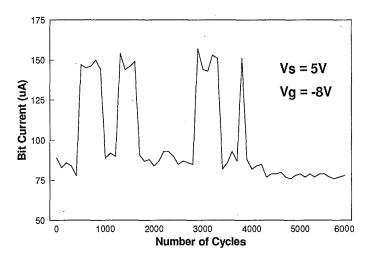

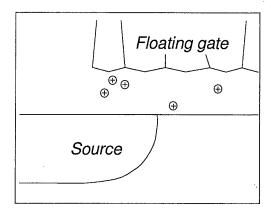

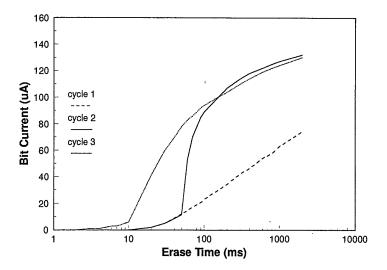

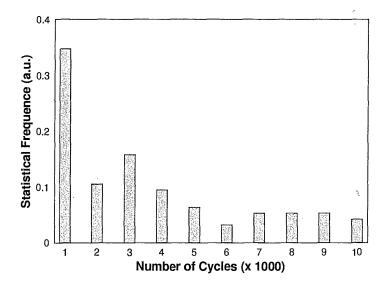

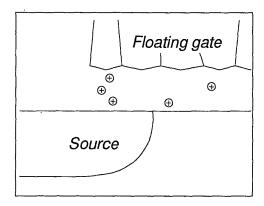

|         |         | 7.5.3.1 The Erratic Erase Phenomenon                                                       | 423        |

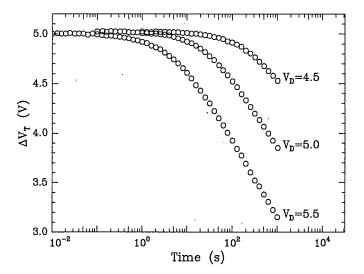

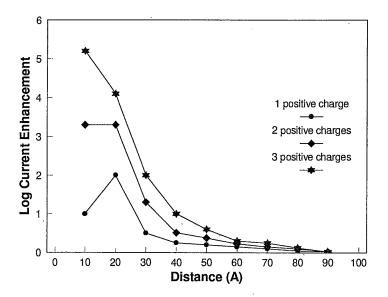

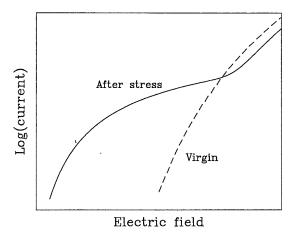

|         |         | 7.5.3.2 Single Bit Data Loss after Program/Erase Cycling                                   | 426        |

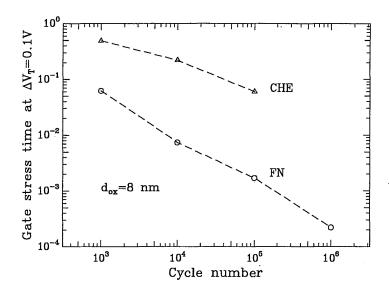

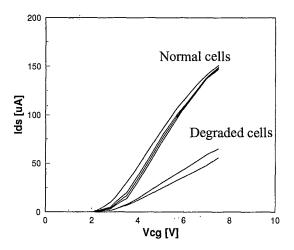

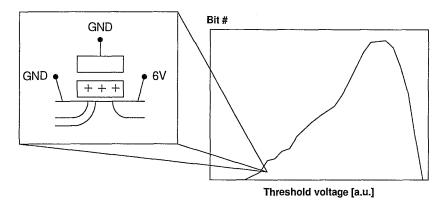

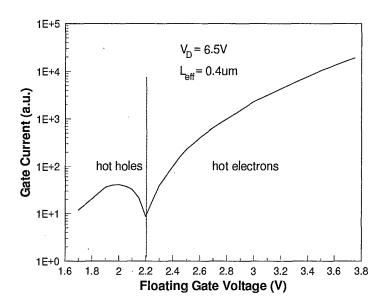

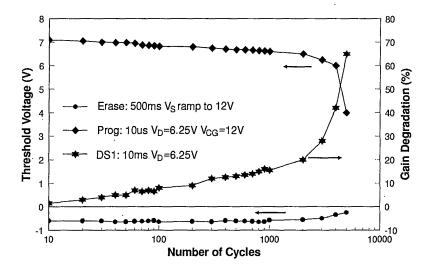

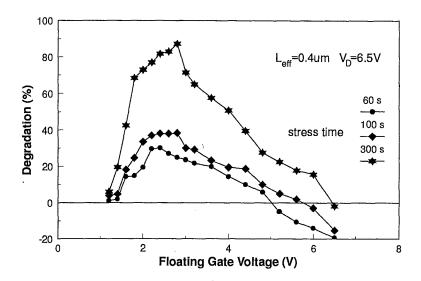

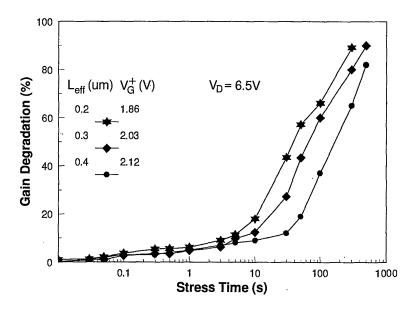

|         |         | 7.5.3.3 Gain Degradation                                                                   | 430        |

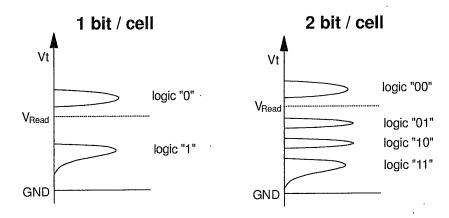

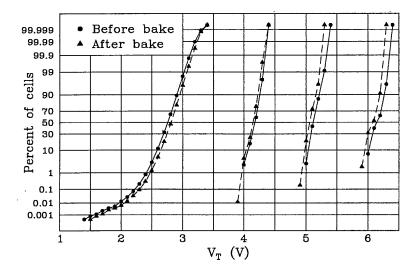

|         | 7.6     | Multilevel Storage Reliability                                                             | 436        |

|         | 7.7     | Conclusion                                                                                 | 439        |

| _       |         |                                                                                            | 420        |

| Κe      | eferenc | ces <sub>,</sub>                                                                           | 439        |

| 3<br>E1 | ۸CH     | MEMORY TESTING                                                                             | 443        |

|         | Casag   |                                                                                            | 773        |

|         |         | Introduction                                                                               | 443        |

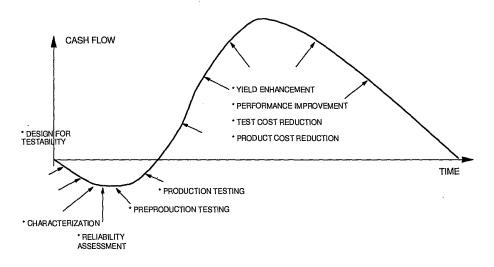

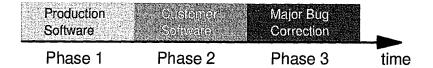

|         | 0.1     | 8.1.1 Impact of Testing on Product Cost                                                    | 443        |

|         |         | 8.1.2 Impact on Product Life Cycle                                                         | 444        |

|         |         | 8.1.3 Objectives of Production Testing                                                     | 445        |

|         |         | 8.1.4 Testing Versus Quality and Reliability                                               | 445        |

|         | 8.2     | Flash Testing Aspects                                                                      | 446        |

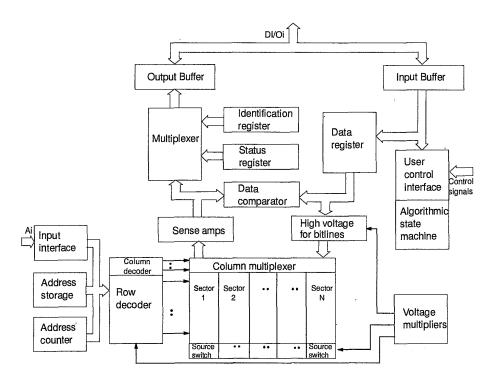

|         |         | 8.2.1 Flash Functional Model                                                               | 446        |

|         |         | 8.2.2 Oxide Stress in a Flash                                                              | 446        |

|         |         | 8.2.3 Flash Testing Aspects                                                                | 447        |

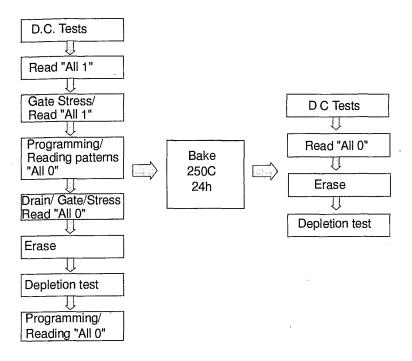

|         |         | 8.2.4 Conceptual Test Flow                                                                 | 448        |

|         | 8.3     | Flash Testability Tools                                                                    | 450        |

|         |         | 8.3.1 Focus on Cell and Technology                                                         | 450        |

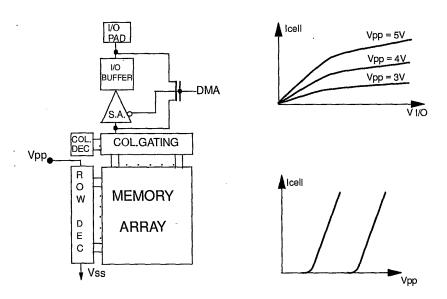

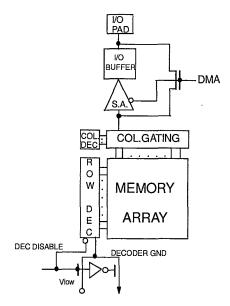

|         |         | 8.3.1.1 Direct Memory Access                                                               | 451        |

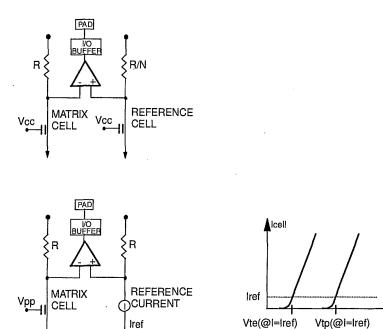

|         |         | 8.3.1.2 Vt Measurement                                                                     | 452        |

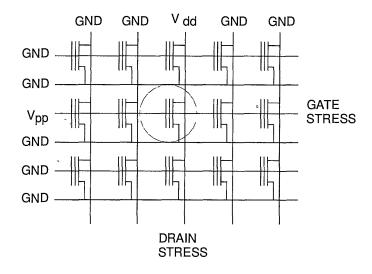

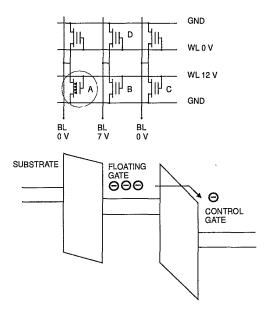

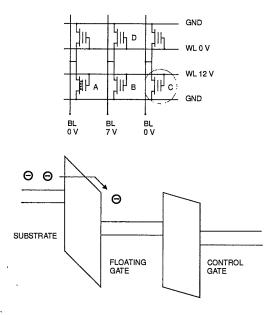

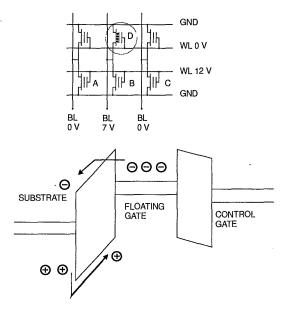

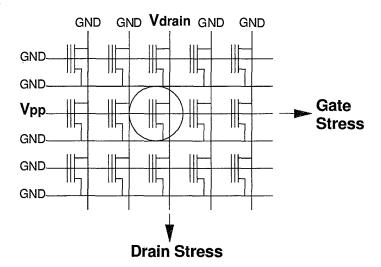

|         |         | 8.3.1.3 Stress Modes                                                                       | 454        |

|         |         | 8.3.1.4 Depletion/Low-Vt Test                                                              | 455        |

|         |         | 8.3.2 Focus on Test Productivity                                                           | 457        |

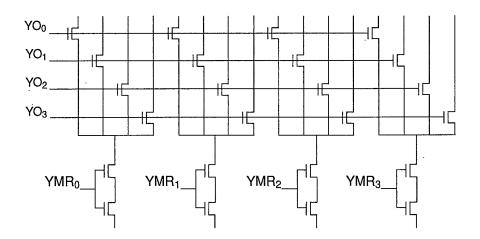

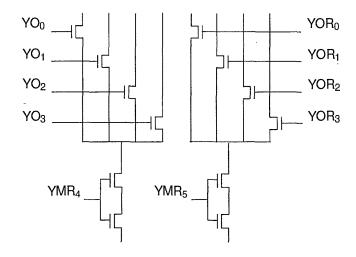

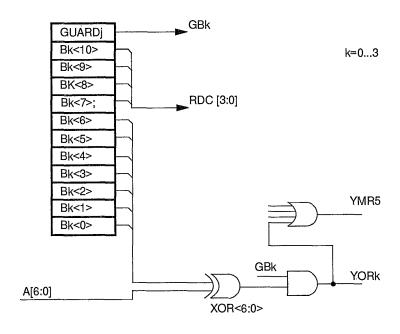

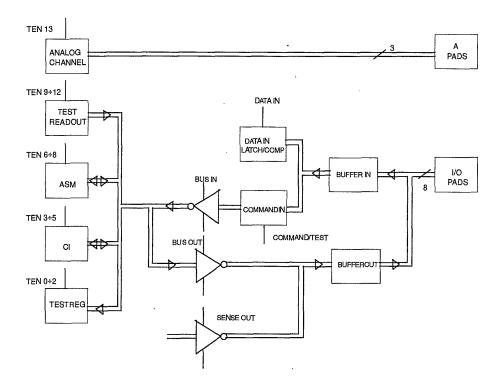

|         |         | <ul><li>8.3.3 Focus on Design</li><li>8.3.4 Flash Design Testability: an Example</li></ul> | 457<br>458 |

|         | 8.4     | Fault Repairing                                                                            | 460        |

|         | 0.4     | 8.4.1 Error Correction                                                                     | 462        |

|         |         | 8.4.2 Redundancy                                                                           | 462        |

|         |         | 8.4.2.1 Diagnosis and Repairing                                                            | 464        |

|         |         | 8.4.2.2 Testability Tools for Redundancy                                                   | 465        |

|         | 8.5     | Production Testing                                                                         | 466        |

|         |         | 8.5.1 DC Tests                                                                             | 467        |

|         |           | Cor                                                                                                                     | ${ m ntents} { m ~xi}$ |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------------|------------------------|

|         | 8.5.2     | Functional Testing                                                                                                      | 468                    |

|         | 8.5.3     | AC Read/Command Interface                                                                                               | 469                    |

|         | 8.5.4     | Erase/Program Performance; Endurance                                                                                    | 470                    |

|         | 8.5.5     | Reliability                                                                                                             | 470                    |

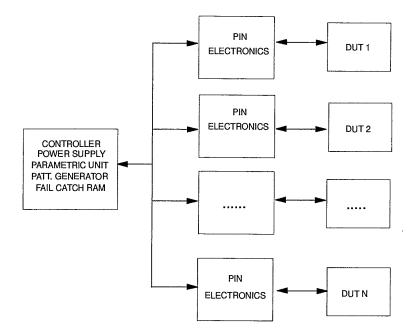

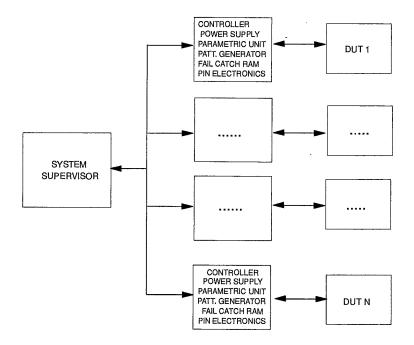

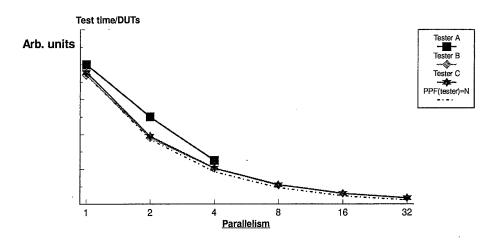

| 8.6     | Test F    | Productivity                                                                                                            | 470                    |

|         | 8.6.1     |                                                                                                                         | 471                    |

|         | 8.6.2     | Parallel Testing Final Test                                                                                             | 473                    |

|         | 8.6.3     | Parallel Testing at EWS                                                                                                 | 473                    |

| 8.7     | Produ     | ct Characterization                                                                                                     | 474                    |

| 8.8     | Concl     | usions                                                                                                                  | 478                    |

| Referen | ices      |                                                                                                                         | 479                    |

|         |           | RIES: MARKET, MARKETING AND ECONOMIC CHALLENGE Bergé, with contributions by C. Kunkel, G. Moy, A. Damiano, R. Féluction |                        |

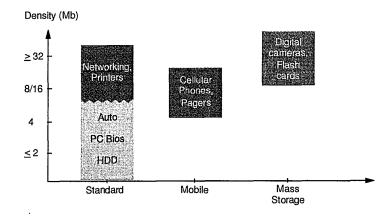

| 9.2     |           | et Segmentations                                                                                                        | 483                    |

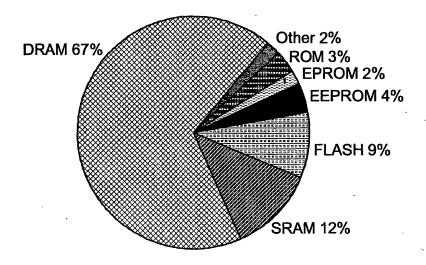

| J       | 9.2.1     | Application Segments and Subsegments                                                                                    | 485                    |

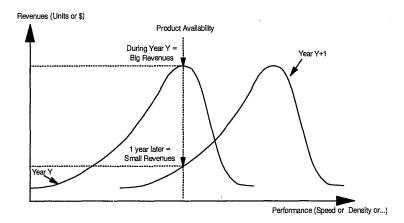

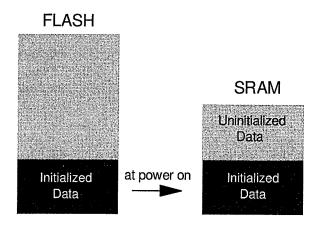

|         | 9.2.2     | Technology, Performances and Applications                                                                               | 488                    |

|         | 9.2.3     |                                                                                                                         | 492                    |

|         | 9.2.4     | Commodity or Non-Commodity?                                                                                             | 493                    |

| 9.3     | Custo     | mer/Supplier Relationship                                                                                               | 495                    |

| 9.4     | , , , , , |                                                                                                                         |                        |

| 9.5     | ·         |                                                                                                                         |                        |

| 9.6     |           | ations More in Detail                                                                                                   | 499<br>500             |

| 5.0     | 9.6.1     | Survey                                                                                                                  | 500                    |

|         | 9.6.2     | Flash in Mobile Phones and Terminals                                                                                    | 503                    |

|         | 9.6.3     | Flash in the BIOS                                                                                                       | 508                    |

|         | 9.6.4     | Flash in Automotive                                                                                                     | 515                    |

| 9.7     | Conclu    | usions                                                                                                                  | 525                    |

| Referen | ces       |                                                                                                                         | 526                    |

# 1 FLASH MEMORIES: AN OVERVIEW

Piero Olivo<sup>1</sup>, Enrico Zanoni<sup>2</sup>

<sup>1</sup> Dipartimento di Ingegneria, Università di Ferrara Via Saragat 1, 44100 Ferrara, Italy olivo@ing.unife.it

Dipartimento di Elettronica e Informatica, Università di Padova Via Gradenigo 6/A, 35131 Padova, Italy zanoni@del.unipd.it

# 1.1 ROLE OF NON VOLATILE MEMORIES IN MICROELECTRONIC SYSTEMS AND IN SEMICONDUCTOR MARKET

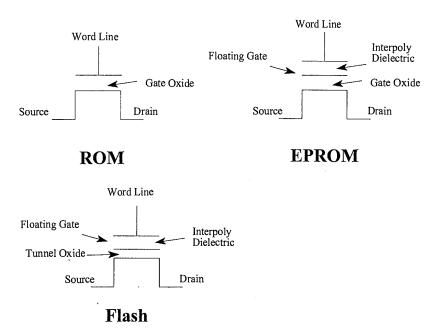

Solid-state memory devices which retain information once the power supply is switched off are called "nonvolatile" memories. For instance, using standard digital technology, a nonvolatile memory can be implemented by writing permanently the data in the memory array during manufacturing (mask-programmed Read Only Memories, ROM). As an alternative, the user can program the information by blowing fusible links or antifuses, thus changing permanently the cell content (i.e. obtaining a Programmable ROM or PROM). In both cases, the memory array can not be erased, thus making these solutions viable only for a limited number of applications.

In the course of the years, several technological solutions have been developed, which have led to the availability of non-volatile memories which can be electrically written and erased. Erasable Programmable Read Only Memories (EPROM) can be electrically programmed, but have to be removed and exposed to ultra-violet (UV) radiation for about 20 minutes in order to be

#### 2

erased. Electrically Erasable Programmable ROMs (EEPROM) are electrically erasable and programmable in-system, byte by byte, but use larger areas than EPROMs, and have therefore higher costs and lower densities.

System designers have long dreamt of a non volatile memory which could be electrically erased and programmed in-system, offering at the same time very high-density and low cost-per-bit, random access, bit alterability, short read/write times and cycle times, excellent reliability. In most of the current system applications, these features should be also combined with low power consumption and single, low-voltage, power supply operation. If available, a solid-state memory technology having these characteristics would not only become dominant in the nonvolatile memory market, but could also make possible an unprecedented design flexibility, replacing all other kinds of memory in many applications. At the moment, this "ideal" memory chip has still to be invented.

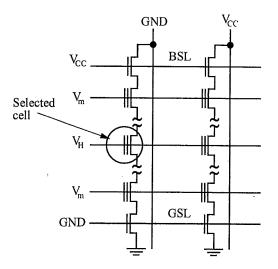

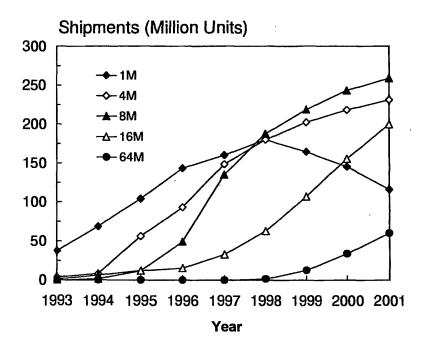

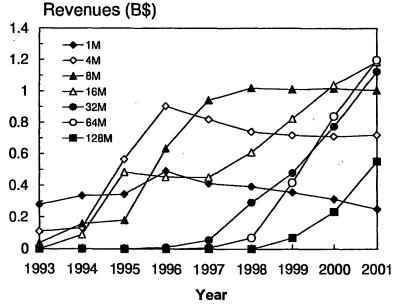

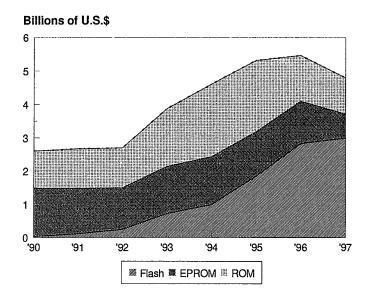

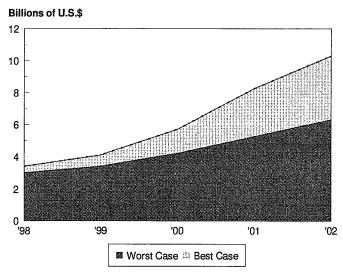

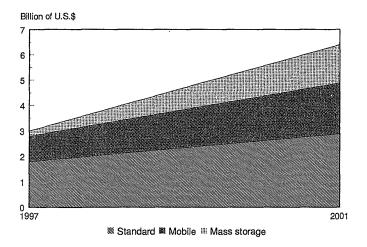

The Flash memory technology has many of the characteristics of the "ideal" memory concept and is consequently considered as a driver for the semiconductor industry in the next decade. In 1996 it was forecasted that nonvolatile memories are going to be 12% of the worldwide memory market by the year 2000; Flash memories will occupy 50% of this nonvolatile memory market. Currently (1998), the Flash memory market is approximately \$2.5B [1].

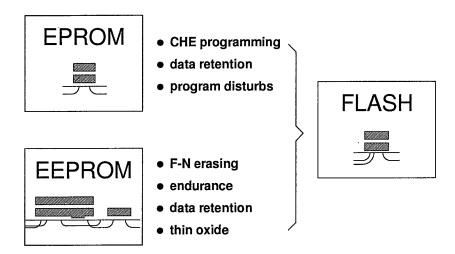

Flash memories are non volatile memories in which a single cell can be electrically programmed and a large number of cells – called a block, sector or page – are electrically erasable at the same time. The word "flash" itself is related to the fact that since the whole memory can be erased at once, erase times can be very fast. Flash technology combines the high density of the UV EPROM (it has basically a single transistor cell like EPROMs) with electrical in-system erasability of EEPROMs.

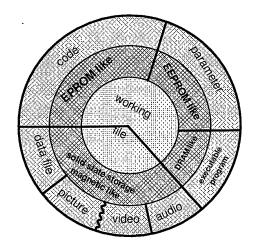

There are two major applications for Flash memories that should be pointed out. One is the possibility of nonvolatile memory integration in logic systems – mainly, but not only, microprocessors – to allow software updates, store identification codes, reconfigure the system on the field, or simply have smart cards. The other application is to create storing elements, like memory boards or solid-state hard disks, made by Flash memory arrays which are configured to create large-size memories to compete with miniaturized hard disks. Flash solid-state disks are very useful for portable applications, since they have small dimensions, low power consumption, and no mobile parts, therefore being more robust.

Flash memories also combine the capability of nonvolatile storage with an access time comparable to Dynamic Random Access Memories (DRAM), which allows direct execution of microcodes. Many programs can be stored in Flash chips, without being continuously loaded and unloaded from the hard disk, and directly executed. Moreover, the realization of new generations of Flash memo-

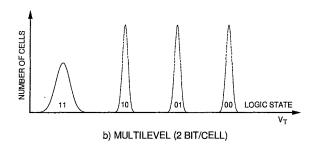

ries that can be erased by blocks of different sizes, emulating EEPROMs in some applications, and with a single power supply, widens the field of applicability for Flash memories and encourages new uses. Besides voice recorders, answering machines and portable audio guides, Flash memories find wide applications in personal computers and peripherals, automotive engine control units, digital cordless telephones, and in emerging applications, such as personal digital assistants (PDAs), digital set-top boxes, digital still cameras, portable medical diagnostic systems and many others, also taking advantage of the recent possibility of storing more bits on a single cell (in "multilevel" Flash memories).

In this introduction the reader will find a description of the basic concepts and characteristics which have led to the development of Flash memories. The basic cell structures, device physics, memory chip architecture, reliability and testing issues of Flash memories will be analyzed in details in the following Chapters.

#### 1.2 EVOLUTION OF NON-VOLATILE MEMORIES

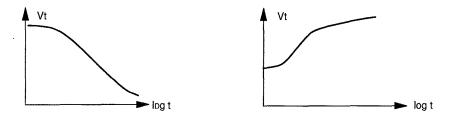

Two are the parameters describing how "good" and reliable a nonvolatile memory cell is: endurance (capability of maintaining the stored information after erase/program/read cycling) and retention (capability of keeping the stored information in time). The need of information modification, however, always contrasts with that of a good data retention; cells with different characteristics have different applications according to the relevance of some device functional parameters (absorbed power, programming/erasing speed and selectivity, capacity...).

To have a memory cell which can commute from one state to the other, and which can store the information independently of external conditions, the storing element needs to be a device whose conductivity can be changed in a non-destructive way.

One solution is to have a transistor with the threshold voltage which can change repetitively from a high to a low state, corresponding to the two states of the memory cell. Following the P1005 IEEE Draft Standard for Definitions, Symbols and Characterization of Floating Gate Memory Arrays [2], the low-and the high-threshold states in Flash memories are generally called as "erased" and "programmed", respectively. It must be noticed, however, that this standard definition is not followed for all kinds of cells; for some implementations, it is common practice to distinguish the "program" and "erase" operations on the basis of the memory array organization; as a consequence, "programmed" does not always correspond to "high threshold". Deviations from the standard definitions will be pointed out in Chapter 3, which describes advanced Flash memory cells.

The threshold voltage  $V_T$  of a MOS transistor can be written as:

$$V_T = K - Q/Cox (1.1)$$

where K is a constant that depends on the gate and substrate material, on the channel doping, and gate oxide thickness, Q is the charge weighted with respect to its position in the gate oxide, and Cox is the gate oxide capacitance. As can be seen, the threshold voltage of a MOS memory cell can be altered by changing the amount of charge present between the gate and the channel, i.e. by changing Q/Cox. Two are the most common solutions used to store charge:

- 1. in traps which are present in the insulator or at the interface between two dielectric materials. The most commonly used interface is the silicon oxide/nitride interface. Devices obtained in this way are called MNOS (Metal-Nitride-Oxide-Silicon) cells;

- 2. in a conductive material layer between the gate and the channel and completely surrounded by insulator; this is the "floating gate" (FG) device.

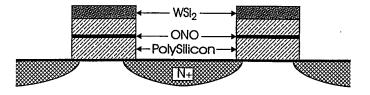

Because of their lower endurance and retention, MNOS devices are used only in specific applications (such as in military, thanks to their radiation hardness). Their modern counterpart, the SONOS (Silicon - Oxide - Nitride - Oxide - Silicon) nonvolatile memory technology, is still based on electron trapping in the nitride layer, but exploits the achievement of a better control of the processing of the ONO (Oxide-Nitride-Oxide) layer. By using a relatively thin (5-10 nm) dielectric layer low programming voltages (5 to 10 V) can be achieved. Despite these improvements, however, nonvolatile memories based on charge trapping are still a very low fraction of the total nonvolatile memory production.

Floating gate devices, on the contrary, are at the basis of every modern nonvolatile memory, and are used in particular for Flash applications.

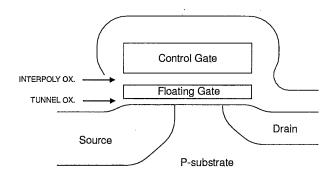

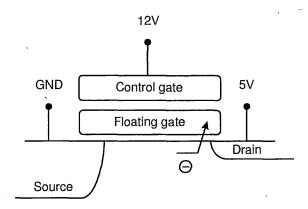

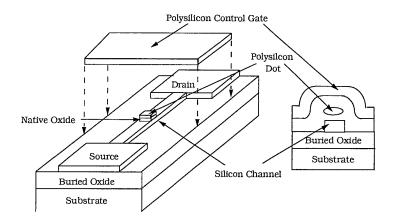

# 1.3 THE FLOATING GATE DEVICE

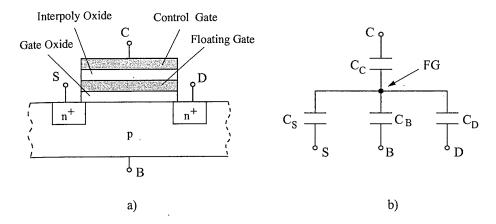

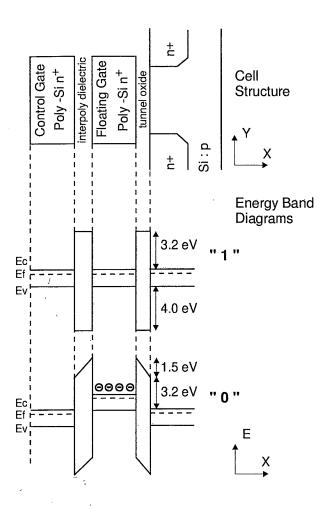

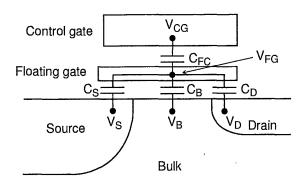

The schematic cross section of a generic floating gate device is shown in Fig. 1.1a: the upper gate is the control gate, while the lower one, completely surrounded by dielectric, is the floating gate. The basic concepts and the functionality of a FG device can be easily understood by determining the relationship between the FG potential, that physically controls the channel conductivity, and the control gate potential, controlled by external circuitry. This can be done by using the simple electrical model of Fig. 1.1b, where  $C_C$ ,  $C_S$ ,  $C_D$  and  $C_B$  are the capacitance between FG and control gate, source, drain and bulk regions, respectively. The FG potential  $(V_F)$  is:

$$V_F = \frac{C_C}{C_T} V_C + \frac{C_S}{C_T} V_S + \frac{C_D}{C_T} V_D + \frac{C_B}{C_T} V_B + \frac{Q}{C_T}$$

(1.2)

**Figure 1.1** a) Schematic cross section of a generic floating gate device; b) electrical model of a floating gate device (junction capacitances are neglected).

where  $V_C$ ,  $V_S$ ,  $V_D$ , and  $V_B$  are the control gate, drain, source and bulk potentials, respectively; Q is the charge within the FG, while  $C_T = C_C + C_S + C_D + C_B$  is the total capacitance.

Eq. (1.2) shows that the FG potential does not depend on the control gate voltage only, but also on source, drain and bulk potentials. If the source and bulk are both grounded and all potentials are referred to the source, (1.2) can be rearranged as

$$V_{FS} = \frac{C_C}{C_T} V_{CS} + \frac{C_D}{C_T} V_{DS} + \frac{Q}{C_T} . {1.3}$$

By defining  $\alpha_C = C_C/C_T$  as the "coupling factor" and  $f = C_D/C_C$ , (1.3) can be written as

$$V_{FS} = \alpha_C \left( V_{CS} + f V_{DS} + \frac{Q}{C_C} \right) . \tag{1.4}$$

The characteristics of a FG device depend on the threshold voltage, that is the potential  $(V_{T_{FS}})$  that must be applied to the FG (with  $V_{DS}=0$ ) to reach the inversion of the surface population. Since the floating gate cannot be accessed,  $V_{T_{FS}}$  is applied to the floating gate when a suitable voltage  $(V_{T_{CS}})$ , to be derived from (1.4), is applied to the control gate:

$$V_{T_{CS}} = \frac{1}{\alpha_C} V_{T_{FS}} - \frac{Q}{C_C} \ . \tag{1.5}$$

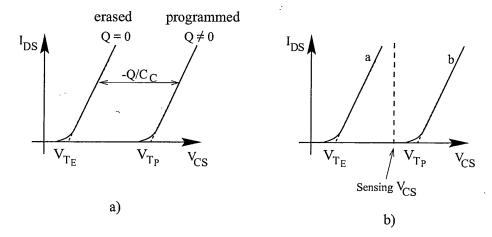

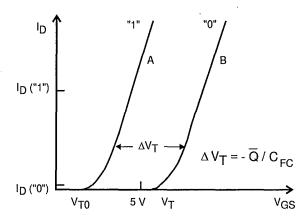

Figure 1.2 a) I-V trans-characteristics of a FG device for two different values of charge stored within the FG (Q=0, and Q<0), denoting two different states, respectively: erased and programmed; b) reading operation of a FG device: a suitable control gate voltage ( $V_{T_E} < V_{CS} < V_{T_P}$ ) is applied to the device to determine whether it is conductive or not.

While  $V_{T_{FS}}$  depends only on the device technology (and on the possible charge trapped within the gate oxide),  $V_{T_{CS}}$  varies with the charge within the FG and this is the key result explaining the success of the FG device as the basic cell for nonvolatile memories applications. Fig. 1.2a shows two different I-V trans-characteristics obtained by modifying the FG charge. In particular, by choosing a suitable "threshold shift" ( $|Q/C_C|$ ), it is possible to define two different (and separate) device states: erased for Q=0, and programmed for  $Q\ll 0$ . The corresponding threshold voltages applied to the control gate are

$$V_{T_{CS}} = \frac{1}{\alpha_C} V_{T_{FS}} = V_{T_E} , \qquad (1.6)$$

$$V_{T_{CS}} = \frac{1}{\alpha_C} V_{T_{FS}} - \frac{Q}{C_C} = V_{T_P} , \qquad (1.7)$$

and they are denoted as "erased threshold" and "programmed threshold", respectively.

The device state can be read by applying an appropriate "sensing" voltage to the control gate, as shown in Fig. 1.2b. When the FG device I-V curve corresponds to curve a (Q=0), then  $V_{CS}>V_{T_E}$  and the device is ON; when the device has been previously programmed (curve b),  $V_{CS}< V_{T_P}$  and the device is OFF.

#### 1.4 CHARGE INJECTION MECHANISMS

There are many solutions used to transfer electric charge from and into the floating gate. For both erase and program, the problem is making the charge pass through a layer of insulating material. The different physical phenomena which contribute to determine the behavior of a nonvolatile memory cell are analyzed in depth in Chapter 4.

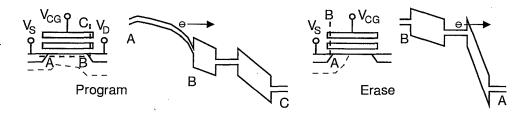

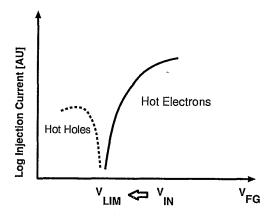

The hot-electron injection and the Fowler-Nordheim tunneling mechanisms are generally used to write Flash memories. In the former, a lateral electric field (between source and drain) "heats" the electrons, and a transversal electric field (between channel and control gate) promotes the injection of the carriers through the oxide. The latter starts when there is a high electric field through a thin oxide. In these conditions, the energy band diagram of the oxide region is very steep; therefore, there is a high probability of electrons passing through the energy barrier itself.

Hot electrons and tunneling effects have been extensively studied since they can induce reliability problems in scaled MOS transistors. In nonvolatile memory cells, the very same mechanisms are controlled and exploited to become efficient program/erase mechanisms.

#### 1.5 ERASABLE PROGRAMMABLE READ ONLY MEMORIES

1.5.1 The Floating gate Avalanche-injection MOS transistor (FAMOS) Cell

In 1967 D. Khang and S. M. Sze at Bell Laboratories [3] proposed a MOS-based nonvolatile memory cell based on a floating gate in a metal-insulator-metal-insulator-semiconductor structure. The lower insulator had to be thin enough (< 5 nm) to allow quantum-mechanical tunneling of electrons from the substrate to the floating gate and viceversa. At that time, however, it was almost impossible to deposit such a thin oxide layer without introducing fatal defects.

As a consequence, the tunneling mechanism was initially abandoned, and the first operating floating gate device, which adopted a fairly thick oxide layer, was developed at Intel in 1971 by Frohman-Bentchowsky [4]. This cell had no control gate, and was programmed by applying a highly-negative voltage at the drain, thus avalanching the drain/substrate junction, and creating a plasma of highly energetic electrons underneath the gate. The electrons were injected into the oxide and reached the floating gate, thus programming the cell.

Due to the absence of a control gate, however, the operation was extremely inefficient, and enormous voltages were needed. In order to inject electrons in the floating gate, p-channel devices had to be used. Erasure was obtained by providing externally the energy required by electrons to be re-emitted from the

floating gate. This was accomplished by exposing the cell to ultra-violet (UV) radiation.

## 1.5.2 The basic Erasable Programmable Read Only Memory (EPROM)

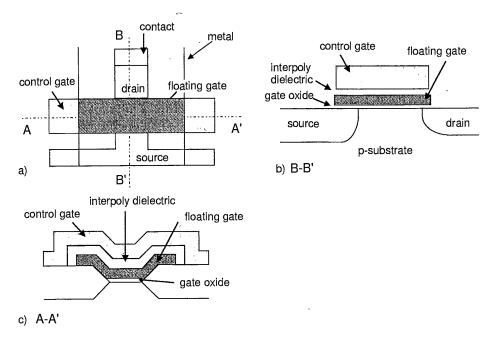

The FAMOS concept eventually evolved into a double polysilicon stacked gate n-channel cell, as schematically shown in Fig. 1.1, which constitutes the basic cell of an EPROM.

This cell is programmed by injection of channel hot-electrons into the floating gate and is erased using UV radiation. The programming consists in raising both the control gate (wordline) and the drain (bitline) to high voltages, typically 12 V. There are several relevant features:

- 1. hot electron programming is a very inefficient process, which requires both high voltage and high current. The stacked gate EPROM can not work with a single, low voltage supply;

- 2. only the cell which has both the control gate and the drain at high voltage is programmed: the operation is bit-selective. The same applies to the reading operation;

- 3. both the bit-selective hot-electron programming mechanism and the UV erasure process, which is obviously carried out on the whole array, are self-limiting. In particular, by UV erasure one can not indefinitely remove electrons from the floating gate, thus obtaining a cell with a too low threshold, i.e. an overerased cell. An over-erased cell is a cell with excessive source-drain leakage current when unselected, due to the threshold of the cell itself being lower than the applied control gate voltage.

Since the programming and reading operations are automatically bit-selective, while erasure is carried out on the whole chip, the EPROM does not require a select transistor or a split-gate structure to carry out bit selection, and can be implemented as a one-transistor memory cell. Its T-shaped cell is therefore extremely compact, leading to densities of 64 Mbit and more. Low-density memories, often adopting special processes can reach access times as fast as 15 ns, and a single supply voltage of +5 V is required for all operations except programming, which requires 12 V.

If reprogramming is needed, the EPROM must be removed from the circuit board, UV erased and then reprogrammed. The UV erasure requires the adoption of expensive packages having a transparent quartz window over the chip. When reprogramming is not required, a cheaper, plastic-packaged version of the same EPROM chip is often available, called One Time Programmable (OTP) memory. Since UV erasure is impossible, the memory can be written

only once, and represents a more dense, reliable, and cheaper alternative to PROMs.

#### 1.6 **ELECTRICALLY ERASABLE PROGRAMMABLE READ ONLY MEMORIES**

Since the very beginning of nonvolatile memories development, various methods to achieve in-system electrical erasure, thus obtaining an Electrically Erasable Programmable Read Only Memory (EEPROM), were developed.

In 1967 Wegener et al. [5] introduced the already mentioned MNOS cell. The MNOS cell resembles a standard MOS transistor in which the oxide has been replaced by a nitride-oxide stacked layer. Electrons and holes can be trapped in the nitride, which then behaves as a charge storage element. Programming is achieved by applying a high, positive bias  $V_G$  to the gate, thus inducing quantum-mechanical tunneling of electrons from the channel region into the nitride traps. Erasure is obtained by tunneling of holes from the semiconductor to the nitride traps when  $V_G$  is negative and sufficiently high.

In order to improve the charge retention of MNOS memories, new structures have been developed. The SNOS (Silicon Nitride Oxide Semiconductor) employs a nitride layer deposited by Low Pressure Chemical Vapor Deposition (LPCVD) and a hydrogen anneal which improves the quality of the interfaces. The retention of the SNOS improves as the thickness of the nitride is reduced; unfortunately this leads to enhanced hole injection from the gate. In order to eliminate this problem, a top oxide layer is used between the gate and the nitride layer, thus obtaining the SONOS (Silicon Oxide Nitride Oxide Semiconductor) structure. SONOS EEPROM have been reported to withstand erase/write cycling up to 10M cycles, with 1.0  $\mu$ m<sup>2</sup> cells suitable for 256MB memory arrays and PCMCIA cards [6].

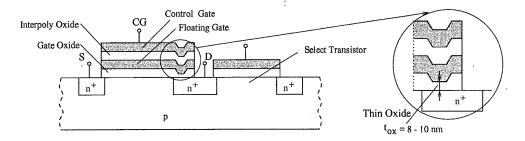

## The FLOating gate Thin Oxide (FLOTOX) Memory Cell

In order to obtain an electrically erasable and programmable non volatile memory, one can adopt Fowler-Nordheim for both programming and erasing, as proposed for the first time by Harari et al. [7]. Figure 1.3 shows the schematic cross-section of the FLOTOX cell, including a "selection" transistor which is required due to the non-selectivity of the tunneling process, as explained below. This combination represents the basic cell of a byte-addressable EEPROM memory [8]. Programming is obtained by applying a high voltage to the control gate, with the drain at low bias. By capacitive coupling, the voltage on the floating gate is also increased, and tunneling of electrons from the drain to the floating gate is initiated through the thin (8-10 nm) oxide grown on top of the

Figure 1.3 Schematic section of a FLOTOX cell including the select transistor.

drain, see the inset in Fig. 1.3. Erasing occurs when the drain is raised to a high voltage, and the control gate is grounded; the floating gate is capacitively-coupled to a low voltage, and electrons tunnel from the floating gate into the drain. The drain bias is controlled by the select transistor.

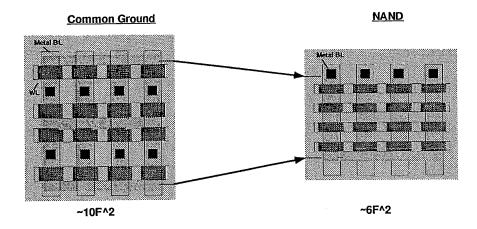

The process variations behind the implementation of a FLOTOX EEPROM cell starting from an EPROM process are relatively simple, so this kind of nonvolatile memory is widely diffused both as a stand alone memory product and within ASICs and logic. EEPROMs are erased on a bit or byte level, and can be reprogrammed in-system, with endurance up to 10<sup>6</sup> cycles. Since Fowler-Nordheim is a low current programming/erasing mechanism, the high voltage required can be generated within the chip, by specific charge-pumping circuits which multiply the supply voltage. The main limit of EEPROM is the cell size (3-4 times larger than that of a single transistor ROM cell) and the low density, due to the need of a select transistor (i.e. a two-transistors cell); typical densities of 4Mbit can be now reached.

Writing the EEPROM is also a rather slow process which has to take place in two steps. Referring to Fig. 1.3, the first step consists in programming all the byte cells by injecting electrons in the floating gate; this is carried out by raising the control gate and the gate of the select transistor, grounding the drain of the select transistor itself (the  $n^+$  region at the extreme right in Fig. 1.3). Subsequently, selective erasing of the single bits is carried out. Electrons are removed only in selected cells (bits) by grounding the control gate, raising the select gate and applying a high voltage to the drain of the select transistor which transfers it to the floating gate transistor.

#### 1.6.2 Textured Polysilicon Cells

Instead of exploiting tunneling through the thin oxide layer between the floating gate and the silicon drain area, textured polysilicon cells adopt tunneling through oxides thermally grown on polysilicon, with charge exchange between

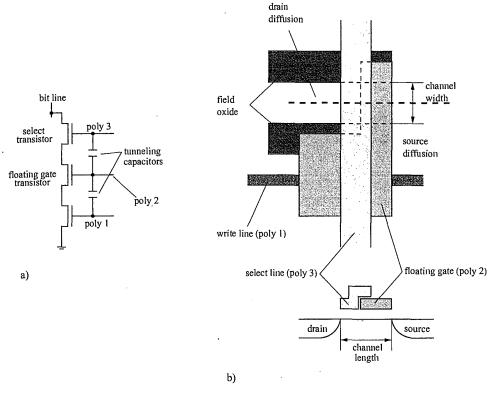

Figure 1.4 Equivalent circuit (a), layout and schematic cross-section (b) of a textured poly EEPROM cell

different polysilicon gates. The advantage is that, since the surface of polysilicon is rough (i.e. "textured"), electric field enhancement takes place, and tunneling is possible, for the same applied voltage, also using thick oxide layers. The cell consists in three transistors in series (see Fig. 1.4a), having their polysilicon gates partially overlapped, see Fig. 1.4b; the alignment of these layers may result critical for the adopted lithography. The floating gate is in the middle (poly2); electrons are injected from poly1 to the floating gate (programming) and from the floating gate to poly3 (erasing). The voltage on poly3 is always high, so erasing or programming is selected according to the voltage applied to the drain. The overlapping of the gates results in a compact vertical structure, which occupies an area lower than that of the FLOTOX EEPROM cell, resulting in an advantage for higher density EEPROMs. Moreover, this cell does not require programming before selective erasure, as in the case of the FLOTOX EEPROMs. The quality and reliability of this technology strongly

depends on the feature of the polysilicon and of the oxide thermally grown on it. Trapping in the poly oxide may result in device wearout.

## 1.6.3 The EEPROM Architecture

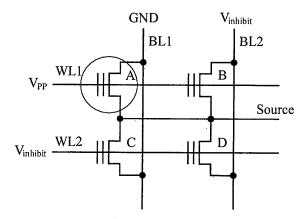

To understand why an EEPROM cell includes the actual storage element together with a series transistor, it is necessary to move our analysis to the architectural level. In a NOR architecture (see Fig 1.5 for the simplest  $2\times 2$  matrix without select gates), the same word line drives several control gates, while each bit line is shorted to the drain of many cells.

**Figure 1.5** Simple  $2 \times 2$  NOR-EEPROM architecture showing a program disturb on cell C when cell A is programmed.

If, as shown in Fig. 1.5, cell A is to be programmed, its control gate must be driven at the high programming voltage  $V_{PP}$ , while its drain must be kept at ground, so that a high oxide field allows for electron tunneling from the drain to the floating gate FG. Cell B, that shares the same word line WL1, may be also programmed, if its drain is also kept at a low voltage. Therefore, to inhibit an undesired programming of B, its drain, i.e. BL2, must be raised to a high voltage  $V_{inhibit}$  (possibly equal to  $V_{PP}$ , to reduce the number of different biases) guaranteeing that no electrons may tunnel into its FG.

At this point, however, the problem of undesired writing is moved to cells C or D: if WL2 is kept at a low voltage, cell D may be erased (or even overerased if not already programmed, thus becoming depleted) since the high oxide field forces electron tunneling from the FG into the drain while, if WL2 is driven at a inhibiting voltage  $V_{inhibit} = V_{PP}$ , cell C is automatically programmed.

These write disturbs, as well as those occurring during erasing operations, may be reduced by using a lower inhibiting voltage, for instance  $V_{inhibit} = V_{PP}/2$ , with the need of an internal generation of such a voltage.

However, the general solution consists in the integration of a selecting transistor in series to any storage element, so that writing operations can affect only the selected cell. As discussed previously, such a solution implies a larger area occupied by the cell.

#### 1.6.4 Ferroelectric Memories

Charge storage on a floating gate is not the only way to obtain a nonvolatile memory element. Other electrical properties of materials can be exploited in order to obtain an EEPROM-like memory cell; in particular, various approaches adopting ferroelectric materials have been demonstrated in recent years.

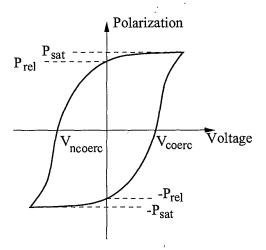

Ferroelectric materials are composed by small crystals characterized by a charge dipole which tends to align in parallel to an externally applied electric field. On increasing the electric field, the polarization level increases and saturates (see Fig. 1.6); the same applies when the electric field is reversed, so that there are two stable polarization states. These states do not require external electric field or current to be maintained and can be used for nonvolatile digital data storage.

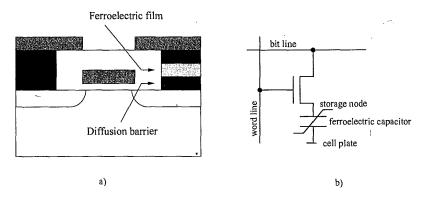

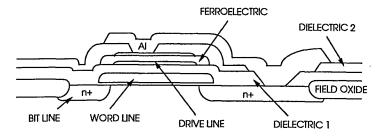

The memory element is usually (but not always) represented by a capacitor, using a ferroelectric thin film as dielectric (see right-hand side of Fig. 1.7a). One of the most commonly adopted materials is lead zirconate titanate,  $Pb(Zr,Ti)O_3$  (PZT), which can be deposited by sol-gel or RF sputtering as an add-on of a standard CMOS process.

When the voltage applied to the capacitor exceeds a certain positive value  $V_{coerc}$ , the polarization becomes positive and increases up to a saturation value  $P_{sat}$  (see Fig. 1.6). The same applies for negative voltage lower than  $V_{ncoerc}$ , leading to a saturated polarization  $-P_{sat}$ . When the electric field is removed, the ferroelectric film maintains its state of polarization, but the value of polarization is somewhat reduced to a relaxation value  $P_{rel}$  (or  $-P_{rel}$  if a negative voltage has been applied). Two logic states are therefore possible, corresponding to the  $P_{rel}$  and  $-P_{rel}$  polarizations. When, during the read operation, a positive voltage is applied to the ferroelectric capacitor the polarization changes from  $P_{rel}$  to  $P_{sat}$ , thus requiring a low current (logic state 0) or from  $-P_{rel}$  to  $P_{sat}$ , which corresponds to a high current, or to the logic state 1. The difference in current between two memory states is sensed to generate the output. After reading the 1 state, the  $-P_{rel}$  negative polarization must be regenerated by applying a negative voltage to the capacitor.

**Figure 1.6** Typical hysteresis curve of a ferroelectric capacitor, identifying polarization states.

**Figure 1.7** a) Schematic cross-section of a ferroelectric nonvolatile DRAM; b) equivalent circuit.

Potential advantages of ferroelectric memories can be summarized as follows: i) ferroelectric memories can use a single low voltage supply for all operations [9]; ii) fast read/write operations can be achieved, with access times of the order of 50 ns and cycle times lower than 100 ns; iii) ferroelectric memories are characterized by an excellent endurance, of over  $10^{12}$  cycles, which would be impossible to achieve with Flash memories [10]; iv) ferroelectric films can maintain their characteristics in a very wide range of temperatures, up to 350°C; v) they can achieve excellent radiation tolerance characteristics, suitable for space and military applications.

The basic ferroelectric random access memory cell is composed by the series connection of one transistor and one ferroelectric capacitor, as shown in Fig. 1.7b, and its size is still much larger than that of DRAMs. Single-transistor cells adopting the ferroelectric film as dielectric in a Metal - Ferroelectric - Semiconductor Transistor (MFST) are affected by fabrication difficulties, poor data retention, high write voltage and read disturb [10]. Despite other solutions such as NAND organization (sacrifying random access) or vertical transistors (at the cost of very difficult fabrication) have been tried, the cell size limitations still has to be solved, though a 60 ns, 1 Mb nonvolatile ferroelectric memory has been presented in 1996 [11].

Ferroelectric Random Access Memories have a great potential as a future high density non volatile memories, because of the advantages previously listed; however, the ferroelectric films used as memory storage elements have some reliability concerns, such as aging effects after extensive cycling, thermal stability, degradation due to electric field, time-dependent breakdown phenomena. Extensive research activity concerning ferroelectric materials properties is being carried out; quaternary compounds such as  $SrBi_2Ta_2O_9$  (SBT) currently provide best performances in terms of fatigue-free, low-voltage operation.

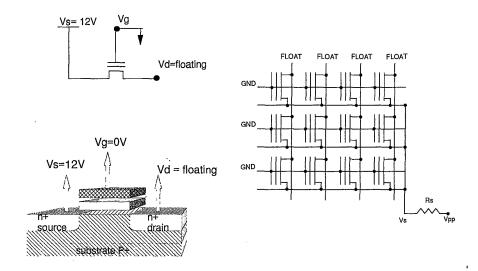

# 1.7 FLASH MEMORIES: THE BASIC ETOX CELL. PROGRAMMING AND ERASING MECHANISMS

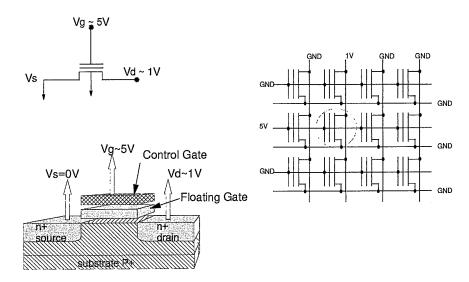

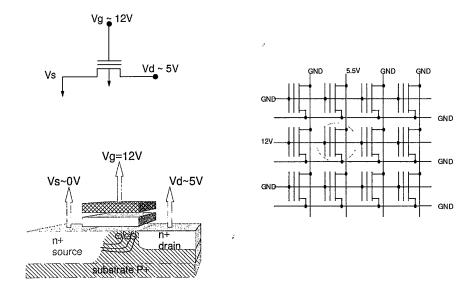

Flash memories represent the synthesis of EPROM and EEPROM, since they are programmed and erased electrically but composed by single transistor cells. Programming is carried out selectively by means of the hot electron mechanism; erasing is based on tunneling, and is carried out in blocks of different sizes, from 512 bytes to full chip [12]. The first cell based on this concept was presented in 1979 [13]; the first commercial product, a 256-K memory chip, was presented by Toshiba in 1984 [14]. The market did not take off until this technology was proven to be reliable and manufacturable [15].

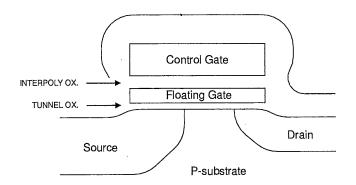

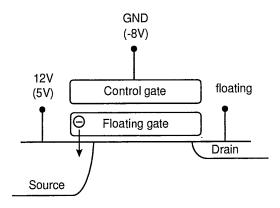

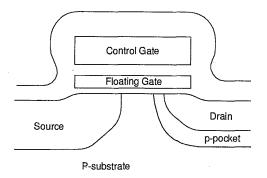

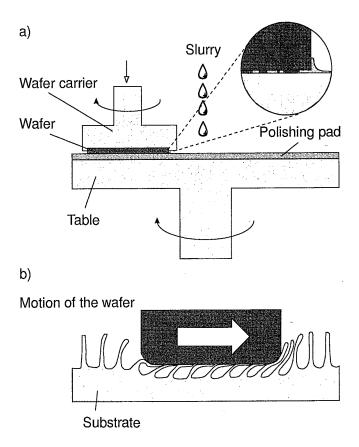

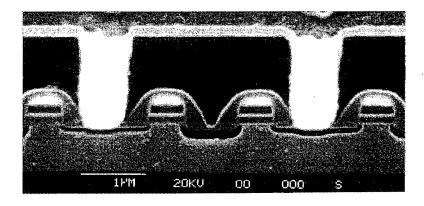

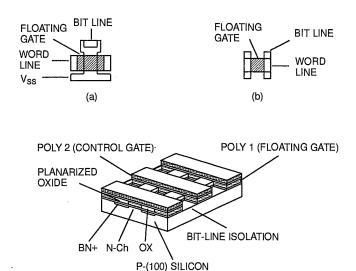

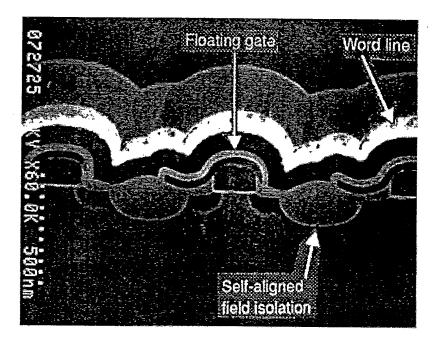

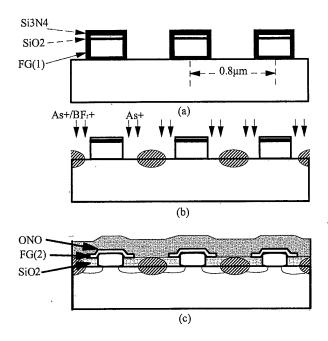

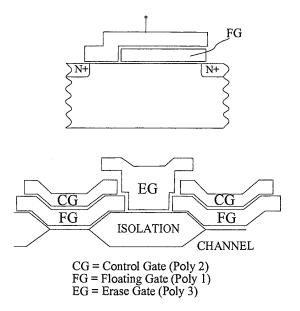

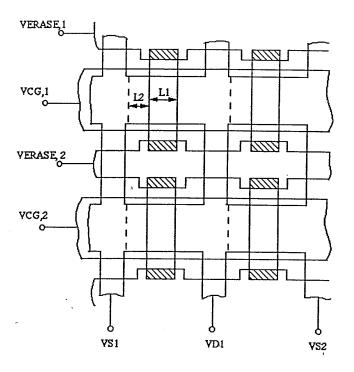

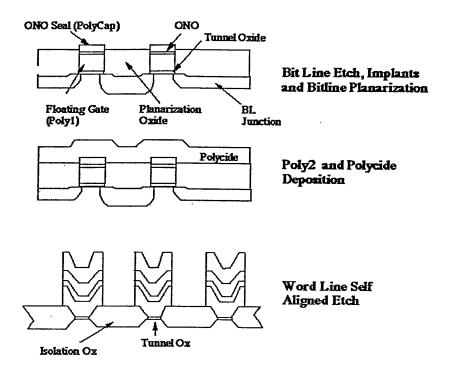

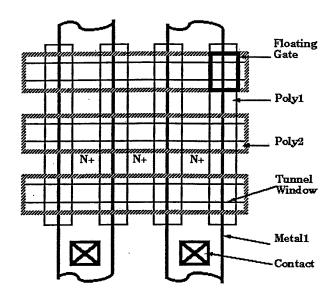

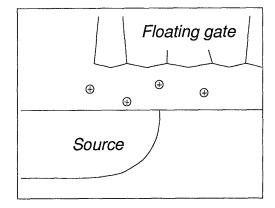

Figure 1.8 shows the cross-section of an industry-standard Flash cell. This cell structure was presented for the first time by INTEL in 1988 and named  $ETOX^{TM}$  (EPROM Tunnel OXide; ETOX is a trademark of INTEL) [16]. Though it is derived from an EPROM cell, there are a few meaningful differences.

First, the oxide between the substrate and the floating gate is very thin (of the order of 10 nm). Therefore if a high voltage is applied at the source when the control gate is grounded, a high electric field exists in the oxide, enabling electron tunneling from the floating gate to the source. This bias condition is dangerously close to the breakdown of the source-substrate junction. Therefore, the source diffusion is realized differently from the drain diffusion, which

Figure 1.8 Schematic cross-section of an industrial Flash cell.

does not undergo such bias conditions. To do so, a new mask is added to the technological process to discriminate source and drain implants. The cell is not symmetrical, but this is the only difference with respect to the standard EPROM process. This is a great advantage, since all the accumulated experience in process development can be used to produce these devices.

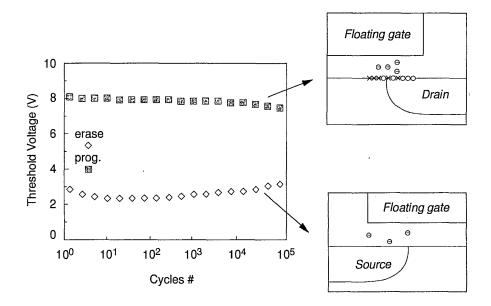

The first Flash prototypes needed an external supply voltage for programming and external management of the erasing algorithm. They featured only a bulk-erase capability and their endurance was very poor (less than 10000 cycles). As an advantage versus EPROM's, they offered just an electrical-erase capability. Modern Flash memories have an embedded microcontroller to manage the erasing algorithms and offer sector erase capability and single power supply. In the following it will become clear that the correct operation of a Flash memory requires the design of a complex electronic circuit; due to the interaction between the various cells of the array, also the yield, quality, testing and reliability of the memory depend not only on the cell technology, but also, and in a more subtle way, on its architecture, which will be specifically discussed in Chapter 5. Flash reliability and testing will be addressed in Chapters 7 and 8, respectively.

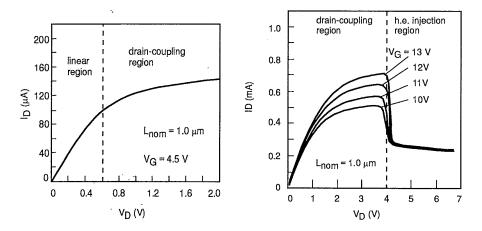

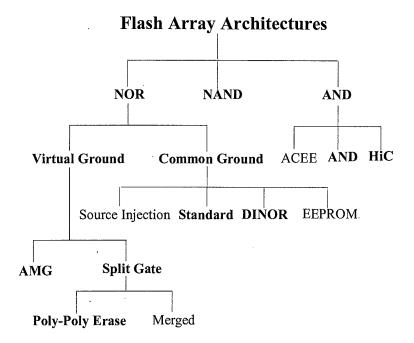

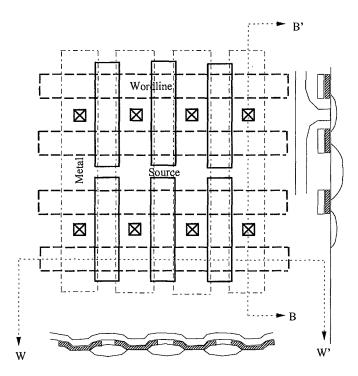

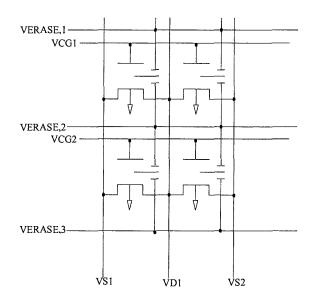

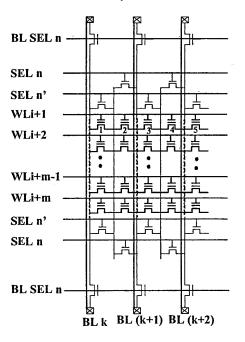

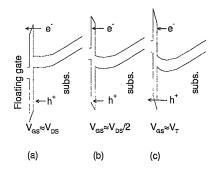

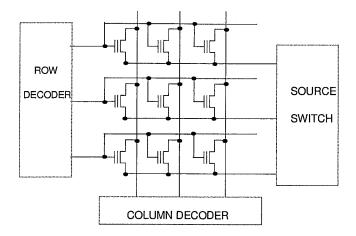

#### 1.8 MEMORY NOR ARCHITECTURE AND RELATED ISSUES

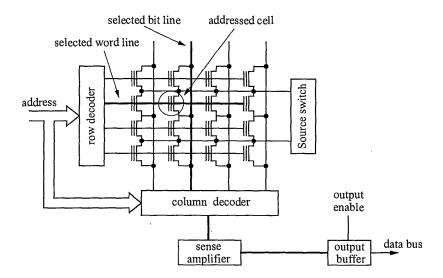

There are three basic operations in a Flash memory: read (a byte or a word), program (a byte or a word), erase (one or more sectors). Among these operations, the read one is the most frequent and it is also the simplest. To illustrate this basic operation, we consider that only one cell (rather than a byte or a word) is read at a time, as shown in Fig. 1.9, where a NOR organization has been considered. The extrapolation of the read procedure to a real case is quite simple since all the cells belonging to the same byte or word share the

**Figure 1.9** Schematic structure of the read path in a NOR organization. Only one bit at a time is here considered as addressable.

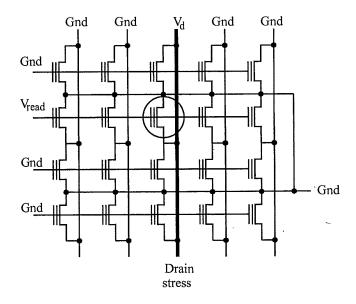

same word line, while 8 or 16 bit lines, as well as 8 or 16 sense amplifiers, are activated simultaneously. Once the cell address has been provided, the row decoder activates the selected word line by raising its voltage while keeping all the others at ground. The addressed bit line is connected to the sense amplifier. If the addressed cell is programmed (high threshold voltage, corresponding to the logic state "0"), no current flows through the cell and the bit line. On the contrary, if the cell is erased (low threshold voltage, corresponding to a logic "1"), the cell is ON and its current is detected by the sense amplifier.

The activation of the output enable signal transfers the read data to the data bus and the read operation ends. As it will be extensively illustrated in Chapter 5, the basic role is played by the sense amplifier, whose design must take into account several constrains.

The write operations (program and erase) are much more complex, as it can be understood by the following schematic description.

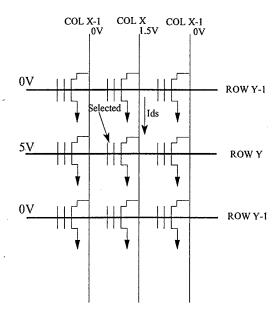

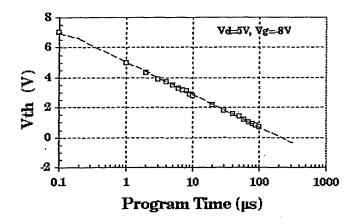

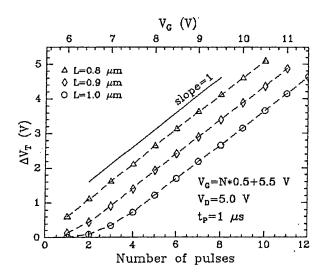

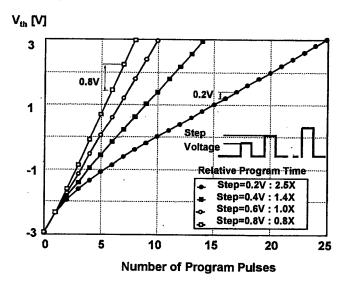

When programming, the word line is raised to activate the cell to be programmed. If the input data is 0, the bit line is driven at a high voltage, to allow for channel hot electrons to raise the cell threshold voltage. After the application of the programming pulse it is necessary to verify whether the cell has been correctly programmed, i.e. to verify whether the threshold voltage is larger than a minimum acceptable value  $V_{Tp_m}$ . This basic task is performed by reading the cell with a gate voltage higher than that usually applied during normal reading and by comparing the read data with that to be programmed,

that has been latched in a dedicated register. If the two data coincide, it means that the threshold voltage of the cell has risen from the erased value to the programmed one and that, since this read operation has provided a correct result with a higher reading voltage, the correct value is expected to be detected even in a conventional reading. If the verification fails, another programming pulse is applied to the cell (always by raising both gate and drain), until the cell is correctly programmed or a maximum number of pulses has been reached, so that a fail signal is produced.

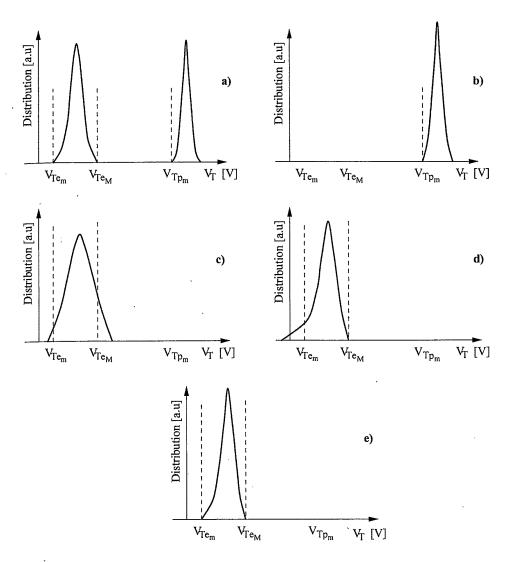

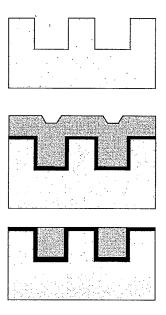

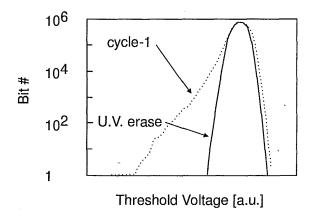

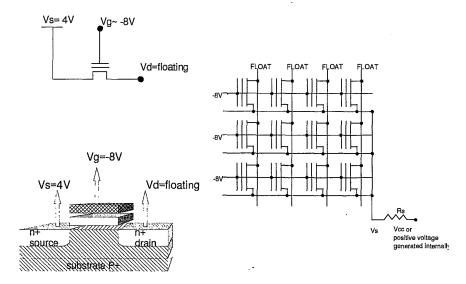

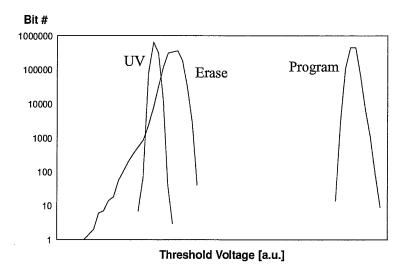

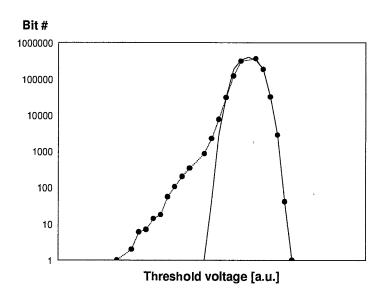

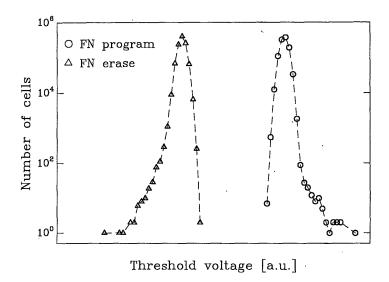

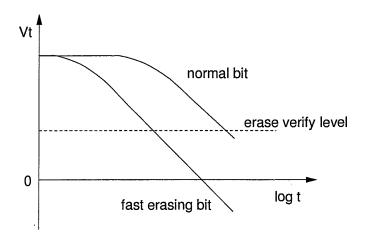

For several reasons the erase procedure is even more complicated. First of all, it is performed on an entire sector, so that the verification process requires that all the cells of the sector are read in sequence. In addition, it is important to check whether the threshold of some cells become too low and, in case, to raise their threshold to a higher value. A schematic behavior of the thresholds' distribution for cells belonging to the same sector is shown in Fig. 1.10, starting from a typical situation occurring before erasing (Fig. 1.10a). Once the erase procedure has been activated, all the cells of the sector are programmed with a 0, so that their threshold is raised (Fig. 1.10b). This normalization task reduces the possibility of overerasing cells written with a 1 (that could become leaky when unadressed), and it allows for a more uniform distribution of the erased thresholds, since all the initial thresholds belong to the same range.

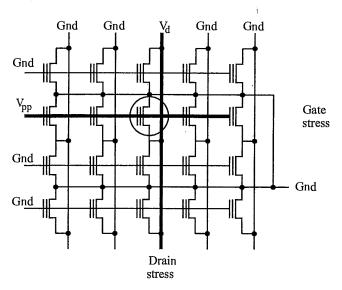

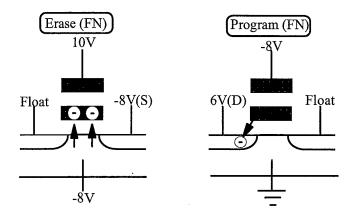

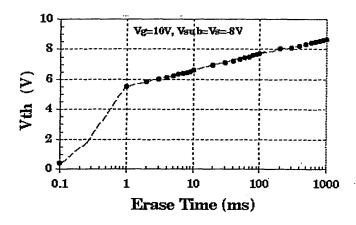

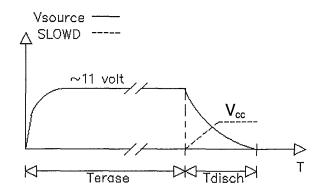

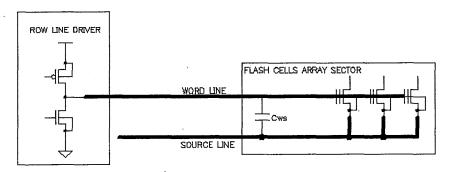

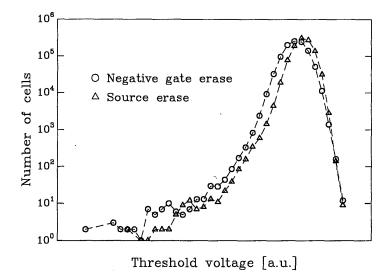

To erase a single sector, a high electric field must be applied between the sources and the gates of the cells belonging to the sector, to allow for Fowler-Nordheim current to discharge the floating gate of the cells. This task is accomplished in two different ways: i) by applying a high voltage (in the range of 12 V) to the source of the cells to be erased while grounding their gates (source erase), or ii) by splitting the biasing voltage between source (at  $5 \div 7$  V) and gate (at  $-8 \div -10$  V) (negative gate erase). Both solutions present a major drawback: the highly negative bulk-source voltage drop can activate avalanche injection in the former case, while the generation of a negative voltage is required in the latter.

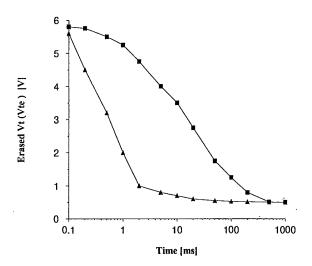

As illustrated in Chapter 4, tunneling current depends on many physical and technological parameters, so that even adjacent cells can discharge at different rates. After a single erase pulse has been applied, the threshold distribution may be similar to that depicted in Fig. 1.10c. In particular, many cells are not fully erased  $(V_T > V_{Te_M})$ , while others may feature threshold voltages below the minimum allowed  $(V_T < V_{Te_m})$ .

As for the programming operation, it is then mandatory to check for the correctness of the erase procedure, by reading the entire sector with a gate voltage lower than that usually applied during normal reading. If the data read is "1", it means that the threshold voltage of the cell has been lowered from the programmed value to the erased one and that, since this read operation

**Figure 1.10** Schematic distribution of the threshold voltages during an erase operation: a) before erase; b) after a "program all-0" operation; c) after a single erase pulse; d) after the erase verify procedure has been successfully performed; e) after soft-programming.

has provided a correct result with a low reading voltage, the correct value is expected to be detected even in a conventional reading. If the verification fails for at least one cell, another erasing pulse is applied to the sector until all the cells are correctly erased or a maximum number of pulses has been reached, so that a fail signal is produced. After the erase verify procedure

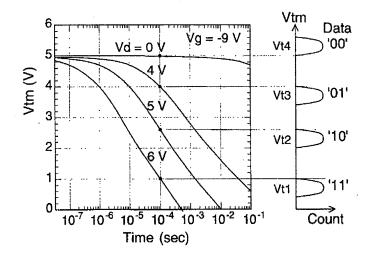

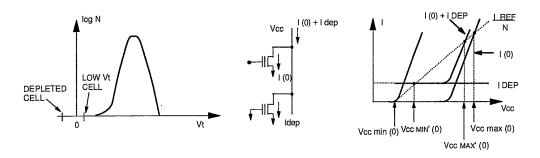

(see Fig. 1.10d), it is important to check whether some cells are overerased ("depletion verify") and, in case, their thresholds must be driven to the correct range ("soft programming"). The former operation must check whether some cells feature low or even negative threshold (depleted cells), so that they would draw current even if not biased, thus preventing from a correct reading of cells belonging to the same bit line. With the latter operation, these cells are written with suitable gate and drain voltages that, lower than those used during the normal program procedure, allow for a slight increase of the threshold voltage. The final threshold distribution is then bounded between  $V_{Te_m}$  and  $V_{Te_M}$  (see Fig. 1.10e).

From the schematic description of the three basic operations it is possible to stress some peculiar features concerning the architecture and the reliability of Flash memories:

Line biasing. Word lines (cell gates), bit lines (cell drains) and common source must be biased at different voltages, depending on the selected operation and even during the same procedure (for example, during erasing, the gate of a single cell must be driven at the programming voltage during "all-0 programming", at ground or at a negative voltage when an erase pulse is applied, at a low reading voltage during "erase verify", at suitable voltages during "depletion verify" and "soft programming").

As it will be extensively shown in Chapter 5, these requirements make the circuitry controlling these voltages quite complex, in particular in terms of decoders, switches and charge/discharge of highly-capacitive lines, noise disturbs due to capacitive coupling.

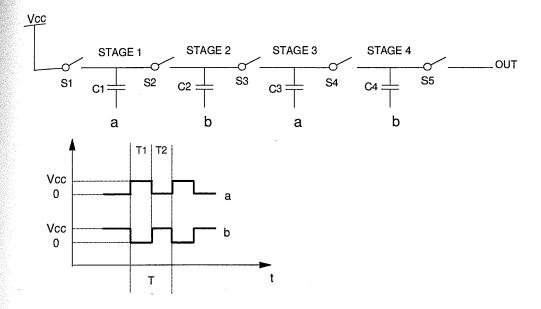

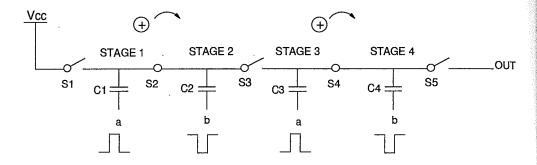

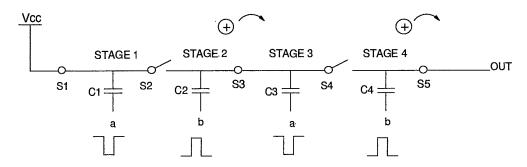

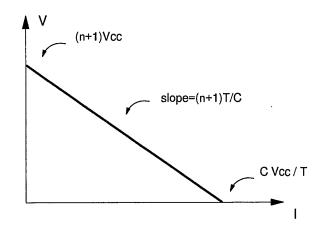

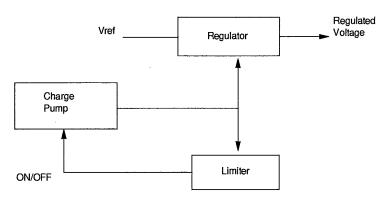

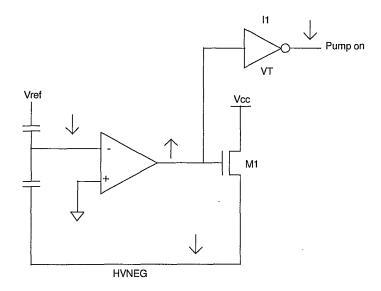

High voltage requirements. Since writing requires high fields applied to the cells, high voltages must be provided to cell terminals. These writing voltages are higher than those used during normal operations and to bias logic circuits. Therefore, two solutions are adopted: i) double voltage supply devices, in which the high voltages to be applied during programming are provided at an external pin; ii) single voltage supply devices, in which high voltages are generated internally, by means of charge pumps.

Charge pumps present several limitations making the overall performance of a Flash memory critically dependent on their design, in particular when low-voltage supplies are used. The main problems and solutions, detailed in Chapter 5, can be summarized as follow: relevant power consumption, large area and time requirements for high voltage generation, limited maximum output current.

In addition, when the negative gate erase scheme is chosen, both positive and negative charge pumps must be integrated.

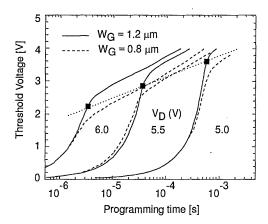

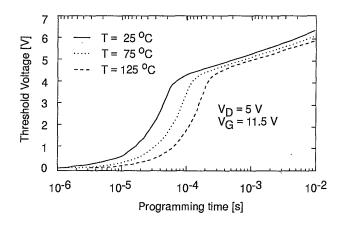

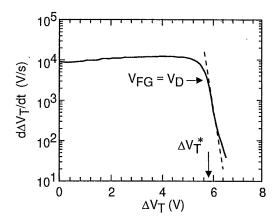

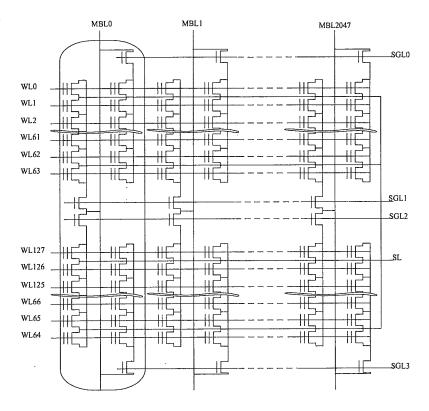

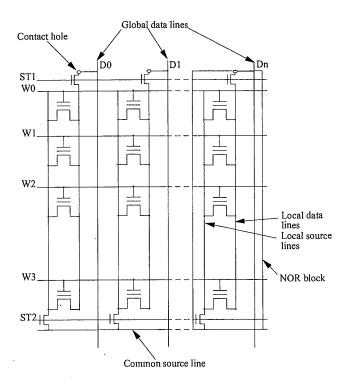

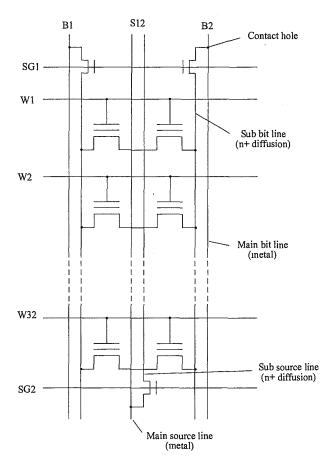

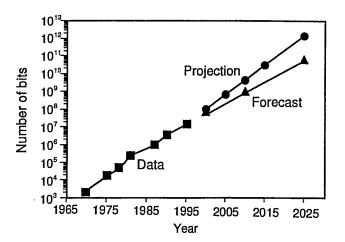

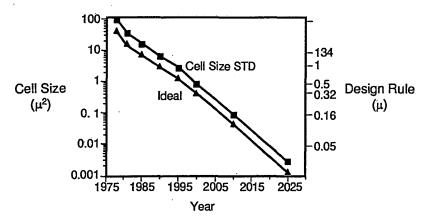

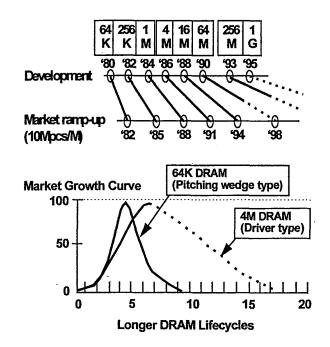

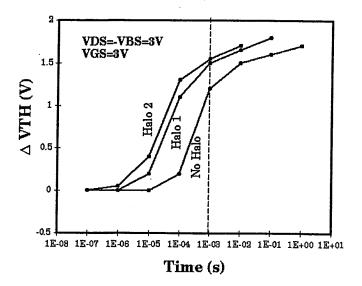

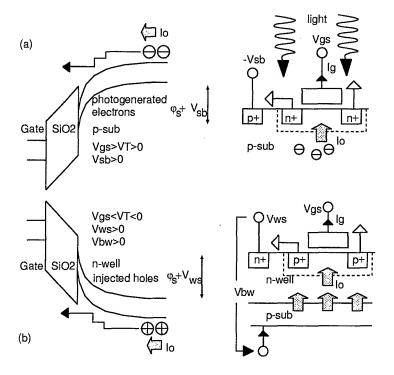

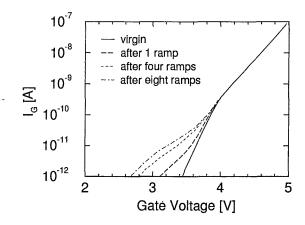

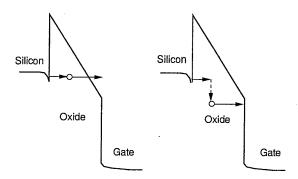

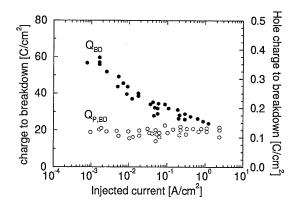

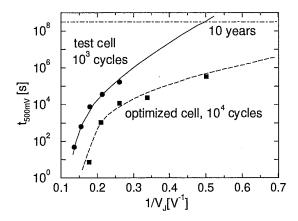

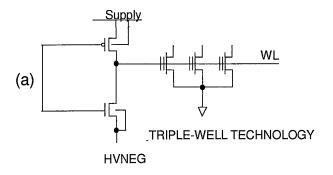

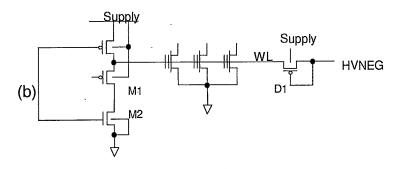

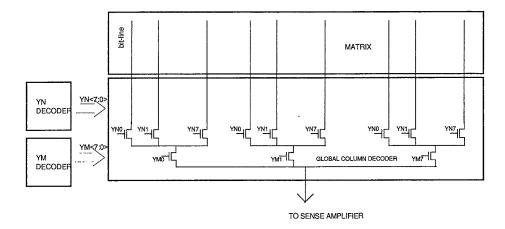

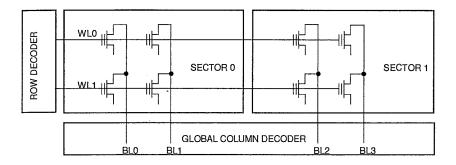

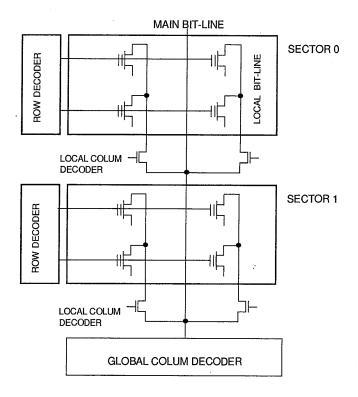

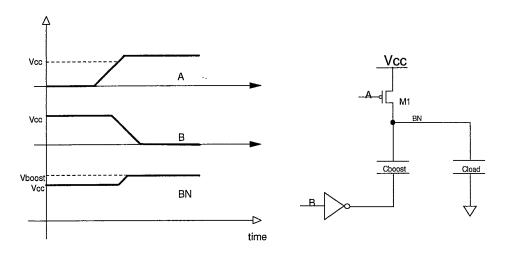

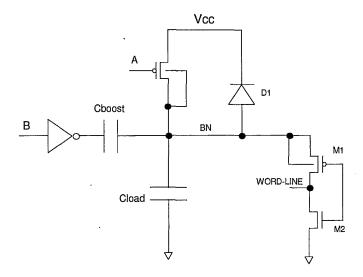

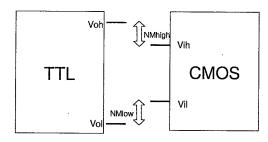

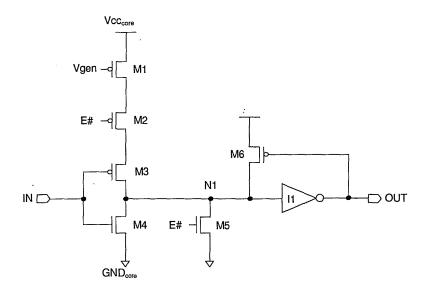

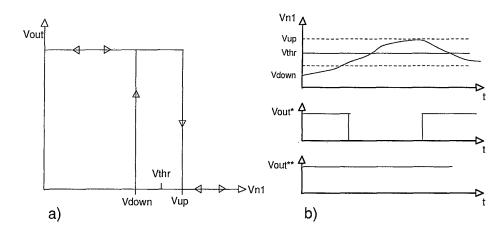

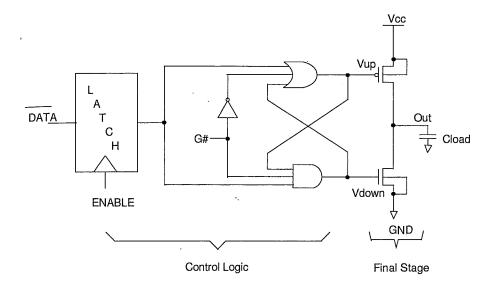

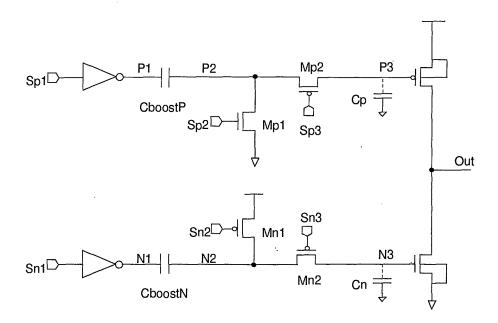

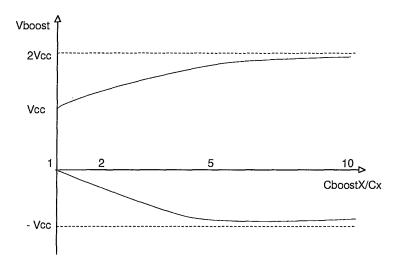

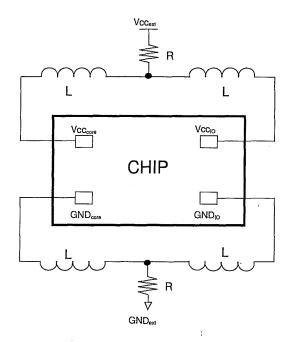

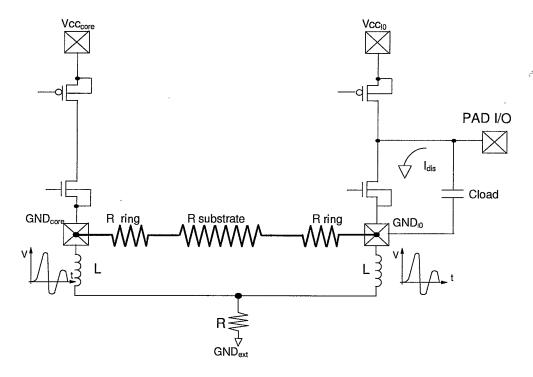

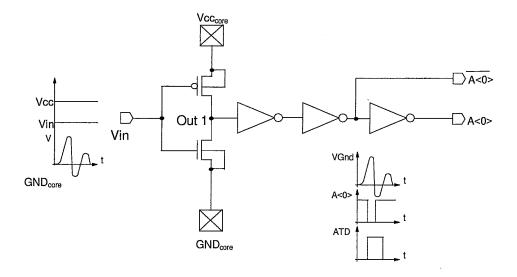

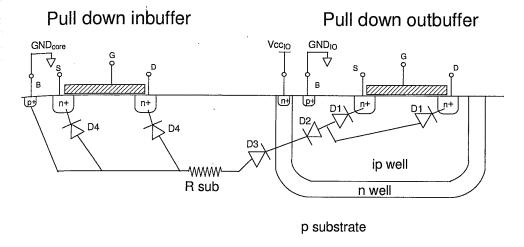

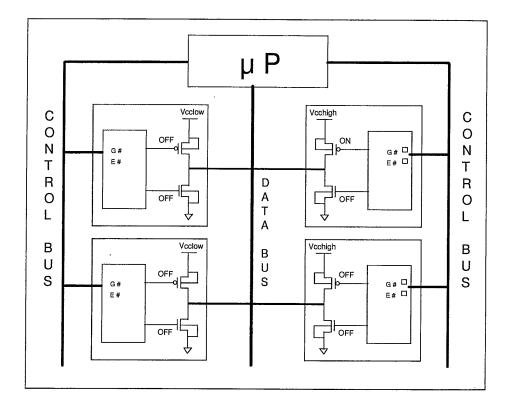

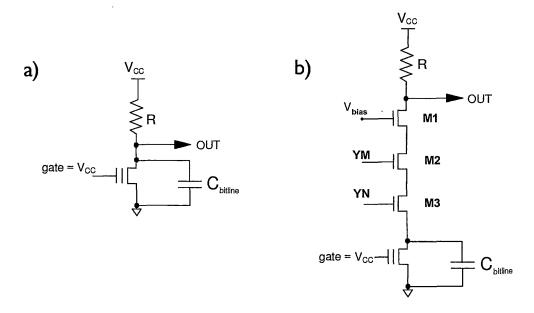

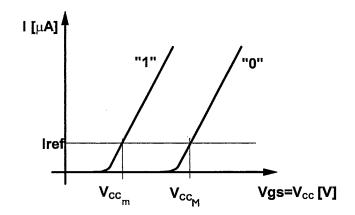

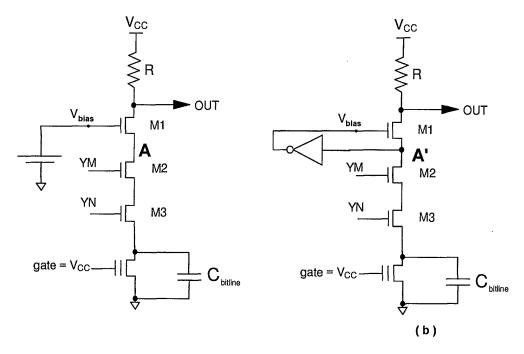

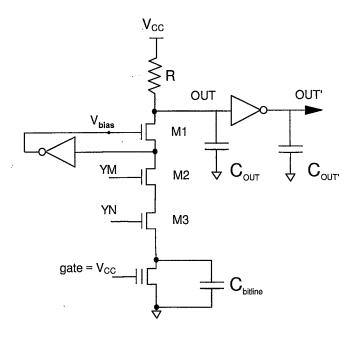

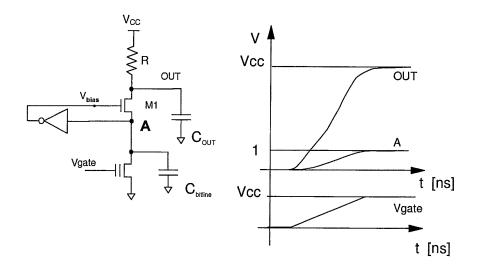

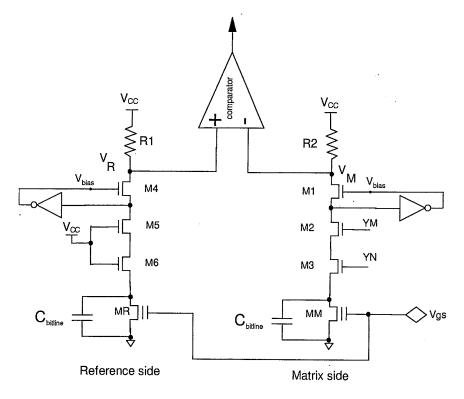

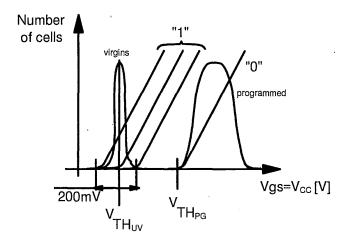

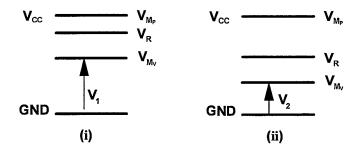

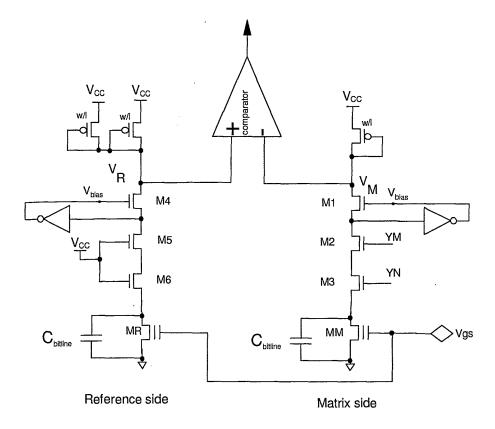

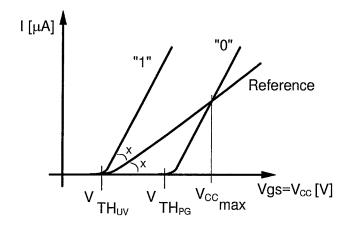

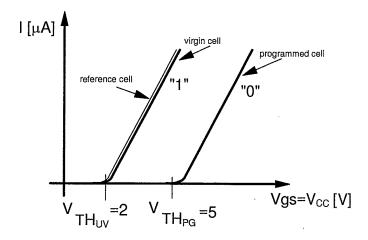

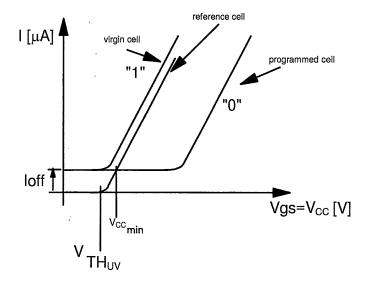

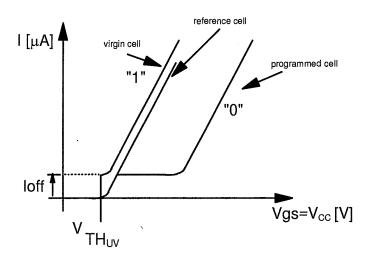

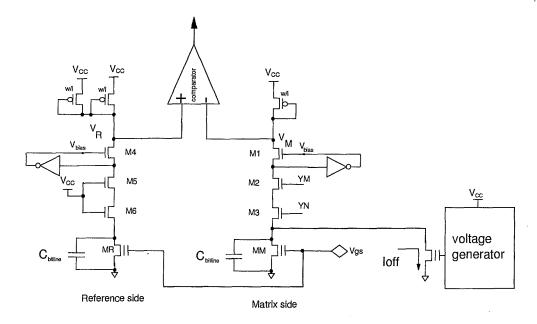

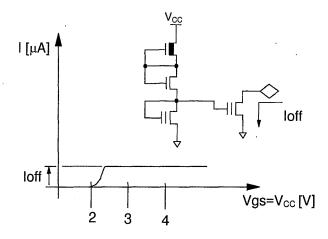

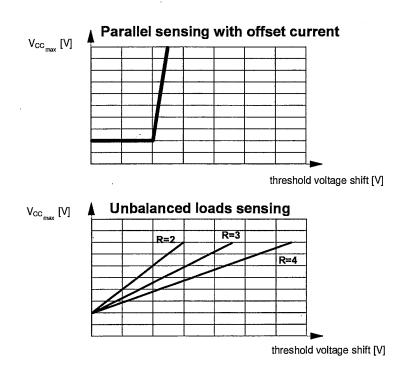

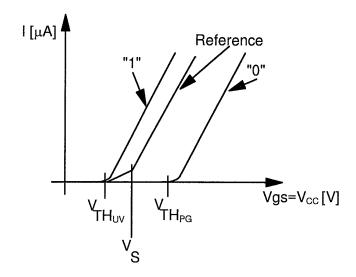

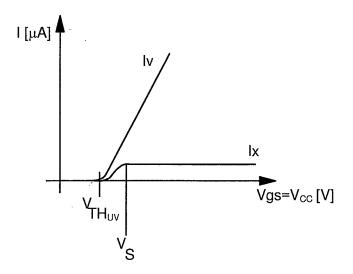

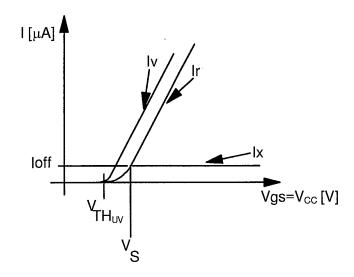

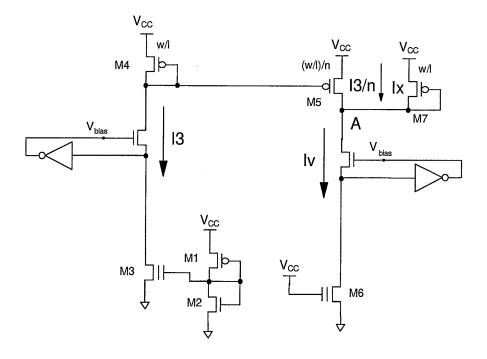

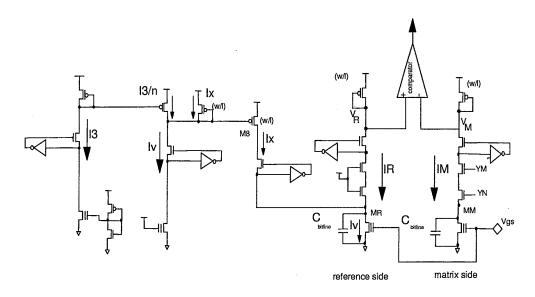

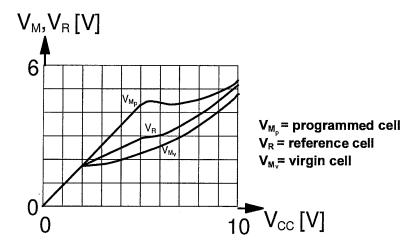

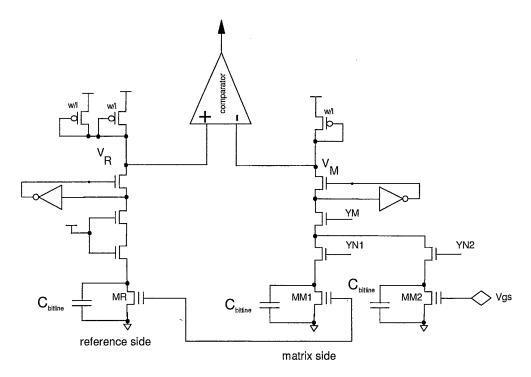

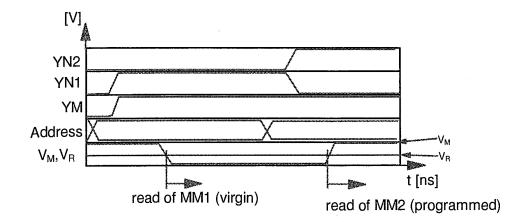

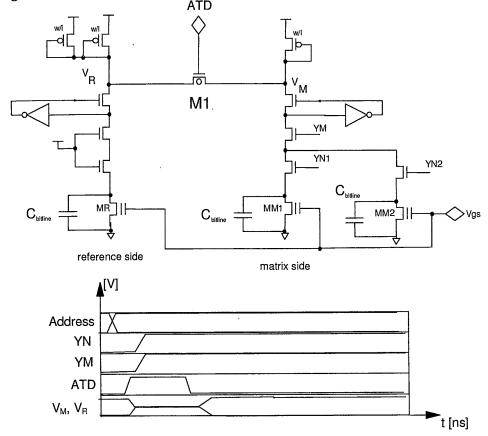

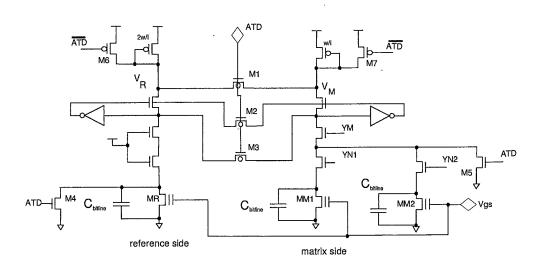

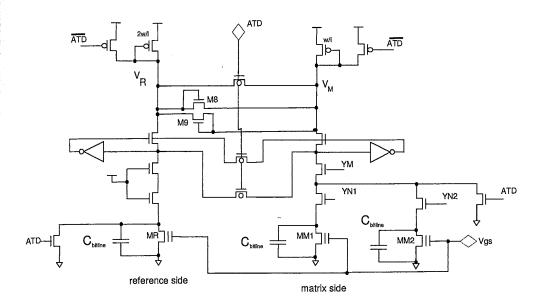

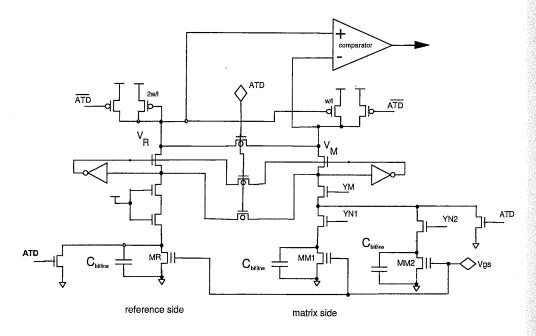

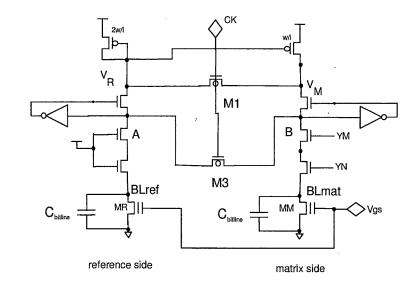

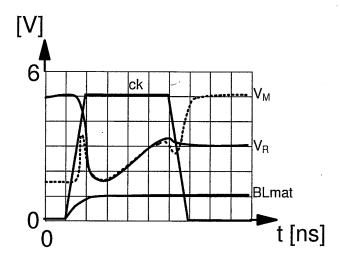

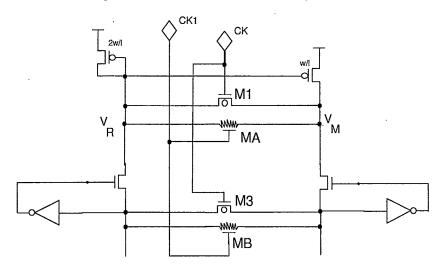

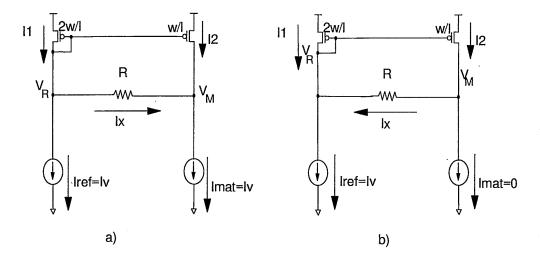

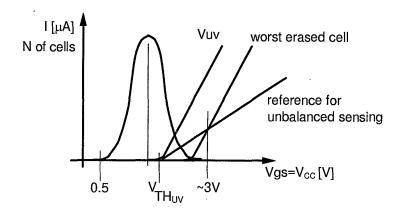

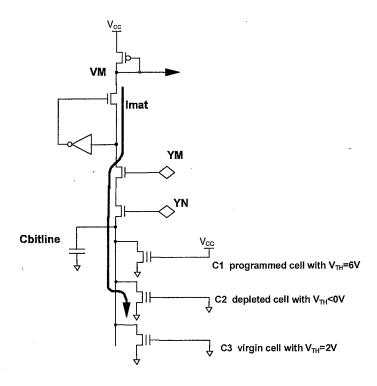

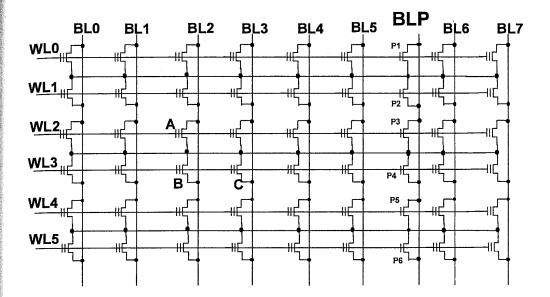

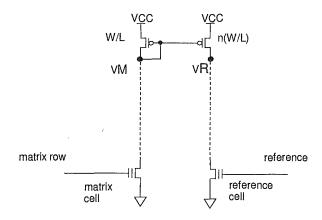

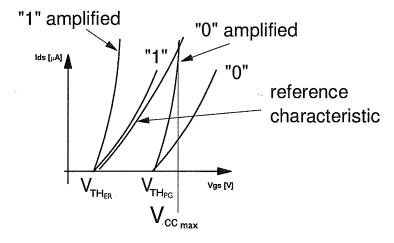

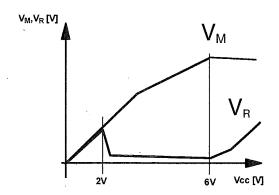

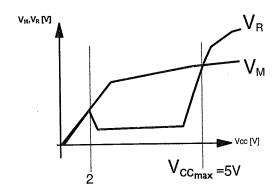

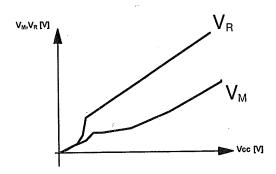

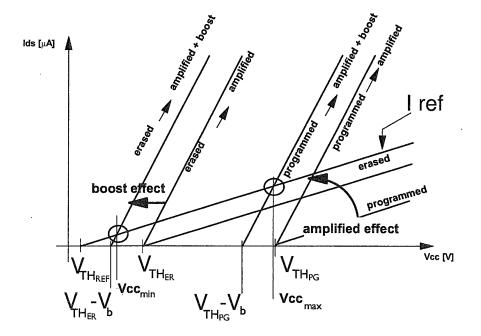

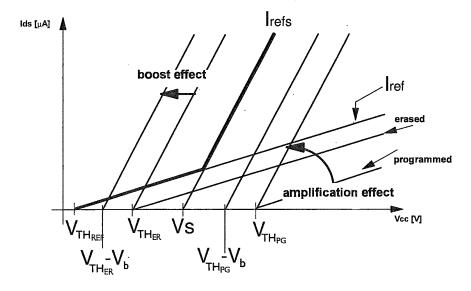

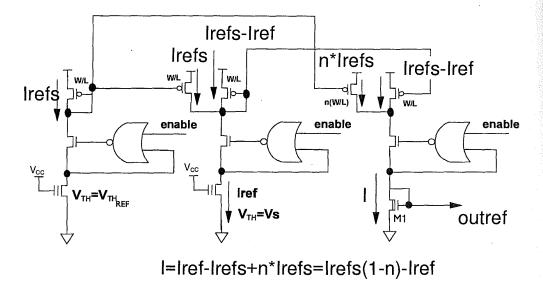

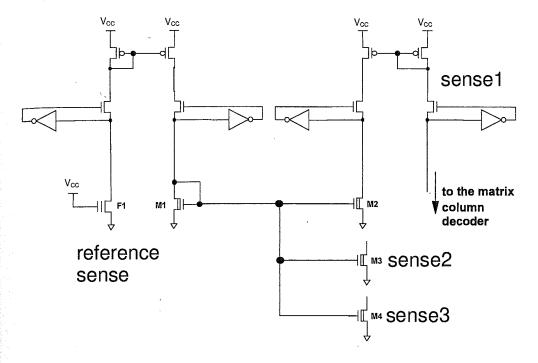

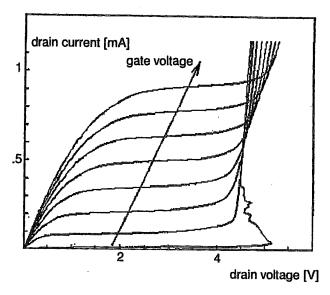

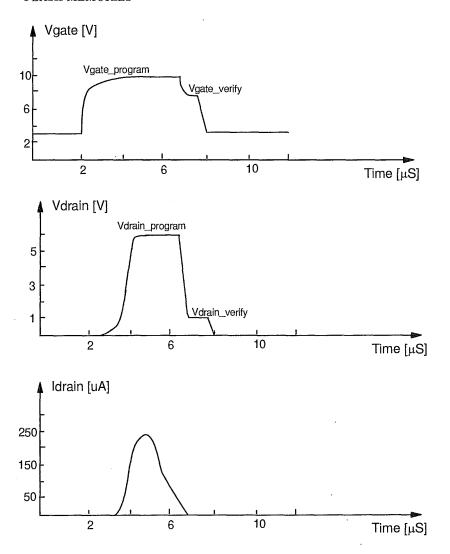

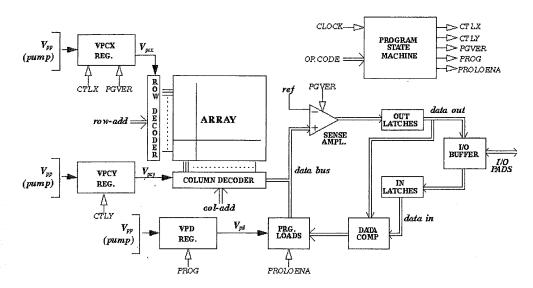

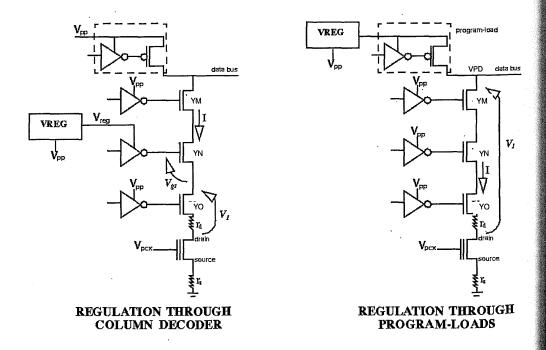

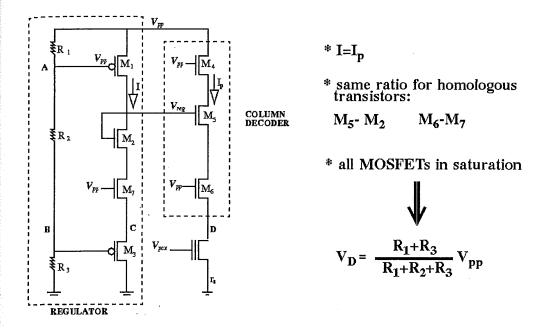

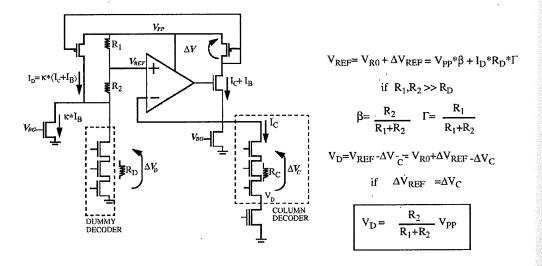

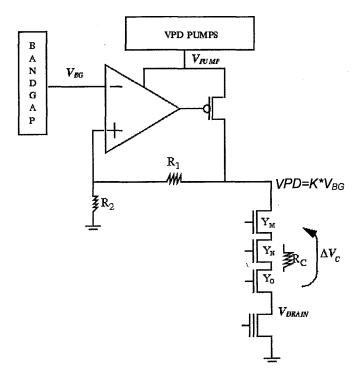

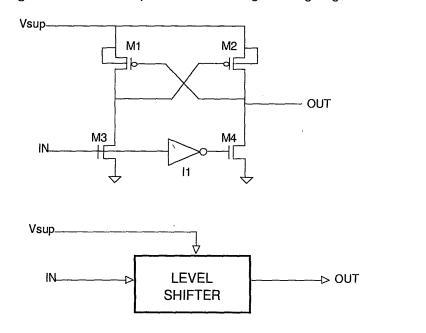

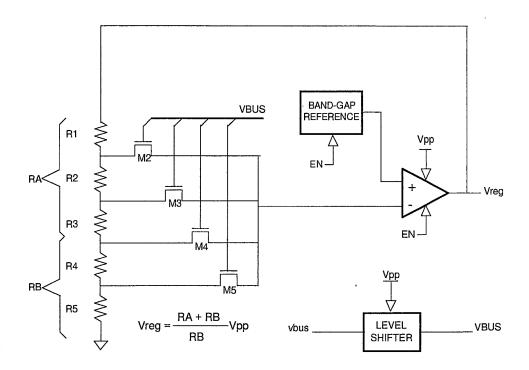

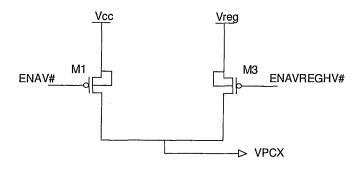

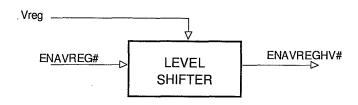

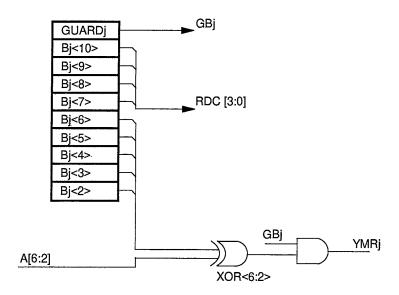

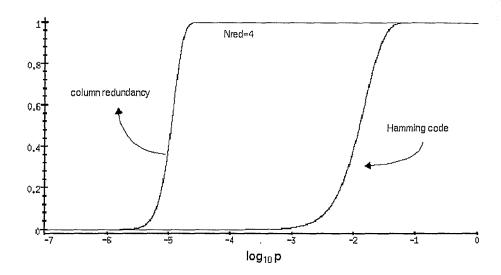

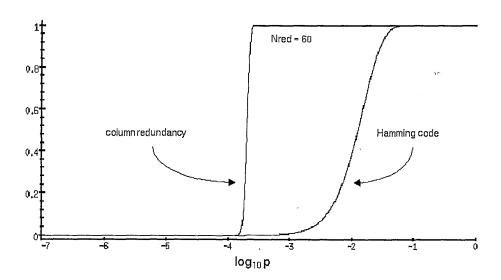

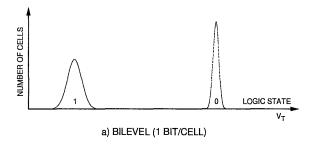

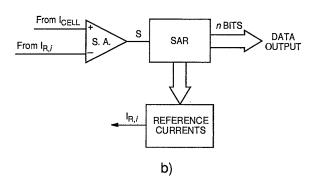

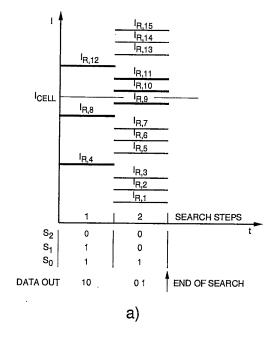

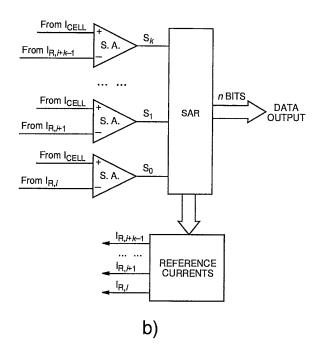

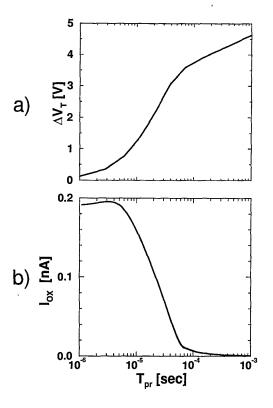

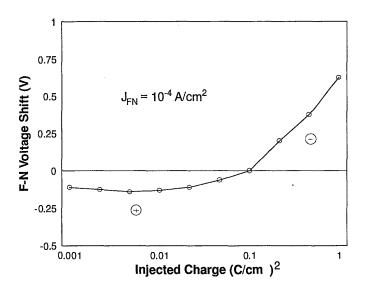

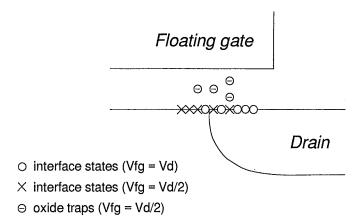

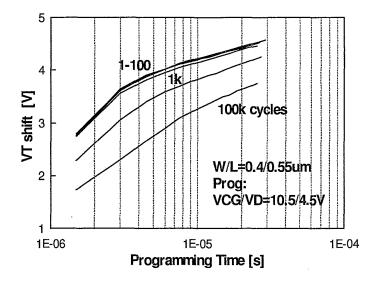

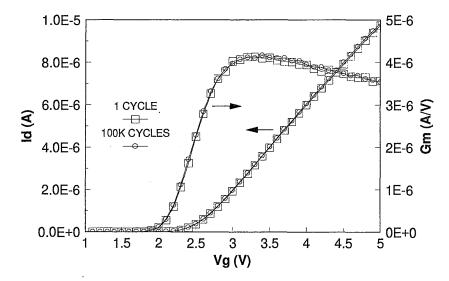

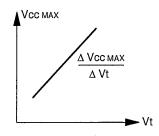

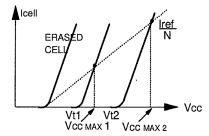

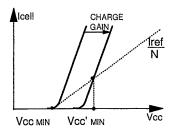

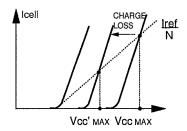

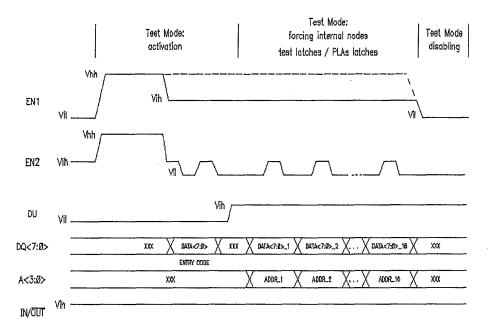

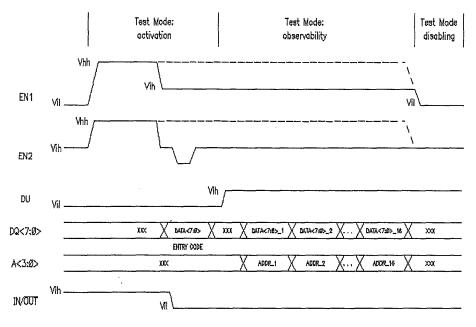

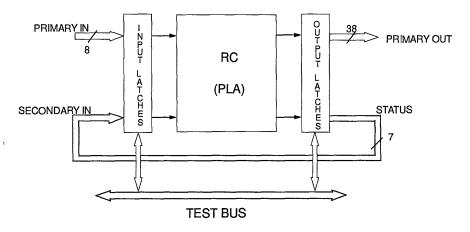

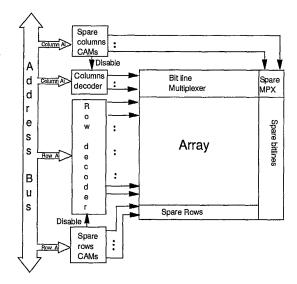

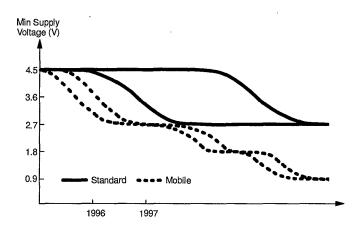

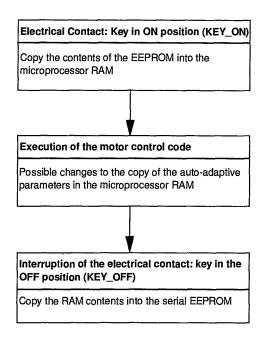

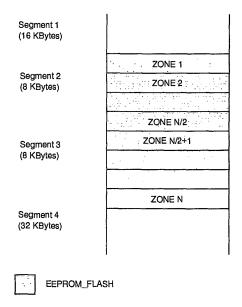

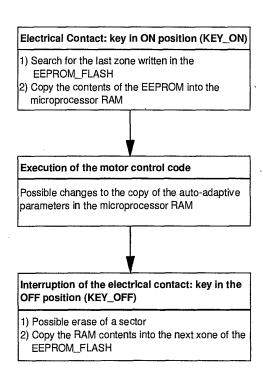

Low voltage requirements. To reduce the total power consumption, that is proportional to the square of the power supply  $V_{cc}$ , there is a general trend towards low power supplies, with two basic implications: