PTO/SB/58 (02-09)

Approved for use through 02/28/2013. OMB 0651-0064

U.S. Patent and Trademark Office; U.S. DEPARTMENT OF COMMERCE

fer the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it displays a valid OMB control number. med to as FORM PTO-1465)

### REQUEST FOR INTER PARTES REEXAMINATION TRANSMITTAL FORM

|     |          | Address to:  Mail Stop Inter Partes Reexam Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450  Address to:  Attorney Docket No.: 19968-0006RX1  Date: January 19, 2012 |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | X        | 6.256.130                                                                                                                                                                            |

| 2.  | $\times$ |                                                                                                                                                                                      |

|     |          | Fish & Richardson P.C.                                                                                                                                                               |

|     |          | 1425 K St, NW #1100, Washington, DC 20005                                                                                                                                            |

|     |          | b. The real party in interest (37 CFR 1.915(b)(8)) is: Hynix Semiconductor Inc.                                                                                                      |

| 3.  |          | a. A check in the amount of \$ is enclosed to cover the reexamination fee, 37 CFR 1.20(c)(2);                                                                                        |

|     | X        | b. The Director is hereby authorized to charge the fee as set forth in 37 CFR 1.20(c)(2) to Deposit Account No. 06-1050 ; or                                                         |

|     |          | c. Payment by credit card. Form PTO-2038 is attached.                                                                                                                                |

| 4.  | X        | Any refund should be made by check or credit to Deposit Account No. 06-1050  37 CFR 1.26(c). If payment is made by credit card, refund must be to credit card account.               |

| 5.  | X        | A copy of the patent to be reexamined having a double column format on one side of a separate paper is enclosed. 37 CFR 1.915(b)(5)                                                  |

| 6.  |          | CD-ROM or CD-R in duplicate, Computer Program (Appendix) or large table  Landscape Table on CD                                                                                       |

| 7.  |          | Nucleotide and/or Amino Acid Sequence Submission If applicable, items a. – c. are required.                                                                                          |

|     |          | a. Computer Readable Form (CRF)                                                                                                                                                      |

|     |          | b. Specification Sequence Listing on:                                                                                                                                                |

|     |          | i. CD-ROM (2 copies) or CD-R (2 copies); or                                                                                                                                          |

|     |          | c. Statements verifying identity of above copies                                                                                                                                     |

| 8.  |          | A copy of any disclaimer, certificate of correction or reexamination certificate issued in the patent is included.                                                                   |

|     |          | 1.3 and 5.7                                                                                                                                                                          |

| 9.  |          |                                                                                                                                                                                      |

| 10. | X        | A copy of every patent or printed publication relied upon is submitted herewith including a listing thereof on Form PTO/SB/08, PTO-1449, or equivalent                               |

| 11. |          | An English language translation of all necessary and pertinent non-English language patents and/or printed publications is included.                                                 |

[Page 1 of 2] This collection of information is required by 37 CFR 1.915. The information is required to obtain or retain a benefit by the public which is to file (and by the USPTO to process) an application. Confidentiality is governed by 35 U.S.C. 122 and 37 CFR 1.11 and 1.14. This collection is estimated to take 18 minutes to complete, including gathering, preparing, and submitting the completed application form to the USPTO. Time will vary depending upon the individual case. Any comments on the amount of time you require to complete this form and/or suggestions for reducing this burden, should be sent to the Chief Information Officer, U.S. Patent and Trademark Office, U.S. Department of Commerce, P.O. Box 1450, Alexandria, VA 22313-1450. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. SEND TO: Mail Stop Inter Partes Reexam, Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450.

If you need assistance in completing the form, call 1-800-PTO-9199 and select option 2.

PTO/SB/58 (02-09)

Approved for use through 02/28/2013. OMB 0651-0064

U.S. Palent and Trademark Office; U.S. DEPARTMENT OF COMMERCE

Under the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it displays a valid OMB control number.

| 12. X The attached detailed request include                                                                                                                                                                                                                                                                                                         | s at least the following items:                                                                                                                                               |                                                                                              |               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------|

| <ul> <li>a. A statement identifying each substance publications. 37 CFR 1.915(b)(3)</li> <li>b. An identification of every claim for and manner of applying the cited art to</li> </ul>                                                                                                                                                             | which reexamination is requeste                                                                                                                                               | ed, and a detailed explanation of t                                                          | he pertinency |

| 13. X It is certified that the estoppel provision                                                                                                                                                                                                                                                                                                   | ons of 37 CFR 1.907 do not proh                                                                                                                                               | ibit this reexamination. 37 CFR 1                                                            | .915(b)(7)    |

| 14. \( \) a. It is certified that a copy of this required 37 CFR 1.33(c). The name and address of the party KILPATRICK TOWNSENI                                                                                                                                                                                                                     | y served and the date of service                                                                                                                                              |                                                                                              | ded in        |

| TWO EMBARCADERO C                                                                                                                                                                                                                                                                                                                                   | ENTER, 8TH FLOOR                                                                                                                                                              |                                                                                              |               |

| SAN FRANCISCO, CA 94                                                                                                                                                                                                                                                                                                                                | 1111                                                                                                                                                                          |                                                                                              |               |

| Date of Service:                                                                                                                                                                                                                                                                                                                                    | January 19, 2012                                                                                                                                                              | ; or                                                                                         |               |

| b. A duplicate copy is enclosed becaumade to serve patent owner is atta                                                                                                                                                                                                                                                                             |                                                                                                                                                                               | s not possible. An explanation of                                                            | the efforts   |

| 15. Third Party Requester Correspondence A                                                                                                                                                                                                                                                                                                          | ddress: Direct all communicatio                                                                                                                                               | ns about the reexamination to:                                                               |               |

| X The address associated with Custo                                                                                                                                                                                                                                                                                                                 | omer Number:                                                                                                                                                                  | 26171                                                                                        |               |

| OR Firm or Individual Name                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                               |                                                                                              |               |

|                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                               |                                                                                              |               |

| Firm or Individual Name                                                                                                                                                                                                                                                                                                                             | State                                                                                                                                                                         | Zip                                                                                          |               |

| Firm or Individual NameAddress                                                                                                                                                                                                                                                                                                                      | State                                                                                                                                                                         | Zip                                                                                          |               |

| Firm or Individual NameAddress  City  Country                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                               | Zip                                                                                          |               |

| Firm or Individual NameAddress  City  Country  Telephone                                                                                                                                                                                                                                                                                            | Email                                                                                                                                                                         |                                                                                              |               |

| Firm or Individual Name  Address  City  Country  Telephone  16. The patent is currently the subject of a. Copending reissue Application b. Copending Interference No C. Copending Interference No d. Copending litigation styled:                                                                                                                   | Email the following concurrent proceetion No. Control No.                                                                                                                     | ding(s):                                                                                     |               |

| Firm or Individual Name  Address  City  Country  Telephone  16.                                                                                                                                                                                                                                                                                     | Email the following concurrent proceetion No. Control No.                                                                                                                     | x Semiconductor                                                                              |               |

| Firm or Individual Name  Address  City  Country  Telephone  16.                                                                                                                                                                                                                                                                                     | Email  the following concurrent proceed tion No.  Control No.  Innovation, LLC v. Hynitation No.  t Northern Dist of IL Case may become public. Credit                        | x Semiconductor se# 1:11-cv-04356 c card information should not zation on PTO-2038.          | be            |

| Firm or Individual Name  Address  City  Country  Telephone  16. The patent is currently the subject of a. Copending reissue Application b. Copending reexamination C. Copending Interference No d. Copending litigation styled:  Cascades Computer  Inc. in U.S. Dist Cour  WARNING: Information on this form included on this form. Provide credit | Email  i the following concurrent proceed tion No.  Control No.  Innovation, LLC v. Hynit t Northern Dist of IL Case of the card information and authority                    | x Semiconductor se# 1:11-cv-04356 card information should not zation on PTO-2038. 01/19/2012 | be            |

| Firm or Individual Name  Address  City  Country  Telephone  16. The patent is currently the subject of a. Copending reissue Applicate b. Copending reexamination of c. Copending Interference No d. Copending litigation styled: Cascades Computer Inc. in U.S. Dist Court                                                                          | Email  i the following concurrent proceed tion No.  Control No.  Innovation, LLC v. Hynix t Northern Dist of IL Case may become public. Credit card information and authority | x Semiconductor se# 1:11-cv-04356 c card information should not zation on PTO-2038.          | be            |

[Page 2 of 2]

### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

| In re Patent to Podlesny, et al. | ) |

|----------------------------------|---|

| U.S. Patent No.: 6,366,130       | ) |

| Issued: April 2, 2002            | ) |

| Serial No.: 09/505,656           | ) |

| Filed: February 17, 2000         | ) |

| For: HIGH SPEED LOW POWER DATA   | ) |

| TRANSFER SCHEME                  | ) |

Mail Stop Inter Partes Reexam Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

# REQUEST FOR INTER PARTES REEXAMINATION UNDER 35 U.S.C. §§ 302 and 311 AND 37 C.F.R. § 1.902 et seq.

\*\*\*REEXAMINATION REQUEST FOR PATENT ASSERTED IN LITIGATION\*\*\*

### TABLE OF CONTENTS

| OVE   | ERVIEW OF APPENDICES | 3                                                                    |

|-------|----------------------|----------------------------------------------------------------------|

| I.    | INTRODUCTION         | 4                                                                    |

| 11.   |                      | ATENT AND CLAIMS, AND REAL PARTY IN6                                 |

| ш.    | LITIGATION INVOLVE   | NG THE '130 PATENT6                                                  |

| IV.   |                      | REEXAMINATION IS REQUESTED AND PRIOR ART                             |

| v.    | OVERVIEW OF THE GI   | ROUNDS OF UNPATENTABILITY7                                           |

| VI.   |                      | BLE LIKELIHOOD THAT THE REQUESTER WILL CT TO THE CLAIMS CHALLENGED11 |

|       | A. HAR               | DEE11                                                                |

|       | В. БИЛ               | II13                                                                 |

|       | C. KOY               | /ANAGI15                                                             |

| VII.  |                      | G CITED PRIOR ART TO EVERY CLAIM FOR ION IS REQUESTED17              |

|       | A. HAR               | RDEE18                                                               |

|       | B. FUJI              | II31                                                                 |

|       | c. Koy               | /ANAGI44                                                             |

| X/YYY | CHMMADY OF CROUN     | DO DOD TIND A TENTA DIL TEN                                          |

### **OVERVIEW OF APPENDICES**

Appendix A: U.S. Patent No. 6,366,130 to Podlesny (hereinafter "Podlesny")

Appendix B1: Complaints from Pending Litigations involving U.S. Patent No. 6,366,130

Appendix B2: Select Excerpts from Prosecution History of U.S. Patent No. 6,366,130

Appendix C: European Patent No. 0 597 231 to Hardee (hereinafter "Hardee")

Appendix D: U.S. Patent No. 5,274,598 to Fujii (hereinafter "Fujii")

Appendix E: U.S. Patent No. 5,659,512 to Koyanagi (hereinafter "Koyanagi")

Appendix F: IDS Form PTO/SB/08

### I. INTRODUCTION

Pursuant to 35 U.S.C. §§ 302 and 311 and 37 C.F.R. § 1.902 et seq., inter partes reexamination is requested for U.S. Patent No. 6,366,130 ("the '130 patent'). A copy of the '130 patent is attached in Appendix A.

Requestor is aware of one presently-pending proceeding in the United States District Court for the Northern District of Illinois, in which the '130 patent has been asserted. Section III of this request provides further detail on the pending litigation involving the '130 patent. In view of the current litigation, special dispatch pursuant to 35 U.S.C. §§ 314 is respectfully requested to expedite the handling of this request and for any subsequent reexamination proceedings.

Requestor is not aware of any reexamination certificates that have issued for the '130 patent. The '130 patent is not subject to a terminal disclaimer.

In accordance with 37 C.F.R. § 1.915, as modified by The Leahy-Smith America Invents Act (HR 1249, pp.16-20; Federal Register, Vol. 76, No. 185, pp.59055-58), this Request includes the following:

- an identification of the patent by patent number and every claim for which reexamination is requested (Section II);

- a citation of the patents and printed publications which are presented to provide a showing that there is a reasonable likelihood that the requester will prevail with respect to at least one of the claims challenged in the request (Section IV);

- 3. a statement pointing out, based on the cited patents and printed publications, each showing of a reasonable likelihood that the requester will prevail with respect to at least one of the claims challenged in the request, and a detailed explanation of the pertinence and manner of applying the patents and printed publications to every claim for which reexamination is requested (Sections VI and VII);

- a copy of every patent or printed publication relied upon or referred to in paragraphs

through (3) above, accompanied by an English language translation of all the

necessary and pertinent parts of any non-English language document (Appendices C-E);

- a copy of the entire patent including the front face, drawings, and specification/claims (in double column format) for which reexamination is requested, and a copy of any disclaimer, certificate of correction, or reexamination certificate issued in the patent (Appendix A);

- a certification by the third party requester that a copy of the request has been served in its entirety on the patent owner at the address provided for in § 1.33(c)

(Certification Following Signature Page);

- 7. a certification by the third party requester that the estoppel provisions of § 1.907 do not prohibit the *inter partes* reexamination (Section II); and

- a statement identifying the real party in interest to the extent necessary for a

subsequent person filing an *inter partes* reexamination request to determine whether

that person is a privy (Section II).

The Director is hereby authorized to charge payment in the amount of \$8,800 for the *inter* partes reexamination fee specified by 37 C.F.R. § 1.20(c)(2) to Deposit Account 06-1050.

# II. IDENTIFICATION OF PATENT AND CLAIMS, AND REAL PARTY IN INTEREST

In accordance with 37 C.F.R. § 1.915(b)(1), (b)(7), and (b)(8), requester Hynix Semiconductor Inc. ("Hynix" or "Requester") requests *inter partes* reexamination of claims 1-3 and 5-7 of the '130 patent, assigned to Elbrus International Limited, Cayman Islands ("Elbrus")<sup>1</sup>. Requester certifies that the estoppel provisions of 37 C.F.R. § 1.907 do not prohibit this inter partes reexamination.

As explained below, claims 1-3 and 5-7 are unpatentable over the prior art patents and publications identified and applied in this Request. The patents and printed publications relied upon in this request, and the manner in which they are applied to the claims, present substantial new questions of patentability and show a reasonable likelihood that the Requester will prevail with respect to the claims challenged in the Request.

### III. LITIGATION INVOLVING THE '130 PATENT

The '130 patent is the subject of pending litigation. In particular, Cascades Computer Innovation, LLC ("Cascades") has asserted the '130 patent against Hynix Semiconductor Inc. in the United States District Court for the Northern District of Illinois, Case No. 1:11-cv-04356. No other parties were named as co-defendants. Hynix has waived service of the complaint and its answer is due on January 19, 2012. A copy of the complaint is included in Appendix B1.

# IV. CLAIMS FOR WHICH REEXAMINATION IS REQUESTED AND PRIOR ART REFERENCES APPLIED

Reexamination is requested for claims 1-3 and 5-7 of the '130 patent in view of the following art:

European Patent Publication No. 0 597 231 to Hardee (copy provided in Appendix C) (hereinafter "Hardee");

<sup>&#</sup>x27;Assignee listed on the US 6,366,130 patent: Elbrus International Limited, George Town Grand Cayman (KY). Appendix A at page 1. Assignee listed on the USPTO Assignment Database: Elbrus International Limited, P.O. BOX 265, George Town Grand Cayman, Cayman Island. In the Complaint for Patent Infringement, the plaintiff, Cascades Computer Innovation LLC stated that "Cascades owns the exclusive license and right to sue for past, present and future infringement of the '130 patent." Appendix B1 at page 2.

- U.S. Patent No. 5,274,598 to Fujii (copy provided in Appendix D) (hereinafter "Fujii"); and

- 3. U.S. Patent No. 5,659,512 to Koyanagi (copy provided in Appendix E) (hereinafter "Koyanagi").

Each of the above references is listed on IDS Form PTO/SB/08 provided in Appendix F.

These references independently qualify as prior art under 35 U.S.C. § 102. Specifically,

Hardee qualifies as prior art under 35 U.S.C. § 102(b) because Hardee issued was published on

May 18, 1994, which is more than one year prior to the earliest possible effective February 17,

1999 filing date of the '130 patent.

Fujii qualifies as prior art under 35 U.S.C. § 102(b) because Fujii issued as a patent on December 28, 1993, which is more than one year prior to the earliest possible effective February 17, 1999 filing date of the '130 patent.

Koyanagi qualifies as prior art under 35 U.S.C. § 102(b) because Koyanagi issued as a patent on August 19, 1997, which is more than one year prior to the earliest possible effective February 17, 1999 filing date of the '130 patent.

None of the references were considered during prosecution of the '130 patent.

#### V. OVERVIEW OF THE GROUNDS OF UNPATENTABILITY

The '130 patent is directed to an electronic circuit configured to enable data transfer with relatively high speed and low power consumption. '130 patent at 2:34-38. The '130 patent attributes its improved speed and power characteristics to pre-charging of a differential bus and a differential data bus. Specifically, data buses are pre-charged to voltage levels prior to data transfer operations. Then, when data transfer is desired, the pre-charged voltage levels on opposing differential buses are each changed in the opposite manner, yielding a differential voltage level that represents data to be transferred. In this process, relatively modest voltage level changes are quickly and efficiently imparted on each data bus, with the resulting opposite but marginal changes reflecting a differential of sufficient magnitude to yield perceptible and transferable data.

Against this backdrop, the basic concept of pre-charging bus lines was itself recited by claims of the '130 patent. This feature was highlighted by applicants during original prosecution when seeking to distinguish prior art, and indeed, it was relied upon by that original Examiner as

the sole basis for allowing the claims of the '130 patent. Appendix B2 at page 24, Notice of Allowance mailed in Application No. 09/505,656 on February 22, 2001.

Below, additional details are provided regarding structure and function disclosed by the '130 patent, with reference to its specification and figures, despite the fact that claims of the patent were allowed based on pre-charging of the data buses alone.

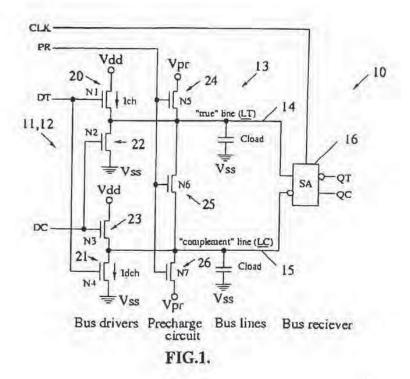

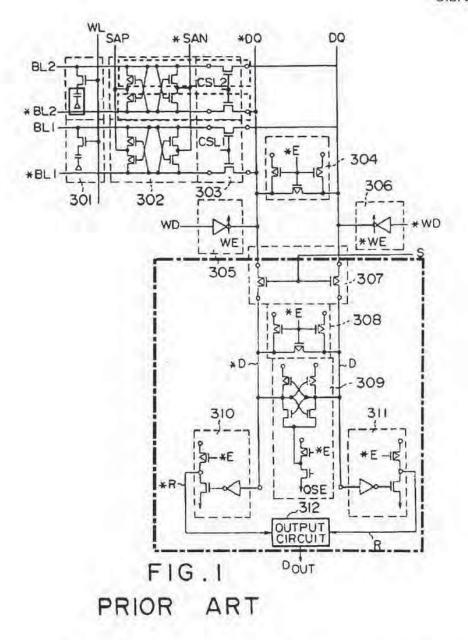

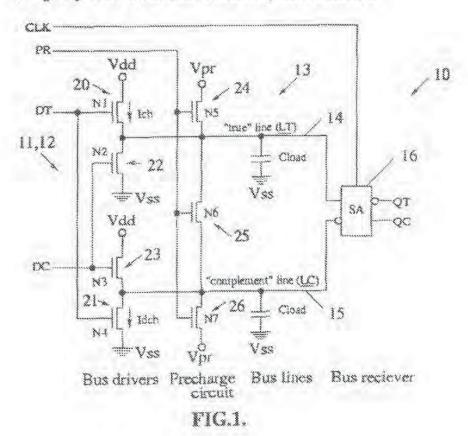

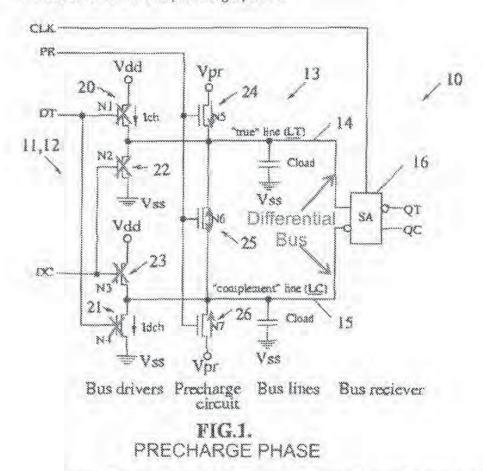

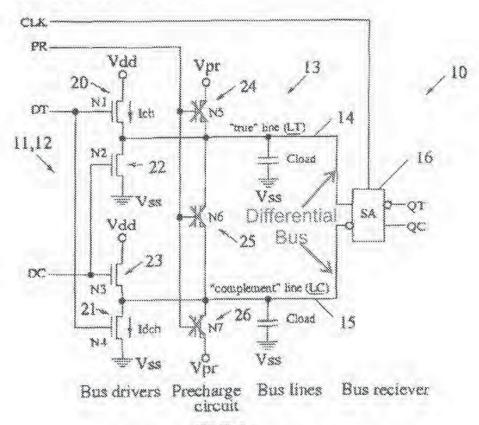

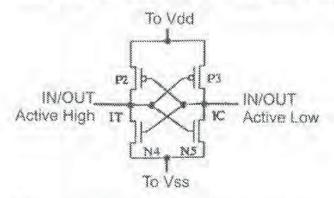

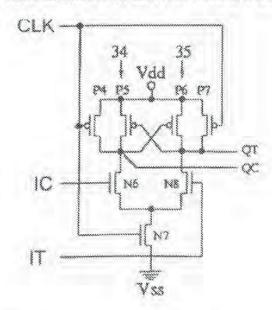

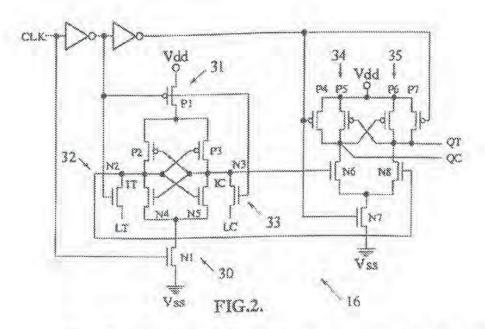

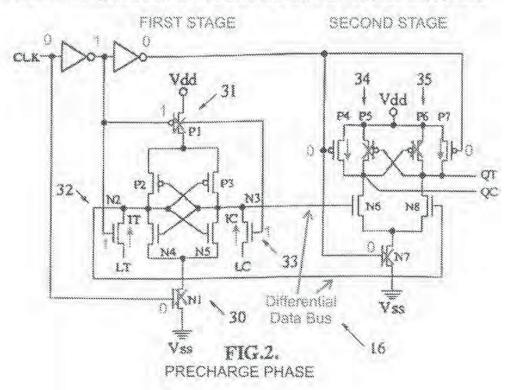

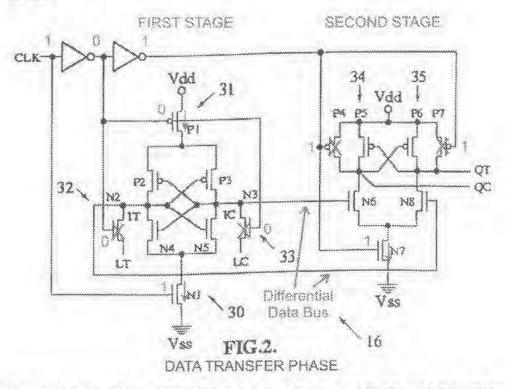

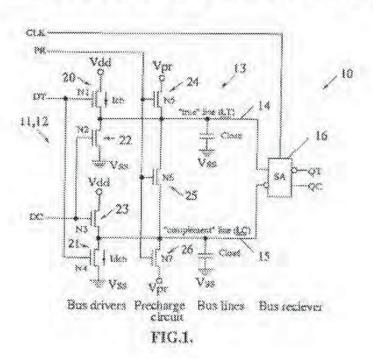

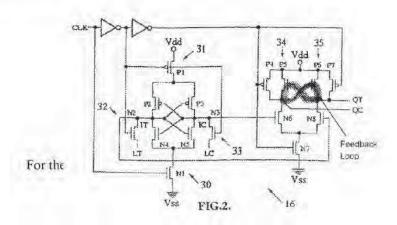

Structurally, the '130 patent uses just two figures to illustrate an electronic circuit responsible for the pre-charging and claimed functionality. FIG. 1 provides an overview of the complete electronic circuit, and FIG. 2 shows details relating to a particular aspect of FIG. 1, namely its sensing amplifier element 16. Below, FIG. 1 is reproduced for convenient visual reference.

As indicated by labels applied on the bottom of the drawing itself, FIG. 1 shows bus drivers, a precharge circuit/source, and bus lines (i.e., a differential bus) coupled to the bus drivers and to the voltage precharge circuit/source. Also coupled to the bus lines is a latching

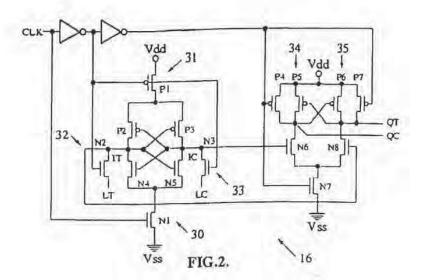

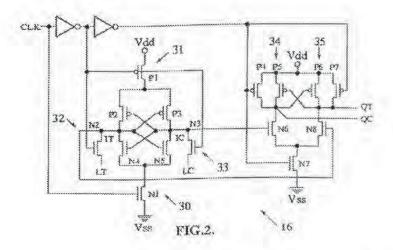

sense amplifier 16, the contemplated details of which are illustrated by FIG. 2, reproduced below.

In particular, in FIG. 2, latching sense amplifier 16 is shown to include a cross-coupled latch having internal nodes IT and IC coupled to differential data buses, and complementary outputs QT and QC.

Functionally, two phases of operation are describe for the bus driver circuit of FIG. 1, and two analogous but opposite phases of operation for the sense amplifier shown by FIG. 2. With respect to each, the two phases is identified as (1) a bus precharge phase and (2) a data transfer phase, but as indicated, they are opposite/offset to promote data propagation through the circuit. Below, the phases are described, first with respect to components of the bus driver circuit shown in FIG. 1 and then with respect to components of the sense amplifier shown by FIG. 2.

During the precharge phase of the bus driver circuit shown by FIG. 1:

[t]he true phase driver on transistors 20 and 21 and the complement phase driver on transistors 22 and 23 are in high impedance state and both bus lines are equalized and precharged to a potential Vpr (buses precharging voltage level) through the turned on transistors 24, 25 and 26. '130 patent at 2:18-22.

Thereafter, during the data transfer phase of the bus driver circuit shown by FIG. 1:

[o]ne of the drivers is pulled up and charges the appropriate bus line from the precharged level Vpr toward a more positive Vdd – Vt (where Vt is the threshold voltage of the pull up NMOS transistor of the driver). At the same time, the other driver is pulled down and discharges the opposite bus line from the precharged

level Vpr towards a more negative level Vss (ground). This provides a differential voltage: +dV and -dV from the precharging level Vpr between true and complement bus lines. Id. at 2:25-33.

During the precharge phase of the sense amplifier circuit shown by FIG. 2 (which occurs when the bus driver circuit is operating in its data transfer phase), the control input CLK is low, such that the differential voltage on bus lines 14 and 15:

passes to the internal nodes IT (positive binary single-rail internal point of the sensing amplifier) and IC (negative binary single-rail data input phase internal 55 point of the sensing amplifier) of the latched amplifier. The output nodes of both dynamic gates are precharged to Vdd and the complementary outputs QT (true phase of dual-rail data output signal) and QC (complement phase of dual-rail output data signal) of the sensing amplifier become high. Id. at 2:52-59.

And, during the data transfer phase of the sense amplifier circuit shown by FIG. 2 (which occurs when the bus driver circuit is operating in its precharge phase), the control input CLK is high, such that the differential voltage passed to the internal nodes IT and IC is received and passed by the cross-coupled amplifier

to power buses (transistors 30 and 31 are turned on) and [the cross-coupled amplifier] begins to amplify the low voltage swings of the internal nodes IT and IC to full logic levels. The output node of one of the dynamic gates is discharged to ground and the appropriate output QT or QC of the sensing amplifier becomes low. Id. at 2:64-3:3.

During original prosecution, the handling Examiner rejected the original claims based on U.S. Patent No. 5,598,371 ("Lee") in view of U.S. Patent No. 6,184,722 ("Hayakawa"). Indeed, allowance was not secured until applicants amended the claims to recite pre-charging of bus lines, nor until they presented arguments suggesting that this general concept was missing from within the prior art. The Examiner's reasons for allowance, reproduced below, make clear that allowance was secured on this basis alone:

applicants' arguments have been fully considered and deemed to be persuasive. The present invention teaches precharging the buses to a specific level between ground and Vdd, which results in equal, low differential Voltage swings, providing increased speed of data transfer. The prior art of Lee et al. does not teach such precharging buses as described above. Appendix B2 at page 24, Notice of Allowance mailed in Application No. 09/505,656 on February 22, 2001.

Despite the Examiner's determination that these features are absent from the prior art, a close inspection reveals that these features relate to very basic differential voltage amplification techniques that have been well-known among engineers designing sensing amplifier circuits for memory systems.

Because these features were well-known prior to the '130 patent, as demonstrated by the references applied in this Request, which show the features of claims 1-3 and 5-7 of the '130 patent, Requester requests reexamination of the '130 patent and cancellation of the challenged claims.

## VI. THERE IS A REASONABLE LIKELIHOOD THAT THE REQUESTER WILL PREVAIL WITH RESPECT TO THE CLAIMS CHALLENGED

The legal standard for ordering *inter partes* reexamination was recently modified by The Leahy-Smith America Invents Act. See HR 1249, pp.16-20; Federal Register, Vol. 76, No. 185, pp.59055-58). An *inter partes* reexamination should be granted when there is a showing that there is a reasonable likelihood that the requester will prevail with respect to at least one of the claims challenged in the request (the "reasonable likelihood" standard). This standard replaced the previously applicable "substantial new question of patentability" standard. Regardless of how this new controlling standard is interpreted and applied in the courts and the Office, the instant Request is sufficient to justify reexamination. Indeed, the grounds of rejection proposed by this Request are based on patents and printed publications and they raise substantial new questions of patentability that are reasonably likely to be upheld against the claims being challenged.

Below, Requester sets forth proposed grounds for rejection of claims 1-3 and 5-7 of the '130 patent, demonstrating why the prior art applied in the proposed grounds are reasonably likely to be adopted and sustained against these claims. Because none of the references applied in this request were considered during prosecution of the '130 patent, they also raise substantial new questions of patentability with respect to claims 1-3 and 5-7 of the '130 patent.

#### A. HARDEE

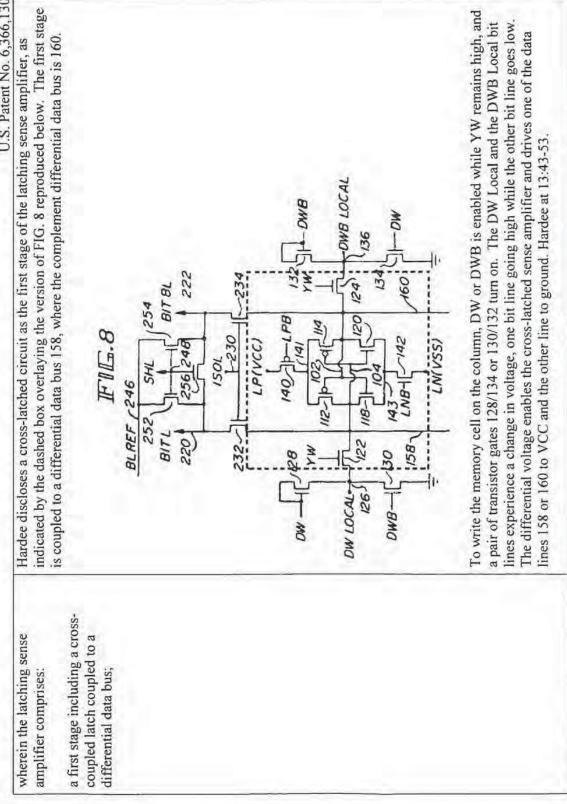

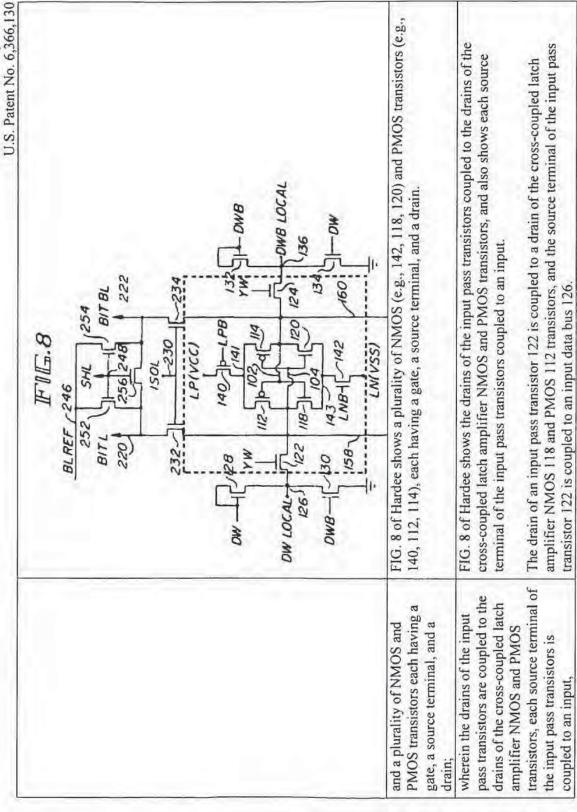

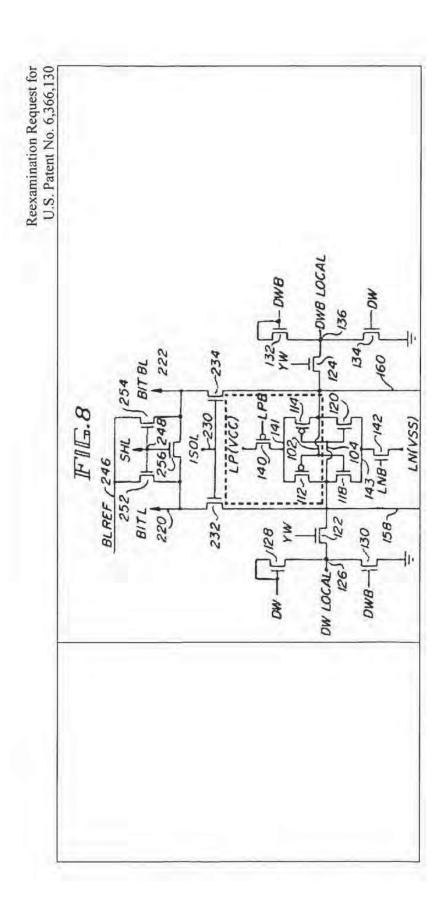

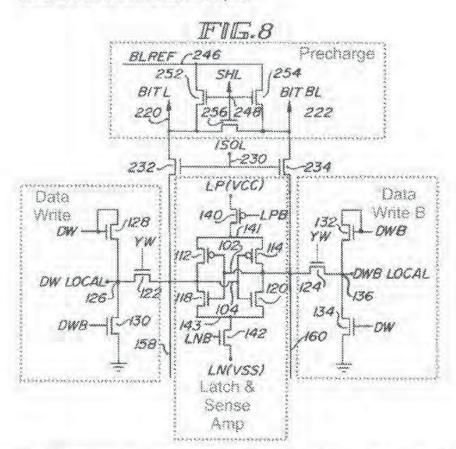

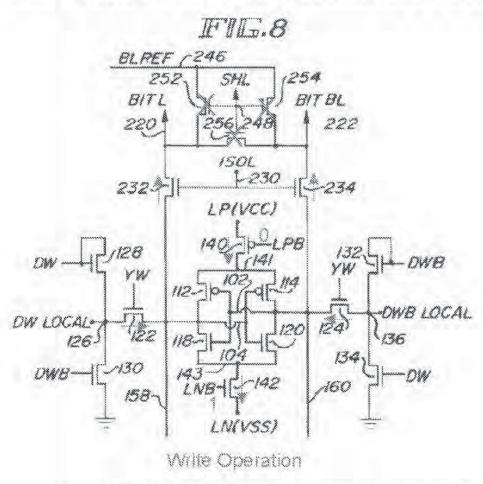

Hardee describes a memory circuit that amplifies a voltage difference between two precharged data buses during a write operation. In this manner, Hardee contemplates the concept of precharging differential buses that was deemed sufficient to justify allowance of the '130 patent claims.

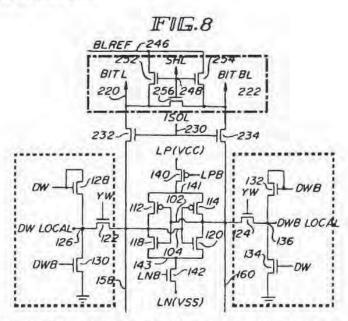

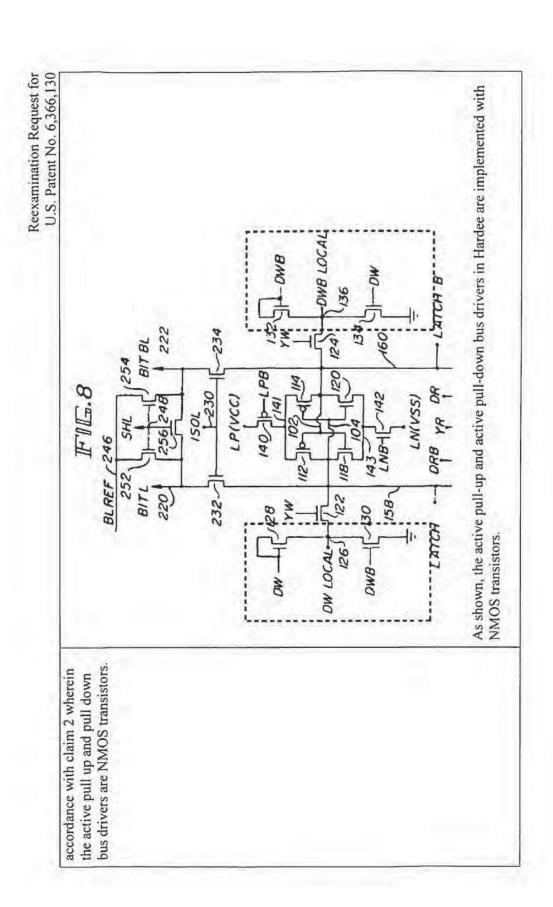

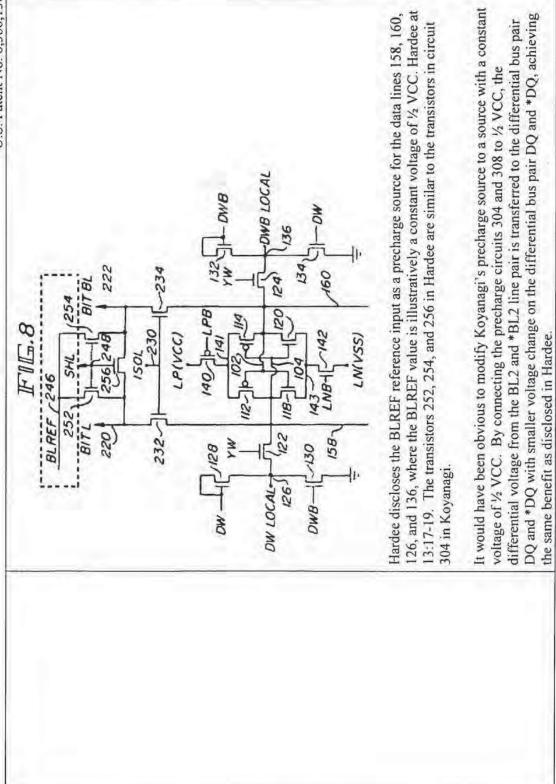

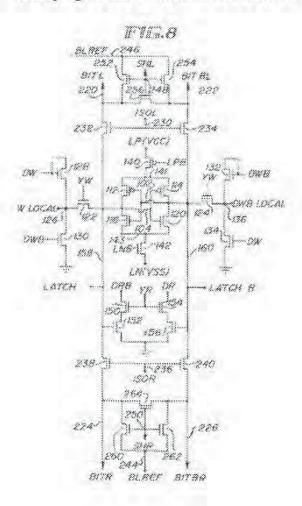

Structurally, the Hardee memory circuit as shown in FIG. 8 represents one of many columns in a memory system, where the YW signal selects the column of memory circuit to be written. The true and complement data input signals are DW and DWB, respectively, and the

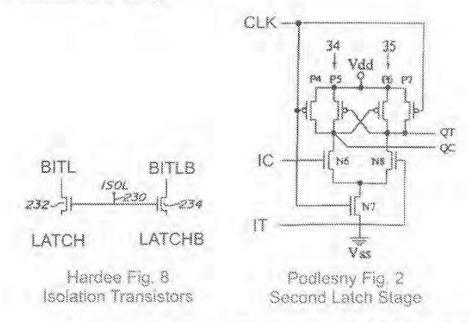

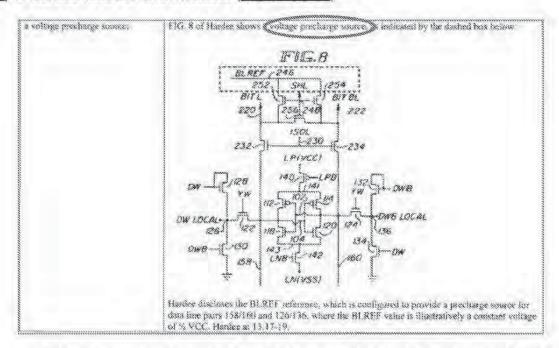

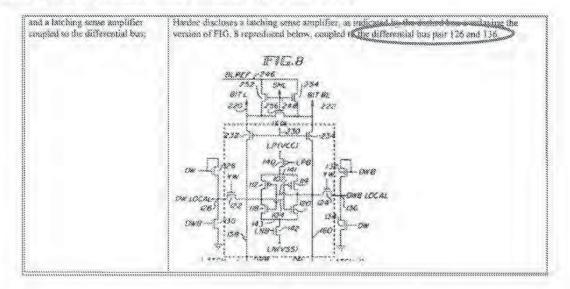

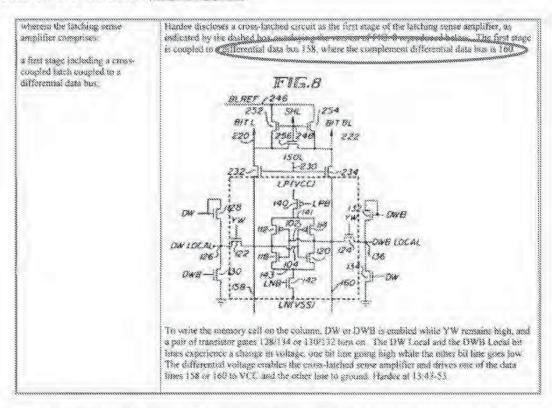

true and complement data output signals are BIT L and BIT BL, respectively, which lead to a memory cell. As shown in representative FIG. 8 reproduced below, the Hardee memory circuit includes a precharge source BLREF, a precharge circuit as enclosed in the dashed-dotted box, two bus drivers as enclosed in the dashed boxes, a cross-latched sense amplifier, and isolation transistors 232 and 234.

Functionally, prior to writing the memory cell on a column, both DW and DWB are disabled. The YW signal is enabled, resulting in the DW Local and DWB Local bit lines being coupled to the data lines 158 and 160, respectively. Upon activating precharge circuit and the isolation transistors 232 and 234, the DW Local and DWB Local bit lines and the data lines 158 and 160 are precharged to a voltage BLREF, which is illustratively a constant voltage of ½ VCC. Hardee at 13:17-19. The precharged lines are then isolated by turning off the isolation transistors.

To write the memory cell on the column, DW or DWB is enabled while YW remains high, and a pair of transistor gates 128/134 or 130/132 turn on. The DW Local and the DWB Local bit lines experience a change in voltage, one bit line going high while the other bit line goes low. The differential voltage then enables the cross-latched sense amplifier and drives one of the data lines 158 or 160 to VCC and the other line to ground. Hardee at 13:43-53. The isolation transistors 232 and 234 are coupled to the output of the data lines 158 and 160, and

controlled to pass the voltage on the data lines 158 and 160 to the BIT L and BIT BL outputs after the voltages have reached a steady state.

As described, Hardee discloses a scheme for precharging differential data line pairs to a voltage of ½ VCC, and amplifying a differential voltage across a differential data line pair when writing data to a memory cell. In doing so, Hardee discloses the features identified by the Examiner as justifying allowance of independent claim 1. This and other teachings of Hardee establish a substantial (and new) question of patentability, and they also establish a reasonable likelihood that the requester will prevail with respect to at least independent claim 1.

#### B. FUJII

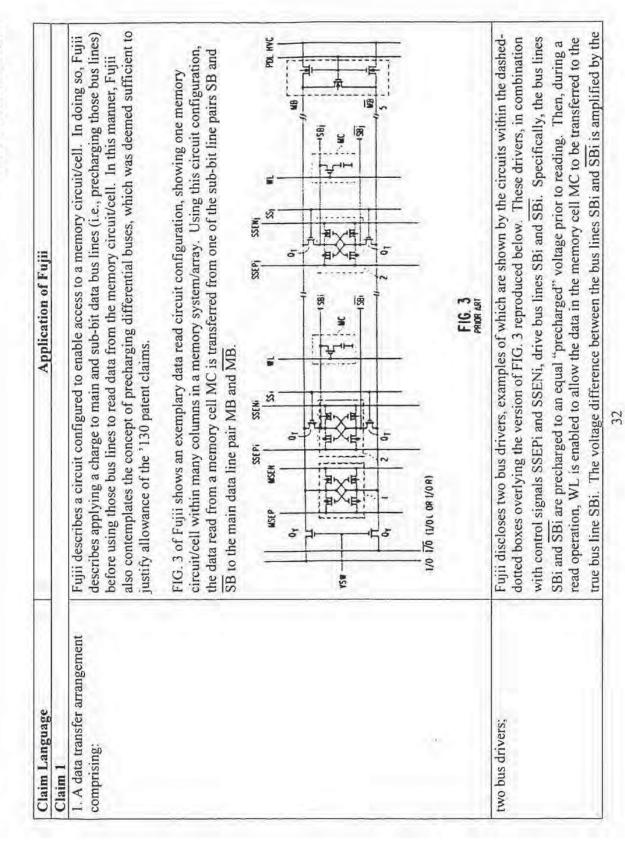

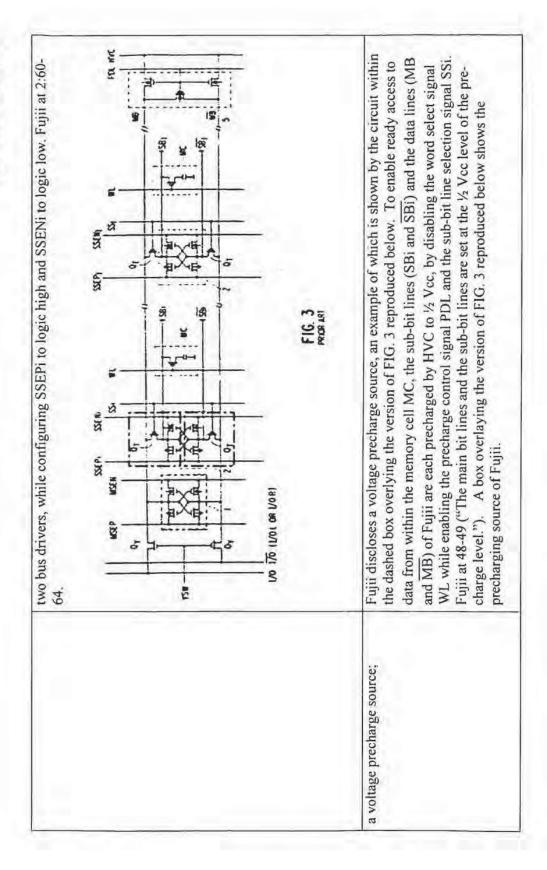

Fujii describes a circuit configured to enable access to a memory circuit/cell. In doing so, Fujii describes applying a charge to main and sub-bit data bus lines (i.e., precharging those bus lines) before using those bus lines to read data from the memory circuit/cell. In this manner, Fujii also contemplates the concept of precharging differential buses, which was deemed sufficient to justify allowance of the '130 patent claims.

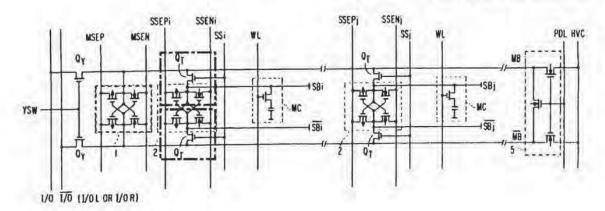

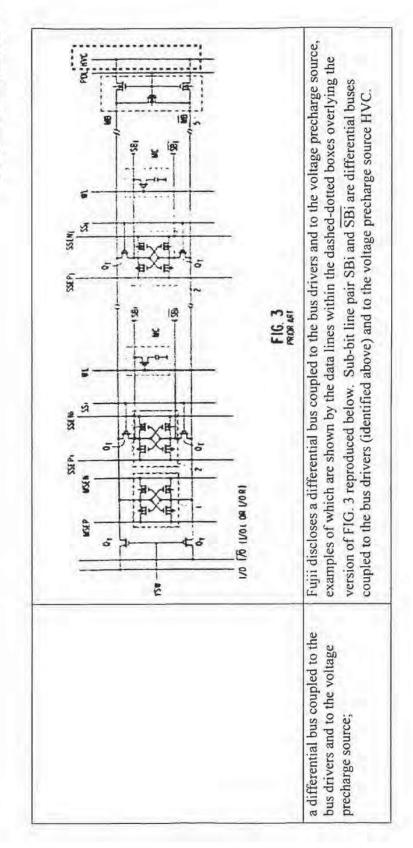

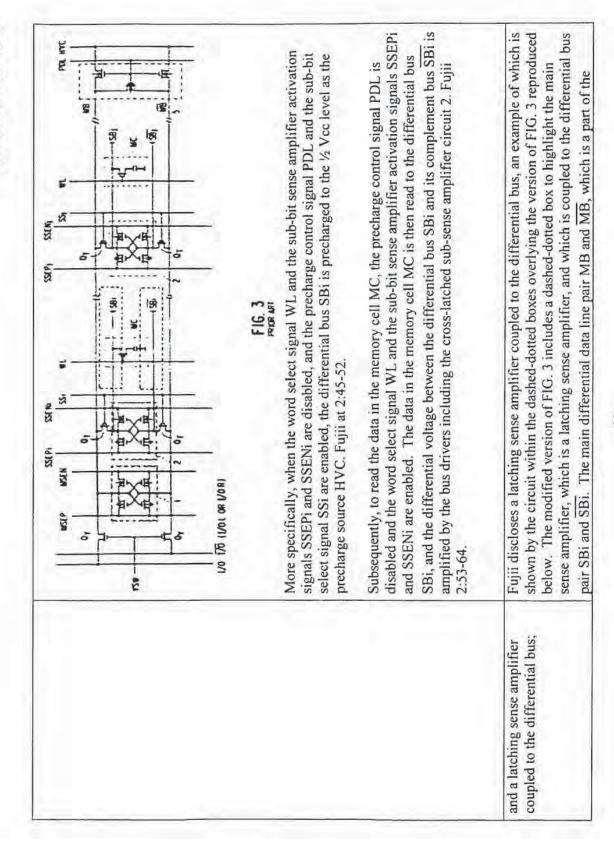

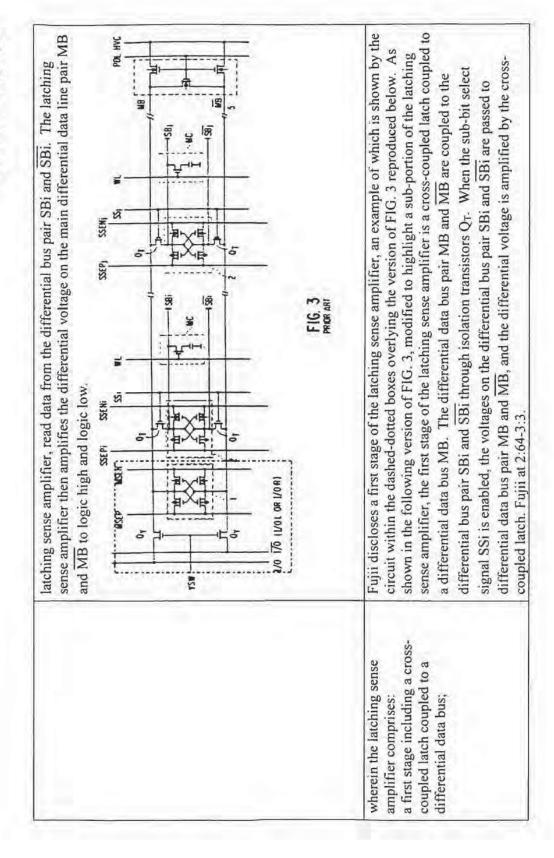

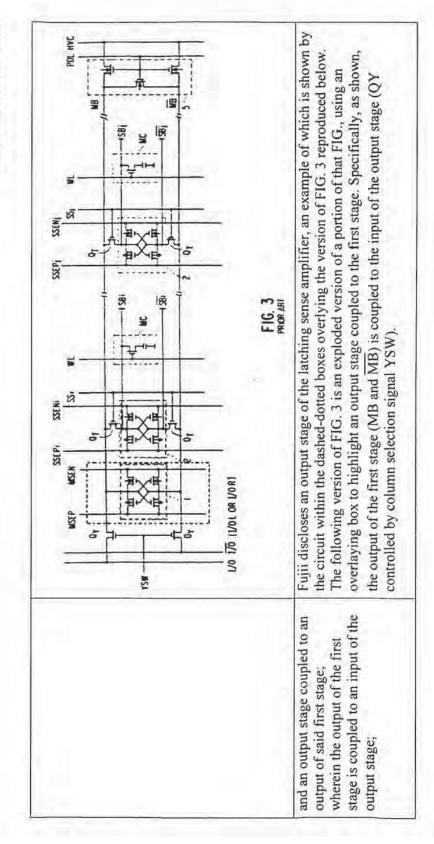

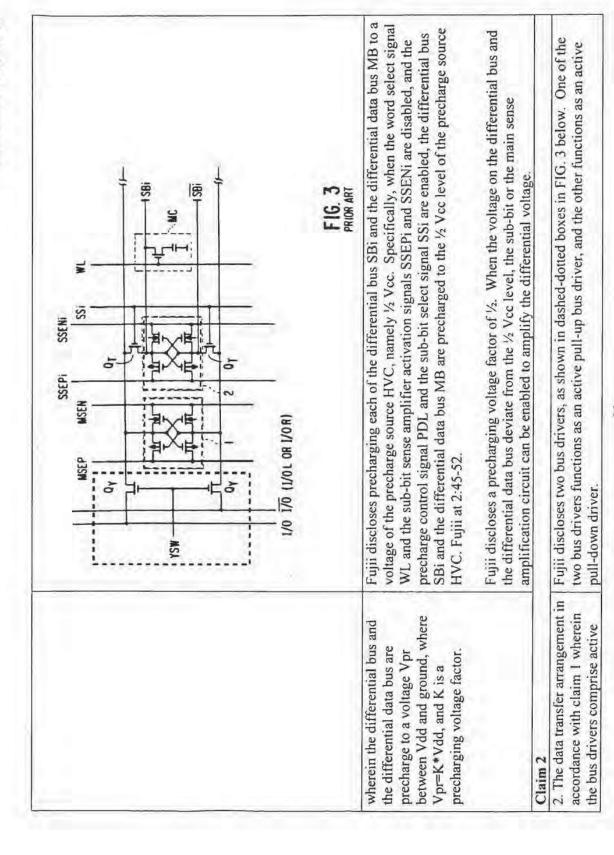

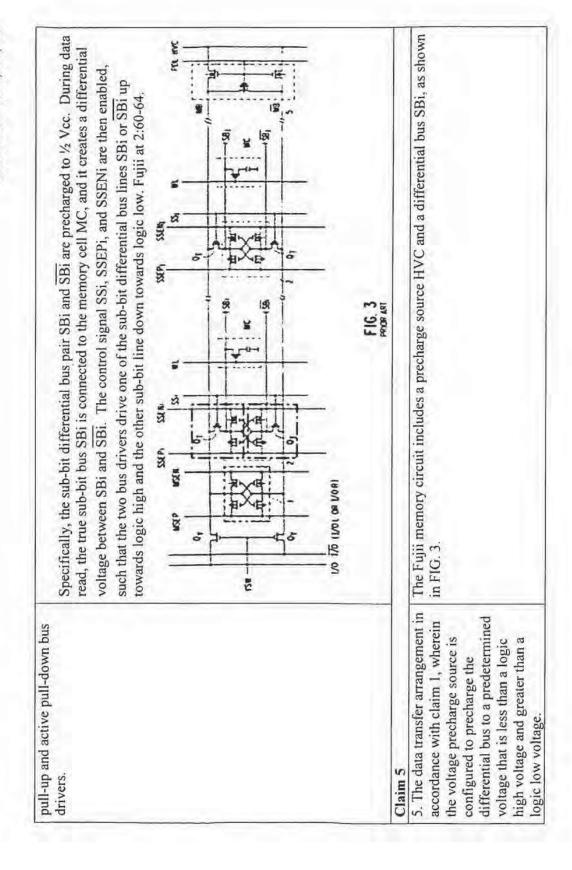

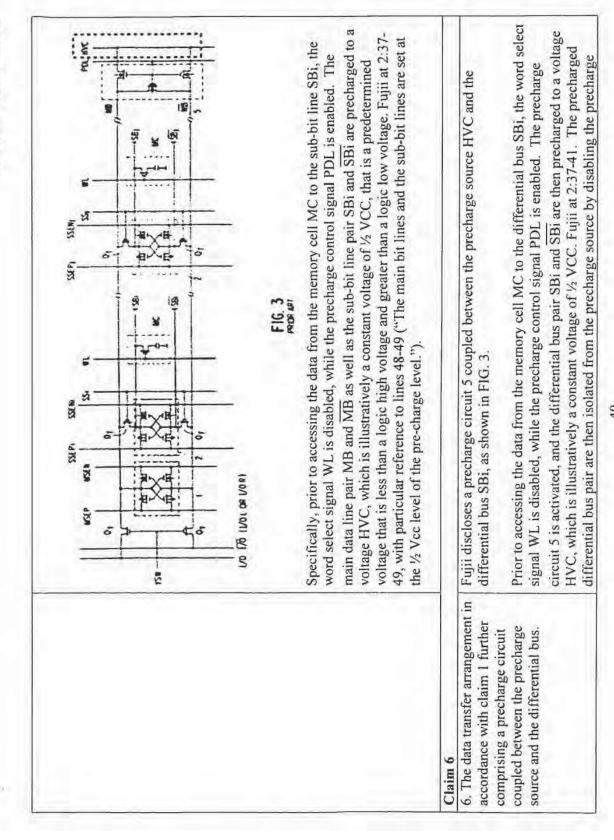

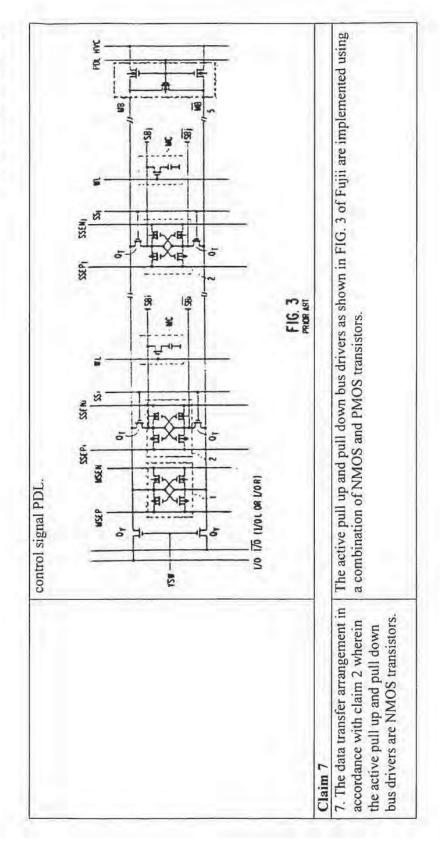

Structurally, with reference to FIG. 3 of Fujii, reproduced below, there exist several selectable memory circuits (MCs) in a memory array. Each memory circuit (MC) includes a true and complement sub-bit line (SB and  $\overline{SB}$ ) used to read data from within the memory cell (MC). When selected, the sub-bit lines SBi/ $\overline{SBi}$  for a particular memory circuit (i) may be used to communicate data from within that memory cell to main data lines (MB and  $\overline{MB}$ ), which yield memory contents through their connection at output buses I/O and  $\overline{I/O}$ . Importantly, a precharge source HVC and a precharge circuit 5 are configured to work together to precharge main data line pair MB and  $\overline{MB}$  and sub-bit lines SBi/ $\overline{SBi}$ . Also bus drivers (enclosed in the dashed-dotted boxes), a main cross-latched sense amplifier 1, and isolation transistors  $Q_Y$  and  $Q_T$  are configured to facilitate flow of precharge voltage and data to/from sub-bit data lines (SB and  $\overline{SB}$ ).

FIG. 3

Functionally, the sub-bit line selection signal SSi is enabled when access is desired to data within a corresponding a memory cell MC. Responsively, the main data line pair MB and  $\overline{\text{MB}}$  are coupled to the sub-bit line pair SBi and  $\overline{\text{SBi}}$ , where the index "i" corresponds to one of the several sub-bit line pairs able to be connected to the main data line pair, namely, the sub-bit line pair corresponding to the sub-bit line selection signal SSi.

To enable ready access to data from within the memory cell MC, the sub-bit lines (SBi and  $\overline{\text{SBi}}$ ) and the data lines (MB and  $\overline{\text{MB}}$ ) are each precharged<sup>2</sup>, by disabling the word select signal WL while enabling the precharge control signal PDL and the sub-bit line selection signal SSi. The precharged main and sub-bit lines are thereafter isolated from the precharge source by disabling the precharge control signal PDL, and they are isolated from each other by disabling the sub-bit line selection signal SSi. Fujii at 2:53-56.

The precharged sub-bit line SBi then accesses the data from the memory cell MC by enabling the word select signal WL, enabling the precharged sub-bit line SBi to experience a change in voltage reflective of the memory cell MC data contents/charge. Moreover, this change in voltage is experienced in the opposite direction on the complement sub-bit line SBi by controlling the driver control signals SSEPi and SSENi. Fujii at 2:56-64.

Ultimately, the sub-bit line selection signal SSi is again enabled to connect the main data line pair MB and  $\overline{\text{MB}}$  to the sub-bit line pair SBi and  $\overline{\text{SBi}}$ , and using the main sense amplifier

<sup>&</sup>lt;sup>2</sup> Fujii discloses "[t]he main bit lines and the sub-bit lines are set at the ½ Vcc level of the pre-charge level." Fujii at 2:48-49.

activation signals MSEP and MSEN, the differential voltage at the sub-bit line pair SBi and  $\overline{\text{SBi}}$  is passed to the main data line pair MB and  $\overline{\text{MB}}$ . Fujii 2:60-3:3.

The two isolation transistors, both identified as  $Q_Y$  are coupled to the output of the main data lines MB or  $\overline{MB}$ , and used to control passage of the voltages on the main data lines MB and  $\overline{MB}$  to the output buses I/O and  $\overline{I/O}$  after those voltages have reached a steady state.

As described, Fujii discloses a sensing amplifier circuit that precharges the main and subbit (differential) data lines to a voltage of ½ VCC. In doing so, Fujii discloses the features identified by the Examiner as justifying allowance of independent claim 1, establishing a substantial (and new) question of patentability, and also establishing a reasonable likelihood that the requester will prevail with respect to at least independent claim 1.

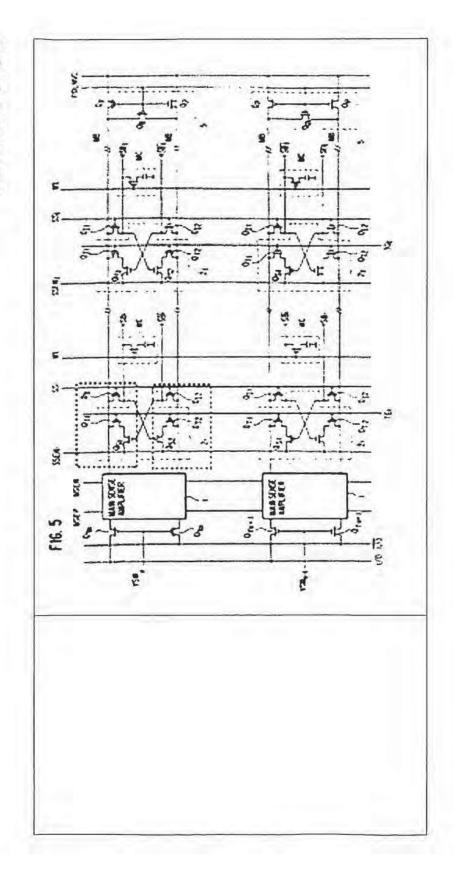

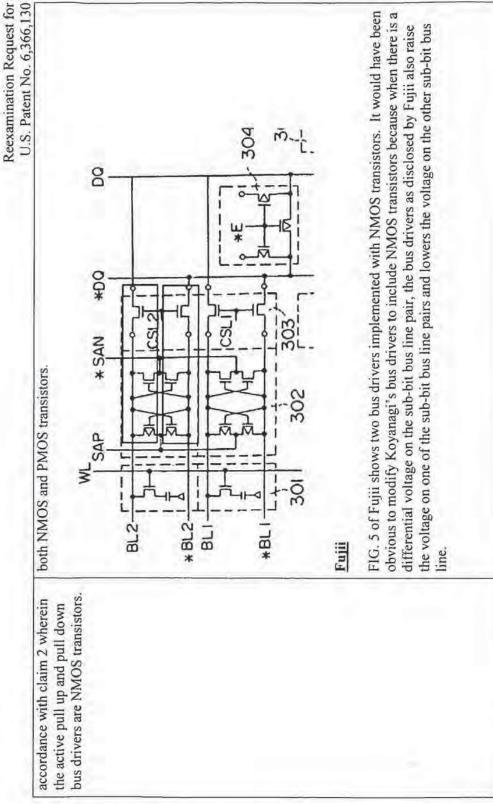

#### C. KOYANAGI

Koyanagi describes a circuit configured to enable data to be read from a memory circuit/cell. Koyanagi, like other prior art described above, discloses precharging of differential buses used to communicate the data from the memory cell to an output. In particular, in the following paragraphs, data line pairs DQ/\*DQ and D/\*D are each precharged. In this manner, Koyanagi contemplates the concept of precharging differential buses that was deemed sufficient to justify allowance of the '130 patent claims.

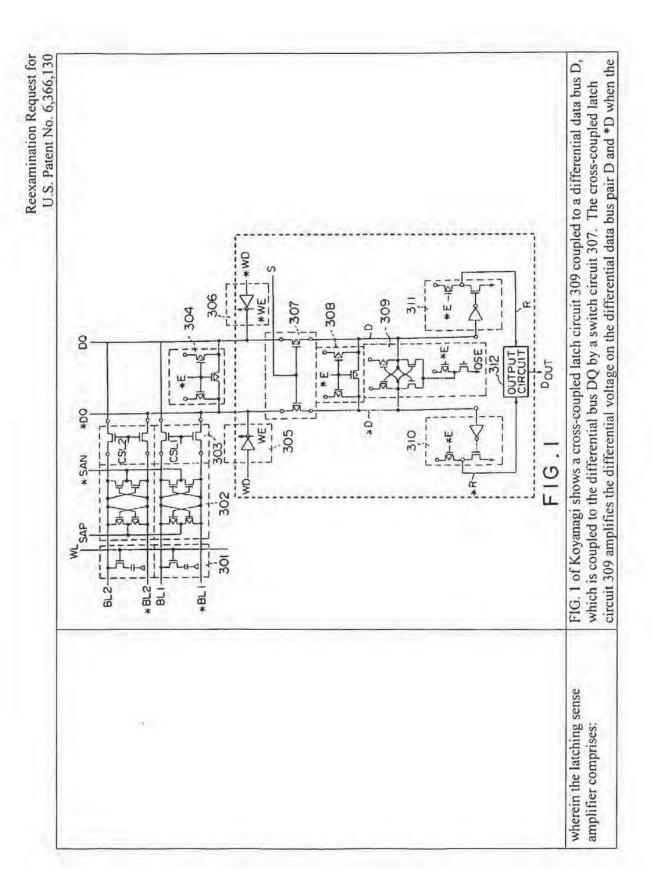

Structurally, and in accord with the FIG. 1 illustration of two memory circuits/cells in a memory system/array, reproduced below, Koyanagi describes a data read circuit which includes paired bit lines BL1/\*BL1 and BL2/\*BL2 that may be selected to enable a read of a corresponding memory circuit/cell, where an example is enclosed in a solid-lined box. Indeed, each exemplary bit line pair (e.g., BL1/\*BL1 and BL2/\*BL2) of the data read circuit described by Koyanagi couple both to a corresponding memory cell, and to the differential data line pair (DQ and DQ\*). The data read circuit includes a precharge source and circuits 304 and 308 for precharging the differential data line pairs DQ/\*DQ and D/\*D, respectively, to a high-impedance value (e.g. Vcc). Koyanagi also describes two bus drivers (within the dashed boxes), a latching sense amplifier (within the dashed-dotted box), and isolation circuits 310/311.

Functionally, prior to reading the data from a memory cell, both CSL1 and CSL2 are disabled to isolate the bit line pairs BL1/\*BL1 and BL2/\*BL2 from data line pair DQ/\*DQ. The \*E signal is then enabled, such that the voltage sources coupled to circuits 304 and 308 are

respectively applied as precharging voltages to the separated<sup>3</sup> data line pairs DQ/\*DQ and D/\*D. The precharging voltage is illustratively a constant voltage of VCC. Koyanagi at 1:54-58.

When the Koyanagi circuit reads data from an exemplary bit line pair BL2/\*BL2 in FIG. 1, the word select signal WL is enabled, and data from the memory cell is coupled to the true bit line BL2. The control signals SAP and \*SAN are then controlled to logic high and low, respectively, which enables the bus driver 302 to raise the voltage on one bit line of the bit line pair BL2 or \*BL2 and to lower the voltage on the other bit line. Koyanagi at 1:40-45. CSL2 is then enabled to connect the bit line pair BL2/\*BL2 to the precharged data line pair DQ/\*DQ, which induces a voltage difference between the data line pair DQ/\*DQ. Koyanagi at 1:60:64. Control signal S is then enabled to connect the data line pair DQ/\*DQ to the precharged data line pair D/\*D, which induces a voltage difference between the data line pair DQ/\*DQ.

The differential voltage then enables the cross-latched sense amplifier 309 and connects one of the data lines D or \*D to ground and the other line to VCC. Consequently, the voltage on one of the data lines D or \*D lowers from VCC to ground, while the voltage on the other data line stays constant at VCC. Koyanagi at 2:15-17. The isolation circuits 310/311 are coupled to the output of the data lines D and \*D, and controlled to pass the voltage on the data lines D and \*D to the R and \*R outputs after the voltages have reached a steady state. Koyanagi at 2:18-20.

As described, Koyanagi discloses precharging the data pairs DQ/\*DQ and D/\*D to a high-impedance state voltage, and thereafter adjusting the voltage on those lines to reflect differentials that correspond to data read from memory cell. Because Koyanagi discloses the features identified by the Examiner as justifying allowance of independent claim 1, Koyanagi establishes a substantial (and new) question of patentability, and it also establishes a reasonable likelihood that the requester will prevail with respect to at least independent claim 1.

## VII. MANNER OF APPLYING CITED PRIOR ART TO EVERY CLAIM FOR WHICH REEXAMINATION IS REQUESTED

In this Section, Requester proposes various grounds of rejection for claims 1-3 and 5-7, justifying reexamination. Requester presents claim charts that compare the claim language, under its broadest reasonable construction, with the disclosure of the prior art, as understood by one of ordinary skill in the art. The proposed rejections include anticipation rejections. Requester

The two data line pairs DQ/\*DQ and D/\*D are separated by isolation circuit 307 as shown in FIG. 1 of Koyanagi.

further notes that under the M.P.E.P., the closeness of the prior art with the claimed invention at times merits alternative rejections over a single reference, namely an anticipation or an obviousness rejection. See M.P.E.P. § 2112. ("There is nothing inconsistent in concurrent rejections for obviousness under 35 U.S.C. 103 and for anticipation under 35 U.S.C. 102." In re Best, 562 F.2d 1252, 1255 n.4, 195 U.S.P.Q. 430, 433 n.4 (CCPA 1977)). For several of the claims, Requester has proposed alternative anticipation/obviousness rejections to advise the Examiner of the various options for rejecting the challenged claims.

### A. HARDEE

As shown in the Claim Chart below, each and every limitation of claims 1-3 and 5-7 of the '130 patent are anticipated by Hardee. Specifically, the following grounds of rejection are presented in the claim chart below:

(1) Claims 1-3, and 5-7 of the '130 patent are anticipated by Hardee.

| established for DW and DWB. When DW is set to a logic high and DWB is consequentially set to a logic low, the voltage levels at 126 and 136 rise and fall, respectively. Whereas, when DW is set to a logic low and DWB is consequentially set to a logic low, the voltage levels at 126 and 136 fall and rise, respectively. Hardee at 14:43-53.  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the dashed box below:  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the dashed box below:  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the dashed box below:  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the dashed box below:  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the dashed box below:  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the dashed box below:  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the dashed box below:  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the dashed box below:  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the dashed box below:  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the dashed box below:  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the dashed box below:  FIG. 8 of Hardee shows a voltage precharge source, as indicated by the voltage levels at 126 miles at 126 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a differential bus coupled to the Harden bus drivers and to the voltage above-precharge source;                                                                                                                                                                                                | and a latching sense amplifier Harde coupled to the differential bus;                                                                                                                                                                                                                                                                                                                            | DW LOCAL<br>IZ6                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Hardee discloses a differential bus 126 and its complement 136, each being coupled to the above-identified bus drivers (DW and DWB) and to the above-identified voltage precharge source BLREF.  In greater detail, when control signals YW, SHL, and ISOL are high, the differential bus pair | 126 and 136 are connected to BLREF and precharged to ½ Vcc. Conversely, when control signals ISOL and SHL are low, the differential bus pair 126 and 136 are connected to the bus drivers. Hardee at 14:43-53.  Hardee discloses a latching sense amplifier, as indicated by the dashed box overlaying the version of FIG. 8 reproduced below, coupled to the differential bus pair 126 and 136. | BLREF 246  252 256 246  220 256 248  220 256 248  222  232  222  232  232  232  232 |

| Hardee discloses an output stage, as indicated by the dashed box overlaying the version of FIG. 8 provided below, coupled to an output of the cross-latched circuit. Specifically, the output stage includes two isolation transistors 232 and 234 controlled by the ISOL signal. The differential voltage pair 158 and 160, at the output of the first stage, serve as the input of this output stage. Hardee at 14:19-23. | DW LOCAL   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   188   1 | When ISOL and YW signals are enabled, the differential bus 158 and the differential data bus 126 are precharged to ½ Vcc. Specifically, in Hardee, "[t]ransistors 252 and 254 have their source-drain paths connected between the bit line reference BLREF at node 246 and the bit lines 220, 222, respectively, and will therefore, when turned on, couple the bit line reference |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and an output stage coupled to an output of said first stage; wherein the output of the first stage is coupled to an input of the output stage;                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | wherein the differential bus and<br>the differential data bus are<br>precharge to a voltage Vpr<br>between Vdd and ground, where                                                                                                                                                                                                                                                   |

Reexamination Request for U.S. Patent No. 6 366, 130

|                                                                                                                                               | U.S. Patent No. 6,366,130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vpr=K*Vdd, and K is a precharging voltage factor.                                                                                             | voltage to the bit lines themselves The bit line reference is illustratively a constant voltage approximately equal to ½ VCC in one preferred embodiment." Hardee at 13:5-19.                                                                                                                                                                                                                                                                                                                                       |

| Claim 2                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2. The data transfer arrangement in accordance with claim 1 wherein the bus drivers comprise active pull-up and active pull-down bus drivers. | The two bus drivers DW and DWB are pull-up and pull-down bus drivers. Specifically, the voltage at data lines 126 and 136 are driven based on the voltage levels established for DW and DWB. When DW is set to a logic high and DWB is consequentially set to a logic low, the voltage levels at 126 and 136 rise and fall, respectively. Whereas, when DW is set to a logic low and DWB is consequentially set to a logic high, the voltage levels at 126 and 136 fall and rise, respectively. Hardee at 14:43-53. |

| Claim 3                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

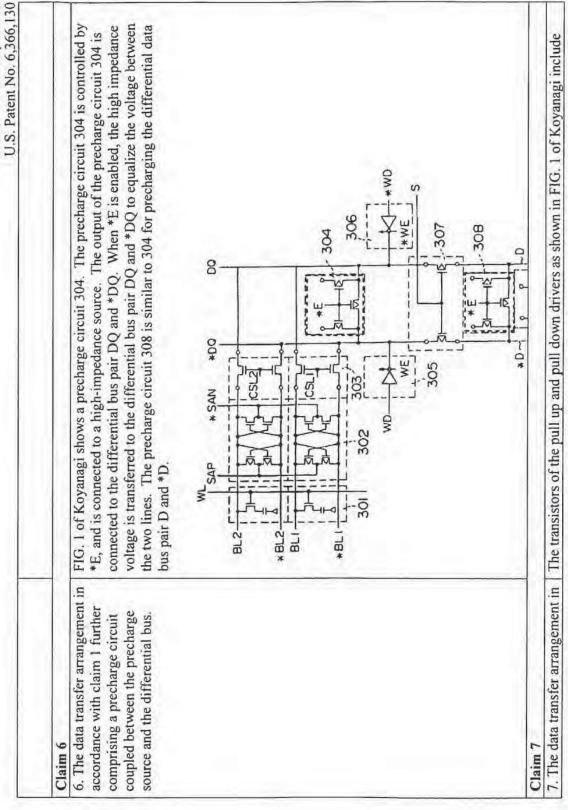

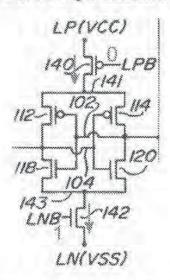

| 3. The data transfer arrangement in accordance with claim 1, wherein the first stage of the latching sense amplifier comprises:               | Hardee, as shown using the dashed box overlying the following reproduction of FIG. 8 shows aspects of the first stage of its latching sense amplifier, including input pass transistors (e.g., NMOS 122 and 124), each having a gate, a source terminal, and a drain.                                                                                                                                                                                                                                               |

| a plurality of input pass transistors each having a gate, a source terminal, and a drain;                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Similarly, the drain of an input pass transistor 124 latch amplifier NMOS 120 and PMOS 114 transis transistor 124 is coupled to an input data bus 136.                                                                                           | the sources of the cross-coupled latch amplifier NMOS transistors are coupled to the drain of the drain of the NMOS transistor coupled to a clock signal input,  OW LOCAL TO SECTION TO SEC | and the sources of the PMOS  fransistors are coupled to the drain of the PMOS transistor of the PMOS transistor having a gate coupled to an inverted clock              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Similarly, the drain of an input pass transistor 124 is coupled to a drain of the cross-coupled latch amplifier NMOS 120 and PMOS 114 transistors, and the source terminal of the input pass transistor 124 is coupled to an input data bus 136. | Within the box overlaying the version of FIG. 8 reproduced below, Hardee discloses coupling between the sources of the cross-coupled latch amplifier NMOS transistors 118 and 120 and the drain of the NMOS transistor 142 coupled to a LNB input.  232                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FIG 8 of Hardee shows that the sources of the PMOS transistors 112 and 114 are coupled to the drain of the PMOS transistor 140 having a gate coupled to the LPB signal. |

28

| high voltage and greater than a                                                                    | equal to ½ VCC in one preferred embodiment." Hardee at 13:5-19.                                                                                                                                             |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| logic low voltage.                                                                                 |                                                                                                                                                                                                             |