Filed on behalf of: Samsung Electronics Co., Ltd.

By: Steven L. Park (stevenpark@paulhastings.com)

Naveen Modi (naveenmodi@paulhastings.com)

Paul Hastings LLP

#

SAMSUNG ELECTRONICS CO., LTD. Petitioner

v.

ELBRUS INTERNATIONAL LIMITED Patent Owner

\_\_\_\_\_

U.S. Patent No. 6,366,130

\_\_\_\_\_

#### DECLARATION OF DR. R. JACOB BAKER

## TABLE OF CONTENTS

| 1.                    | Introduction1                                                                                 |                      |                                                                                                                                           | 1  |

|-----------------------|-----------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| II.                   | Qual                                                                                          | Qualifications       |                                                                                                                                           |    |

| III.                  | Sumi                                                                                          | Summary of Opinions5 |                                                                                                                                           |    |

| IV.                   | The '                                                                                         | The '130 Patent      |                                                                                                                                           |    |

| V. Claim Construction |                                                                                               |                      | 9                                                                                                                                         |    |

|                       | A.                                                                                            | Latch                | ning Sense Amplifier (Claims 1 and 3)                                                                                                     | 10 |

|                       | B.                                                                                            | Stage                | e (Claims 1, 3, and 9)                                                                                                                    | 11 |

| VI.                   | The Prior Art Discloses or Suggests Every Feature of the Challenged Claims of the '130 Patent |                      |                                                                                                                                           |    |

|                       | A.                                                                                            | Brief                | Description of the Prior Art                                                                                                              | 12 |

|                       | В.                                                                                            | Refe                 | ullo, Either Individually or in Combination with Other rences, Discloses or Suggests Every Feature of the enged Claims of the '130 Patent | 14 |

|                       |                                                                                               | 1.                   | Ternullo Discloses the Features of Claims 1-3 and 5-6                                                                                     | 14 |

|                       |                                                                                               | 2.                   | Ternullo and Hardee Disclose or Suggest the Features of Claim 7                                                                           | 61 |

|                       |                                                                                               | 3.                   | Ternullo and Sukegawa Disclose or Suggest the Features of Claim 9                                                                         | 64 |

| VII.                  | Conc                                                                                          | lusion               |                                                                                                                                           | 68 |

I, R. Jacob Baker, declare as follows:

#### I. INTRODUCTION

- 1. I have been retained by Samsung Electronics Co., Ltd. ("Petitioner") as an independent expert consultant in this proceeding before the United States Patent and Trademark Office. Although I am being compensated at my rate of \$450 per hour for the time I spend on this matter, no part of my compensation is dependent on the outcome of this proceeding, and I have no other interest in this proceeding.

- 2. I understand that this proceeding involves U.S. Patent No. 6,366,130 ("the '130 Patent") (Ex. 1001), the application for which was filed on February 17, 2000, as U.S. Patent Application No. 09/505,656, and issued on April 2, 2002. I also understand, as demonstrated by the face of the '130 Patent, that the '130 Patent purports to claim priority to February 17, 1999, the filing date of U.S. Provisional Application No. 60/120,531 ("the '531 provisional application").

- 3. I have been asked to consider whether certain references disclose or suggest the features recited in the claims of the '130 Patent. My opinions are set forth below.

### II. QUALIFICATIONS

4. I serve as a Professor of Electrical and Computer Engineering at the University of Nevada, Las Vegas ("UNLV"). I have been teaching electrical

engineering at UNLV since 2012. Before this, I was a Professor of Electrical and Computer Engineering with Boise State University beginning in 2000. Before my position at Boise State University, I was an Associate Professor of Electrical Engineering between 1998 and 2000 and an Assistant Professor of Electrical Engineering between 1993 and 1998, both at the University of Idaho. I have been teaching electrical engineering since 1991. I received my Ph.D. in Electrical Engineering from the University of Nevada, Reno, in 1993. I also received a MS and BS in Electrical Engineering from UNLV in 1988 and 1986, respectively.

5. As further described in my CV, I am a licensed Professional Engineer in the State of Idaho and have more than 25 years of experience, including extensive experience in circuit design and manufacture of Dynamic Random Access Memory (DRAM) semiconductor integrated circuit chips and CMOS Image Sensors (CISs) at Micron in Boise, Idaho. I also spent considerable time working on the development of Flash memory while at Micron. My efforts resulted in more than a dozen Flash-memory related patents. Among many other experiences, I led the development of the delay-locked loop (DLL) in the late 1990s so that Micron DRAM products could transition to the DDR memory standard. I also provided technical assistance with Micron's acquisition of Photobit during 2001 and 2002. This assistance included help transition the manufacture of CIS products into Micron's DRAM process technology. I have worked as a

consultant at other companies designing memory chips, including Sun, Oracle, and Contour Semiconductor. I have worked at other companies designing CISs, including Aerius Photonics, Lockheed-Martin, and OmniVision.

- 6. I am the author of several books covering the area of integrated circuit design including: *DRAM Circuit Design: Fundamental and High-Speed Topics* (two editions), *CMOS Circuit Design, Layout, and Simulation* (three editions), and *CMOS Mixed-Signal Circuit Design* (two editions). I have authored, and/or co-authored, more than 100 papers and presentations in the areas of solid-state circuit design and packaging.

- 7. As a professor, I have been the main advisor to five Doctoral students and over 65 Masters students.

- 8. I am the named inventor on over 137 granted U.S. patents in integrated circuit design including flash memory, DRAM, and CMOS image sensors.

- 9. I have received numerous awards for my work, including the Frederick Emmons Terman (the "Father of Silicon Valley") Award. The Terman Award is bestowed annually upon an outstanding young electrical/computer engineering educator in recognition of the educator's contributions to the profession.

- 10. I have also received the IEEE Circuits and Systems Education Award (2011), the IEEE Power Electronics Best Paper Award (2000), and I am a Fellow of the IEEE for contributions to memory circuit design.

- 11. In addition, I have received the President's Research and Scholarship Award (2005), Honored Faculty Member recognition (2003), Outstanding Department of Electrical Engineering Faculty recognition (2001), all from Boise State University. I have also received the Tau Beta Pi Outstanding Electrical and Computer Engineering Professor Award the three years I have been at UNLV.

- 12. I have also given over 50 invited talks at conferences and universities in the areas of integrated circuit design including: AMD, Arizona State University, Beijing Jiaotong University, Carleton University, Carnegie Mellon, Columbia University, Dublin City University (Ireland), École Polytechnique de Montréal, Georgia Tech, Gonzaga University, Hong Kong University of Science and Technology, Indian Institute of Science (Bangalore, India), Instituto de Informatica (Brazil), Instituto Tecnológico y de Estudios Superiores de Monterrey, ITESM (Mexico), Iowa State University, Laval University, Lehigh University, Princeton University, Temple University, University of Alabama, University of Arkansas, University of Buenos Aires (Argentina), University of Illinois, Urbana-Champaign, Utah State University, University of Nevada, Las Vegas, University of Houston, University of Idaho, University of Nevada, Reno, University of Macau, University

of Toronto, University of Utah, Yonsei University (Seoul, Korea), University of Maryland, IEEE Electron Devices Conference (NVMTS), IEEE Workshop on Microelectronics and Electron Devices (WMED), the Franklin Institute, National Semiconductor, AMI semiconductor, Micron Technology, Rendition, Saintgits College (Kerala, India), Southern Methodist University, Sun Microsystems, Stanford University, ST Microelectronics (Delhi, India), Tower (Israel), Foveon, ICySSS keynote, and Xilinx.

13. Details of my professional and educational background, as well as a listing of other matters on which I have provided consulting and/or provided testimony as a technical expert, are provided in my Curriculum Vitae, attached as Appendix A to this Declaration.

#### III. SUMMARY OF OPINIONS

14. All of the opinions contained in this Declaration are based on the documents I reviewed, my experience and background, and my knowledge and professional judgment. In forming the opinions expressed in this Declaration, I reviewed the '130 Patent (Ex. 1001); the prosecution file history for the '130 Patent (Ex. 1003); the file history of the *inter partes* reexamination (control no. 95/000,657) ("the '657 proceeding") for the '130 Patent, excerpts of which I understand are being submitted as Ex. 1004; U.S. Patent No. 6,052,328 to Ternullo et al. ("*Ternullo*") (Ex. 1005); U.S. Patent No. 5,828,241 to Sukegawa

("Sukegawa") (Ex. 1006); U.S. Patent No. 6,249,469 to Hardee ("Hardee") (Ex. 1007); and excerpts from the Modern Dictionary of Electronics (7th ed. 1999) (Ex. 1008), while drawing on my experience and knowledge in the field.

- 15. My opinions have also been guided by my appreciation of how a person of ordinary skill in the art would have understood the claims of the '130 Patent at the time of the alleged invention, which I have been asked to initially assume is February 17, 1999, the filing date of the '531 provisional application from which the '130 Patent purports to claim priority. At the time of the alleged invention, a person of ordinary skill in the art related to the technology of the '130 Patent would have had an undergraduate degree in Electrical Engineering or equivalent and at least two to three years of experience in the design and/or analysis of data transfer circuits or the equivalent. In determining the level of ordinary skill, I was asked to consider, for example, the types of problems encountered in the art, prior solutions to those problems, the rapidity with which innovations are made, the sophistication of the technology, and the educational level of active workers in the field.

- 16. Based on my experience and expertise, it is my opinion that certain references disclose or suggest all the features recited in claims 1-3, 5-7, and 9 ("the challenged claims") of the '130 Patent.

#### IV. THE '130 PATENT

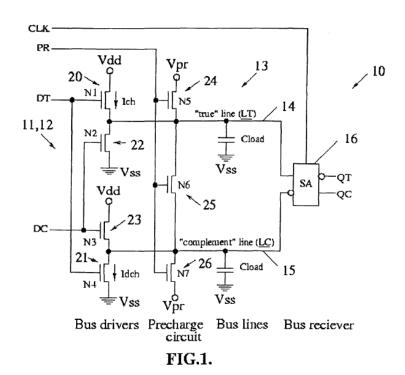

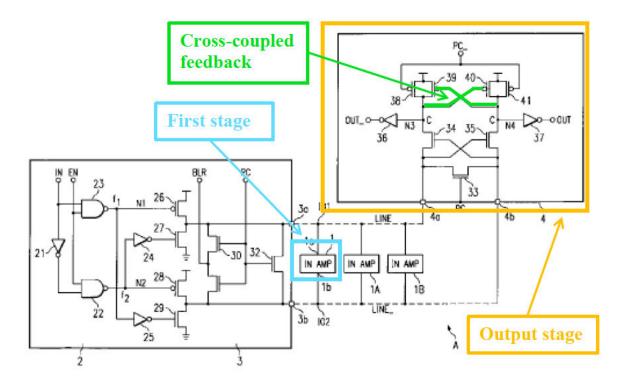

17. The '130 Patent is purportedly directed to a data transfer scheme that includes two bus drivers, a precharge circuit, two complementary bus lines, and a latching sense amplifier. *See, e.g.*, Ex. 1001 2:1-8. Figure 1 of the '130 Patent illustrates two bus drivers 11, 12 (consisting of transistors 20, 21, 22, and 23) and two complementary bus lines 14, 15 as inputs to a latching sense amplifier 16:

18. The data transfer scheme operates in two phases: a precharge phase and a data transfer phase (Ex. 1001 2:12-13), with the bus drivers and complementary bus lines operating in opposite phases to the latching sense amplifier (Ex. 1001 2:43-44). In other words, when the complementary bus lines

and the bus drivers are in the precharge phase, the sense amplifier is in data transfer phase and vice versa.

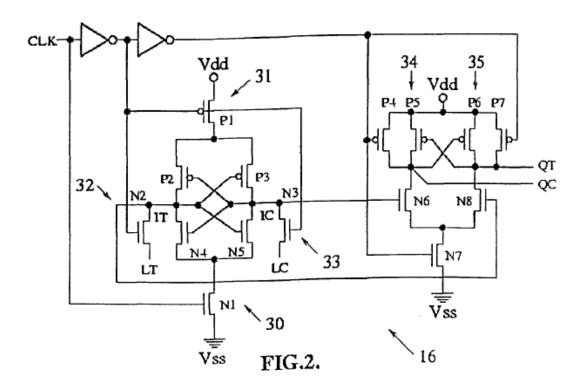

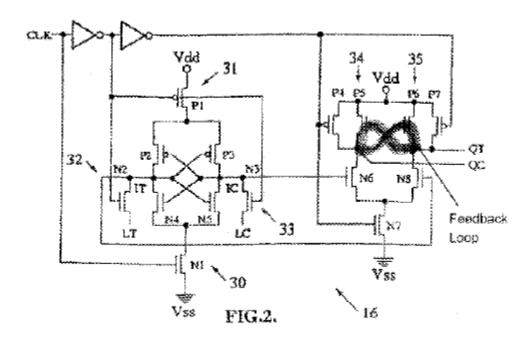

19. Figure 2 of the '130 Patent discloses a latching sense amplifier:

- 20. I understand that the '130 Patent includes 9 claims with claims 1 and 8 being independent and claims 2-7 and 9 being dependent from claim 1. I further understand that claim 9 was added during reexamination. As I note above, I was asked to opine with respect to some of the claims of the '130 Patent. I have reproduced claim 1 below:

- 1. A data transfer arrangement comprising:

two bus drivers;

a voltage precharge source;

a differential bus coupled to the bus drivers and to the voltage precharge source; aid [sic]

a latching sense amplifier coupled to the differential bus;

wherein the latching sense amplifier comprises:

a first stage including a cross-coupled latch coupled to a differential data bus; and

an output stage coupled to an output of said first stage;

wherein the output of the first stage is coupled to an input of the output stage;

wherein the differential bus and the differential data bus are precharge to a voltage Vpr between Vdd and ground, where Vpr = K\*Vdd, and K is a precharging voltage factor.

#### V. CLAIM CONSTRUCTION

21. I understand that a claim subject to *inter partes* review receives the broadest reasonable construction in light of the specification of the patent in which it appears. I also understand that in these proceedings, any term that is not construed should be given its plain and ordinary meaning under the broadest reasonable construction. I have followed these principles in my analysis. I discuss a few terms below and what I understand to be Petitioner's constructions of these terms.

#### A. Latching Sense Amplifier (Claims 1 and 3)

22. Independent claim 1 and dependent claim 3 of the '130 Patent recite a "latching sense amplifier." I understand Petitioner has offered that the broadest reasonable construction of the term "latching sense amplifier" that is consistent with the use of the term in the claims and specification of the '130 Patent is "a circuit, including a latch, that detects and amplifies signals." I have used this construction in my analysis and agree with it because the specification describes its latching sense amplifier to include a latch (see, e.g., Ex. 1001 2:39-40, 2:48-50) for detecting (see, e.g., Ex. 1001 2:33-38, 2:64-67) and amplifying received signals (see, e.g., Ex. 1001 2:64-67). Furthermore, latching sense amplifiers were well known at the time of the alleged invention of the '130 Patent, and this construction is consistent with the understanding of one of ordinary skill in the art at the time of the alleged invention of the '130 Patent as well as dictionary definitions for similar terms (see, e.g., Ex. 1008 at 679 (defining "sense amplifier" as "[a] circuit used to sense low-level voltages ... and to amplify these signals to the logic voltage levels of the system"). In my opinion, the claims additionally specify what a "latching sense amplifier" has to include. For example, claim 1 requires that the "latching sense amplifier" include both a first stage with a cross-coupled latch and an output stage. See, e.g., Ex. 1001 4:8-13.

#### **B.** Stage (Claims 1, 3, and 9)

23. Independent claim 1 and dependent claims 3 and 9 recite a "stage." I understand Petitioner has offered that the broadest reasonable construction of the term "stage" that is consistent with the use of the term in the claims of the '130 Patent is "portion of a circuit." I have used this construction in my analysis and agree with it. In my experience and in the field, the term "stage" is sometimes used to refer to a portion of a circuit. This construction is consistent with dictionary definitions for the term. See, e.g., Ex. 1008 at 728 (defining "stage" as "[a] single section of a multisection circuit or device"). This meaning is further reinforced by the claims. Claim 1 specifies that a latching sense amplifier comprises of a "first stage" and an "output stage," and claims 3 and 9 use the terms in the context of particular circuitry found within a "first stage" and an "output stage." See, e.g., Ex.1001 4:8-13, 4:21-23, Reexam Cert. 1:20-21. As the latching sense amplifier is itself a circuit, it follows accordingly that particular "stages" of the circuit reflect a portion of the circuit. My understanding is also consistent with the specification's use of the term "stage." Ex. 1001 3:4-5.

## VI. THE PRIOR ART DISCLOSES OR SUGGESTS EVERY FEATURE OF THE CHALLENGED CLAIMS OF THE '130 PATENT

24. I have reviewed several references, discussed further below, that I understand are prior art to the '130 Patent. In my opinion, these references disclose or suggest all features of the challenged claims of the '130 Patent.

#### A. Brief Description of the Prior Art

- 25. Ternullo describes "a method and apparatus that accomplishes a high performance, random read/write SDRAM design by synchronizing the read and write operation at the data line sense amplifier." Ternullo Abstract. As such, Ternullo generally relates to the transmission of signals in an electronic circuit. Ternullo sought to overcome the challenges of using the same set of lines for efficient read and write operations (see, e.g., id. 2:9-35), and in doing so, teaches, among other things, a "high performance write process without impacting the critical read path" (id. 1:9-10).

- 26. Sukegawa describes "a type of signal transmission circuit wherein the signal is amplified and transmitted by means of the positive feedback of an intermediate amplifier circuit having input/output shared terminals." Sukegawa 1:11-15. The signal transmission circuit disclosed sought to increase the signal transmission distance as well as increase the speed and lower the power consumption of a transmission. Id. 4:52-55. Sukegawa discloses that its signal

transmission circuit comprises of "a driver circuit, a receiver circuit, an equalizer circuit, and an intermediate amplifier circuit." *Id.* 4:62-65. The intermediate amplifier circuit relies on positive feedback to amplify the signal provided by the driver circuit and transmit the amplified signal to the receiver circuit. *See, e.g., id.* 5:1-4.

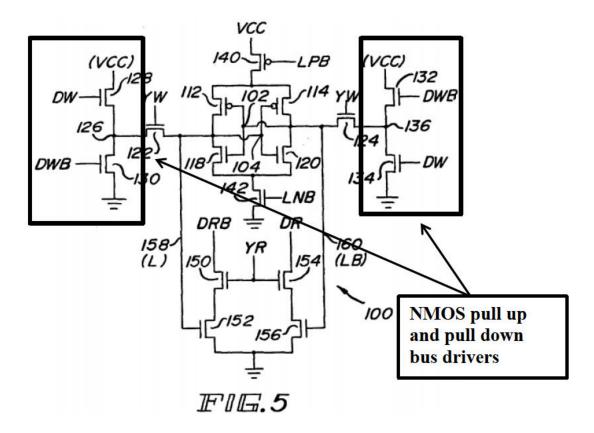

- 27. *Hardee* is yet another prior art reference relating to signal transmission, and in particular, "integrated circuit memories" and "sense amplifiers for use therein." *See, e.g., Hardee* 1:8-10. *Hardee* introduces a sense amplifier highlighted by three "salient" features:

- (1) the connection of each sense amplifier via transistors or other switching devices to the power supply lines without directly connecting together power supply lines for multiple sense amplifiers;

- (2) the use of local read amplifiers;

- (3) the use of local write circuitry.

See i.d. 5:24-32.

28. All the prior art references mentioned above relate to signal transmission and were motivated to improve the efficiency of such transmissions. As such, one of ordinary skill in the art at the time of the alleged invention of the

'130 Patent would have been motivated to combine the teachings of these references.

- B. Ternullo, Either Individually or in Combination with Other References, Discloses or Suggests Every Feature of the Challenged Claims of the '130 Patent

- 29. In my opinion, *Ternullo*, either individually or in combination with other references, such as *Hardee* and *Sukegawa*, discloses or suggests the features recited in the challenged claims of the '130 Patent.

#### 1. Ternullo Discloses the Features of Claims 1-3 and 5-6

30. In my opinion and as shown in the charts below, *Ternullo* discloses each and every feature recited in claims 1-3 and 5-6 of the '130 Patent.

#### a. Claim 1

31. Ternullo discloses each and every feature of claim 1.

| Claim Language     | Ternullo                                                         |

|--------------------|------------------------------------------------------------------|

| 1. A data transfer | Ternullo discloses a data transfer arrangement.                  |

| arrangement        | For example, Ternullo states that its "present invention         |

| comprising:        | provides a method and apparatus that accomplishes a high         |

|                    | performance, random read/write SDRAM design by                   |

|                    | synchronizing the read and write operations at the data line     |

|                    | sense amplifier." Ternullo Abstract.                             |

|                    | Ternullo further discloses that "[d]uring a read operation, read |

| Claim Language | Ternullo                                                       |

|----------------|----------------------------------------------------------------|

|                | data is transferred from the memory cells of the device across |

|                | a series of consecutive pairs of data lines to an input/output |

|                | port of the memory device." Ternullo Abstract (emphasis        |

|                | added).                                                        |

|                | Fig. 2 of Ternullo "shows a schematic diagram of the read      |

|                | circuitry 32A that is formed in accordance with the present    |

|                | invention as it may be implemented as part of the data sense   |

|                | line sense amplifier and supporting circuitry 32 (FIG. 1). The |

|                | read circuitry 32A is required for performing a read           |

|                | operation." Ternullo 4:63-67.                                  |

| Claim Language   | Ternullo                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------|

|                  | 32/                                                                                                  |

|                  | DL1  DL2  DL2  DL2  DL2  DL2  DL2  DL2                                                               |

|                  | DCLK ISOLATION CIRCUIT -70  LATI - 80  AND BCLKT BATA LATCH LOCK BCCKTN LINE LATCH LOCK BCCKTN LATCH |

|                  | READ READ READ DRIVERS  BLL2  DLL1                                                                   |

|                  | Fig. 2.                                                                                              |

|                  | See also, e.g., Ternullo Fig. 1.                                                                     |

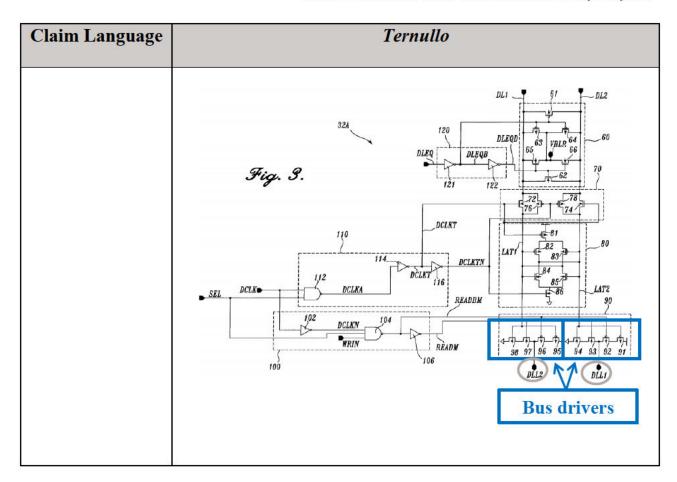

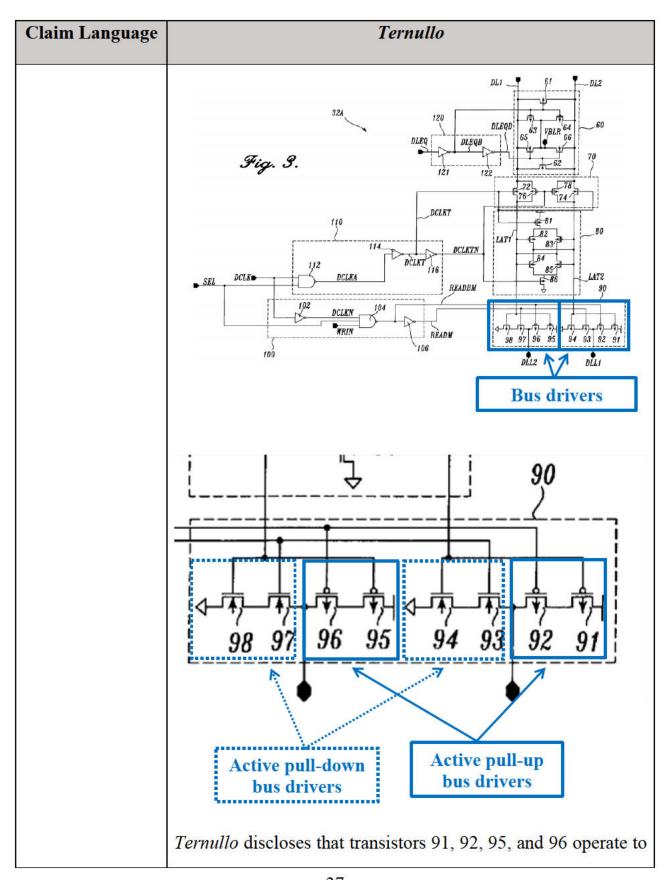

| two bus drivers; | Ternullo discloses two bus drivers (e.g., transistor group 91-94                                     |

|                  | and transistor group 95-98). See, e.g., Ternullo Fig. 3                                              |

|                  | (annotated below).                                                                                   |

Declaration of Dr. R. Jacob Baker Inter Partes Review of U.S. Patent 6,366,130

| Claim Language | Ternullo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | #RIN 104  DLEQ DLEQD 65 VBLR 66 60 60 65 VBLR 66 60 60 65 VBLR 66 60 65 VBLR 66 60 65 VBLR 66 VBLR 66 65 VBLR 66 V |

|                | Two bus drivers  Ternullo discloses that "read driver coupled to latch line LAT2 includes PFET transistors 91 and 92 and NFET transistors 93 and 94. The read driver coupled to latch line LAT1 includes PFET transistors 95 and 96 and NFET transistors 97 and 98."  Ternullo 7:15-18.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | The two bus drivers drive the outputs of Fig. 3 on lines DLL1 and DLL2. See, e.g., Ternullo 7:31-37 ("The read driver operates such that when the signal on the latch line LAT2 is low, PFET transistor 91 is biased on, and if the signal READBM is also low at that time, a high signal will be passed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Claim Language    | Ternullo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | to the line DLL1. If the latch line LAT2 is high, then the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                   | NFET transistor 94 will be biased on, and if the signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   | READM is high, then a low signal will be passed to the line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | DLL1."); 7:18-22 ("While the connections and operation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                   | the read driver connected to latch line LAT2 will be described                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | below, it is understood that the read driver connected to latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | line LAT1 is constructed and operates similarly.").                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

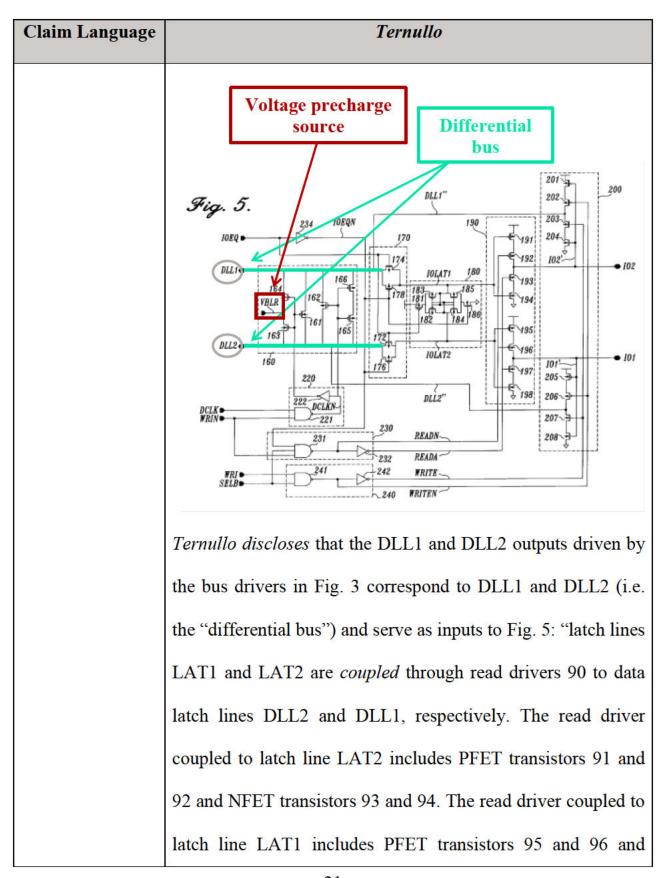

| a voltage         | Ternullo discloses a voltage precharge source (e.g., VBLR).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| precharge source; | See, e.g., Ternullo Fig. 5 (annotated below).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                   | ### 231   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   101   10 |

|                   | VBLR represents a voltage precharge source because prior to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Claim Language     | Ternullo                                                        |

|--------------------|-----------------------------------------------------------------|

|                    | receiving data on lines DLL1 and DLL2, these lines are          |

|                    | precharged to the midlevel voltage VBLR: "when control          |

|                    | signal DCLKD is high and signal DCLKN is low, NFET              |

|                    | transistor 161 and PFET transistor 162 couple line DLL1 to      |

|                    | line DLL2, while NFET transistors 163 and 164 and PFET          |

|                    | transistors 165 and 166 couple the lines DLL1 and DLL2 to       |

|                    | the midlevel voltage source VBLR." Ternullo 8:28-32; see        |

|                    | also, e.g., id. 10:35-40.                                       |

|                    |                                                                 |

| a differential bus | Ternullo discloses a differential bus (e.g., DLL1 and DLL2)     |

| coupled to the bus | coupled to the bus drivers (e.g., transistor group 91-94 and    |

| drivers and to the | transistor group 95-98) and to the voltage precharge source     |

| voltage precharge  | (e.g., VBLR). See, e.g., Ternullo Figs. 3, 5 (annotated below). |

| source; aid [sic]  |                                                                 |

Declaration of Dr. R. Jacob Baker Inter Partes Review of U.S. Patent 6,366,130

| Claim Language | Ternullo                                                          |

|----------------|-------------------------------------------------------------------|

|                | NFET transistors 97 and 98." Ternullo 7:13-18 (emphasis           |

|                | added); see also id. Figs. 1-5. Thus, the bus drivers are coupled |

|                | to the differential bus.                                          |

|                | Ternullo further discloses that "when control signal DCLKD is     |

|                | high and signal DCLKN is low, NFET transistor 161 and             |

|                | PFET transistor 162 couple line DLL1 to line DLL2, while          |

|                | NFET transistors 163 and 164 and PFET transistors 165 and         |

|                | 166 couple the lines DLL1 and DLL2 to the midlevel voltage        |

|                | source VBLR." Ternullo 8:28-32 (emphasis added); see also,        |

|                | e.g., id. 10:35-40.                                               |

|                | One of ordinary skill in the art at the time of the alleged       |

|                | invention of the '130 Patent would have recognized DLL1 and       |

|                | DLL2 as the "differential bus" because a voltage differential     |

|                | (i.e., a difference in voltages between the two bus lines) can    |

|                | develop on these two bus lines. See, e.g., Ternullo 10:35-43. In  |

|                | addition, DLL1 and DLL2 precede isolation circuit170 within       |

|                | Ternullo's latching sense amplifier (discussed further below),    |

|                | and is consistent with the Patent Owner's own mapping of          |

|                | "differential bus" in the '657 proceeding:                        |

| Claim Language      | Ternullo                                                                                                                                                                                                                           |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | Differential SA QT Vss Vpr Vss Bus drivers Precharge Bus lines Bus reciever circuit Ex. 1004, p. 68 (declaration of Dr. Philip Koopman submitted by Patent Owner; labeled differential bus LT and LC precedes sense amplifier 16). |

| a latching sense    | Ternullo discloses a latching sense amplifier (shown in purple)                                                                                                                                                                    |

| amplifier coupled   | coupled to the differential bus DLL1 and DLL2. See, e.g.,                                                                                                                                                                          |

| to the differential | Ternullo Fig. 5 (annotated below).                                                                                                                                                                                                 |

| bus;                |                                                                                                                                                                                                                                    |

Declaration of Dr. R. Jacob Baker Inter Partes Review of U.S. Patent 6,366,130

| Claim Language | Ternullo                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | The purple box drawn above for the latching sense amplifier is consistent with Petitioner's proposed construction of "latching sense amplifier," as it is a circuit, including a latch, that detects and amplifies signals. This circuit includes an input/output latch 180. The circuit detects and amplifies the signal on DLL1 and DLL2 received through isolation circuit 170. Ternullo 7:58-8:3, 8:51-55, 10:46-49. |

| Claim Language     | Ternullo                                                        |

|--------------------|-----------------------------------------------------------------|

|                    | Ternullo discloses that "[w]hen NFET transistor 186 is biased   |

|                    | on by a high on control signal IOEQN and when PFET              |

|                    | transistor 181 is biased on by a low on control signal IOEQ,    |

|                    | the input/output latch 180 is turned on. Once the input/output  |

|                    | latch 180 is turned on, when a high or low signal appears on    |

|                    | either of the lines IOLAT1 or IOLAT2, the other line IOLAT1     |

|                    | or IOLAT2 is correspondingly driven to the opposite state by    |

|                    | the function of the latch." Ternullo 8:48-55.                   |

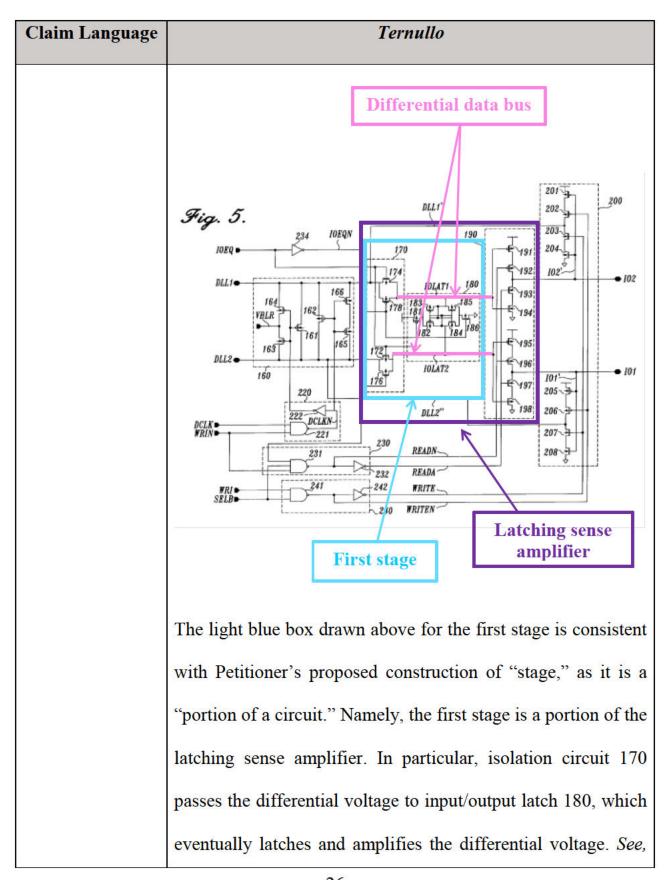

| wherein the        | Ternullo discloses a latching sense amplifier (shown in purple) |

| latching sense     | wherein a first stage (shown in light blue) includes a cross-   |

| amplifier          | coupled latch (e.g., input/output latch 180) coupled to a       |

| comprises: a first | differential data bus (e.g., IOLAT1 and IOLAT2). See, e.g.,     |

| stage including a  | Ternullo Fig. 5 (annotated below).                              |

| cross-coupled      |                                                                 |

| latch coupled to a |                                                                 |

| differential data  |                                                                 |

| bus; and           |                                                                 |

Declaration of Dr. R. Jacob Baker Inter Partes Review of U.S. Patent 6,366,130

| Claim Language | Ternullo                                                       |

|----------------|----------------------------------------------------------------|

|                | e.g., Ternullo 7:58-8:3, 8:48-55, 10:35-43.                    |

|                | Ternullo discloses that "[w]hen NFET transistor 186 is biased  |

|                | on by a high on control signal IOEQN and when PFET             |

|                | transistor 181 is biased on by a low on control signal IOEQ,   |

|                | the input/output latch 180 is turned on. Once the input/output |

|                | latch 180 is turned on, when a high or low signal appears on   |

|                | either of the lines IOLAT1 or IOLAT2, the other line IOLAT1    |

|                | or IOLAT2 is correspondingly driven to the opposite state by   |

|                | the function of the latch." Ternullo 8:48-55.                  |

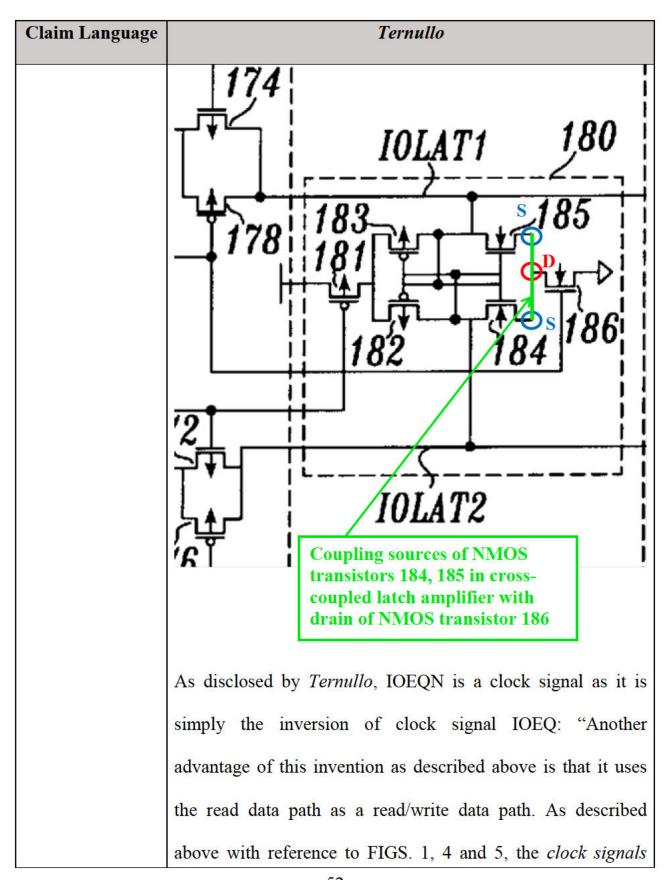

|                | Fig. 5 of Ternullo (annotated below) further teaches that the  |

|                | latch in Ternullo's first stage is cross coupled because the   |

|                | output of a first transistor is tied to the input of a second  |

|                | transistor, and vice versa:                                    |

Declaration of Dr. R. Jacob Baker Inter Partes Review of U.S. Patent 6,366,130

| Claim Language | Ternullo                                                       |

|----------------|----------------------------------------------------------------|

|                | 183 185 186 182 184 186                                        |

|                | One of ordinary skill in the art at the time of the alleged    |

|                | invention of the '130 Patent would have understood that        |

|                | input/output latch 180 in Fig. 5 is mistakenly drawn           |

|                | incorrectly. The gates of the transistors are improperly       |

|                | connected to each other (the section of annotated Fig. 5 below |

|                | covered by the green lines should be removed):                 |

Declaration of Dr. R. Jacob Baker Inter Partes Review of U.S. Patent 6,366,130

| Claim Language | Ternullo                                                                                                                                                                                                                                                                   |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | IOLAT1 180                                                                                                                                                                                                                                                                 |

|                | 183                                                                                                                                                                                                                                                                        |

|                | Indeed, <i>Ternullo</i> teaches that "input/output latch operate[s] similarly to data line latch 80 in FIG. 2" ( <i>Ternullo</i> 7:63-65), and data line latch 80, as further detailed in Fig. 3, is drawn correctly without the transistor gates connected to each other: |

Declaration of Dr. R. Jacob Baker Inter Partes Review of U.S. Patent 6,366,130

| Claim Language  | Ternullo                                                              |

|-----------------|-----------------------------------------------------------------------|

|                 | Gate of transistor 82 not connected to gate of transistor 83  LAT2  9 |

|                 | Additionally, one of ordinary skill in the art at the time of the     |

|                 | alleged invention of the '130 Patent would have recognized            |

|                 | IOLAT1 and IOLAT2 as the "differential data bus" because it           |

|                 | represents an amplified voltage differential representative of        |

|                 | the data to be read out by the latching sense amplifier. See,         |

|                 | e.g., Ternullo 8:45-55. Indeed, one of ordinary skill in the art      |

|                 | at the time of the alleged invention of the '130 Patent would         |

|                 | have understood IOLAT1 and IOLAT2 to include differential             |

|                 | data because of the amplified voltage differential on these           |

|                 | lines.                                                                |

| an output stage | Ternullo discloses a latching sense amplifier (shown in purple)       |

Declaration of Dr. R. Jacob Baker Inter Partes Review of U.S. Patent 6,366,130

| Claim Language      | Ternullo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|