**Developer Note**

# Macintosh Quadra 840AV and Macintosh Centris 660AV Computers

Developer Press © Apple Computer, Inc. 1993

> PUMA EXHIBIT 2005 PART 1 OF 10

Apple Computer, Inc.

© 1993, Apple Computer, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Computer, Inc. Printed in the United States of America.

The Apple logo is a registered trademark of Apple Computer, Inc. Use of the "keyboard" Apple logo (Option-Shift-K) for commercial purposes without the prior written consent of Apple may constitute trademark infringement and unfair competition in violation of federal and state laws.

No licenses, express or implied, are granted with respect to any of the technology described in this book. Apple retains all intellectual property rights associated with the technology described in this book. This book is intended to assist application developers to develop applications only for Apple Macintosh computers.

Apple Computer, Inc. 20525 Mariani Avenue Cupertino, CA 95014 408-996-1010

Simultaneously published in the United States and Canada.

Apple, the Apple logo, APDA, AppleTalk, EtherTalk, LaserWriter, LocalTalk, Macintosh, MPW, and TokenTalk are trademarks of Apple Computer, Inc., registered in the United States and other countries.

Apple Desktop Bus, AppleScript, Apple SuperDrive, A/ROSE, Finder, GeoPort, Macintosh Centris, Macintosh Quadra, MacroMaker, PlainTalk, PowerBook, QuickTime, and ResEdit are trademarks of Apple Computer, Inc.

Adobe and PostScript are trademarks of Adobe Systems Incorporated, which may be registered in certain jurisdictions.

Classic is a registered trademark licensed to Apple Computer, Inc. DSP3210 is a registered trademark of AT&T Corporation.

FileMaker and MacWrite are registered trademarks of Claris Corporation.

FrameMaker is a registered trademark of Frame Technology Corporation. Helvetica and Palatino are registered trademarks of Linotype Company. ITC Zapf Dingbats is a registered trademark of International Typeface Corporation.

Excel and Microsoft are registered trademarks of Microsoft Corporation. Motorola is a registered trademark of Motorola Corporation. NuBus is a trademark of Texas Instruments. QuicKeys is a trademark of CE Software, Inc. UNIX is a registered trademark of UNIX System Laboratories, Inc.

#### LIMITED WARRANTY ON MEDIA AND REPLACEMENT

If you discover physical defects in the manual or in the media on which a software product is distributed, APDA will replace the media or manual at no charge to you provided you return the item to be replaced with proof of purchase to APDA.

ALL IMPLIED WARRANTIES ON THIS MANUAL, INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, ARE LIMITED IN DURATION TO NINETY (90) DAYS FROM THE DATE OF THE ORIGINAL RETAIL PURCHASE OF THIS PRODUCT.

Even though Apple has reviewed this manual, APPLE MAKES NO WARRANTY OR REPRESENTATION, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS MANUAL, ITS QUALITY, ACCURACY, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. AS A RESULT, THIS MANUAL IS SOLD "AS IS," AND YOU, THE PURCHASER, ARE ASSUMING THE ENTIRE RISK AS TO ITS QUALITY AND ACCURACY.

IN NO EVENT WILL APPLE BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT OR INACCURACY IN THIS MANUAL, even if advised of the possibility of such damages.

THE WARRANTY AND REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND IN LIEU OF ALL OTHERS, ORAL OR WRITTEN, EXPRESS OR IMPLIED. No Apple dealer, agent, or employee is authorized to make any modification, extension, or addition to this warranty.

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

# Contents

|           | Figures, Tables, and Listings xv                                                                                                                                                                                                                                                                              |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface   | About This Developer Note xxi                                                                                                                                                                                                                                                                                 |

|           | Contents of This NotexxiHardware OverviewxxiiiSoftware OverviewxxiiiDigital Signal ProcessingxxivText-to-Speech ConversionxxivSpeech RecognitionxxvNew SCSI ManagerxxvOther System Software ChangesxxviSupplementary Documentsxxviii                                                                          |

| Part 1    | Hardware 1                                                                                                                                                                                                                                                                                                    |

| Chapter 1 | The Macintosh Quadra 840AV and<br>Macintosh Centris 660AV Computers       3         Models and Accessories       4         Summary of Features       5         Differences Between Models       6         System Software       7         Compatibility Issues       7         Machine Identification       8 |

| Chapter 2 | Hardware Details 9                                                                                                                                                                                                                                                                                            |

|           | Physical Forms10Parts Layout10System Architecture10Functional Units12Main Processor12Read-Only Memory12Random-Access Memory12Memory Controller and Arbiter13Digital Signal Processor13                                                                                                                        |

Peripheral Subsystem Controller 13 Macintosh Universal NuBus Interface 14 Cyclone Integrated Video Interfaces Controller 14 Sebastian 14 Video Data Path Chip 15 Mickey 15 New Age 15 Curio 16 Apple Telecom External Clock Synchronizer 16 Cuda 16 Singer 16 Endeavor 17 Digital Multistandard Decoder 17 System Clocks 17 Signal Buses 18 **Bus** Arbitration 18 **Bus Timeouts** 19 19 ROM and RAM Management **DRAM** Configurations 19 Startup Memory Addressing 20 Access Timing 20 **External Device Interfaces** 21 Apple Desktop Bus 21 **Ethernet** Port 22 22 Serial Ports SCSI Connection 24 **Power Budgets** 24 Internal SCSI Locations 24 **Pin Assignments** 26 Automatic SCSI Termination 27 Installing Internal SCSI Devices 28 Floppy Disk Drive Connection 28 **PSC** Functions 29 DMA Channels Controlled by the PSC 29 29 Bus Arbitration Performed by the PSC Video and Graphics I/O 30 External Video Input 32 Video RAM Usage 33 Video Monitor Interface 35 Video Output Timing 36 Miniature Videocam 37 Sound I/O 38 NuBus Interface 39 Slot Connections 40 Digital Audio/Video Expansion Connector 42 **DAV Sound Interface** 44 DAV Video Interface 45

| Processor-Direct Cards for the Macintosh Centris 660AV |  |

|--------------------------------------------------------|--|

| The Macintosh Centris 660AV PDS Connector 47           |  |

| Processor Bus Burst Write Timing 51                    |  |

| RAM Expansion Cards 52                                 |  |

| VRAM Expansion Cards 54                                |  |

Part 2 Real-Time Data Processing 57

#### Introduction to Real-Time Data Processing Chapter 3 59 60 Introduction to Digital Signal Processors Concepts of Digital Signal Processing 60 **Real-Time Processing Capability** 61 **Real-Time Processing Architecture** 62 Software Model 64 **Dual Programming Model** 64 **Real Time Manager** 65 DSP Operating System 66 **DSP** Driver 66 Other Software Components 66 Software Layers 67 70 **DSP-Aware Applications** Software Architecture 71 73 Frame Organization 74 Frame Size Selection Visible Caching 75 DSP and Main Processor Addressing 77 Containers 78 Primary and Secondary Pointers 78 78 **One-Container Sections Two-Container Sections** 78 On-Chip and Off-Chip Addressing 79 Guaranteed Processing Bandwidth 79 80 Smooth and Lumpy Algorithms Calculating GPB 80 GPB for Lumpy Algorithms 81 Fast Execution Versus Real-Time Execution 82 82 Processor Allocation for Timeshare Tasks Frame Overruns 83 Category One Frame Overrun 84 84 Category Two Frame Overrun 84 Category Three Frame Overrun

| Data Structures 85                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sections Defined 86                                                                                                                                                                                                                                                                                                                              |

| AutoCache 87                                                                                                                                                                                                                                                                                                                                     |

| DemandCache 87                                                                                                                                                                                                                                                                                                                                   |

| Sections and Caching 88                                                                                                                                                                                                                                                                                                                          |

| Container Memory Allocation 89                                                                                                                                                                                                                                                                                                                   |

| A Complete Software Example 90                                                                                                                                                                                                                                                                                                                   |

| Data Buffering 90                                                                                                                                                                                                                                                                                                                                |

| FIFO Buffers 92                                                                                                                                                                                                                                                                                                                                  |

| AIAO Buffers 94                                                                                                                                                                                                                                                                                                                                  |

| Buffer Connections Between Modules 95                                                                                                                                                                                                                                                                                                            |

| Buffer Connections Between Tasks 97                                                                                                                                                                                                                                                                                                              |

| Unified I/O Architecture 101                                                                                                                                                                                                                                                                                                                     |

| Execution Models 102                                                                                                                                                                                                                                                                                                                             |

| Section Control Flags 102                                                                                                                                                                                                                                                                                                                        |

| 0                                                                                                                                                                                                                                                                                                                                                |

| Setting Up Input and Output for Connections 103                                                                                                                                                                                                                                                                                                  |

| Setting Up Input and Output for Connections 103<br>AutoCache Execution Model 104                                                                                                                                                                                                                                                                 |

| AutoCache Execution Model 104                                                                                                                                                                                                                                                                                                                    |

| AutoCache Execution Model 104<br>DemandCache Execution Model 106                                                                                                                                                                                                                                                                                 |

| AutoCache Execution Model 104<br>DemandCache Execution Model 106<br>DemandCache for Dynamic Sections 107                                                                                                                                                                                                                                         |

| AutoCache Execution Model 104<br>DemandCache Execution Model 106                                                                                                                                                                                                                                                                                 |

| AutoCache Execution Model 104<br>DemandCache Execution Model 106<br>DemandCache for Dynamic Sections 107<br>DemandCache for Static Sections 108                                                                                                                                                                                                  |

| AutoCache Execution Model104DemandCache Execution Model106DemandCache for Dynamic Sections107DemandCache for Static Sections108Connections in DemandCache108FIFO Connections111                                                                                                                                                                  |

| AutoCache Execution Model104DemandCache Execution Model106DemandCache for Dynamic Sections107DemandCache for Static Sections108Connections in DemandCache108FIFO Connections111Grouped Modules112                                                                                                                                                |

| AutoCache Execution Model104DemandCache Execution Model106DemandCache for Dynamic Sections107DemandCache for Static Sections108Connections in DemandCache108FIFO Connections111Grouped Modules112GPB for Grouped Modules113                                                                                                                      |

| AutoCache Execution Model104DemandCache Execution Model106DemandCache for Dynamic Sections107DemandCache for Static Sections108Connections in DemandCache108FIFO Connections111Grouped Modules112GPB for Grouped Modules113Module Scaling113                                                                                                     |

| AutoCache Execution Model104DemandCache Execution Model106DemandCache for Dynamic Sections107DemandCache for Static Sections108Connections in DemandCache108FIFO Connections111Grouped Modules112GPB for Grouped Modules113Module Scaling113                                                                                                     |

| AutoCache Execution Model 104<br>DemandCache Execution Model 106<br>DemandCache for Dynamic Sections 107<br>DemandCache for Static Sections 108<br>Connections in DemandCache 108<br>FIFO Connections 111<br>Grouped Modules 112<br>GPB for Grouped Modules 113<br>Module Scaling 113<br>Selecting Module Scale Factor 116<br>Standard Sound 116 |

| AutoCache Execution Model104DemandCache Execution Model106DemandCache for Dynamic Sections107DemandCache for Static Sections108Connections in DemandCache108FIFO Connections111Grouped Modules112GPB for Grouped Modules113Module Scaling113Selecting Module Scale Factor116Standard Sound116                                                    |

| AutoCache Execution Model104DemandCache Execution Model106DemandCache for Dynamic Sections107DemandCache for Static Sections108Connections in DemandCache108FIFO Connections111Grouped Modules112GPB for Grouped Modules113Module Scaling113Selecting Module Scale Factor116Standard Sound116Sound Manager Interface117                          |

Chapter 4

# Real Time Manager 123

| About the Real Time Manager 124  |     |

|----------------------------------|-----|

| Real Time Manager Structure 124  |     |

| Guaranteed Processing Bandwidth  | 126 |

| Devices and Clients 127          |     |

| Tasks 130                        |     |

| Modules 131                      |     |

| Module Definition 131            |     |

| Execution Flow for Modules 131   |     |

| Sections 133                     |     |

| Section Definition 133           |     |

| Section Flags and Data Types 134 |     |

| Connecting Sections 135          |     |

|                                  |     |

Using the Real Time Manager 136 Accessing the DSP 137 Creating a Task 140 Loading a Module 141 143 Getting Data Putting the Task to Work 147 Getting Off the DSP Task List 149 Sending Messages 152 From DSP to Host 152 From Host to DSP 153 Message Action Procedure 153 Message Format 154 **Real Time Manager Reference** 155 **Client Routines** 155 **Device Routines** 157 163 Task API Routines Module API Routines 168 173 Section API Routines **FIFO API Routines** 175 Summary of the Real Time Manager 184Constants 184 Data Types 188 Data Structures 189 Trap Macros and Routine Selectors 194

Chapter 5

#### DSP Operating System 203

| About DSP Modules 204<br>DSP3210 Register Model 205  |     |

|------------------------------------------------------|-----|

| 32-Bit Data Transfers 206                            |     |

| DSP Program Information for the Macintosh Programmer | 206 |

| Input and Output Sections 206                        |     |

| Parameter Sections 207                               |     |

| GPB Scaling Vectors 207                              |     |

| Grouping Assumptions 207                             |     |

| Run-Time Environment 207                             |     |

| DSP Operating System Reference 207                   |     |

| Creating a Module 208                                |     |

| Building a Section 210                               |     |

| Code and Variables 212                               |     |

| Data Input 216                                       |     |

| Data Output 219                                      |     |

| DSP Operating System Macros 223                      |     |

| General Manipulation Macros 223                      |     |

| Section Manipulation Macros 225                      |     |

| Module Manipulation Macro 228                        |     |

| 1                                                    |     |

| Task Manipulation Macros        | 229   |     |

|---------------------------------|-------|-----|

| FIFO Manipulation Macros        | 230   |     |

| GPB Manipulation Macros         | 235   |     |

| Semaphore Manipulation Ma       | cros  | 237 |

| Message Manipulation Macro      | o 23  | 9   |

| Summary of the DSP Operating Sy | ystem | 240 |

| Constants 240                   |       |     |

| Routines 252                    |       |     |

|                                 |       |     |

# Part 3 Speech Synthesis and Recognition 261

| Chapter 6 | Speech Manager 263                                             |

|-----------|----------------------------------------------------------------|

|           | Speech Manager Overview 264                                    |

|           | Speech Manager Concepts 265                                    |

|           | Using the Speech Manager 266                                   |

|           | Getting Started 266                                            |

|           | Determining If the Speech Manager Is Available 266             |

|           | Determining Which Version of the Speech Manager Is Running 267 |

|           | Making Some Noise 267                                          |

|           | Determining If Speaking Is Complete 268                        |

|           | A Simple Example 269                                           |

|           | Essential Calls—Simple and Useful 269                          |

|           | Working With Voices 269                                        |

|           | Managing Connections to Speech Synthesizers 273                |

|           | Starting and Stopping Speech 275                               |

|           | Using Basic Speech Controls 276                                |

|           | Putting It All Together 279                                    |

|           | Advanced Routines 280                                          |

|           | Advanced Speech Controls 280                                   |

|           | Converting Text Into Phonemes 285                              |

|           | Getting Information About a Speech Channel 286                 |

|           | Advanced Control Routines 291                                  |

|           | Application-Defined Pronunciation Dictionaries 298             |

|           | Associating a Dictionary With a Speech Channel 299             |

|           | Creating and Editing Dictionaries 301                          |

|           | Advanced Voice Information Routine 301                         |

|           | Embedded Speech Commands 302                                   |

|           | Embedded Speech Command Syntax 302                             |

|           | Embedded Speech Command Set 304                                |

|           | Embedded Speech Command Error Reporting 307                    |

|           | Summary of Phonemes and Prosodic Controls 307                  |

|           | Phoneme Set 307                                                |

|           | Prosodic Controls 309                                          |

viii

| Summary of the Speech Manager |     |     | 310 |  |

|-------------------------------|-----|-----|-----|--|

| Constants                     | 310 |     |     |  |

| Data Types                    | 312 |     |     |  |

| Speech Manager Routines 314   |     |     |     |  |

| Callback Prototypes 315       |     |     |     |  |

| Error Return Codes            |     | 316 |     |  |

#### Chapter 7 Introduction to Speech Recognition 317

How Does Casper Work? 318 319 Software Installation 321 Using the Microphone Getting Started 321 Setting Your Computer's Name 322 Choosing Speech Feedback 323 Setting the Attention Key 324 The Casper User Interface 324 324 **Operational Control** Feedback Control 325 Speech Macro Editor 326 Scripting Tool Requirements 326 326 AppleScript QuicKeys 327 **User Requirements** 327 Using the Speech Macro Editor 328 329 Recording a New Macro 330 Renaming a Macro Saving Macro Changes 330 Loading Macros 330 Built-in Speech Rules and Grammar 331 Performance 332 **Real-Time Response** 332 Types of Errors 333 Acceptable Limits or Constraints 333

Chapter 8

#### Speech Rules 335

Overview 336 Speech Rules Files 342 Speech Rules File Syntax 345 Command Rules 345 Phrases and AppleScript Clauses 347 Internal Category Rules 348 External Category Rules 348

| Context Specifiers    | 349     |     |     |

|-----------------------|---------|-----|-----|

| Default Statements    | 350     |     |     |

| Global Scripts 35     | 1       |     |     |

| CompileRules Error Me | essages | 352 |     |

| Apple Events Speech E | vents   | 354 |     |

| An Example: A Simple  | Checkbo | ook | 354 |

## System Software Modifications 359

Chapter 9

Part 4

## SCSI Manager 4.3 361

| SCSI Manager 4.3 Features 362                    |

|--------------------------------------------------|

| Compatibility 364                                |

| System Performance Impact 364                    |

| Impact on Developers 364                         |

| Design Overview 365                              |

| General Concepts 365                             |

| Transport Layer 367                              |

| SCSI Interface Modules 367                       |

| CAM Deviations 368                               |

| Implementation 368                               |

| Optional Features Not Supported in the SIM 370   |

| Compatibility and Emulation 370                  |

| Virtual Bus 371                                  |

| Data Transfer Descriptions 372                   |

| Guidelines for SCSI Device Driver Developers 373 |

| Booting and Drive Mounting 373                   |

| Asynchronous Behavior 374                        |

| Virtual Memory Operation 376                     |

| Guidelines for SIM/HBA Developers 377            |

| SIM Initialization and General Operation 377     |

| Support for the Old SCSI Manager 378             |

| Interrupt Support 380                            |

| Handshaking of Data Bytes 380                    |

| DMA Support 381                                  |

| SCSI Manager 4.3 Reference 381                   |

| Data Structure 382                               |

| SCSI Manager Parameter Block 382                 |

| Routines 386                                     |

| Driver Routines 386                              |

| SCSI Interface Module Calls to Transport 397     |

| Transport Calls to SCSI Interface Modules 399    |

|                                                  |

| Summary of th | e SCSI Manager 4 | .3 400 |

|---------------|------------------|--------|

| Constants     | 400              |        |

| Data Type     | 403              |        |

| Routines      | 404              |        |

#### Chapter 10 DMA Serial Driver 405

Architecture 406 Changes in Implementation 407 Interrupt Handling 407 DMA Versus Non-DMA Transmissions 408 PollProc Mechanism 408 DMA Use 408

#### Chapter 11 Video Driver 409

Video Television Output 410 New Control and Status Routines 411 NuBus Block Moves 411 Configuration ROM Programming 412 Using the Trap Macro SlotBlockXferCtl 412

| Chapter 12 | New Age Floppy Disk Driver 413                                                                |

|------------|-----------------------------------------------------------------------------------------------|

|            | Floppy Disk Support 414<br>Programming Interface Changes 414<br>Operational Compatibility 415 |

| Chapter 13 | Virtual Memory Manager 417                                                                    |

| Appendix A | DSP d Commands for MacsBug 421<br>Getting Started 421                                         |

|            | Getting Started 421<br>Using the d Commands 421                                               |

d Commands Reference 423

| Appendix B | BugLite User's Guide 427                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Getting Started 427<br>Installation 427<br>What You See When You Launch BugLite 428<br>Tools of the Trade 429<br>Using BugLite 430<br>Getting Information 434<br>Task Info Window 434<br>Module Info Window 434<br>Section Information 436                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Appendix C | Snoopy User's Guide 437                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            | Getting Started 437<br>Installation 437<br>What You See When You Launch Snoopy 438<br>Task/Module/Section Lists 438<br>The Data Display Window 438<br>Run/Store Address Pop-up Menu 439<br>PC Column 440<br>The Breakpoint Column 440<br>Pane Resizers 440<br>Using Snoopy 440<br>Menu Bar 441<br>Control Menu 441<br>Setting and Clearing Breakpoints 442<br>Breakpoint Restrictions 442<br>Single Stepping 443<br>Inspect Menu 443<br>Formatting 444<br>Editing Data 444<br>Windows Menu 445<br>Additional Information Windows 445<br>Current PC 446<br>The DSP Operating System Routines 446<br>The EVT 447<br>On-Chip SRAM 448<br>Registers 448<br>Standard Menus 449<br>Find Menu 449<br>Module Menu 451 |

| Appendix D | Mechanical Details 453 |

|------------|------------------------|

|            |                        |

|            |                        |

|            | Glossary 477           |

|            |                        |

|            |                        |

|            | Index 483              |

# Figures, Tables, and Listings

| Chapter 1 The Macintosh Quadra 840Av and<br>Macintosh Centris 660Av Computers 3 |                            |                                                                             |

|---------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------|

|                                                                                 | Table 1-1                  | Gestalt values for the Macintosh Quadra 840Av and Macintosh Centris 660Av 8 |

| Chapter 2                                                                       | Hardware De                | tails 9                                                                     |

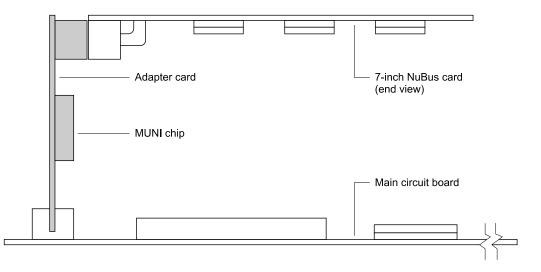

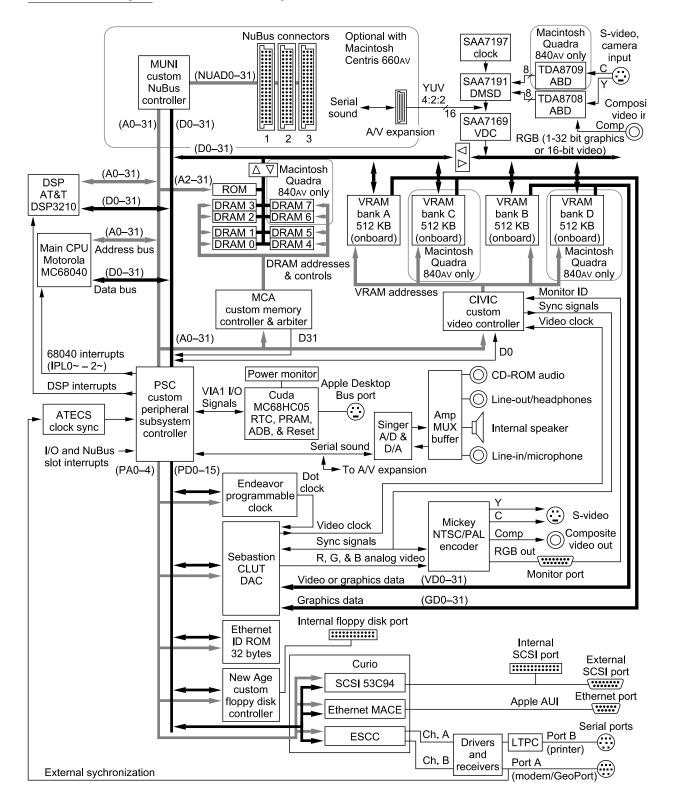

|                                                                                 | Figure 2-1                 | Functional diagram 11                                                       |

|                                                                                 | Figure 2-2                 | ADB socket 21                                                               |

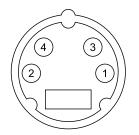

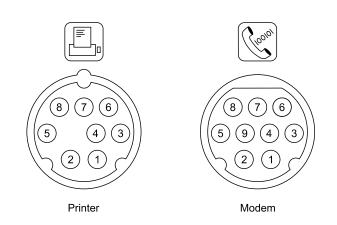

|                                                                                 | Figure 2-3                 | Serial port connectors 23                                                   |

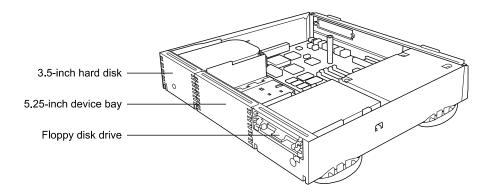

|                                                                                 | Figure 2-4                 | Macintosh Centris 660Av internal SCSI device space 24                       |

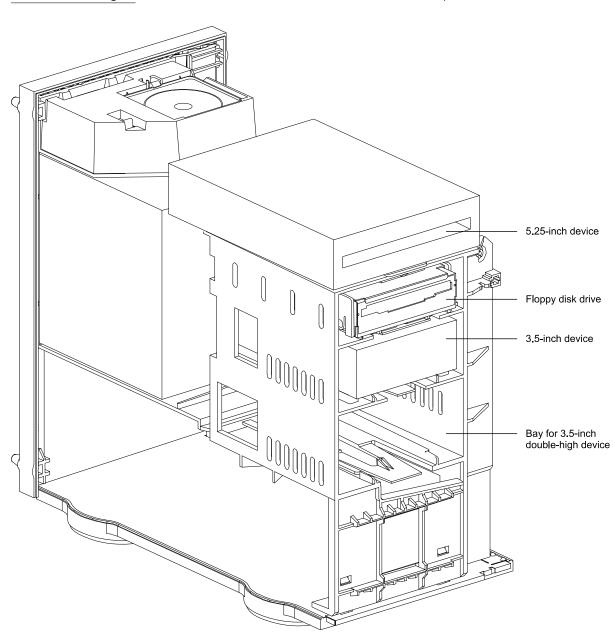

|                                                                                 | Figure 2-5                 | Macintosh Quadra 840Av internal SCSI device space 25                        |

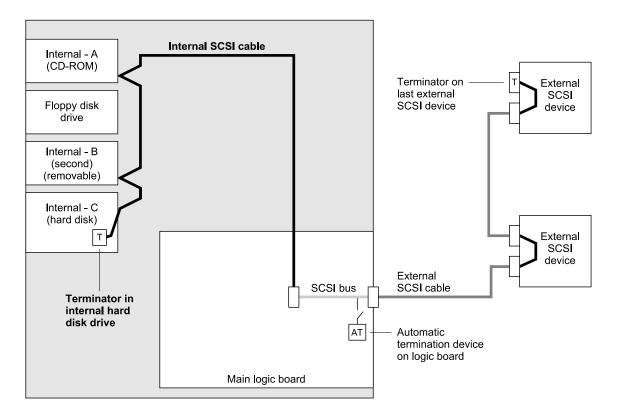

|                                                                                 | Figure 2-6                 | SCSI bus terminators in a typical Macintosh Quadra 840Av configuration 27   |

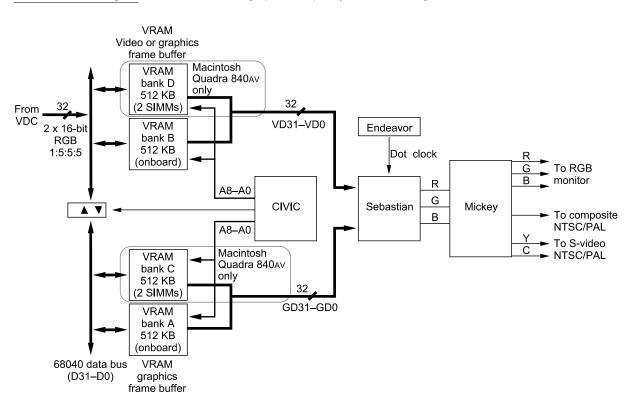

|                                                                                 | Figure 2-7                 | Video and graphics output system block diagram 31                           |

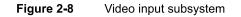

|                                                                                 | Figure 2-8                 | Video input subsystem 32                                                    |

|                                                                                 | Figure 2-9                 | Video input connector 33                                                    |

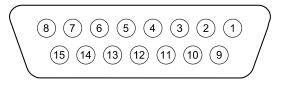

|                                                                                 | Figure 2-10                | Video monitor connector 35                                                  |

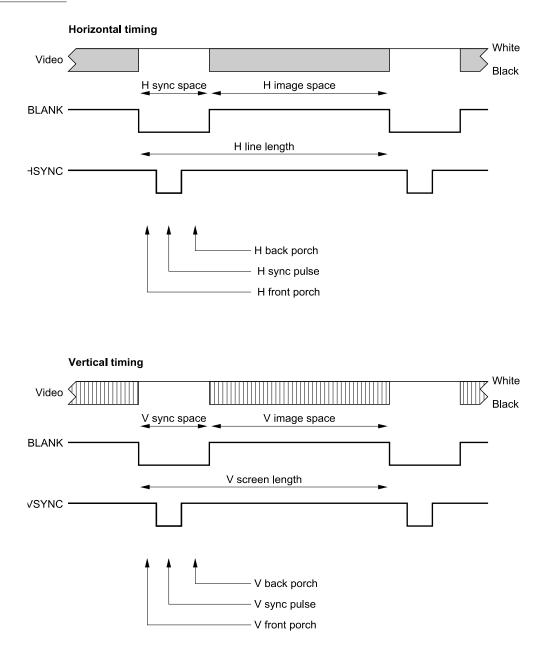

|                                                                                 | Figure 2-11                | Video timing diagram 36                                                     |

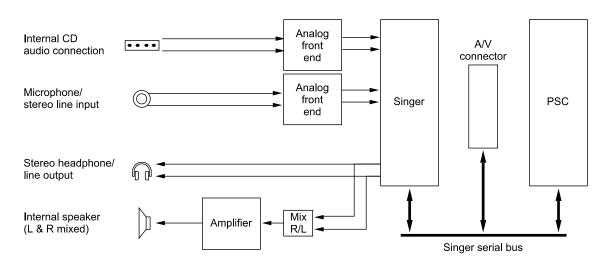

|                                                                                 | Figure 2-12                | Sound I/O components 39                                                     |

|                                                                                 | Figure 2-13                | Macintosh Centris 660Av accessory card mounting 40                          |

|                                                                                 | Figure 2-14                | DAV connection on a NuBus card 43                                           |

|                                                                                 | Figure 2-15                | Singer sound frame 44                                                       |

|                                                                                 | Figure 2-16                | Sound frame and word synchronization 45                                     |

|                                                                                 | Figure 2-17<br>Figure 2-18 | Sound subframe synchronization 45<br>DAV video timing 46                    |

|                                                                                 | Figure 2-19                | Burst write timing 51                                                       |

|                                                                                 | Figure 2-10                | RAM SIMM mechanical dimensions 53                                           |

|                                                                                 | Figure 2-21                | VRAM SIMM mechanical dimensions 54                                          |

|                                                                                 | Table 2-1                  | External dimensions 10                                                      |

|                                                                                 | Table 2-2                  | Clock frequencies 17                                                        |

|                                                                                 | Table 2-1                  | DRAM configurations 19                                                      |

|                                                                                 | Table 2-3                  | DRAM access times 20                                                        |

|                                                                                 | Table 2-4                  | ADB pin assignments 22                                                      |

|                                                                                 | Table 2-5                  | Ethernet port pin assignments 22                                            |

|                                                                                 | Table 2-6                  | Serial port pin assignments 23                                              |

|                                                                                 | Table 2-7                  | SCSI power budgets 24                                                       |

|                                                                                 | Table 2-8                  | SCSI pin assignments 26                                                     |

|                                                                                 | Table 2-9                  | Floppy disk drive connector pin assignments 28                              |

|                                                                                 | Table 2-10                 | PSC DMA channels 29                                                         |

|                                                                                 | Table 2-11                 | Priority of DMA channel access 30                                           |

|                                                                                 | Table 2-12                 | Video input connector pin assignments 33                                    |

|                                                                                 | Table 2-13                 | VRAM sizes and monitor color depths 34                                      |

| Table 2-14 | Apple monitor timing values 37                            |

|------------|-----------------------------------------------------------|

| Table 2-15 | Sound I/O signals 38                                      |

| Table 2-16 | MUNI buffer capacities 40                                 |

| Table 2-17 | NuBus pin assignments 41                                  |

| Table 2-18 | Power budget for each slot card 42                        |

| Table 2-19 | DAV connector pin assignments 43                          |

| Table 2-20 | DAV connector sound signals 44                            |

| Table 2-21 | Macintosh Centris 660AV PDS connector pin assignments 47  |

| Table 3-22 | Restricted microprocessor signals on the PDS connector 49 |

| Table 3-23 | Nonmicroprocessor signals on the PDS connector 50         |

| Table 3-24 | RAM SIMM pin assignments 52                               |

| Table 3-25 | VRAM SIMM pin assignments 55                              |

| Table 3-26 | VRAM access times 56                                      |

Chapter 3

Introduction to Real-Time Data Processing 59

| Figure 3-1                 | Frames 62                                                       |

|----------------------------|-----------------------------------------------------------------|

| Figure 3-2                 | Real-time and timeshare tasks 62                                |

| Figure 3-3                 | Task list 63                                                    |

| Figure 3-4                 | Real-time data processing organization 65                       |

| Figure 3-5                 | Four-layer Macintosh model 67                                   |

| Figure 3-6                 | Six-layer model 68<br>Example of toolbox and driver layers 69   |

| Figure 3-7                 |                                                                 |

| Figure 3-8                 |                                                                 |

| Figure 3-9                 | ······                                                          |

| Figure 3-10                |                                                                 |

| Figure 3-11                | Frame-based processing 73<br>Multiple code module processing 74 |

| Figure 3-12                | Multiple code module processing 74<br>Process data flow 74      |

| Figure 3-13                | DSPAddress structure 77                                         |

| Figure 3-14<br>Figure 3-15 | Smooth and lumpy DSP algorithms 80                              |

| Figure 3-16                | Timeshare capacity figures 83                                   |

| Figure 3-17                | Task with two modules 85                                        |

| Figure 3-18                | The module data structure 86                                    |

| Figure 3-19                | The section data structure 86                                   |

| Figure 3-20                | Dual-container AutoCache example 88                             |

| Figure 3-21                | Data structure overview 91                                      |

| Figure 3-22                | Example of FIFO buffers 92                                      |

| Figure 3-23                | The FIFO and its data header 93                                 |

| Figure 3-24                | Code module data flow with AIAOs 94                             |

| Figure 3-25                | Connections between modules 95                                  |

| Figure 3-26                | ITB connections for previous and next tasks 98                  |

| Figure 3-27                | ITB open and close task configuration 99                        |

| Figure 3-28                | Example of intertask buffers 100                                |

| Figure 3-29                | Example of DSP task for telephone answering 112                 |

| Figure 3-30                | Controlling GPB in grouped modules 113                          |

| Figure 3-31                | DSP Sound Manager and Sound Driver 116                          |

| Figure 3-32                | Sound Manager processing 117                                    |

| Figure 3-33                | Standard sound task list 118                                    |

| Figure 3-34                | Equalizer used as a recorder task 119                           |

|                            |                                                                 |

xvi

| Figure 3-35 | Equalizer used as a player task 120        |  |

|-------------|--------------------------------------------|--|

| Figure 3-36 | Equalizer used as a preprocess task 121    |  |

|             |                                            |  |

| Table 3-1   | Primary and secondary pointers 78          |  |

| Table 3-2   | On-chip and off-chip addresses 79          |  |

| Table 3-3   | Run-time AutoCache flag combinations 105   |  |

| Table 3-4   | Run-time DemandCache flag combinations 110 |  |

|             |                                            |  |

#### Chapter 4

#### Real Time Manager 123

| Figure 4-1  | DSP subsystem overview 125                           |

|-------------|------------------------------------------------------|

| Figure 4-2  | Examples of different GPB values 127                 |

| Figure 4-3  | Examples of different execution paths 132            |

| Figure 4-4  | Section interconnection 136                          |

| Figure 4-5  | Task example 137                                     |

| Figure 4-6  | Task after loading the CD-XA player module 142       |

| Figure 4-7  | CD-XA player module structure 142                    |

| Figure 4-8  | Module structure after DSPNewFIFO call 144           |

| Figure 4-9  | Task structure after DSPLoadModule call    144       |

| Figure 4-10 | Sections contained in the equalizer module 145       |

| Figure 4-11 | CD-XA player with DSPConnectSections to equalizer 14 |

| Figure 4-12 | Message passing from DSP to host 153                 |

| Figure 4-13 | FIFO threshold 184                                   |

| Table 4-1   | Section flags 134                                    |

| Table 4-2   | Section data-type flags 135                          |

| Table 4-3   | Setting up a task 138                                |

| Table 4-4   | Task insertion locations 148                         |

| Table 4-5   | Removing a task 149                                  |

| Table 4-6   | Message masks 182                                    |

| Listing 4-1 | DSP bandwidth structure 126                          |

| Listing 4-2 | DSP device parameter block structure 128             |

| Listing 4-3 | CPU device parameter block structure 129             |

| Listing 4-4 | Client information parameter block structure 129     |

| Listing 4-5 | Task information parameter block structure 130       |

| Listing 4-6 | Module information parameter block structure 131     |

| Listing 4-7 | Section information parameter block structure 133    |

| Listing 4-8 | Message action procedure 154                         |

| Listing 4-9 | DSP message format 154                               |

| DSP Operati | ng System 203                                        |

| Figure 5-1  | DSP programming model 205                            |

| Figure 5-2  | DSR modulo atrusturo 200                             |

| Figure 5-1             | DSP programming model                         | 205   |     |

|------------------------|-----------------------------------------------|-------|-----|

| Figure 5-2             | DSP module structure                          | 208   |     |

| Figure 5-3             | DSP message structure                         | 240   |     |

| Table 5-1<br>Table 5-2 | DSP3210 register assignn<br>Section flags 211 | nents | 205 |

Chapter 5

|            | Table 5-3<br>Table 5-4<br>Table 5-5                                                           | DSP3210 bank preferences section flags 211<br>Buffer type section flags 211<br>Data type flags 212                                                                                                                      |

|------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 6  | Speech Manag                                                                                  | ger 263                                                                                                                                                                                                                 |

|            | Figure 6-1                                                                                    | Speech synthesis components 264                                                                                                                                                                                         |

|            | Table 6-1<br>Table 6-2<br>Table 6-3                                                           | Embedded speech commands 304<br>American English phoneme symbols 308<br>Prosodic control symbols 309                                                                                                                    |

|            | Listing 6-1<br>Listing 6-2<br>Listing 6-3<br>Listing 6-4                                      | Determining if the Speech Manager is available 266<br>Elementary Speech Manager calls 269<br>Getting information about a voice 273<br>Putting it all together 279                                                       |

| Chapter 7  | Introduction to                                                                               | Speech Recognition 317                                                                                                                                                                                                  |

|            | Figure 7-1<br>Figure 7-2<br>Figure 7-3<br>Figure 7-4<br>Figure 7-5<br>Figure 7-6<br>Table 7-1 | Speech Setup control panel322Setting your computer's name323Choosing feedback signals323Setting the attention key324Typical Speech Macro document window328Typical New Macro window329Grammatical naming conventions333 |

| Chapter 9  | SCSI Manage                                                                                   | r <b>4.3</b> 361                                                                                                                                                                                                        |

|            | Figure 9-1                                                                                    | SCSI Manager software hierarchy 366                                                                                                                                                                                     |

|            | Table 9-1<br>Table 9-2<br>Table 9-3                                                           | CAM to ACAM terminology conversion 366<br>Old call parameter conversion 379<br>SCSI Manager 4.3 function codes 388                                                                                                      |

|            | Listing 9-1<br>Listing 9-2                                                                    | Supported old SCSI Manager routines371SIM initialization information structure377                                                                                                                                       |

| Appendix A | DSP d Comma                                                                                   | ands for MacsBug 421                                                                                                                                                                                                    |

|            | Table A-1<br>Table A-2<br>Table A-3<br>Table A-4<br>Table A-5                                 | d commands423Task flags423Module flags425Section flags425Section types426                                                                                                                                               |

xviii

| Appendix B | BugLite User               | 's Guide 427                                    |

|------------|----------------------------|-------------------------------------------------|

|            | Figure B-1                 | Task window 428                                 |

|            | Figure B-2                 | Open File dialog box 429                        |

|            | Figure B-3                 | Graphical representation of a task 430          |

|            | Figure B-4                 | Graphical representation of a module 431        |

|            | Figure B-5                 | Task connected to a module 431                  |

|            | Figure B-6                 | Disk play of "funky" file 432                   |

|            | Figure B-7                 | Disk player connected to input buffer 432       |

|            | Figure B-8                 | Speaker connection icon 432                     |

|            | Figure B-9                 | Data output buffers connected to speakers 433   |

|            | Figure B-10                | Task with task active indicator 433             |

|            | Figure B-11                | Task Get Info window 434                        |

|            | Figure B-12                | Module Get Info window 435                      |

|            | Figure B-13                | Section Get Info window 436                     |

|            |                            |                                                 |

| Appendix C | Snoopy User                | 's Guide 437                                    |

|            | Figure C-1                 | DSP Control window 438                          |

|            | Figure C-2                 | Real Time Tasks window 439                      |

|            | Figure C-3                 | Run/Store Address pop-up menu 439               |

|            | Figure C-4                 | Vertical and horizontal pane resizers 440       |

|            | Figure C-5                 | Menu bar 441                                    |

|            | Figure C-6                 | Control menu 441                                |

|            | Figure C-7                 | Control commands after break 441                |

|            | Figure C-8                 | Setting breakpoints 442                         |

|            | Figure C-9                 | Setting the breakpoint counter 442              |

|            | Figure C-10                | Inspect menu 443                                |

|            | Figure C-11                | Data display format menu 443                    |

|            | Figure C-12                | Data editing window 444                         |

|            | Figure C-12                | Defined data types 444                          |

|            | Figure C-14                | Windows menu 445                                |

|            | -                          | Current PC window 446                           |

|            | Figure C-15<br>Figure C-16 |                                                 |

|            | -                          | 1 3 3                                           |

|            | Figure C-17                | EVT window 447                                  |

|            | Figure C-18                | On-Chip SRAM window 448                         |

|            | Figure C-19                | Example of SRAM layout 448                      |

|            | Figure C-20                | Registers window 449                            |

|            | Figure C-21                | Find menu 449                                   |

|            | Figure C-22                | Find Command dialog box 450                     |

|            | Figure C-23                | Find Data Types menu 450                        |

|            | Figure C-24                | Search In selection menu 451                    |

|            | Figure C-25                | Module menu 451                                 |

|            | Figure C-26                | Error in loading symbolic table 452             |

| Appendix D | Mechanical [               | Details 453                                     |

|            | Figure D-1                 | CD bezel for the Macintosh Centris 660av 455    |

|            | Figure D-2                 | Blank bezel for the Macintosh Centris 660Av 457 |

|            | Figure D-2                 | Mounting sled for 5.25-inch SCSI devices 459    |

|            | Figure D-S                 |                                                 |

| Figure D-4  | Shield for the CD bezel in the Macintosh Centris 660Av                    | 461 |

|-------------|---------------------------------------------------------------------------|-----|

| Figure D-5  | Magnetic shield for CD-ROM drives 463                                     |     |

| Figure D-6  | Blank bezel for the Macintosh Quadra 840Av 465                            |     |

| Figure D-7  | CD bezel for the Macintosh Quadra 840Av 467                               |     |

| Figure D-8  | Accessory-card bracket for the Macintosh Centris 660AV                    | 469 |

| Figure D-9  | Insulator for the Macintosh Centris 660Av accessory-<br>card bracket 471  |     |

| Figure D-10 | EMI shield for the Macintosh Centris 660Av accessory-<br>card bracket 473 |     |

| Figure D-11 | NuBus adapter card for the Macintosh Centris 660Av                        | 475 |

# About This Developer Note

This developer note introduces the Macintosh Quadra 840AV and the Macintosh Centris 660AV, Apple's newest extensions to the Macintosh family of personal computers. It is written primarily for experienced Macintosh hardware and software engineers who want to create products that are compatible with these computers.

This note assumes that you are already familiar with both the functionality and programming requirements of Macintosh computers. If you are unfamiliar with Macintosh computers or would like more technical information, you may want to obtain copies of the related technical manuals listed in "Supplementary Documents," later in this preface.

## Contents of This Note

This developer note is divided into four main parts, containing a total of 13 chapters.

Part 1, "Hardware," describes the Macintosh Quadra 840AV and Macintosh Centris 660AV computers from a hardware viewpoint. It contains two chapters:

- Chapter 1, "The Macintosh Quadra 840AV and Macintosh Centris 660AV Computers," gives you an overview of the configurations and features of these products.

- Chapter 2, "Hardware Details," describes the circuit boards for the computers, including their physical layout, functional units, signal timing and other electronic characteristics, input and output connectors, and interfaces with other equipment.

Part 2, "Real-Time Data Processing," describes the software technology of the digital signal processing (DSP) facilities in the Macintosh Quadra 840AV and Macintosh Centris 660AV. It contains three chapters:

- Chapter 3, "Introduction to Real-Time Data Processing," summarizes the software architecture of their real-time data processing facility. This facility consists of an AT&T DSP3210 chip that performs data-processing operations for applications that contain DSP code.

- Chapter 4, "Real Time Manager," describes a new part of the Macintosh system software that supplies all the services an application requires to use the digital signal processor, including loading and running DSP code and performing DSP memory management.

- Chapter 5, "DSP Operating System," covers the DSP operating system, contained in the DSP chip. It provides the services every DSP program needs to work with the Macintosh Operating System.

Part 3, "Speech Synthesis and Recognition," explains the capabilities of the Macintosh Quadra 840Av and Macintosh Centris 660AV system software for generating and understanding human speech. It contains three chapters:

- Chapter 6, "Speech Manager," describes a new Macintosh system software manager that provides a standardized way for applications to generate synthesized speech. The Speech Manager also lets an application control one or more speech synthesizers, which generate spoken sound in specific languages, intonations, and speaking styles.

- Chapter 7, "Introduction to Speech Recognition," contains a basic tutorial for the Speech Setup control panel. This control panel provides commands for controlling the speech recognition function.

- Chapter 8, "Speech Rules," explains the speech rules that are built into the Macintosh Quadra 840AV and Macintosh Centris 660AV system software.

Part 4, "System Software Modifications," describe miscellaneous changes to the Macintosh Quadra 840AV and Macintosh Centris 660AV system software, including a new manager for the internal and external SCSI (Small Computer System Interface) ports. It contains five chapters:

- Chapter 9, "SCSI Manager 4.3," describes the new SCSI Manager.

- Chapter 10, "DMA Serial Driver," details the new hardware-independent serial driver that uses direct memory access (DMA).

- Chapter 11, "Video Driver," describes changes to the video driver.

- Chapter 12, "New Age Floppy Disk Driver," lists changes to the floppy disk driver and tells you how they affect floppy disk compatibility with other Macintosh computers.

- Chapter 13, "Virtual Memory Manager," details how the Virtual Memory Manager no longer disables interrupts when performing certain tasks.

Four appendixes follow the main parts of this note. They contain information that can help you with specific development tasks:

- Appendix A, "DSP d Commands for MacsBug," describes three new d commands added to Macsbug that help in debugging DSP code.

- Appendix B, "BugLite User's Guide," describes a DSP module installer with a graphical user interface. It helps programmers create and install tasks to be executed by the DSP.

- Appendix C, "Snoopy User's Guide," tells you how to use a browser and debugger for the DSP. It helps programmers debug real-time tasks that run on the DSP.

- Appendix D, "Mechanical Details" contains foldout drawings of the physical mounting facilities that are provided for internal SCSI devices and accessory cards in the Macintosh Quadra 840AV and Macintosh Centris 660AV.

At the end of this developer note are a glossary and an index. Terms listed in the glossary are printed in **boldface** where they are first defined in the text.

## Hardware Overview

The Macintosh Quadra 840AV and Macintosh Centris 660AV have the most features of any models in the Macintosh family of desktop computers. The Macintosh Quadra 840AV is also the fastest Macintosh computer. The two models have nearly identical electronic circuitry. Their differences are that the Macintosh Quadra 840AV is housed in a minitower enclosure with more room for internal disk drives and accessory cards, while the Macintosh Centris 660AV is housed in a low-profile enclosure designed to be placed under the user's monitor. The Macintosh Centris 660AV also offers somewhat lower speed and performance than the Macintosh Quadra 840AV and sells for a lower price.

Principal new hardware features of these computers include

- digital signal processing, using an AT&T DSP3210 chip

- video input and output facilities in NTSC, PAL, and SECAM formats

- high-quality sound processing

- direct memory access for peripheral devices

- integrated telephone I/O for ISDN, fax, and other signal forms

Chapter 1, "The Macintosh Quadra 840AV and Macintosh Centris 660AV Computers," describes these and other hardware features; Chapter 2, "Hardware Details," provides deeper technical information.

## Software Overview

The Macintosh Quadra 840AV and Macintosh Centris 660AV are supplied with essentially identical versions of the Macintosh System 7.1 software, in ROM and on the internal hard disk. For technical information about standard System 7.1 software, see *Inside Macintosh*, listed in "Supplementary Documents," later in this preface. However, the system software in the Macintosh Quadra 840AV and Macintosh Centris 660AV also contains significant changes and additions to System 7.1. This section summarizes those changes and additions, which are described in greater detail in Chapters 3 through 13.

#### **Digital Signal Processing**

The Macintosh Quadra 840AV and Macintosh Centris 660AV use a digital signal processor (DSP) chip separate from the main microprocessor to perform real-time data processing, such as playing sound files. In addition, the DSP chip can perform processing-intensive operations that do not require real-time execution, such as file compression and three-dimensional drawing. Chapter 3, "Introduction to Real-Time Data Processing," explains this capability in more detail.

To take advantage of the DSP capability, you must write and compile DSP code and include it with your application. A new addition to the Macintosh system software, the Real Time Manager, supplies the services your application needs to handle DSP code. It contains the calls needed to access the DSP, load and run DSP code, and transfer data to and from the DSP. The Real Time Manager also handles system memory management for the DSP and automatically locks and unlocks memory that is accessed by both DSP and Macintosh software. Chapter 4, "Real Time Manager," describes these functions in detail.

The Real Time Manager coordinates usage of the DSP chip through a new concept called guaranteed processing bandwidth (GPB). This type of control guarantees that any application that is granted access to the DSP will always process the needed data at the time required.

The DSP operating system, contained in the DSP chip, provides the services that DSP code needs to drive the chip and work with the Macintosh Operating System. The DSP operating system's application programming interface (API) defines how you can create a resource that can be loaded and run on the DSP chip. It automatically handles on-chip memory management to minimize recaching of code and data used by more than one DSP code module. For real-time applications, actual GPB requirements are determined and saved automatically in the DSP Preferences file. For timeshare applications, the program context is automatically saved when execution switches to real-time code.

The DSP operating system provides a run-time environment for the DSP code modules that minimizes programmer difficulties while providing robust support for a variety of tasks. Caching and saving of data and variables can be handled by the DSP operating system or can be explicitly controlled by the programmer. You can exercise complete control over running DSP code or, by setting a counter, can cause code execution to be determined dynamically at run time. For further information, see Chapter 5, "DSP Operating System."

#### Text-to-Speech Conversion

A new Macintosh manager, the Speech Manager, provides a standardized API for applications to generate synthesized speech. A single call provides simple text-to-speech operation. Other API calls provide more detailed speech

features. Word pronunciation can also be defined by means of embedded commands within the text string being spoken. Chapter 6, "Speech Manager," provides full details of these new capabilities.

### Speech Recognition

A new Macintosh system feature, the Speech Recognition Control Panel, provides start, stop, and parameter setup commands for controlling speech recognition behavior. In the Macintosh Quadra 840AV and Macintosh Centris 660AV, built-in speech recognition is provided for many Macintosh system operations. The standard File and Edit menu commands are fully supported, as are the Finder operations. For example, opening the Control Panels folder is as easy as saying *open control panels*.

User-defined speech macros let you customize the speech recognition software to recognize application-specific speech input for performing common tasks. A 60,000-word dictionary allows selection from a wide variety of words to define spoken phrases that trigger user-defined operations by means of speech macros.

Chapter 7, "Introduction to Speech Recognition," describes the current user controls for speech command in the Macintosh Quadra 840AV and Macintosh Centris 660AV. Chapter 8, "Speech Rules," provides information about further programmable controls for speech recognition.

### New SCSI Manager

SCSI Manager 4.3 incorporates a new multilevel architecture that affects all modes of Small Computer System Interface (SCSI) operation. It uses a parameter-block-based programming interface for executing SCSI inputoutput (I/O) requests, which contains all the information required to complete each I/O operation. The new architecture provides a hardwareindependent interface to the SCSI Manager. The SCSI driver layer passes the hardware support it provides to the SCSI Manager for complete hardware support. The SCSI Manager follows the phases driven by the target and eliminates the need to track the SCSI bus phases.

SCSI Manager 4.3 supports SCSI connect/disconnect, parity transmission and parity error detection, all SCSI-2 mandatory messages, SCSI Fast or Wide, and autosense. The SCSI DMA supports asynchronous protocols using both multiple bus and multiple logic units on each target.

Besides supporting these new features, SCSI Manager 4.3 also supports the existing SCSI device drivers with little or no modification. However, you should evaluate your existing drivers for compatibility and incorporate the new features where possible. See Chapter 9, "SCSI Manager 4.3," for further details.

#### Other System Software Changes

The DMA serial driver was completely rewritten internally. However, there are no API changes. The major operational changes affect interrupt handling and DMA versus non-DMA transmissions, elimination of the PollProc mechanism, and use of the new DMA chip. For technical details, see Chapter 10, "DMA Serial Driver."

The video driver has been modified as a result of new video capabilities. Changes and additions to the video driver are described in Chapter 11, "Video Driver."

The floppy disk driver has been modified to work with the New Age floppy disk drive controller. This has resulted in minor changes to the floppy disk drive control API, as described in Chapter 12, "New Age Floppy Disk Driver."

The Virtual Memory Manager has been changed so that it no longer disables interrupts when performing certain tasks. These tasks are listed in Chapter 13, "Virtual Memory Manager."

### Supplementary Documents

The following documents provide information that complements or extends the information in this developer note:

#### **Apple Computer:**

Inside Macintosh is a collection of books, organized by topic, that describe the system software of Macintosh computers. Together, these books provide the essential reference for programmers, software designers, and engineers. Current volumes include the following titles: Inside Macintosh: Overview Inside Macintosh: Toolbox Essentials Inside Macintosh: More Macintosh Toolbox Inside Macintosh: Files Inside Macintosh: Processes Inside Macintosh: Memory Inside Macintosh: Operating System Utilities Inside Macintosh: Imaging Inside Macintosh: Text Inside Macintosh: Interapplication Communication Inside Macintosh: Devices *Inside Macintosh: QuickTime* Inside Macintosh: QuickTime Components Inside Macintosh: Networking

*Technical Introduction to the Macintosh Family,* second edition, surveys the complete Macintosh family of computers from the developer's point of view.

#### PREFACE

*Macintosh Human Interface Guidelines* provides authoritative information on the theory behind the Macintosh "look and feel" and Apple's standard ways of using individual interface components.

*Designing Cards and Drivers for the Macintosh Family,* third edition, explains the hardware and software requirements for drivers and NuBus '90 accessory cards compatible with Macintosh computers, including the Macintosh Quadra 840Av and Macintosh Centris 660Av.

Technical Note 144 (*Macintosh Color Monitor Connections*) and Technical Note 326 (*M.HW.SenseLines*) provide technical details of the interfaces to various Apple and third-party monitors.

The *NuBus Block Transfers* technical note provides information about block data transfers to and from accessory cards.

Macintosh Classic II, Macintosh PowerBook Family, Macintosh Quadra Family, Macintosh Centris 610, Macintosh Centris 650, and Macintosh Quadra 800 Developer Notes include hardware details for these computers.

The Apple publications listed above are available from APDA, Apple's source for development tools and publications. APDA offers convenient worldwide access to over three hundred Apple and third-party development tools, resources, and information for anyone interested in developing applications on Apple platforms. For a free copy of the *APDA Tools Catalog*, call 1-800-282-2732 (United States), 1-800-637-0029 (Canada), or 716-871-6555 (International).

The following documents are available from the organizations listed:

#### AT&T:

WEDSP3210 Digital Signal Processor Information Manual

#### Comité Consultatif International Radio (CCIR):

Recommended Standard 601-2.

#### **IT&T Semiconductors:**

ASCO 2300 Audio-Stereo Codec Specification

#### Motorola:

MC68040 32-Bit Microprocessor User's Manual MC68040 32-Bit Microprocessor Programmer's Reference Manual MC68040 32-Bit Microprocessor Designer's Handbook

#### **Phillips:**

7169 Video Data Path Chip data sheet 7191B Digital Multistandard Decoder data sheet

## Standard Abbreviations

Acronyms and abbreviations that are specific to Macintosh technology are spelled out in the text where they first occur and are listed in the glossary. Other contractions commonly used in the electronics industry are not spelled out. They include the following:

| А    | amperes      | mm  | millimeters      |

|------|--------------|-----|------------------|

| cm   | centimeters  | ms  | milliseconds     |

| dB   | decibels     | mV  | millivolts       |

| GB   | gigabytes    | NC  | no connection    |

| KB   | kilobytes    | ns  | nanoseconds      |

| Kbit | kilobits     | pF  | picofarads       |

| kHz  | kilohertz    | rms | root mean square |

| kΩ   | kilohms      | V   | volts            |

| mA   | milliamperes | μF  | microfarads      |

| MB   | megabytes    | μs  | microseconds     |

| Mbit | megabits     | Ω   | ohms             |

|      |              |     |                  |

xxviii

# Hardware