#

## MICROSOFT CORPORATION

Petitioner

V.

# BRADIUM TECHNOLOGIES LLC

Patent Owner

CASE: To Be Assigned

Patent No. 8,924,506 B2

DECLARATION OF PROF. WILLIAM R. MICHALSON IN SUPPORT OF PETITION FOR *INTER PARTES* REVIEW

OF U.S. PATENT NO. 8,924,506 B2

I hereby declare that all the statements made in this Declaration are of my own knowledge and true; that all statements made on information and belief are believed to be true; and further that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under 18 U.S.C. 1001 and that such willful false statements may jeopardize the validity of the application or any patent issued thereon.

I declare under the penalty of perjury that all statements made in this Declaration are true and correct.

Executed June 2nd 2015 in Douglas , MA

William R. Michalson

# TABLE OF CONTENTS

|       |                                                         |                                                | Page |  |

|-------|---------------------------------------------------------|------------------------------------------------|------|--|

| LIST  | OF A                                                    | APPENDICES                                     | iv   |  |

| I.    | INTRODUCTION1                                           |                                                |      |  |

| II.   | SUMMARY OF OPINIONS                                     |                                                |      |  |

| III.  | QUALIFICATIONS AND EXPERIENCE.                          |                                                |      |  |

|       | A.                                                      | Education and Work Experience                  | 4    |  |

|       | B.                                                      | Compensation                                   | 8    |  |

|       | C.                                                      | Documents and Other Materials Relied Upon      | 8    |  |

| IV.   | STATEMENT OF LEGAL PRINCIPLES.                          |                                                |      |  |

|       | A.                                                      | Claim Construction                             | 9    |  |

|       | B.                                                      | Anticipation                                   | 9    |  |

|       | C.                                                      | Obviousness                                    | 10   |  |

| V.    | LEVEL OF ORDINARY SKILL IN THE ART10                    |                                                |      |  |

| VI.   | TECHNOLOGY BACKGROUND OF THE 506 PATENT                 |                                                |      |  |

|       | A.                                                      | Data Communications Over the Internet          | 13   |  |

|       | B.                                                      | Data Communications in Wireless Mobile Systems | 15   |  |

|       | C.                                                      | C. Image Tiles and Image Pyramids1             |      |  |

|       | D.                                                      |                                                |      |  |

|       | E. Progressive Image Resolution Enhancement             |                                                | 22   |  |

|       | F.                                                      | Three-Dimensional Graphics                     | 24   |  |

|       |                                                         | 1. Overview of 3D Computer Graphics principles | 24   |  |

|       |                                                         | 2. Texture                                     | 30   |  |

|       | G.                                                      | Mip-Maps                                       | 34   |  |

|       | Н.                                                      | Progressive Meshes                             | 40   |  |

| VII.  | OVERVIEW OF THE 506 PATENT41                            |                                                |      |  |

| VIII. | IDENTIFICATION OF THE PRIOR ART AND SUMMARY OF OPINIONS |                                                |      |  |

| IX.   | CLAIM CONSTRUCTION                                      |                                                |      |  |

| X.    | UNPATENTABILITY OF THE 506 PATENT CLAIMS48              |                                                |      |  |

# TABLE OF CONTENTS

(continued)

| A. | GRO                                                                          | OUND 1: CLAIMS 1-21 ARE UNPATENTABLE UNDER                                                                                                    |     |  |  |

|----|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

|    | 35 U.S.C. § 103(a) AS BEING OBVIOUS OVER POTMESIL, HORNBACKER, and Lindstrom |                                                                                                                                               |     |  |  |

|    | 1.                                                                           | Overview of Potmesil, Hornbacker, and Lindstrom                                                                                               | 50  |  |  |

|    | 2.                                                                           | Motivation to Combine Potmesil, Hornbacker, and Lindstrom.                                                                                    | 58  |  |  |

|    | 3.                                                                           | Claim 1 is Rendered Obvious by Potmesil, and Hornbacker, and Lindstrom                                                                        | 61  |  |  |

|    | 4.                                                                           | Claims 2-7 are Rendered Obvious by Potmesil, Hornbacker, and Lindstrom                                                                        | 73  |  |  |

|    | 5.                                                                           | Claim 8 is Rendered Obvious by Potmesil, Hornbacker, and Lindstrom                                                                            | 81  |  |  |

|    | 6.                                                                           | Claims 9-14 are Rendered Obvious by Potmesil, Hornbacker, and Lindstrom                                                                       | 92  |  |  |

|    | 7.                                                                           | Claim 15 is Rendered Obvious Over Potmesil, Hornbacker, and Lindstrom                                                                         | 94  |  |  |

|    | 8.                                                                           | Claims 16-21 are rendered obvious over Potmesil, Hornbacker, and Lindstrom                                                                    | 100 |  |  |

| В. | UNF<br>OBV                                                                   | OUND 2: CLAIMS 1-3, 5-10, 12-17 AND 19-21 ARE PATENTABLE UNDER 35 U.S.C. § 103(a) AS BEING VIOUS OVER LIGTENBERG IN VIEW OF RUTLEDGE O COOPER | 102 |  |  |

|    | 1.                                                                           | Claim 1 is Rendered Obvious by Ligtenberg in view of Rutledge and Cooper                                                                      |     |  |  |

|    | 2.                                                                           | Claims 2, 3 and 5-7 are Rendered Obvious by Rutledge in view of Ligtenberg and Cooper                                                         | 117 |  |  |

|    | 3.                                                                           | Claim 8 is Rendered Obvious by Rutledge in view of Ligtenberg and Cooper                                                                      | 121 |  |  |

|    | 4.                                                                           | Claims 9, 10 and 12-14 are Rendered Obvious by Rutledge in view of Ligtenberg and Cooper                                                      | 128 |  |  |

Page

# TABLE OF CONTENTS

(continued)

|     |     |            |                                                                                                                                              | Page |

|-----|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|

|     |     | 5.         | Claim 15 is Rendered Obvious by Rutledge in view of Ligtenberg and Cooper                                                                    | 130  |

|     |     | 6.         | Claims 16-17, 19-21 are rendered obvious by Rutledge i view of Ligtenberg and Cooper                                                         |      |

|     | C.  | UND<br>RUT | UND 3: CLAIMS 4, 11 AND 18 ARE UNPATENTABLE<br>ER 35 U.S.C. § 103(a) AS BEING OBVIOUS OVER<br>LEDGE IN VIEW OF LIGTENBERG, COOPER AND<br>SAN |      |

| XI. | OTH | ER PE      | RTINENT GROUNDS OF PRIOR ART                                                                                                                 | 138  |

|     | A.  | UND        | CHALLENGED CLAIMS ARE UNPATENTABLE<br>ER 35 U.S.C. § 103(a) AS BEING OBVIOUS OVER<br>LER IN VIEW OF HORNBACKER                               | 139  |

|     |     | 1.         | Claims 1-21 Are Rendered Obvious by Fuller and Hornbacker                                                                                    | 141  |

|     | В.  | UND        | CHALLENGED CLAIMS ARE UNPATENTABLE ER 35 U.S.C. § 103(a) AS BEING OBVIOUS OVER IN VIEW OF RABINOVICH                                         | 166  |

|     |     | 1.         | The 506 Patent Fails To Distinguish Over Yap                                                                                                 | 167  |

|     |     | 2.         | Claims 1 to 21 are Rendered Obvious by Yap and Rabinovich                                                                                    | 172  |

|     | C.  | UND        | CHALLENGED CLAIMS ARE UNPATENTABLE<br>ER 35 U.S.C. § 103(a) AS BEING OBVIOUS OVER<br>LER IN VIEW OF YAP                                      | 191  |

|     | D.  | UND        | CHALLENGED CLAIMS ARE UNPATENTABLE<br>ER 35 U.S.C. § 103(a) AS BEING OBVIOUS OVER<br>MESIL IN VIEW OF HORNBACKER AND COOPER                  | 192  |

# LIST OF APPENDICES

| Appendix A | Curriculum Vitae of William R. Michalson                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendix B | Excerpt of Hanan Samet, <i>The Design and Analysis of Spatial Data Structures</i> , University of Maryland (1989)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Appendix C | U.S. Patent No. 5,263,136 (DeAguiar et al)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Appendix D | U.S. Patent 4,972,319 (Delorme)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Appendix E | B. Fuller and I. Richer, <i>The MAGIC Project: From Vision to Reality</i> , IEEE Network May/June 1996, pp. 15-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Appendix F | International Telegraph and Telephone Consultative Committee ("CCITT") Recommendation T.81, September 1992                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Appendix G | Ken Cabeen & Peter Gent, Image Compression and the Discrete Cosine Transform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Appendix H | M. Antonini, <i>Image Coding Using Wavelet Transform</i> , IEEE Transactions on Image Processing, Vol. 1, No. 2, April 1992.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Appendix I | U.S. Patent No. 5,321,520 (Inga et al)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Appendix J | U.S. Patent No. 6,182,114 (Yap et al.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Appendix K | U.S. Patent No. 5,179,638 (Dawson et al)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Appendix L | Lance Williams, <i>Pyramidal Parametrics</i> , Computer Graphics, vol. 17, no. 3, July 1983                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Appendix M | OpenGL Standard Version 1.1, March 1997, available: <a href="https://www.opengl.org/documentation/specs/version1.1/glspec">https://www.opengl.org/documentation/specs/version1.1/glspec</a> |

Appendix R Boris Rabinovich & Craig Gotsman, Visualization of Large *Terrains in Resource-Limited Computing Environments* (1997) Appendix S *User Datagram Protocol (UDP) (Windows CE 5.0, Microsoft,* Available: https://msdn.microsoft.com/enus/library/ms885773.aspx [Accessed April 28, 2015] Appendix T OpenGL Standard Version 1.2.1, April 1999, available: https://www.opengl.org/documentation/specs/version1.2/opengl 1.2.1.pdf Appendix U Claim chart illustrating teachings of Potmesil (Ex. 1002) and Hornbacker (Ex. 1003) pertinent to elements of Challenged Claims Appendix V Claim chart illustrating teachings of Rutledge (Ex. 1006), Ligtenberg (Ex. 1005), and Cooper (Ex. 1007) pertinent to elements of Challenged Claims Appendix W Claim chart illustrating teachings of Rutledge (Ex. 1006), Ligtenberg (Ex. 1005), Cooper (Ex. 1007), and Hassan (Ex. 1008) pertinent to elements of Challenged Claims George H. Forman and John Zahorjan, "The challenges of Appendix X mobile computing," Computer vol. 27, no. 4, pp. 38, 47 (April 1994) Appendix Y K. Brown and S. Singh, A Network Architecture for Mobile Computing, INFOCOM '96, Fifteenth Annual Joint Conference of the IEEE Computer Societies, Networking the Next Generation, Proceedings IEEE vol. 3, pp. 1388-139 Appendix Z Kreller, B. et al "UMTS: a middleware architecture and mobile API approach," Personal Communications, IEEE, vol. 5, no. 2, pp. 32-38 (April 1998) Appendix AA Hansen, J. et al, "Real-time synthetic vision cockpit display for general aviation," AeroSense '99, International Society for Optics and Photonics, 1999 Appendix BB U.S. Patent No. 5,760,783 to Migdal et al ("Migdal")

Appendix CC Claim chart illustrating teachings of Fuller (App. E) and

Hornbacker (Ex. 1003) pertinent to elements of Challenged

Claims

Appendix DD Claim chart illustrating teachings of Yap (App. J) and

Rabinovich (App. R) pertinent to elements of Challenged

Claims

Appendix EE Theresa-Marie Rhyne, A Commentary on GeoVRML: A Tool

for 3D Representation of GeoReferenced Data on the Web,

International Journal of Geographic Information Sciences, issue

4 of volume 13, 1999

#### I. INTRODUCTION

- My name is William R. Michalson. I am a faculty member at 1. Worcester Polytechnic Institute. I have been engaged by Microsoft Corporation ("Microsoft") to investigate and opine on certain issues relating to U.S. Patent No. 8,924,506 B2 (the "506 Patent") entitled "System and methods for network image delivery with dynamic viewing frustum optimized for limited bandwidth communication channels" in Microsoft's Petition for *Inter Partes* Review of the 506 Patent ("Microsoft IPR Petition") which requests the Patent Trial and Appeal Board ("PTAB") to review and cancel all claims of the 506 Patent—claims 1-21 ("Challenged Claims"). I have also been engaged by Microsoft to investigate and opine on certain issues relating to two other patents that are related to the 506 Patent—U.S. Patent Nos. 7,908,343 B2 and 7,139,794 B2—in additional petitions for inter partes review by Microsoft. I understand that Bradium Technologies LLC ("Bradium") is asserting all three patents against Microsoft in an on-going patent infringement lawsuit, No. 1:15-cv-00031-RGA, filed in the U.S. District Court for the District of Delaware on January 9, 2015.

- 2. I understand that the 506 Patent was assigned from the inventors Isaac Levanon and Yoni Lavi to Inovo Limited on April 3, 2011, and assigned from Inovo Limited to Bradium on June 17, 2013. Bradium is therefore referred to as the "Patent Owner" in this declaration.

- 3. In this declaration, I will first discuss the technology background related to the 506 Patent and then provide my analyses and opinions on claims 1-21 of the 506 Patent. The discussion of the technology background includes an overview of that technology as it was known before October 1999, which I understand as the earliest invention date of the 506 Patent claimed by the inventors in their inventor declarations submitted to the USPTO during the original prosecution of the 506 Patent's grand-parent patent, U.S. Patent No. 7,644,131. This overview provides some of the bases for my opinions with respect to the 506 Patent.

- 4. This declaration is based on the information currently available to me. To the extent that additional information becomes available, I reserve the right to continue my investigation and study, which may include a review of documents and information that may be produced, as well as testimony from depositions that may not yet be taken.

- 5. In forming my opinions, I have relied on information and evidence identified in this declaration, including the 506 Patent, the prosecution history of the 506 Patent, and prior art references listed as Exhibits to the Microsoft IPR Petition and listed as appendices of this declaration.

#### II. SUMMARY OF OPINIONS

- 6. Claims 1-21 of the 506 Patent relate to system and method for dynamic visualization of image data transferred through a communications channel. For the reasons explained below, none of the features described in Claims 1-21 of the 506 Patent were novel as of October 1999, nor does the 506 Patent teach a novel and non-obvious way of combining these known features.

- 7. Claims 1-21 of the 506 Patent relate to well-known technologies in the computer industry such as multi-resolution hierarchical maps, image compression, packetized data transmission, and three-dimensional (3D) graphics rendering. No element of Claims 1-21 is novel, and Claims 1-21 do not bring these elements together in a way that brings any benefit beyond what a person of ordinary skill in art would expect from the known functions of the individual components. Claims 1-21 describe techniques that were well-known in the field, and combine them in ways that would have been readily apparent to a person of ordinary skill in the art with predictable results.

- 8. It is my opinion that each of Claims 1-21 is invalid under the patentability standard of 35 U.S.C. § 103 as I understand it and as explained to me by Microsoft's counsel. Within this declaration I discuss specific grounds of invalidity of Claims 1-21; however, my opinion that Claims 1-21 are invalid under 35 U.S.C. § 103 is not limited to these specific grounds, and indeed, it is my

opinion that Claims 1-21 would have been invalid in light of the general knowledge of a person of ordinary skill in the art at the time of the alleged invention.

- 9. For purposes of my analyses in this declaration only, I provide my proposed construction of certain terms in Claims 1-21 in detail in a later part of this declaration.

- 10. The subsequent sections of this declaration will first provide my qualifications and experience and then describe details of my analyses and observations.

## III. QUALIFICATIONS AND EXPERIENCE

# A. Education and Work Experience

- 11. I received a Ph.D. degree in Electrical Engineering in 1989 and a Master of Science degree in Electrical Engineering in 1985 from the Worcester Polytechnic Institute. I received a Bachelor of Science degree in Electrical Engineering from Syracuse University in 1981.

- 12. I have more than twenty years of experience in the fields of electrical engineering, computer systems, navigation systems, and communications systems. My experience includes the design, implementation and use of geographic information systems ("GIS"), as well as the design, implementation and use of navigation systems relying on GPS and other positioning system technologies. I

also have extensive experience in computer communication and data processing systems as well as systems for the efficient transmission of digital images and other data. Additionally, I have experience in the design and implementation of hardware and software systems used to render image data for display.

- 13. I have published 16 papers in technical journals and 97 papers in technical conferences. I hold eight U.S. patents in the fields of handheld GPS (Global Positioning System), portable geolocation devices, and communication networks. I have also authored one book chapter relating to optical interconnect networks for massively parallel computers. I became a Senior Member of the Institute of Electrical and Electronics Engineers (IEEE) in 2003.

- 14. My experience spans from product designs and R&D in industry, teaching, research and development in an educational and research institution to technology consulting to industry. I was an engineer at Raytheon Company for ten years from 1981 to 1991. During this period, I worked on projects related to computer display hardware for various applications, including air traffic control applications.

- 15. After leaving Raytheon Company, I joined the Worcester Polytechnic Institute and became a full-time faculty member there in 1991. My research at WPI focuses on navigation systems and related technologies. I am the director of WPI's Center for Advanced Integrated Radio Navigation.

- 16. My research projects at WPI cover various technologies and include (1) a system using tracking and communications technologies to track shipping containers, (2) an automotive based system that combined GPS and map data in an automotive environment, (3) a remote hazard detection system using GPS and radio communications, and (4) a differential GPS system that combined GPS and radio technologies to determine the precise path of vehicles operating off-road during forest operations.

- 17. I have worked as a consultant in the navigation and communication systems fields, e.g., in the context of space shuttle docking operations, transfer of traffic information to GPS devices, combinations of GPS and cellular communications for tracking purposes, and map-based handheld tracking devices.

- 18. I am familiar with numerous GIS and mapping products that existed in the market since the late 1980s, including systems and software developed by Etak, Microsoft, DeLorme, and others. In the conduct of my research and other work, I have routinely used commercially available GIS and mapping products and have developed mapping and visualization software for specialized applications. Additionally, I have used and incorporated database systems such as Microsoft Access, Borland Paradox, Oracle, SQL and others in my research and have incorporated database systems into other hardware and software systems for use in storing and retrieving GIS-related data.

- 19. I have done extensive research work in communications and networking system design, and have worked with all of the digital, analog and software components needed to build communications and navigation systems. My work with communications and networking protocols began in the mid-1980s with TCP/IP over packet radio. I have used these and other communications and networking protocols extensively in conducting my research. In addition, my work on GPS and navigation systems involved implementing low-latency communications to support differential techniques that allow a GPS receiver to provide more accurate positioning information.

- 20. I have extensive experience with the development and maintenance of server computers, including the installation and maintenance of web servers and file servers, as well as the design, development, test, and maintenance of web based applications. These applications typically employ C/C++, Java, JavaScript, PHP, HTML, MySQL, and etc. I am also experienced with server-client systems where the client computer exchanges navigation and/or geographical information with server computer through a wired and/or wireless network.

- 21. My curriculum vitae, which provides a detailed summary of my education, work experience, publication, teaching history, and etc. is attached to this declaration as Appendix A.

## **B.** Compensation

22. I am being compensated for the services I am providing in this and other Microsoft IPR petitions. The compensation is not contingent upon my performance, the outcome of this *inter partes* review or any other proceedings, or any issues involved in or related to this *inter partes* review or any other proceedings.

# C. Documents and Other Materials Relied Upon

23. The documents on which I rely for the opinions expressed in this declaration are documents and materials identified in this declaration, including the 506 Patent, patents related to the 506 Patent, the prosecution history for the 506 Patent and other patents related to the 506 Patent, the prior art references and information discussed in this declaration, including the references attached as exhibits of the IPR Petition for the 506 Patent: Maps Alive: Viewing Geospatial Information on the WWW, Michael Potmesil, Computer Networks and ISDN Systems Vol. 29, issues 8-13, pp. 1327-1342 ("Potmesil") (Ex. 1002), WO 99/41675 to Cecil V. Hornbacker, III ("Hornbacker") (Ex. 1003), An Integrated Global GIS and Visual Simulation System by P. Lindstrom et al., Tech. Rep. GIT-GVU-97-07, March 1997 ("Lindstrom") (Ex. 1004), U.S. Pat. No. 6,650,998 to Charles Wayne Rutledge et al ("Rutledge") (Ex. 1006), U.S. Pat. No. 5,682,441 to Adrianus Ligtenberg et al ("Ligtenberg") (Ex. 1005), U.S. Pat. No. 6,118,456 to

David G. Cooper ("Cooper") (Ex. 1007), and U.S. Pat. No. 5,940,117 to Amer Hassan et al ("Hassan")(Ex. 1008) and any other references specifically identified in this declaration, in their entirety, even if only portions of these documents are discussed here in an exemplary fashion.

#### IV. STATEMENT OF LEGAL PRINCIPLES

#### A. Claim Construction

24. Microsoft's counsel has advised that, when construing claim terms of an unexpired patent, a claim subject to *inter partes* review receives the "broadest reasonable interpretation in light of the specification of the patent in which it appears."

# **B.** Anticipation

25. Microsoft's counsel has advised that in order for a patent claim to be valid, the claimed invention must be novel. Microsoft's counsel has further advised that if each and every element of a claim is disclosed in a single prior art reference, then the claimed invention is anticipated, and the invention is not patentable according to pre-AIA 35 U.S.C. § 102 effective before March 16, 2013. In order for an invention in a claim to be anticipated, all of the elements and limitations of the claim must be shown in a single prior reference, arranged as in the claim. A claim is anticipated only if each and every element as set forth in the claim is found, either expressly or inherently described, in a single prior art

reference. In order for a reference to inherently disclose a claim limitation, that claim limitation must necessarily be present in the reference.

#### C. Obviousness

AIA 35 U.S.C. § 103 effective before March 16, 2013 is a basis for invalidity. I understand that where a prior art reference does not disclose all of the limitations of a given patent claim, that patent claim is invalid if the differences between the claimed subject matter and the prior art reference are such that the claimed subject matter as a whole would have been obvious at the time the invention was made to a person having ordinary skill in the relevant art. Obviousness can be based on a single prior art reference or a combination of references that either expressly or inherently disclose all limitations of the claimed invention. In an obviousness analysis, it is not necessary to find precise teachings in the prior art directed to the specific subject matter claimed because inferences and creative steps that a person of ordinary skill in the art would employ can be taken into account.

#### V. LEVEL OF ORDINARY SKILL IN THE ART

27. I understand from Microsoft's counsel that the claims and specification of a patent must be read and construed through the eyes of a person of ordinary skill in the art at the time of the priority date of the claims. I have also been advised that to determine the appropriate level of a person having ordinary

skill in the art, the following factors may be considered: (a) the types of problems encountered by those working in the field and prior art solutions thereto; (b) the sophistication of the technology in question, and the rapidity with which innovations occur in the field; (c) the educational level of active workers in the field; and (d) the educational level of the inventor.

- 28. The "Background" section of the 506 Patent describes a "well recognized problem" of how to reduce the latency for transmitting full resolution images over the Internet on an "as needed" basis, particularly for "complex images" such as "geographic, topographic, and other highly detailed maps." Ex. 1001 at 1:29-46.

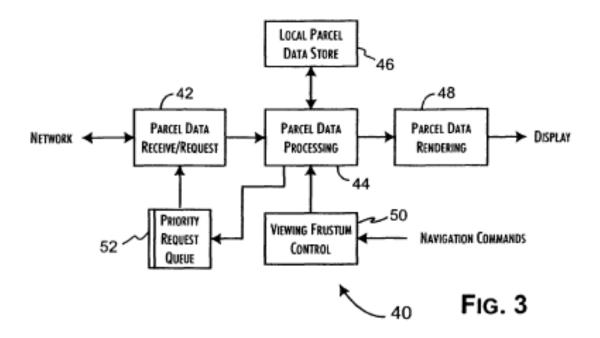

- 29. To solve this problem and to address some perceived issues in the existing art, the 506 Patent discloses a system capable of "optimally presenting image data on client systems with potentially limited processing performance, resources, and communications bandwidth." *Id.* at 3:46-49. The 506 Patent states that the disclosed technology can achieve faster image transfer by (1) dividing the source image into parcels/tiles, (2) processing the parcels/tiles into a series of progressively lower resolution parcels/tiles, and (3) requesting and transmitting the parcels/tiles needed for a particular viewpoint in a priority order, generally lower-resolution tiles first.

- 30. In light of the disclosed technology of the 506 Patent, a person of ordinary skill in the art for the 506 Patent would need education or work experience in computer network communications. Because a "common application" of the 506 Patent is to transmit "geographic, topographic, and other highly detailed maps," (*id.* at 1:41-43), a person of ordinary skill in the art would require some knowledge and experience with geographic information systems ("GIS").

- 31. Based on the above considerations and factors, it is my opinion that a person having ordinary skill in the art should have a Master of Science or equivalent degree in electrical engineering or computer science, or alternatively a Bachelor of Science or equivalent degree in electrical engineering or computer science, with at least 5 years of experience in a technical field related to geographic information system ("GIS") or the transmission of image data over a computer network. This description is approximate and additional educational experience could make up for less work experience and vice versa.

#### VI. TECHNOLOGY BACKGROUND OF THE 506 PATENT

32. It is my opinion that the 506 Patent recites an obvious and predictable combination of elements that were well-known in the art at the time the 506 Patent was filed and at the time of alleged invention. In this section of my declaration, I provide an overview of some general principles that were understood in the art at

the time of filing of the 506 Patent, and therefore would be within the knowledge of a person of ordinary skill in the art. I use certain references (including both patents and non-patent literature) to illustrate the background knowledge of a person of ordinary skill in the art, but the knowledge of a person of ordinary skill in the art at the time regarding the claimed features would not have been limited to these specific references.

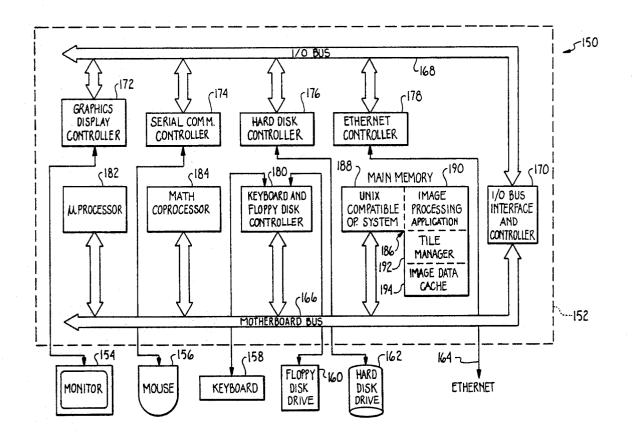

#### A. Data Communications Over the Internet

33. The predominant computer networking technology and set of communications protocols used for most online communications today and prior to the filing of the application for the 506 Patent is known as the Internet Protocol (IP) suite called TCP/IP, after its two main component protocols: the Transmission Control Protocol and the Internet Protocol. The 506 Patent teaches at 8:12-32 that its preferred embodiment uses TCP/IP to send data packets. In this declaration I do not provide a detailed description of all characteristics of the very well-known TCP/IP protocols, but focus on a few specific aspects of TCP/IP that are pertinent to the claims at issue in the 506 Patent. TCP/IP transmits data between computers in a network using data packets, which are formatted units of data carried by the network as suitably sized blocks. Packets are composed of a header and a payload. The "payload" is the information which the packet is actually intended to convey. The header refers to supplemental data placed at the beginning of a block, and

contains information in a standard format such as the sender's and recipient's Internet Protocol addresses, a sequence number indicating where in a sequence of packets being transmitted the packet falls, an offset (how far into the data the payload begins) and the protocol governing the format of the payload. The addresses are used to route the packet to its destination, although unlike a circuitswitched connection, different packets going between the same sender and recipient at the same time may take different routes over the network. A rough analogy for data packets is that the header is the "envelope" which contains the address used to deliver the packet, while the payload is the contents of the envelope. The destination computer uses information in the header to place the data packet in its proper place in order, from which the original data contained in multiple packets can be reassembled. When data segments arrive in the wrong order TCP/IP buffers the out-of-order data until all data can be properly re-ordered and delivered to the application.

34. Before data is transmitted using TCP/IP, the sender and the destination exchange a short series of messages confirming a connection. The connection in this case simply means that the sender and the destination exchange messages to confirm that they are able to exchange messages via the network. When the destination computer receives a packet, it sends a short confirmation message to the sender that the packet has been received. If the confirmation is not

received within a certain time period, the sender re-sends the packet. This method avoids losing data in transmission if the transmission of a single packet fails.

35. A common consideration in building online systems is how large to make the data packets. Among other trade-offs, smaller packets may be more likely to reach their destination without loss or error; however, because the header size is similar for a large packet and a small packet, the amount of bandwidth taken up by header overhead increases with the use of smaller packets. In some cases, the network protocol sets a maximum packet length.

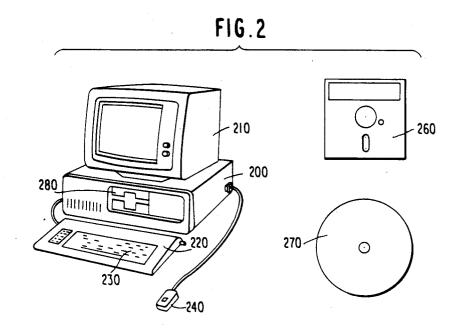

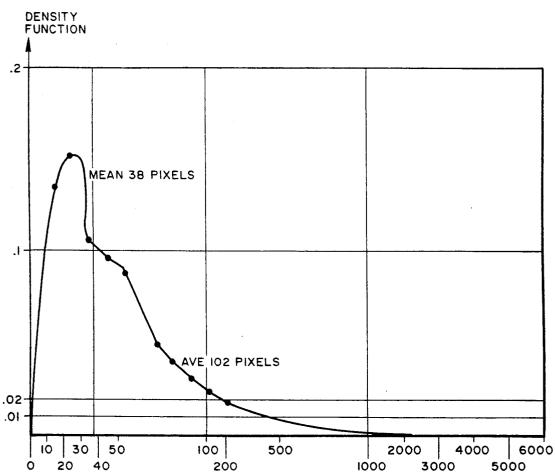

## **B.** Data Communications in Wireless Mobile Systems

- 36. By the late 1990s, it was well-known in the art that digital data could be transmitted by TCP/IP over wireless networks. For example, Appendix X, "The challenges of mobile computing," Computer vol. 27, no. 4, pp. 38, 47 (April 1994) provides an overview of methods for implementing internet connections on mobile devices as of 1994, noting that while wireless networks typically deliver lower bandwidth than wired networks, cellular telephone products of the time could already achieve transmission rates of 9-10 kilobits per second.

- 37. In another example in 1996, K. Brown and S. Singh, *A Network*Architecture for Mobile Computing, INFOCOM '96, Fifteenth Annual Joint

Conference of the IEEE Computer Societies, Networking the Next Generation,

Proceedings IEEE vol. 3, pp. 1388-1397 (Appendix Y) describes technologies that

Internet. This integration was described by using mobile data protocols to interact and be compatible with the TCP/IP structure of the Internet. This paper described how the Universal Mobile Telecommunications System (UMTS) under development in Europe was expected to offer average mobile data rates of between 1-2 megabytes per second (Mbps) per mobile user. Among other features, "Mobile users will be able to access their data and other services such as... map services." App. Y at 2.

38. Appendix Z, Kreller, B. et al "UMTS: a middleware architecture and mobile API approach," Personal Communications, IEEE, vol. 5, no. 2, pp. 32-38 (April 1998) describes the development of third-generation (3G) mobile networks offering "high-bit-rate data services, guaranteed on-demand bandwidth, and low delays." *Id.* at 32. To illustrate the development of frameworks to connect mobile telephone networks with existing fixed networks, the authors use the example of a mapping service called "City Guide," which allows a mobile device to request and download map imagery and other data from a server via hypertext transfer protocol (HTTP) to "provide access to maps describing the current surroundings." *Id.* at 33. The CityGuide could use JPEG compression and decompression, and could achieve bandwidth of up to 9.6 kbps using the then-existing Global System for Mobile Communications (GSM) cellular data standard. *Id.* at 36, 37.

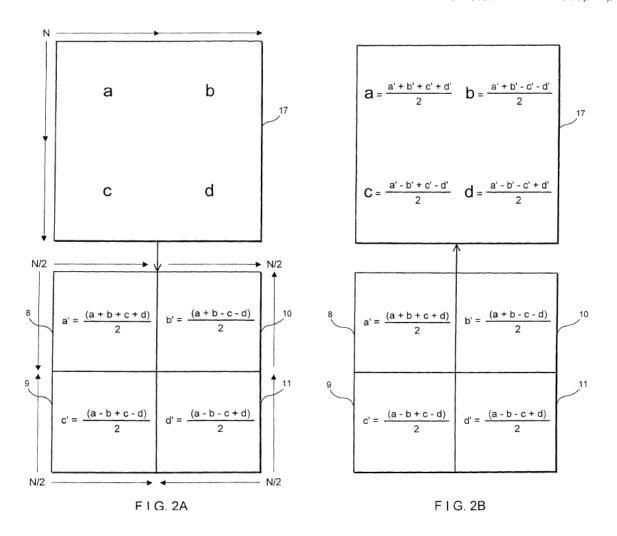

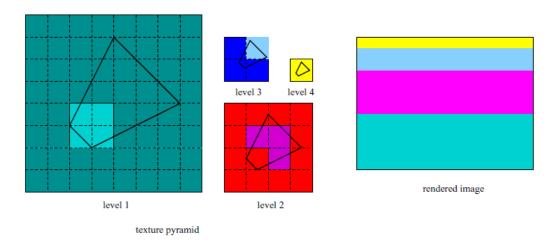

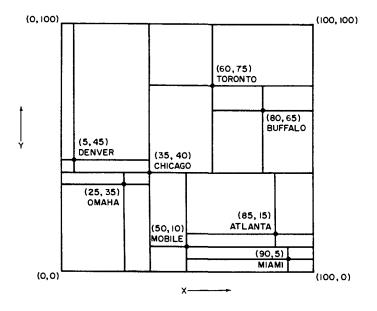

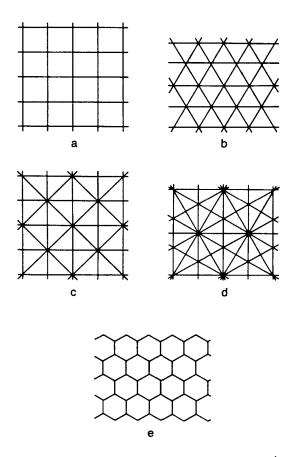

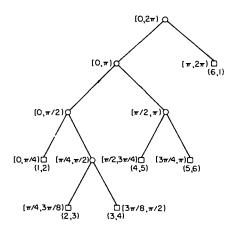

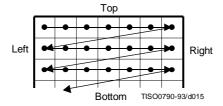

# C. Image Tiles and Image Pyramids

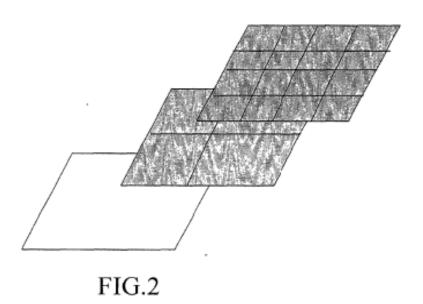

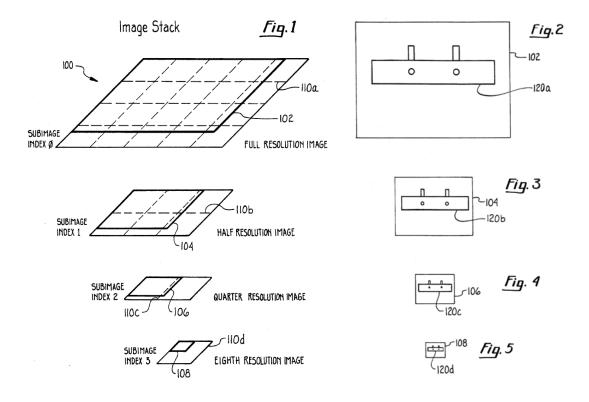

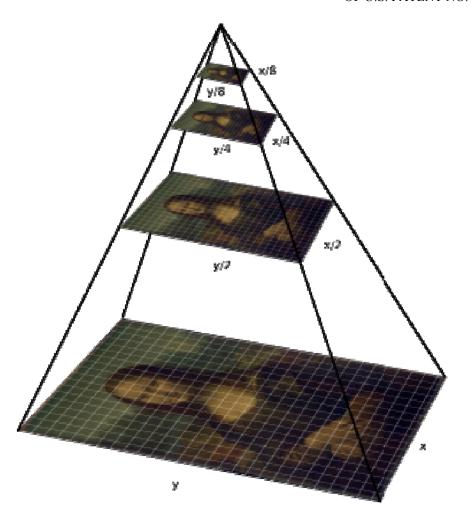

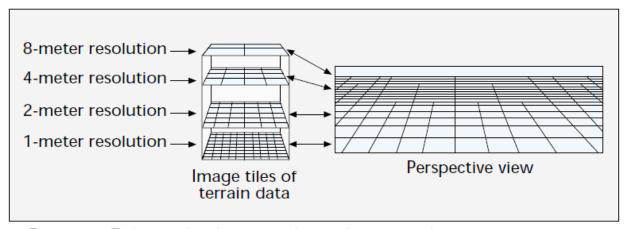

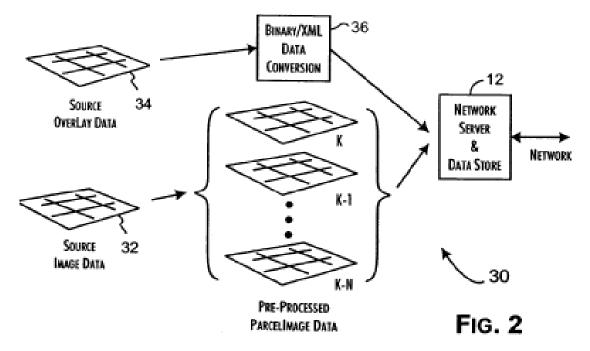

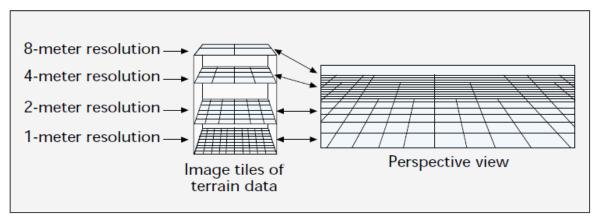

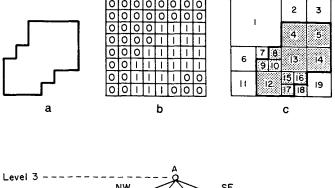

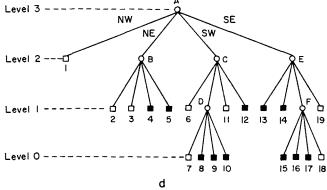

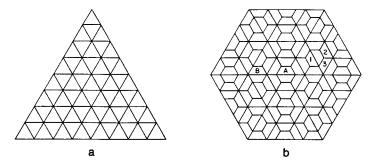

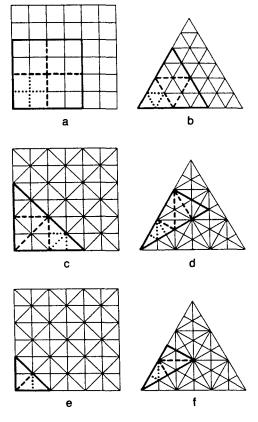

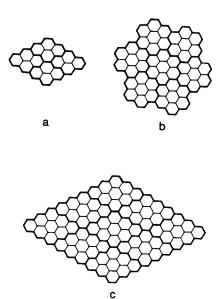

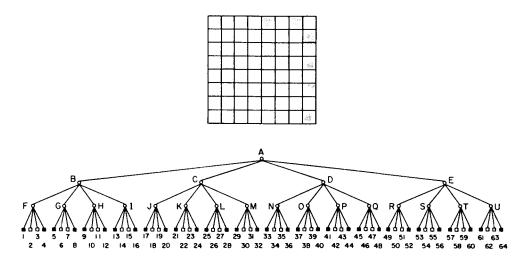

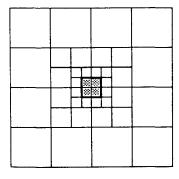

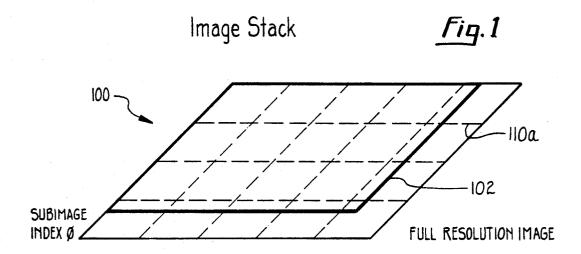

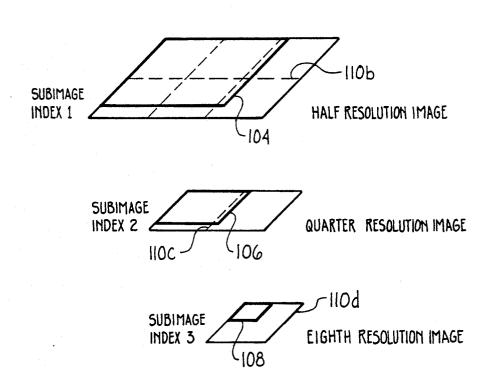

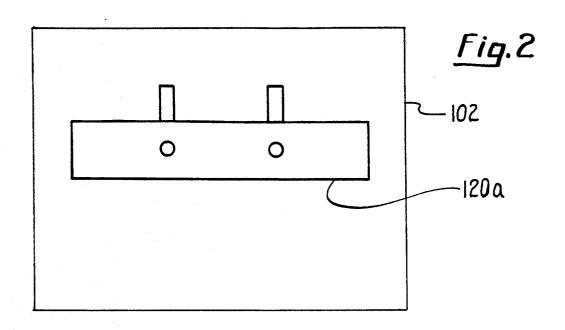

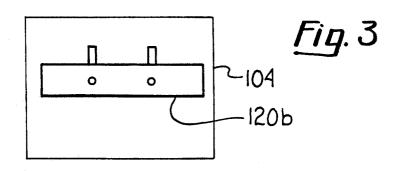

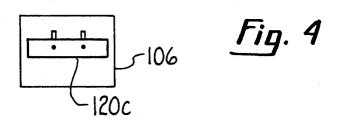

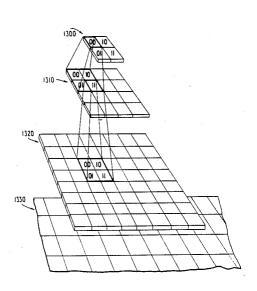

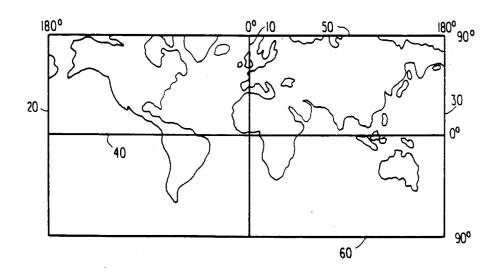

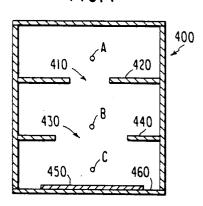

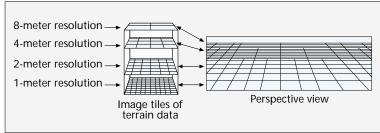

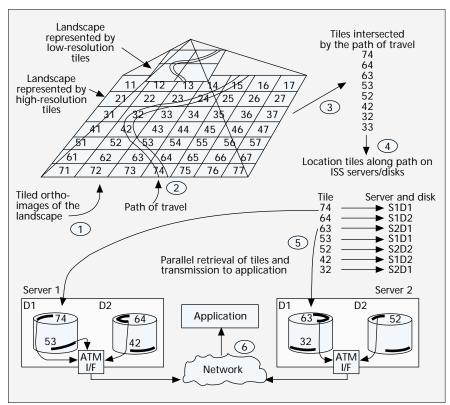

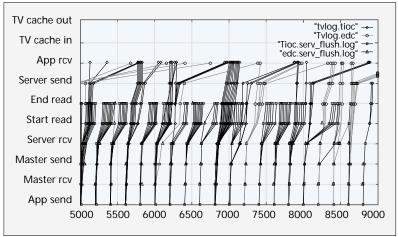

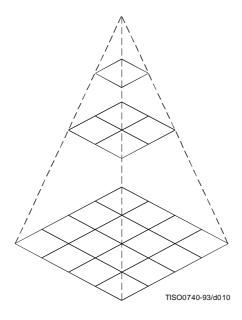

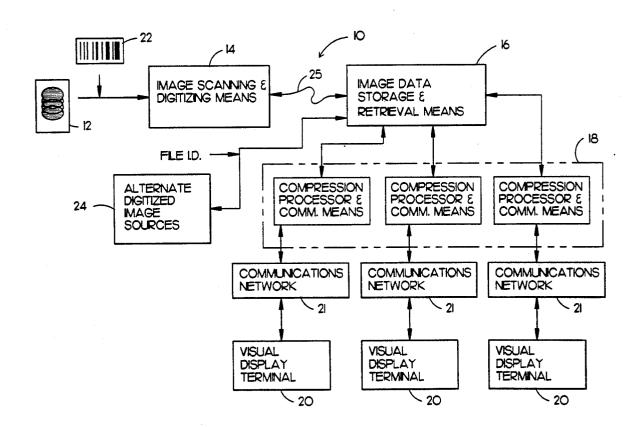

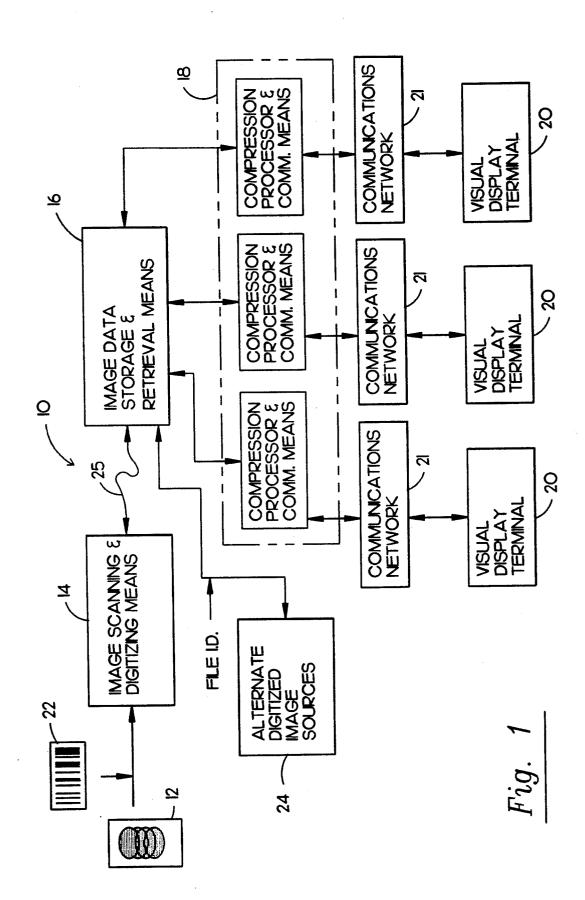

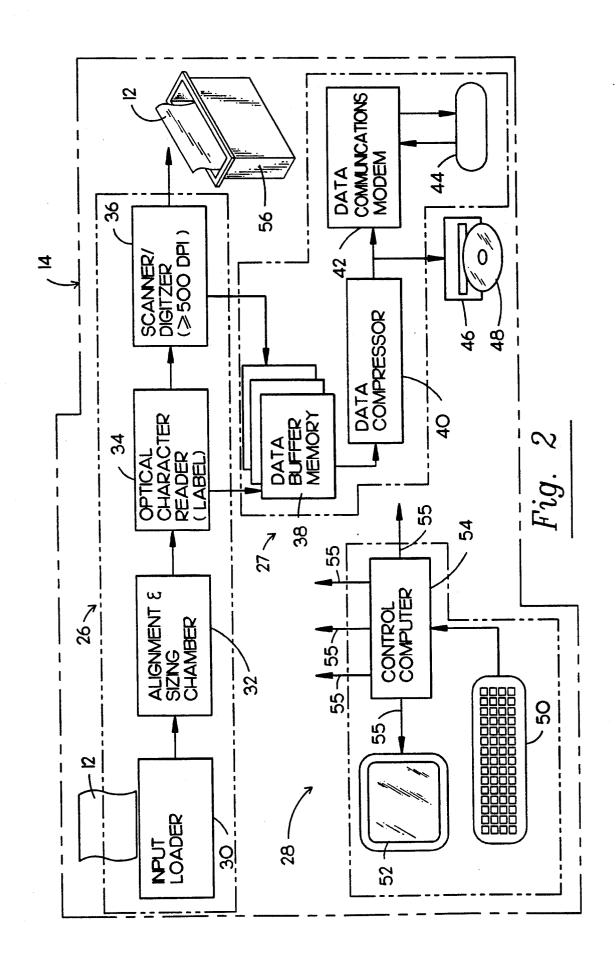

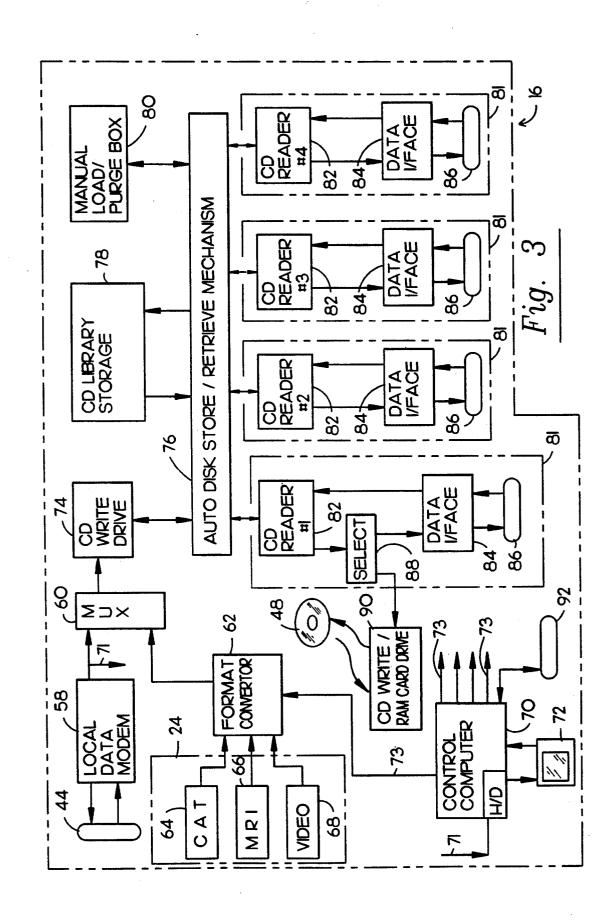

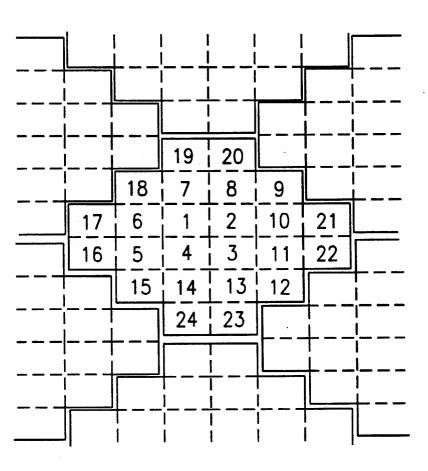

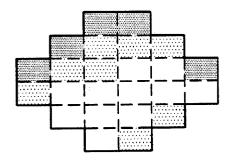

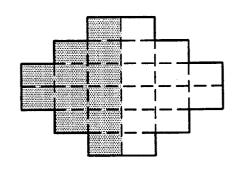

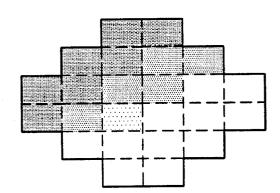

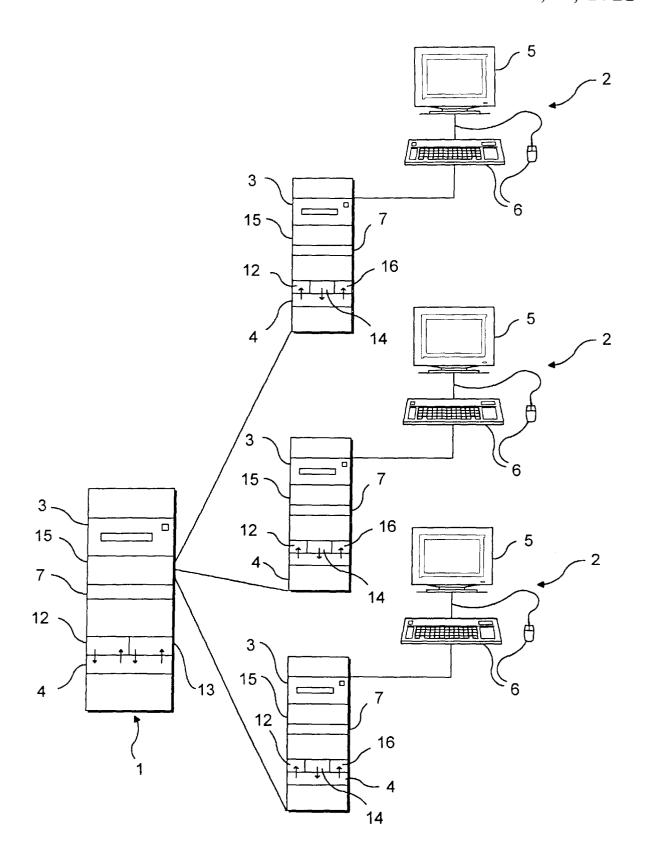

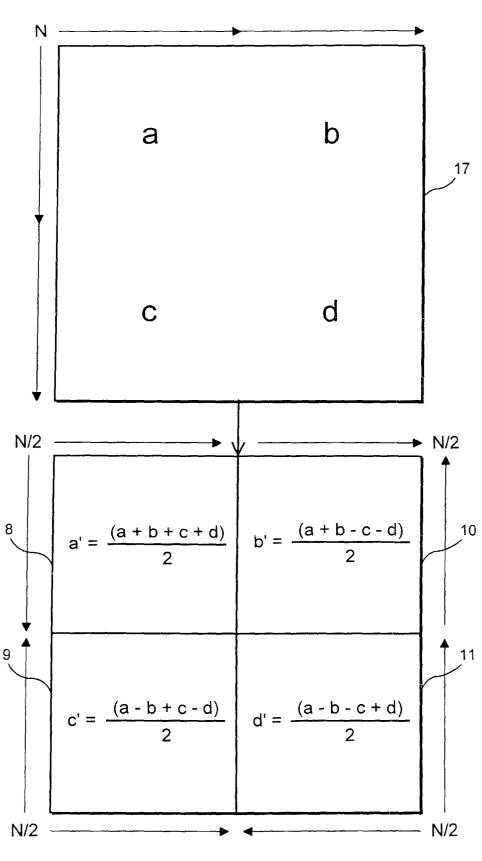

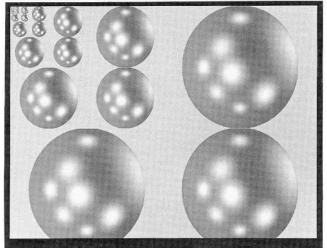

39. The 506 Patent describes sub-dividing a high resolution source image into a regular array of image parcels (a.k.a. image tiles), and pre-processing the image into a series of derivative images of progressively lower resolutions. Ex. 1001 at 6:7-22; Fig. 2. Preferably, the resolution decreases by a factor of four for each derivative image in the series. *Id.* at 6:17-20. Fig. 2 of the six provisional applications to which the 506 Patent claims priority (which is identical in all six provisional applications) best illustrates this image tiling and image pyramid scheme. Ex. 1010 at Fig. 2.

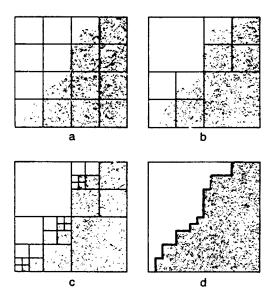

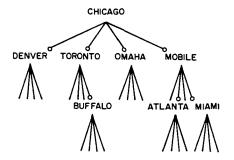

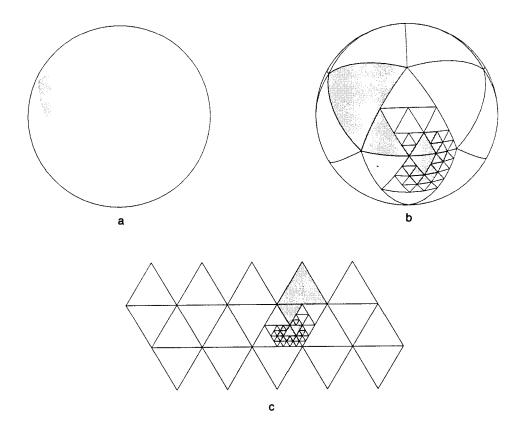

40. This image processing scheme, however, had been developed and widely used long before the 506 Patent's priority date. For example, Hanan Samet's book *The Design and Analysis of Spatial Data Structures* discloses

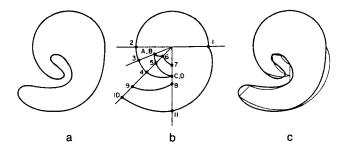

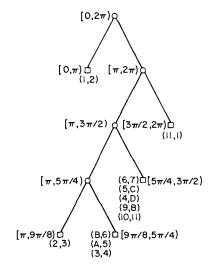

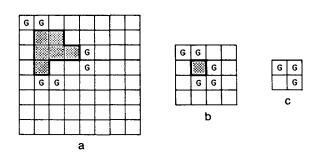

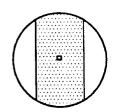

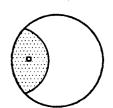

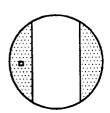

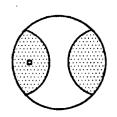

generating an image "pyramid" from a 2<sup>n</sup>x2<sup>n</sup> image array, where the pyramid is "a sequence of arrays {A(i)} such that A(i-1) is a version of A(i) at half the scale of A(i)." App. B, Hanan Samet, *The Design and Analysis of Spatial Data Structures* at 12 (1989, Reprinted with corrections in January, 1994). Fig. 1.7 in the Samet book is virtually the same as Fig. 2 of the 506 Patent's provisional application.

Figure 1.7 Structure of a pyramid having three levels

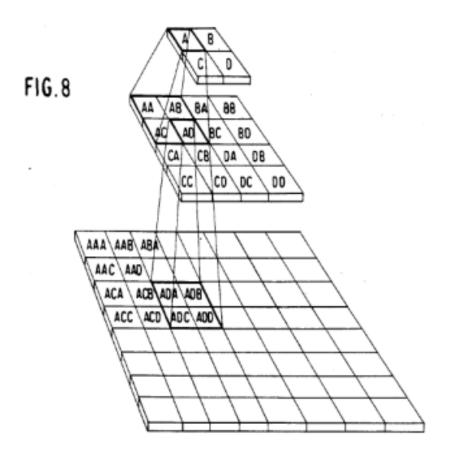

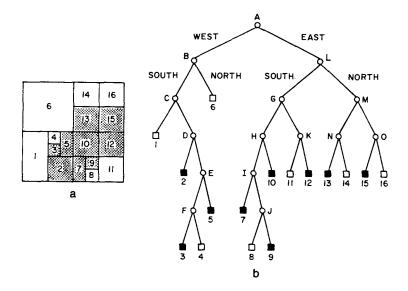

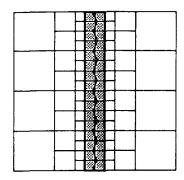

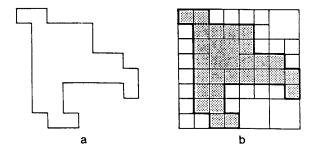

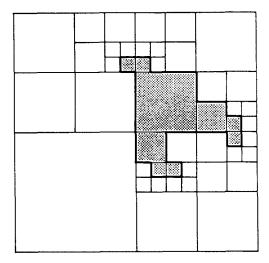

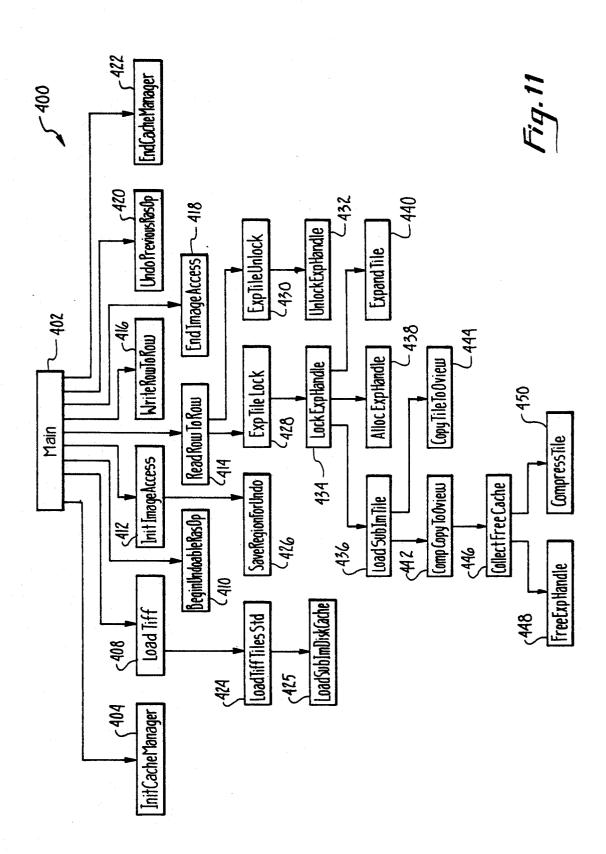

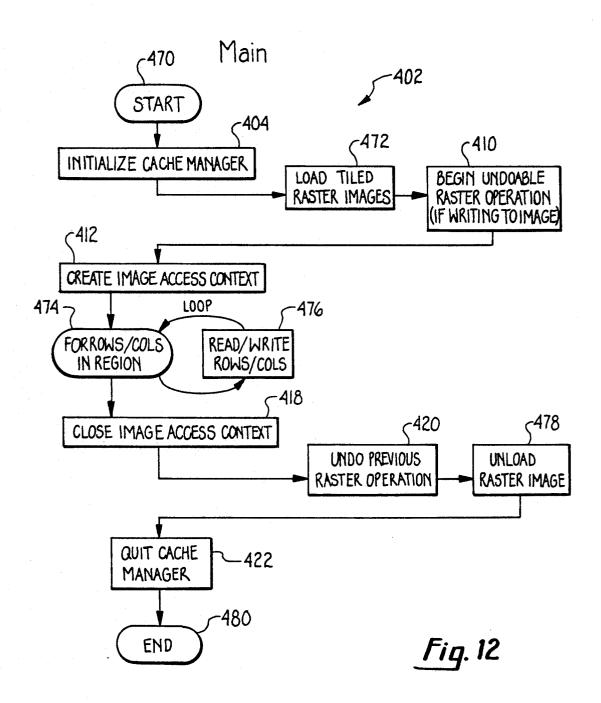

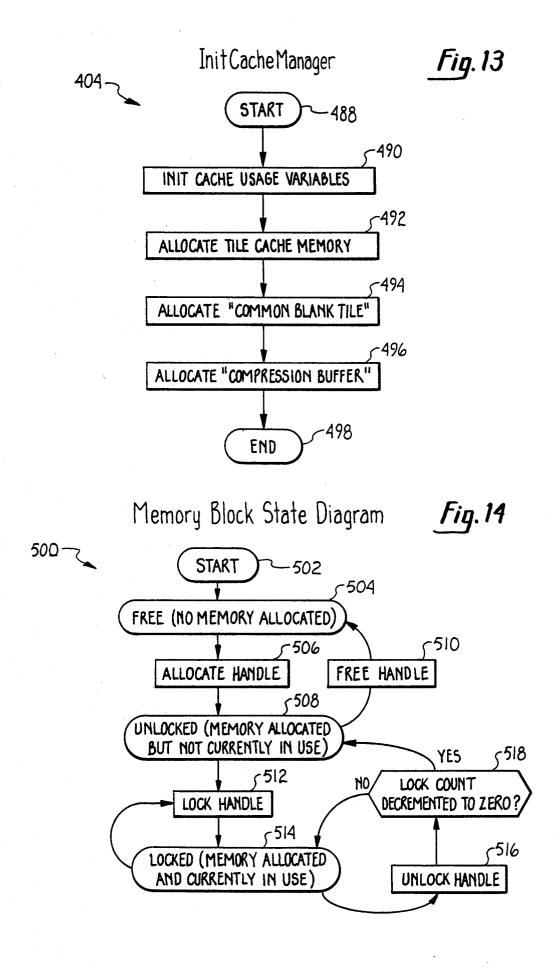

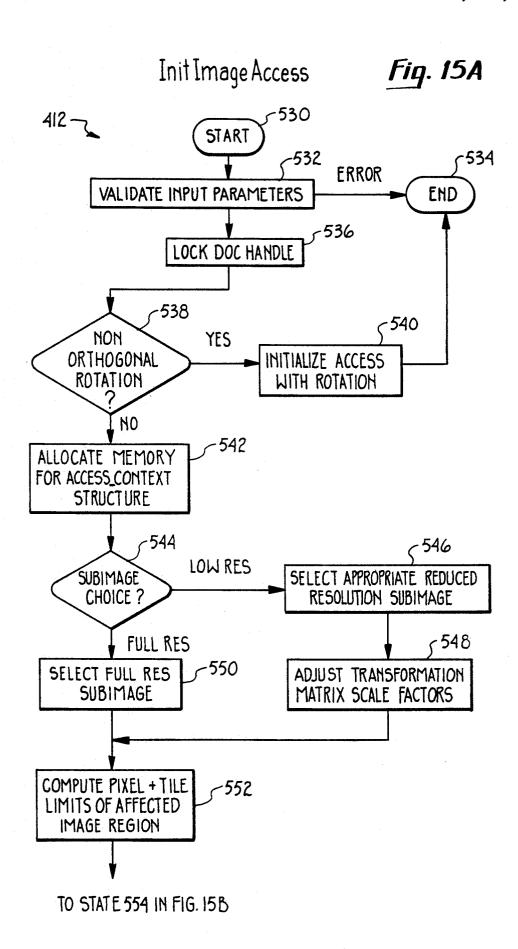

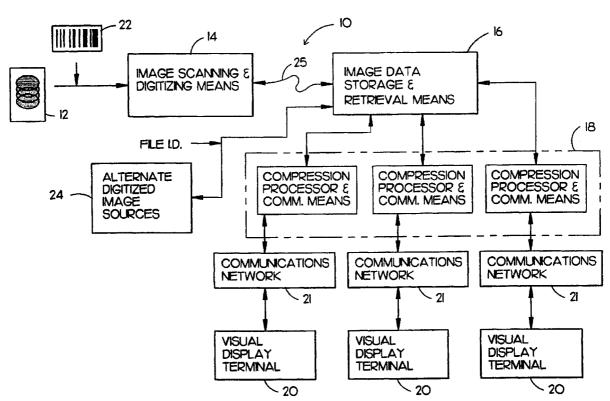

41. In another example, U.S. Patent No. 5,263,136 (DeAguiar et al) filed on April 30, 1991 and issued on November 16, 1993, entitled *System for Managing Tile Images using Multiple Resolutions*, discloses an "image memory management system for tiled images," where "each source image is stored as a full resolution image and a set of lower-resolution subimages." App. C at Abstract; Figs. 1 and 2. Suitable applications of the DeAguiar patent's image tiling and image pyramid scheme include "electrical schematics, topographical maps, satellite images, heating/ventilating/air conditioning (HVAC) drawings, and the like." *Id.* at col. 6:65-7:2.

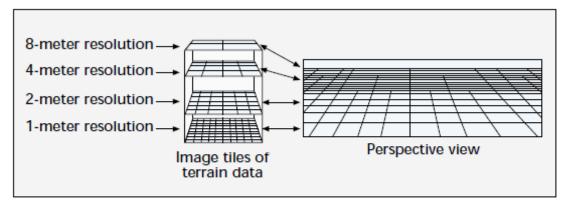

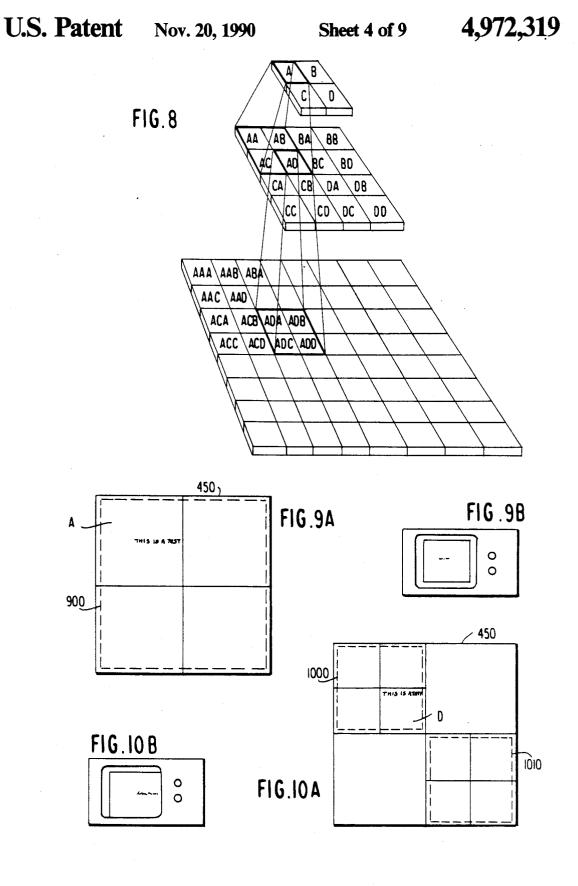

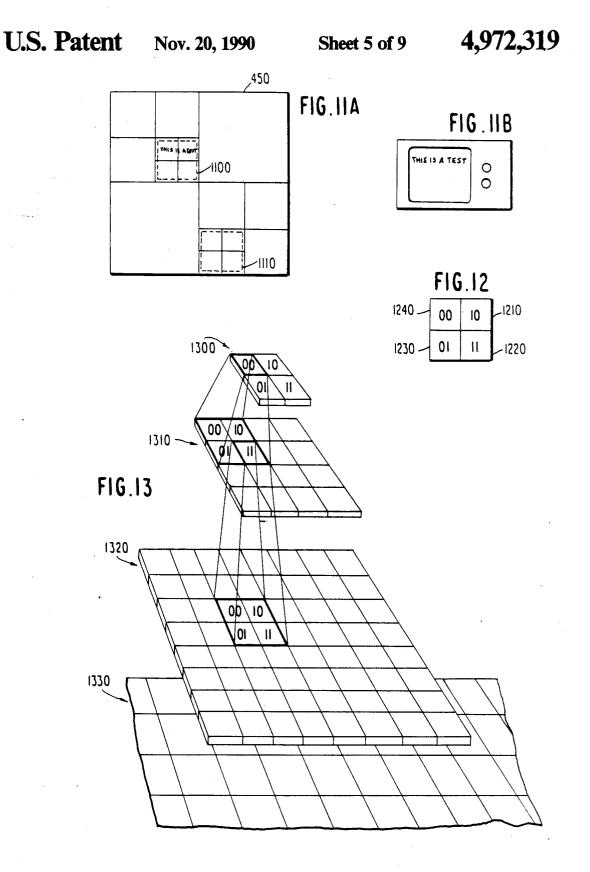

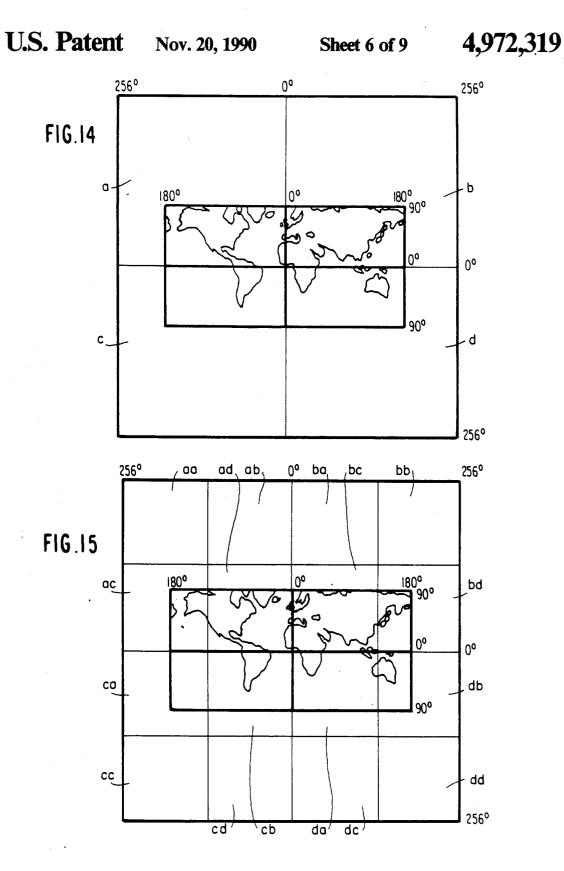

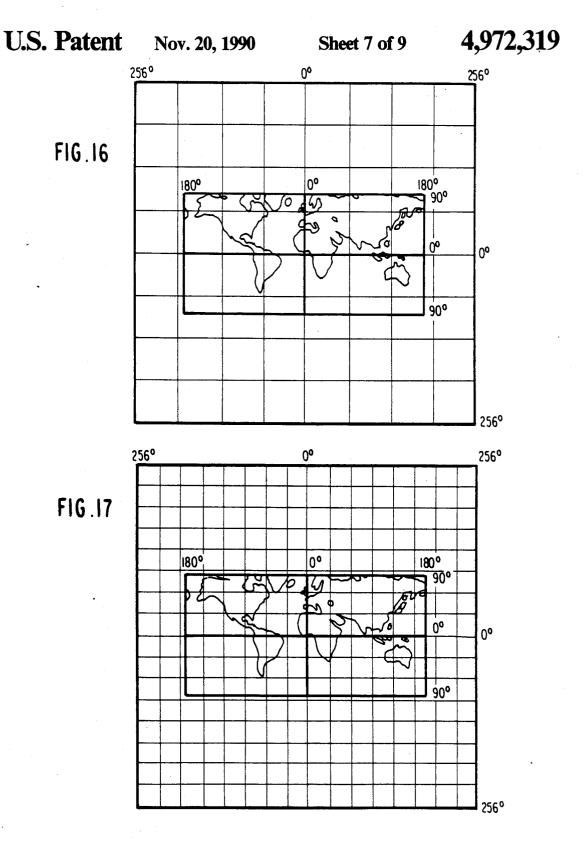

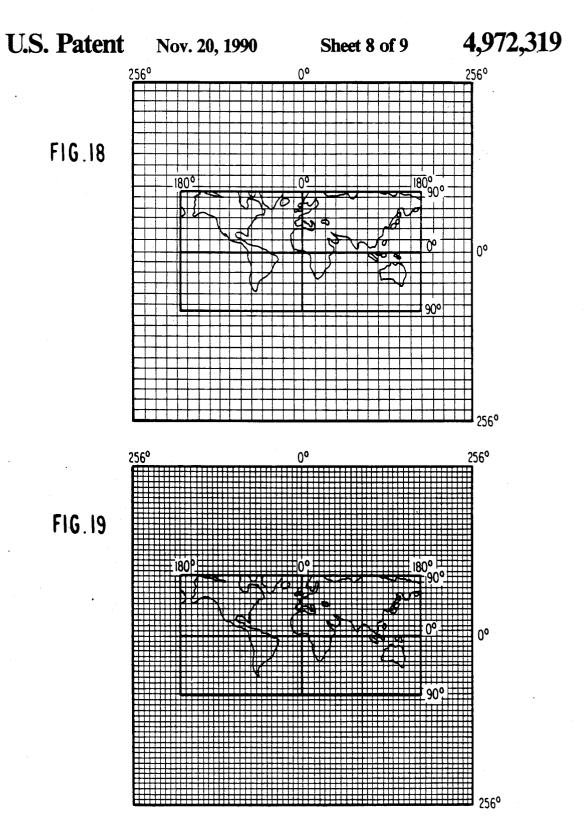

42. U.S. Patent 4,972,319 to Delorme, filed on Sept. 25, 1987 and issued on Nov. 20, 1990, also showed that image tiling and image pyramid can be used in mapping applications. Specifically, the Delorme patent discloses a "global mapping system which organizes mapping data into a hierarchy of successive magnitudes or levels for presentation of the mapping data with variable resolution, starting from a first or highest magnitude with lowest resolution and progressing to a last or lowest magnitude with highest resolution." App. D at Abstract. A pyramid of successively lower resolution image tiles is shown in Fig. 8 of the Delorme 319 patent. *Id.* at Fig. 8.

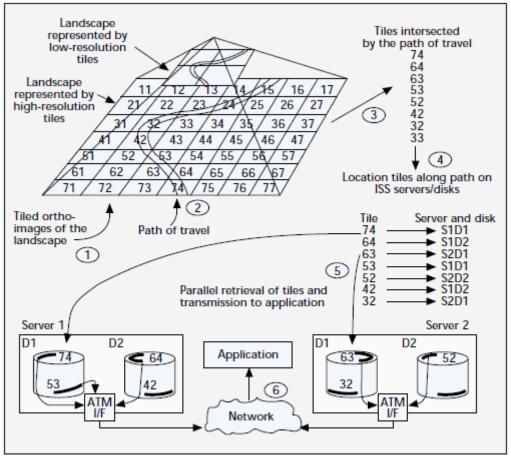

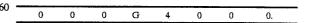

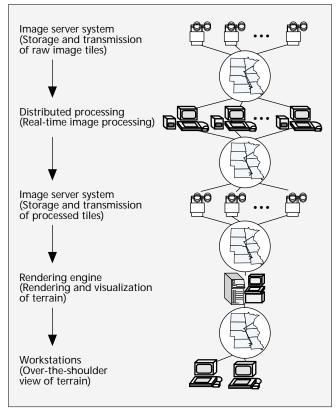

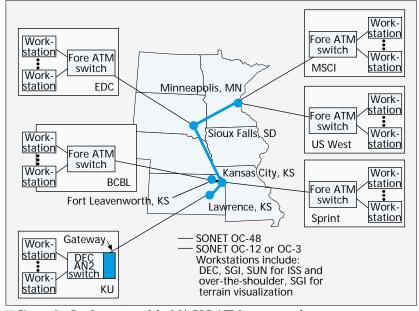

43. In yet another example, a 1996 article entitled "The MAGIC Project: From Vision to Reality" by Barbara Fuller and Ira Richer ("Fuller") also shows the image tiling and image pyramid scheme for mapping applications. App. E at Fig. 3.

■ Figure 3. Relationship between tile resolutions and perspective view. (Source: SRI International)

# **D.** Compression of Image Tiles

- 44. The 506 Patent discusses that the image tiles can preferably be compressed, e.g., for a fixed compression ratio of 4:1. Ex. 1001 at 6:23-28. Numerous methods existed, however, long before the 506 Patent's priority date, to compress images for either a variable or fixed ratio.

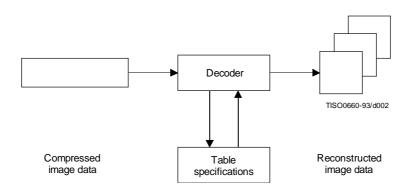

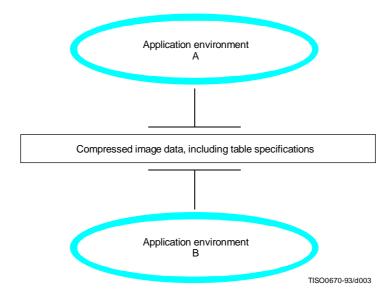

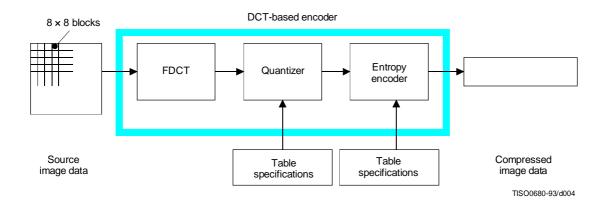

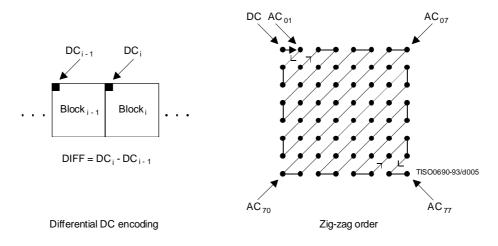

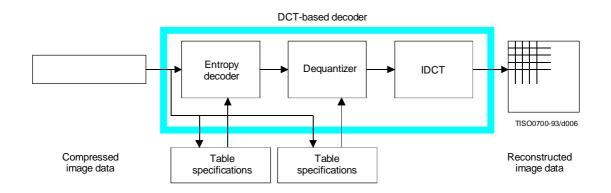

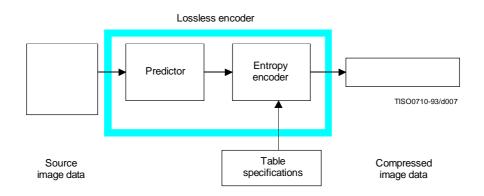

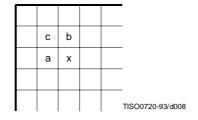

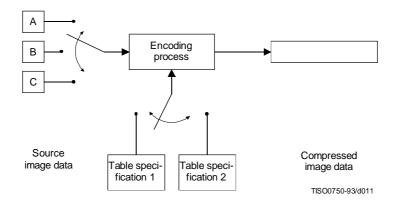

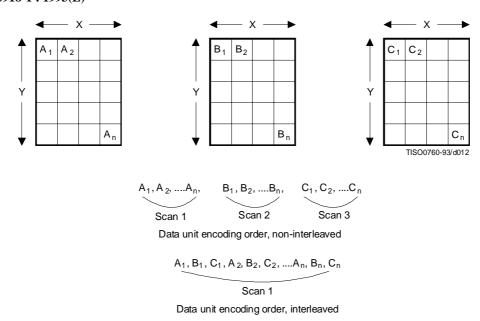

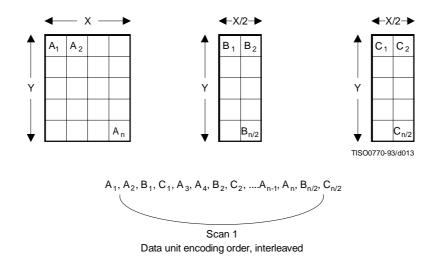

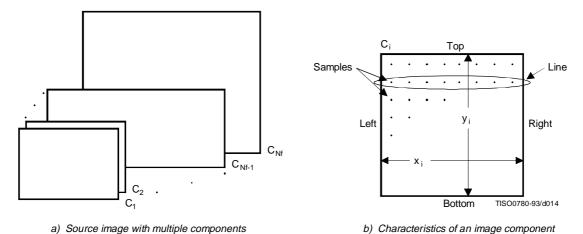

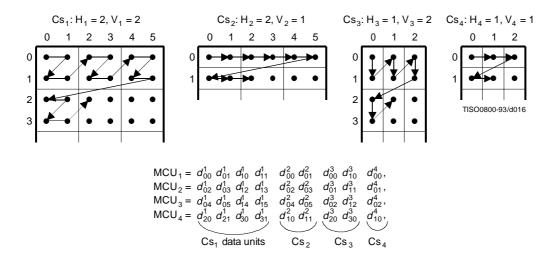

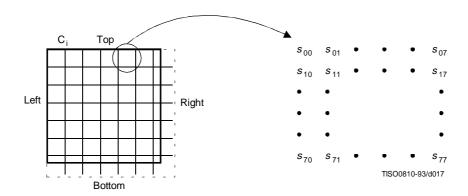

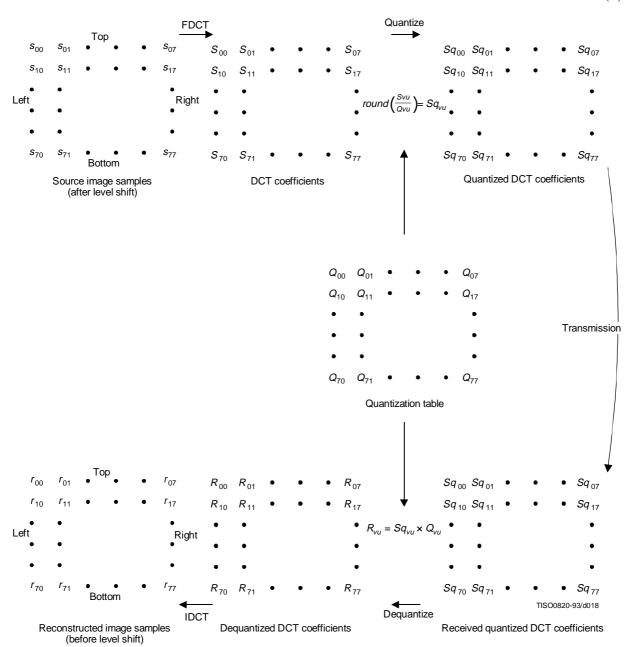

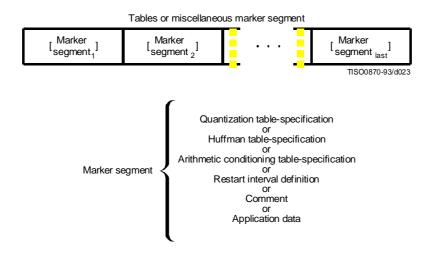

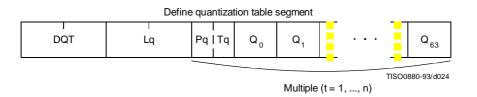

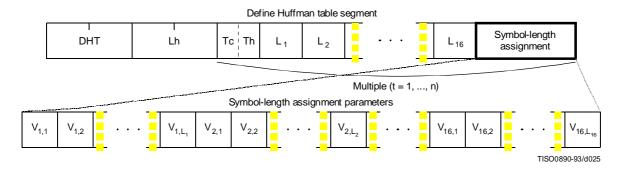

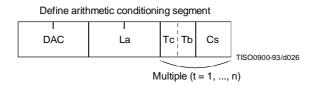

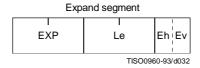

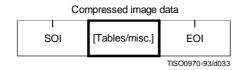

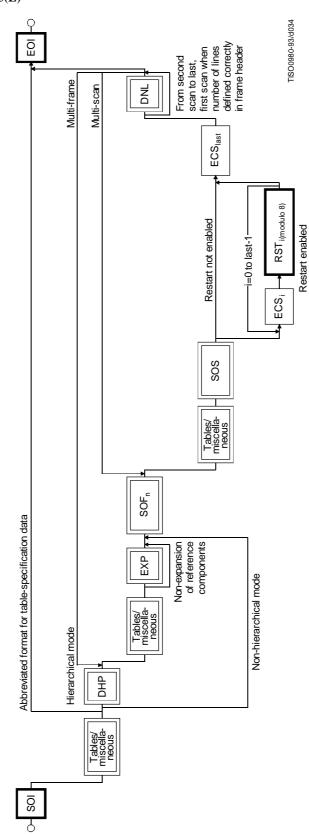

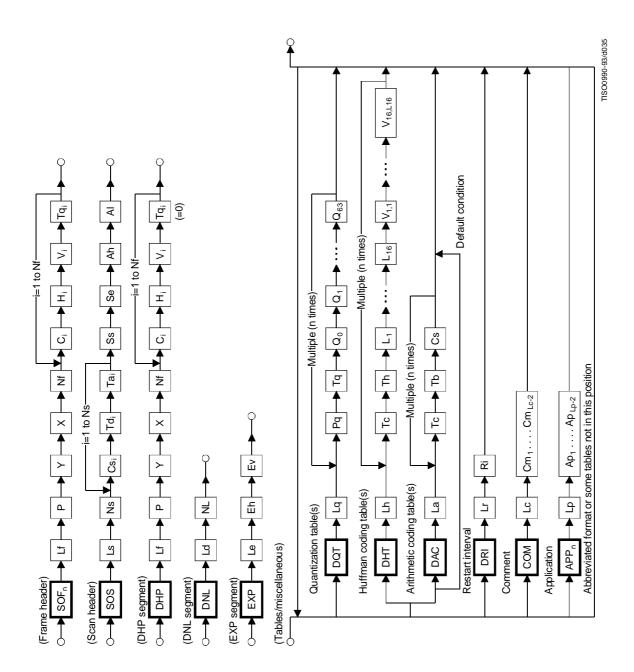

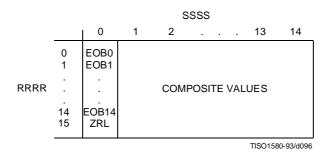

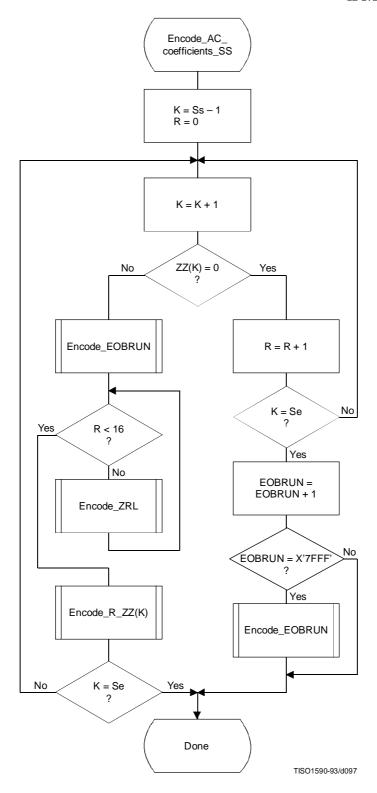

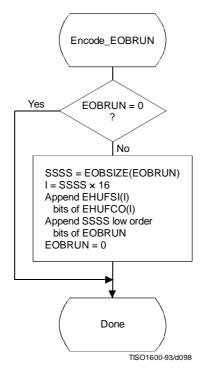

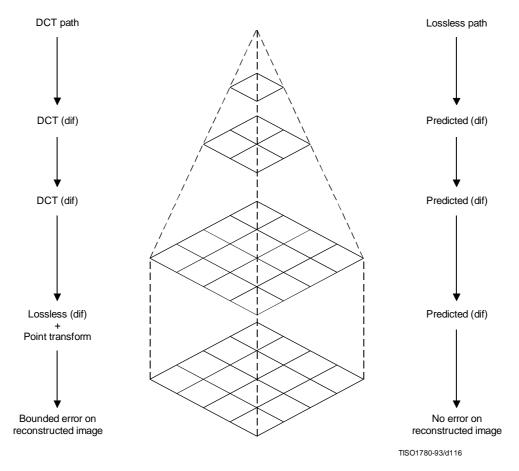

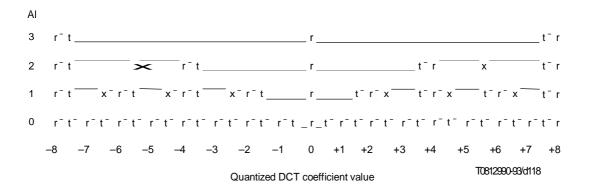

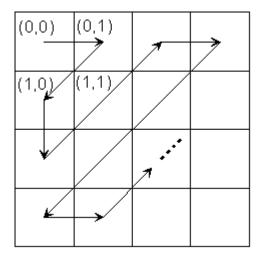

- compression which is based on the Discrete Cosine Transform ("DCT") and is described in the International Telegraph and Telephone Consultative Committee ("CCITT") Recommendation T.81 published in September 1992 (App. F). JPEG compression includes the following main steps: "1. The image is broken into 8x8 blocks of pixels. 2. Working from left to right, top to bottom, the DCT is applied to each block. 3. Each block is compressed through quantization. 4. The array of compressed blocks that constitute the image is stored in a drastically reduced amount of space. 5. When desired, the image is reconstructed through decompression, a process that uses the Inverse Discrete Cosine Transform (IDCT)." App. G at 1, Ken Cabeen & Peter Gent, *Image Compression and the Discrete Cosine Transform*.

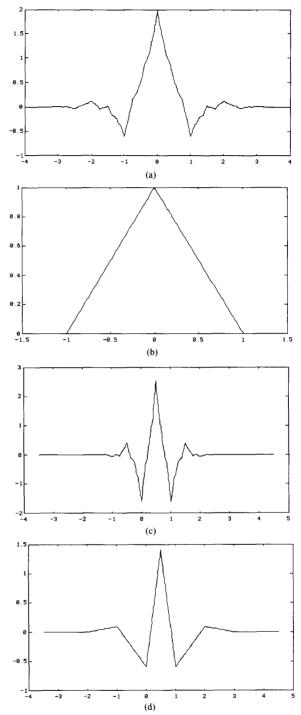

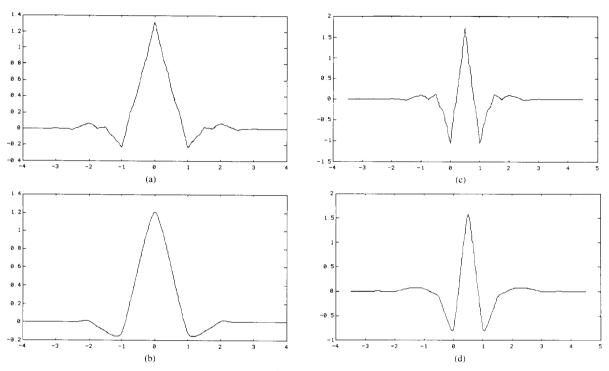

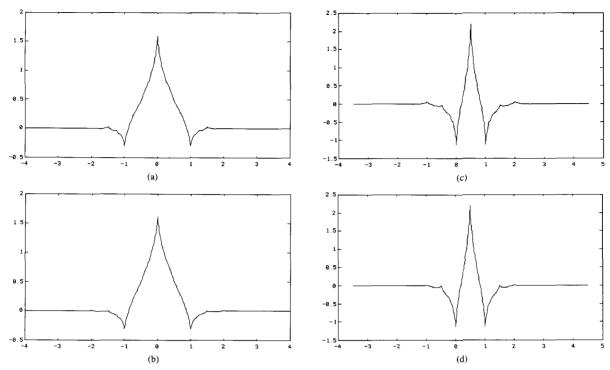

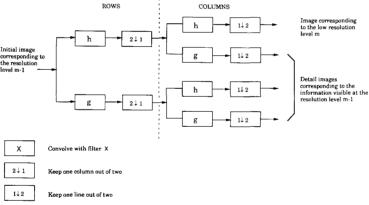

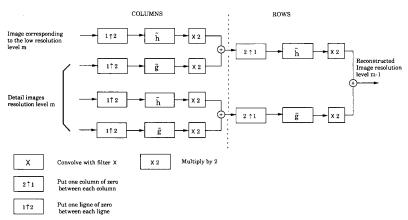

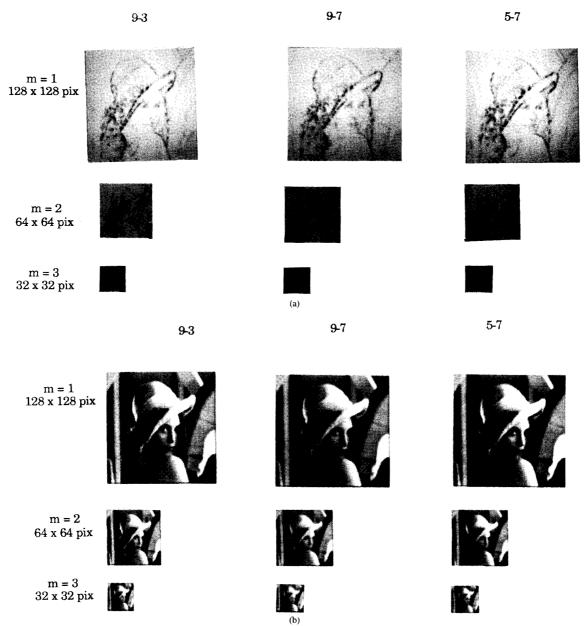

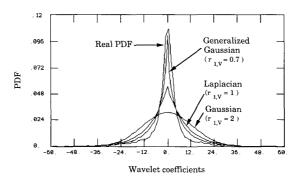

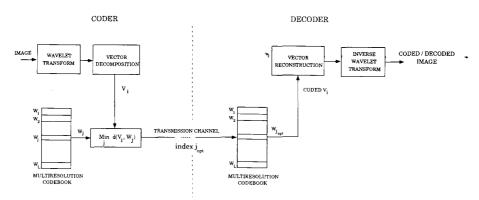

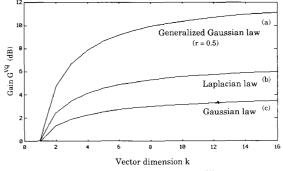

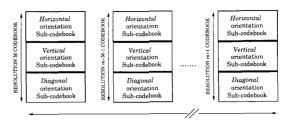

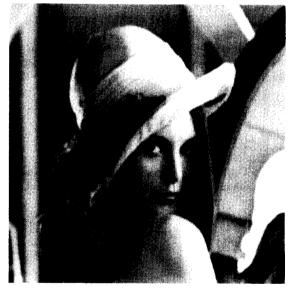

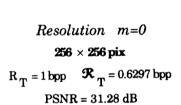

- 46. Another widely used method of digital image compression is based on the wavelet transform. For example, Marc Antonini et al.'s 1992 paper *Image*Coding Using Wavelet Transform discloses a scheme for image compression using

the wavelet transform. *See generally* App. H. In addition, the Antonini paper shows that image compression using wavelet transform not only achieves a good image quality (id. at 217-18), but is also suitable for a progressive transmission scheme to "allow the receiver to recognize a picture as quickly as possible at minimum cost." *Id.* at 218-19.

47. The JPEG 2000 image compression standard, which was designed as the next version of the JPEG Standard to address its identified problems, uses discrete wavelet transform.

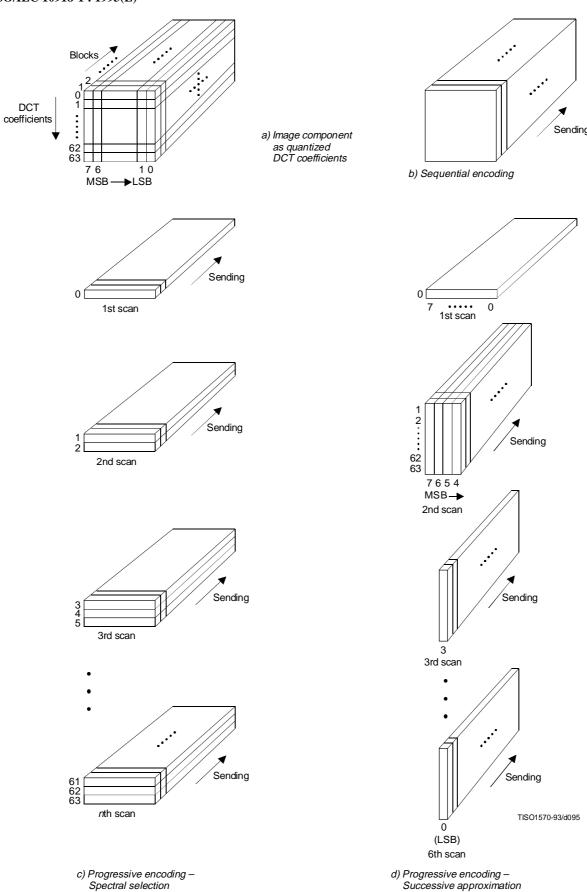

## E. Progressive Image Resolution Enhancement

and claimed in the 506 Patent is one of the "conventional" solutions that have been used to reduce the latency of transmitting complex images over a communications network, as admitted in the "Background of the Invention" section of the 506 Patent. Ex. 1001 at 1:55-65 ("Different conventional systems have been proposed to reduce the latency affect by transmitting the image in highly compressed formats that support **progressive resolution build-up of the image within the current client field of view**. . . . **Progressive image resolution transmission**, typically using a differential resolution method, permits an approximate image to be quickly presented with image details being continuously added over time.") (emphasis added).

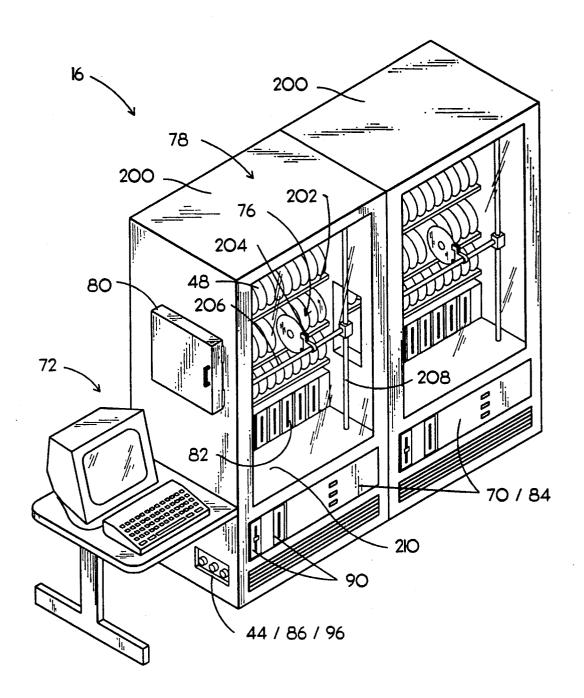

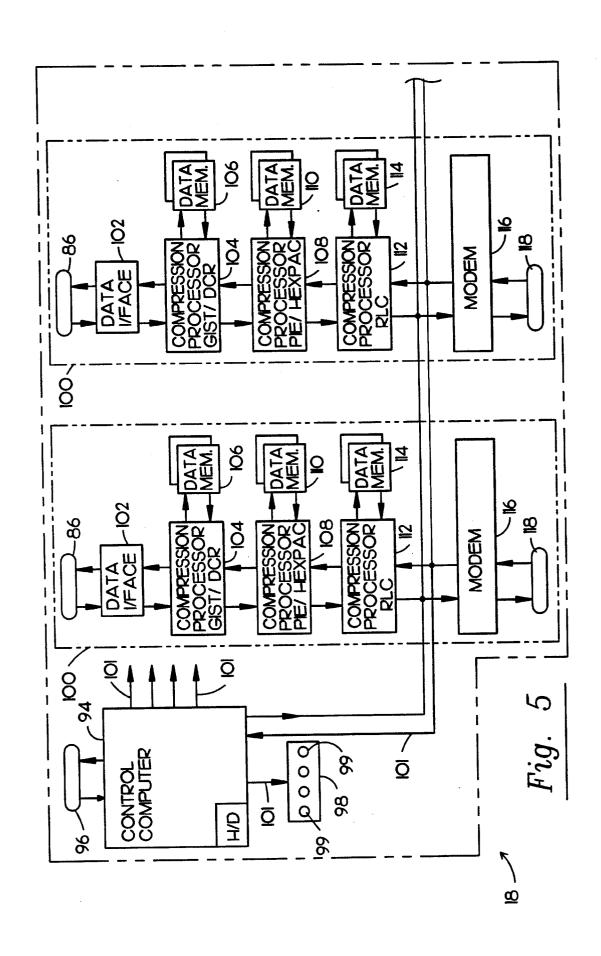

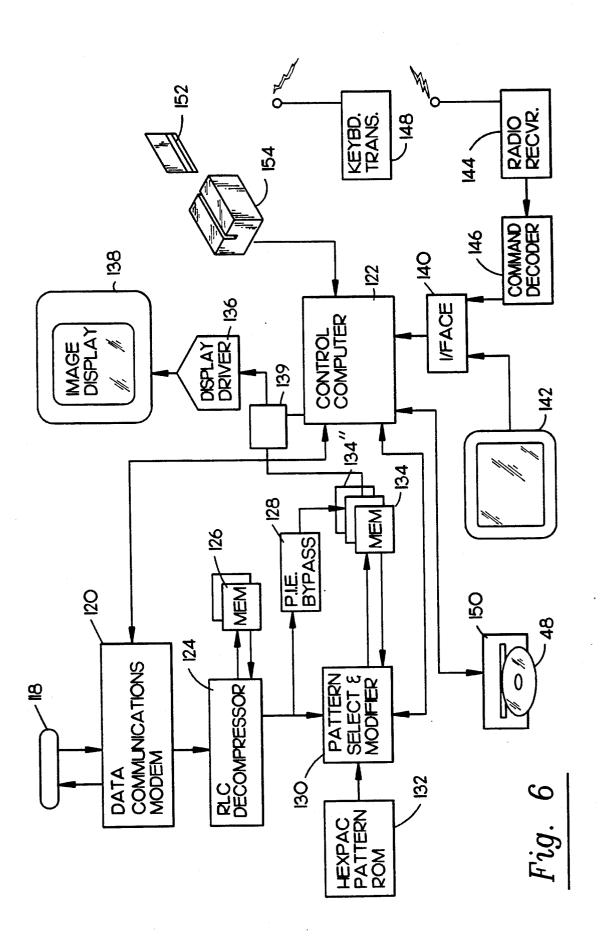

- 49. For example, U.S. Patent No. 5,321,520 to Inga et al., filed July 20, 1992 and issued June 14, 1994, discloses a "Progressive Image Enhancement" ("PIE") method, where a "'crude' image is presented to the subscriber" first and then the method "progressively enhance[s] the quality of the presented image" over time. App. I at col. 12:65-13:1. "The longer the user observers a selected image, the 'better' the image becomes in the sense of pixel resolution and quantity of gray levels." *Id.* at col. 13:1-3.

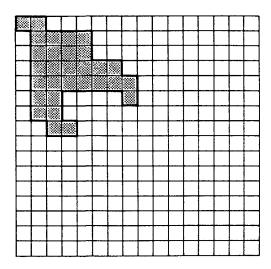

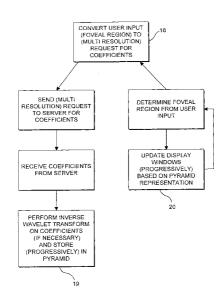

- 50. The U.S. Patent No. 6,182,114 to Yap et al. was filed January 9, 1998 and issued January 30, 2001. The "Background of the Invention" section of the 506 Patent mentions Yap. The Yap Patent recognizes that "progressive transmission" is an existing approach to solve the problem of "realtime visualization of large scale images over a 'thinwire' model of computation," i.e., over a "low bandwidth line." App. J at col. 1:47-65. In addition to the traditional progressive transmission method, where the higher resolution of the entire image will be eventually transmitted, the Yap Patent discloses an improved version of progressive transmission, where "resolution is also varied over the physical extent of the image." *Id.* at col. 2:4-17. Specifically, the Yap Patent discloses that "high resolution data is transmitted at the user's gaze point but with lower resolution as one moves away from that point." Id. at 2:18-20. The same scheme is used in the 506 Patent.

# F. Three-Dimensional Graphics

# 1. Overview of 3D Computer Graphics principles

- 51. Computer graphics is the art and science of drawing pictures on a display screen using a computer. A picture generated using computer graphics is created from numerical data describing the objects to be drawn. Computer graphics is generally divided into 2D ("two-dimensional") graphics that only depict images in two dimensions and 3D ("three-dimensional") graphics that depict images in three dimensions, although by way of a representation on a screen.

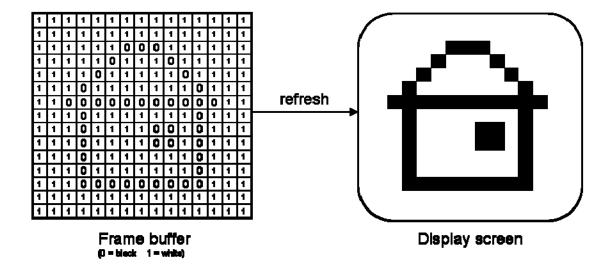

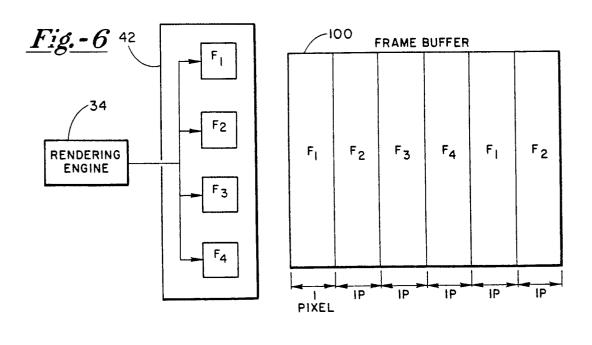

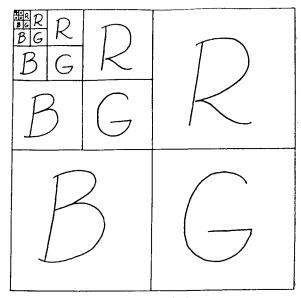

- 52. An image that shows up on a computer display typically corresponds to a large, rectangular, two-dimensional array of values in a computer memory called a frame buffer. An individual location in the frame buffer can hold a color value corresponding to one "dot" or picture element, or pixel for short, on the display screen. In the simple example shown below, the values in the frame buffer at each pixel are either 0 or 1, which get displayed as black and white, respectively, on the screen.

- 53. In display systems, color values at each pixel are usually either represented by a single number representing shades of gray, or by 3 numbers, R, G, and B, corresponding to red, green, and blue intensity values, for each location on the screen. The computer display is generated by repeatedly "scanning out" the array of numerical pixel values from the frame buffer memory in successive rows at a rate like 60 frames/second and used to produce the actual colors seen at each location on the screen.

- 54. When the computer changes an image displayed on the screen, it updates the corresponding values in the frame buffer. Simply writing a new number into the frame buffer at a given location results in a new color appearing at that position on the screen starting with the next refresh cycle.

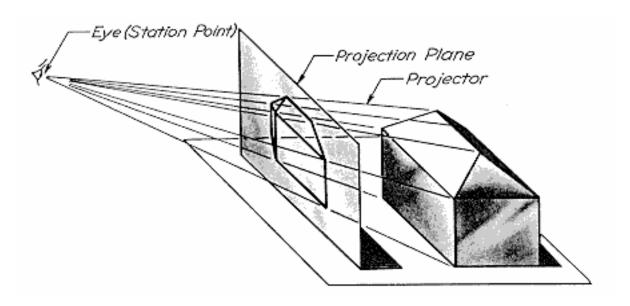

- 55. Creating an image of a 3D scene involves taking a mathematical description of the objects in a scene, looking at it from a given point of view, and

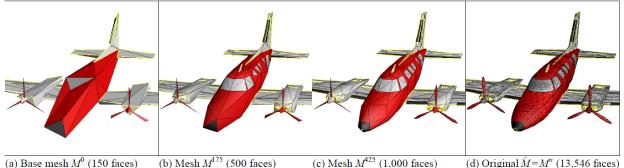

figuring out what colors to draw at all the pixel locations in the frame buffer to create the corresponding image on the screen, as shown in the following example of a 3D house being drawn on a 2D display. All 3D points in the scene are mapped to the corresponding pixels on the screen by projecting along lines of sight, as though the scene was being photographed by a camera onto film.

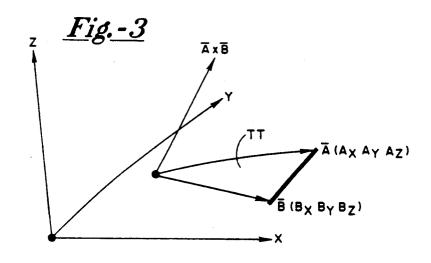

56. The mathematical description of the scene is known as a 3D model. Each 3D object in the 3D model is typically represented using a collection of geometric "primitives" such as points, lines, and polygons (usually triangles) that make up the object surfaces. In the simple example above, the house might be modeled using 4 polygons for the walls and 4 more polygons for the roof. Each polygon is defined by its vertices or corners. Typically, each vertex is specified using 3D numerical coordinates, X, Y, and Z, for its location in 3D space and R, G, and B values for its color. A mathematical process called rendering is used to

model a virtual "camera" looking at the 3D scene from a particular point of view, mathematically project all the 3D polygons into the corresponding 2D pixels in the display, and assign the appropriate colors to them in the frame buffer.

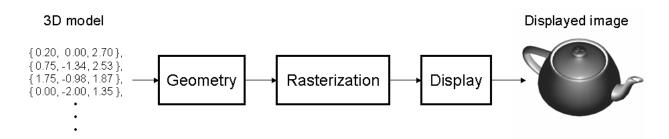

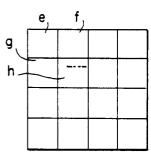

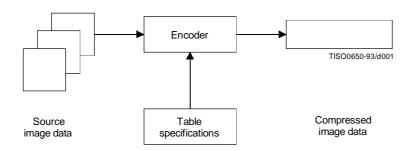

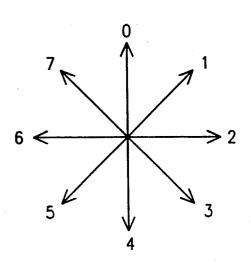

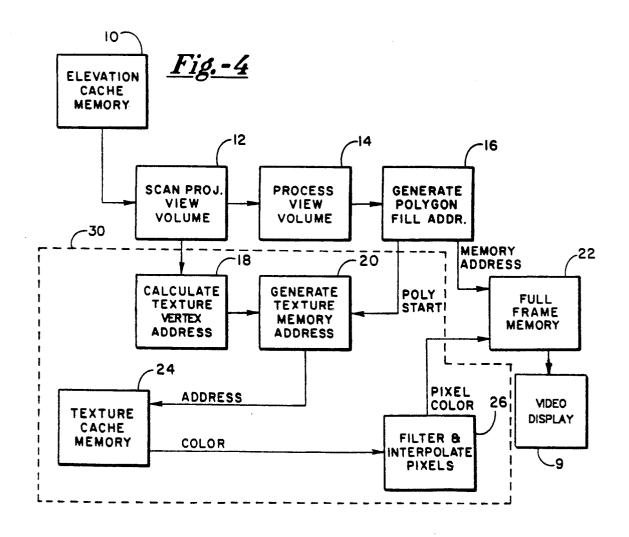

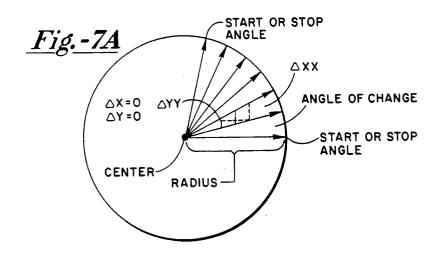

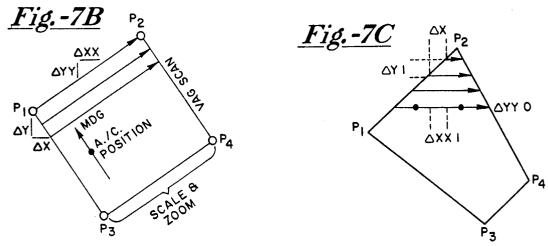

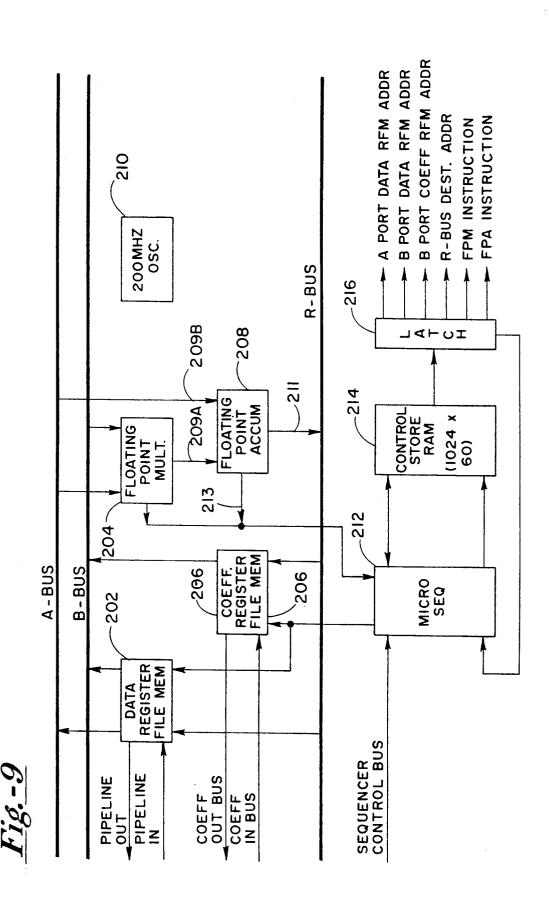

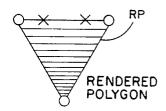

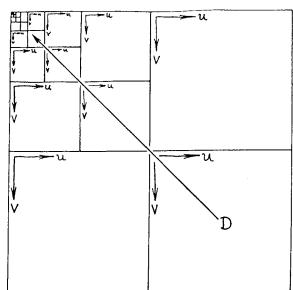

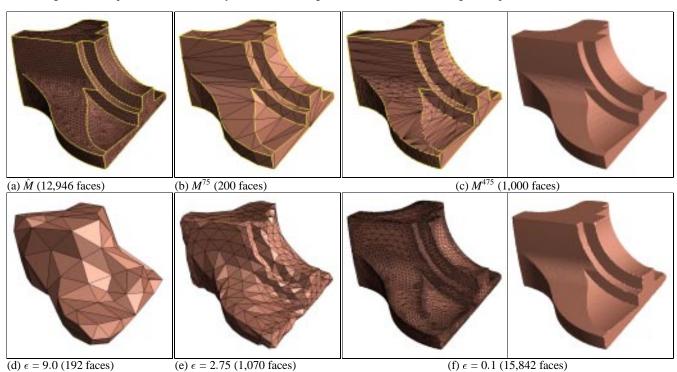

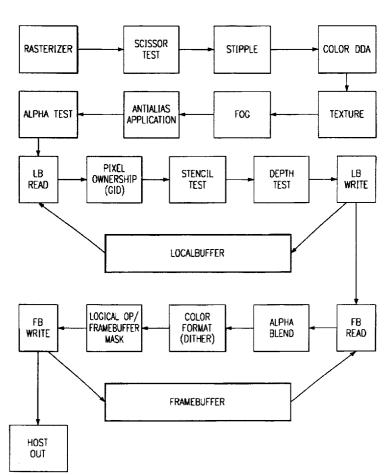

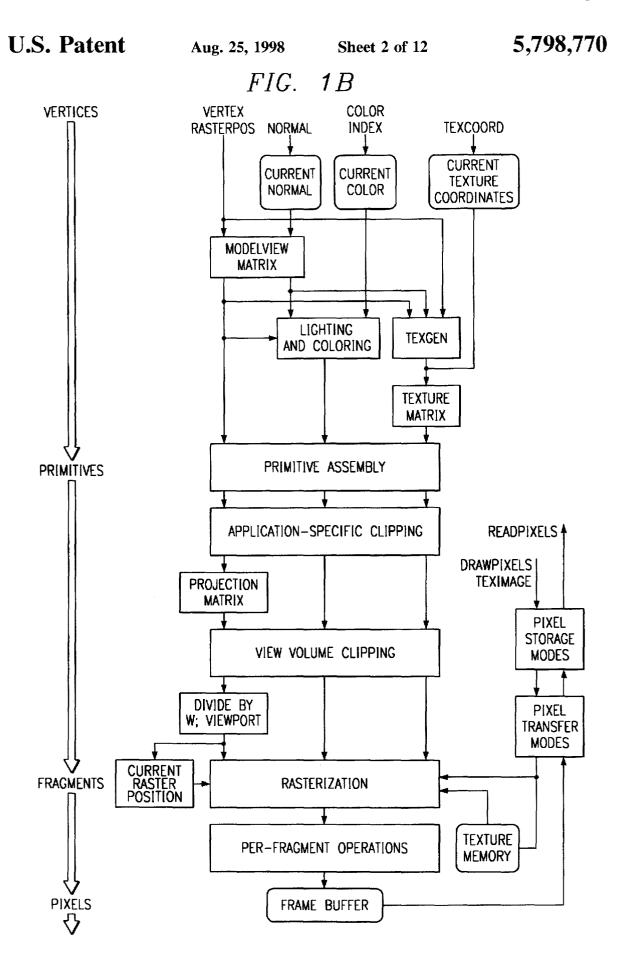

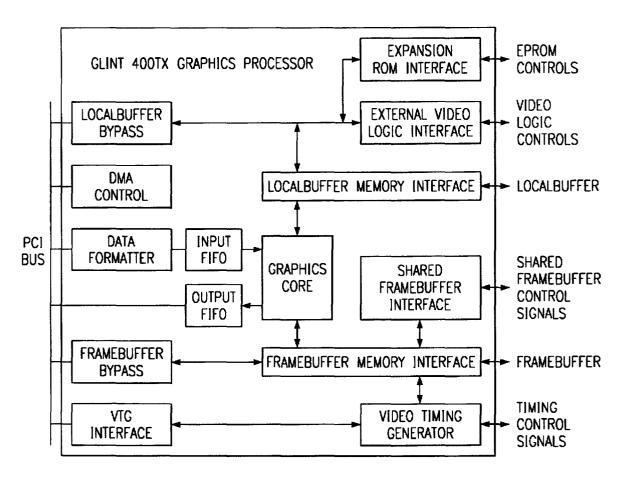

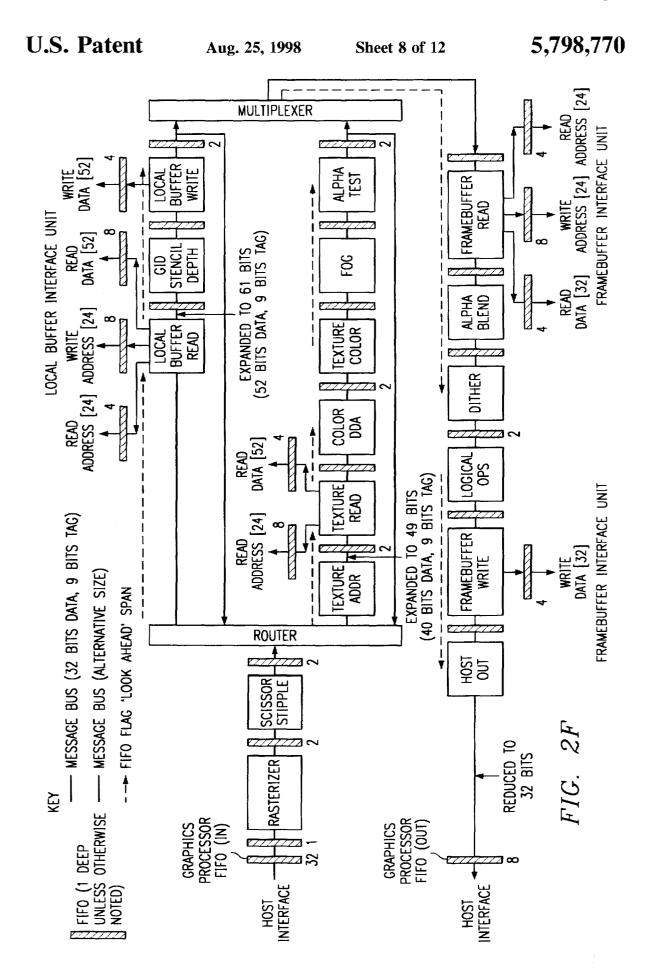

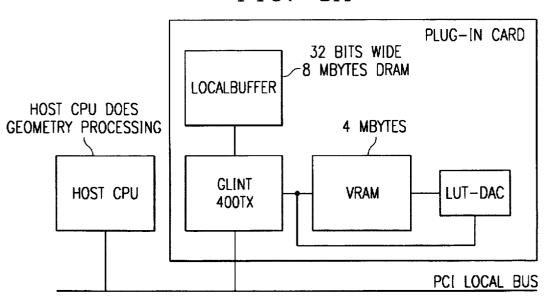

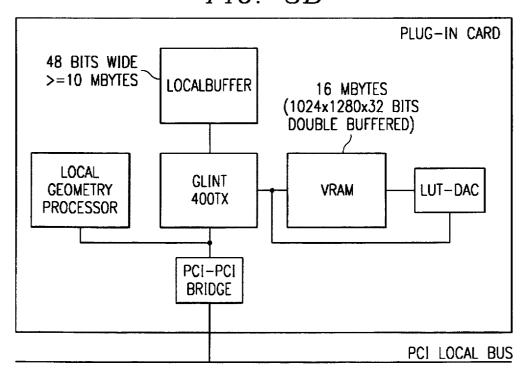

57. Various 3D computer graphics systems are built around the concept of a graphics pipeline. Acting like an assembly line, the graphics pipeline takes in the "raw materials" consisting of the data for the underlying 3D model and processes these through a series of computational steps to produce the image displayed on the 2D screen. In its simplest form, a graphics pipeline is described as having a series of three general phases, geometry, rasterization, and display, as shown in the diagram below:

58. In the above diagram, the 3D model represents the X, Y, Z coordinates and R, G, B color values for all the 3D polygons that make up the objects in the desired scene, along with certain other information such as the location of the camera, light sources, display boundaries, etc. Geometry refers to the calculations performed to mathematically transform the 3D coordinates of all the polygons in the 3D model into corresponding screen coordinates given the

location and orientation of the imaginary camera viewing the scene. Rasterization refers to the computations that determine all of the 2D pixel locations that will be visible within each 3D polygon and the colors those pixels should have. Display is then the process of writing the 2D pixel color values into the frame buffer and thereby causing the corresponding image to be displayed on the screen.

- 59. Rasterizing a polygon generally involves three main tasks: determining which pixels fall within the polygon (scan conversion), determining which of these pixels are visible on the screen (visible-surface determination), and determining what color to assign each visible pixel (shading).

- 60. The process of determining which pixels within the scan converted polygons will actually be visible on the screen is known as visible-surface determination. Depending on the direction from which the scene is viewed by the virtual camera, certain polygons (or portions thereof) may be occluded by other polygons and not visible on the screen, such as the back wall of the house in the example shown above. One common way to solve the visible surface problem is to write the RGB value for a pixel into the frame buffer only if its 3D position is closer to the camera than what may have been previously written into that same location by another polygon, much as an oil painting is painted in layers from back to front. This involves what is known in the art as depth buffering or z-buffering,

that is, keeping track of the depth or "Z" value (distance from the viewer's eye) currently residing at each pixel.

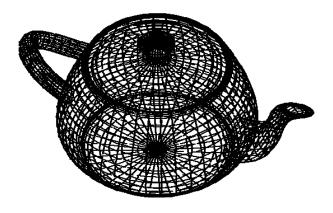

61. Once the scan conversion and rasterization processes are complete, the graphics program must assign colors to each visible pixel, a process that has evolved substantially over the history of computer graphics and depends on the level of realism desired in the resulting image. In the simple example below, only the scan converted pixels that make up the edges of each polygon are drawn with black pixels.

**Example of A Wireframe Image**

62. The rendering program may further assign colors either to the entire polygon or to individual pixels within the polygon. The colors assigned to whole polygons may be calculated based on the "intrinsic" or "base" color of the object itself and the orientation of that particular polygon with respect to an imaginary light source in the 3D scene. The resulting process is commonly known as flat

shading, as shown in the "teapot" example below based on an imaginary light source:

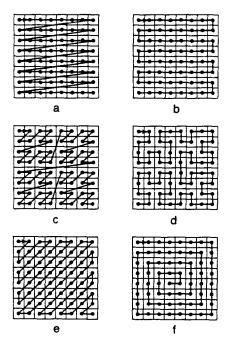

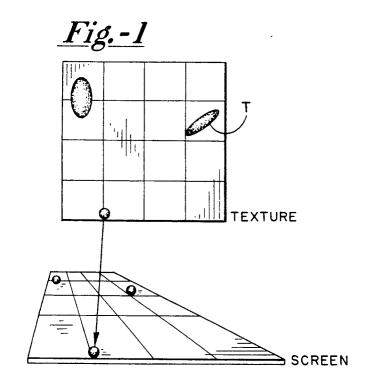

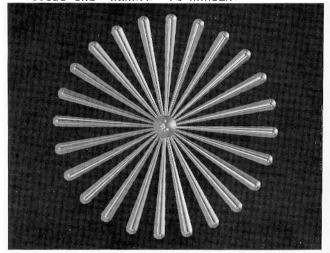

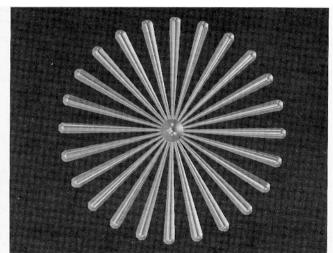

### 2. Texture

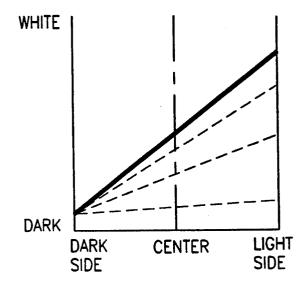

63. In 1974, "texture mapping" was developed as a further improvement in adding detail to objects or images. Texture mapping involves applying a 2D image or function approximating some real-world material like wood, bricks, fabric, marble, or a checkerboard, to the interior of polygons as in the image shown below. The "pixels" of a texture map are often referred to as texture elements or texels to distinguish them from the pixels of the resulting image. Texture mapping is like applying wallpaper or a decal to a surface. It is possible to construct a brick wall by carefully drawing many 3D bricks, which takes a lot of work, or one can simply paste a photograph of a brick wall onto an otherwise flat wall, which is easier and looks like a brick wall if you don't look too close. Texture mapping has become standard in 3D graphics systems to use texture mapping to quickly fill in realistic detail for many of the objects in a 3D scene, especially floors, walls, sky,

and other background areas. Textures can be either color images, or can be monochrome images used to modulate the untextured color of the polygon.

- 64. Some textures may be generic- for example, a 3D graphics rendering program might re-use a "wood" texture for all objects represented as wood. In this scenario, the texture is essentially a "wallpaper" with a repeating pattern applied to certain objects or surfaces within the field of view.

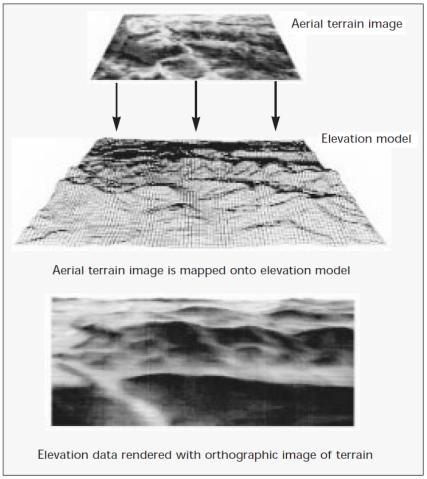

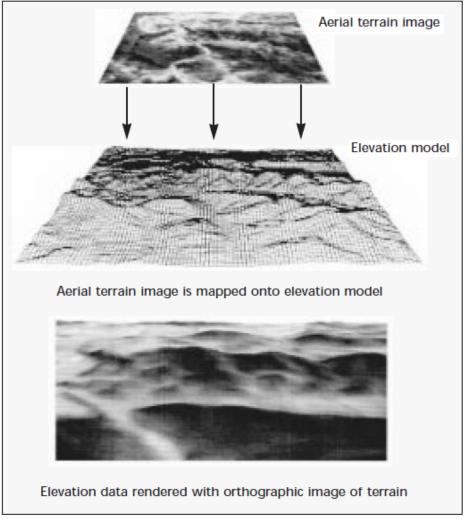

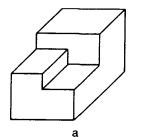

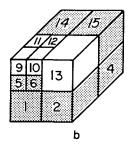

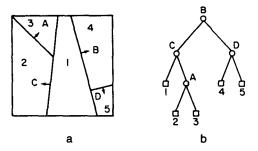

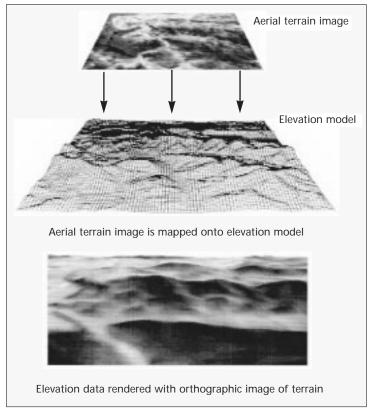

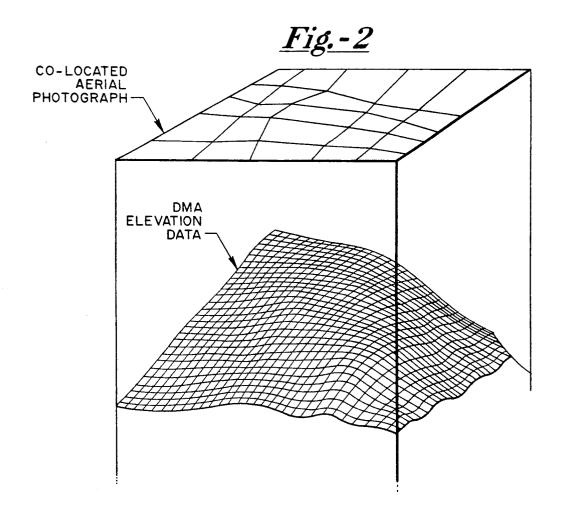

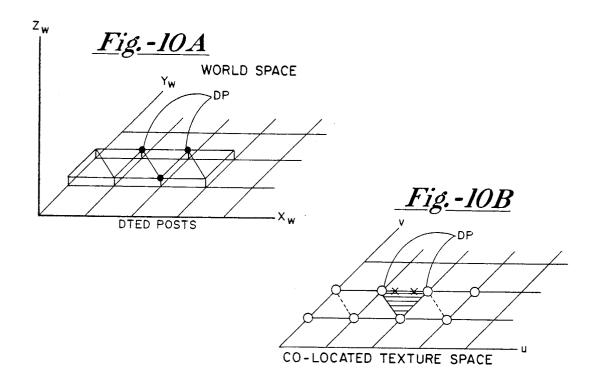

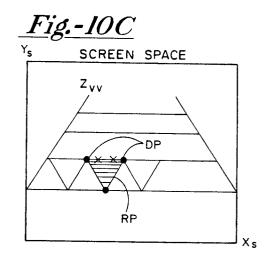

- 65. Textures may also be unique, or specific to a particular surface or object. This is often the case when photographs are used as textures. For example, when satellite or aerial photographs are used in a 3D rendering of a landscape, the specific portions of the imagery that correspond to a particular location are mapped onto the terrain at that location. For example, U.S. Patent No. 5,179,638 to Dawson et al., assigned to Honeywell, Inc., (App. K) illustrates how an aerial photograph can be used as "texture data" and mapped onto co-located digital elevation data, as shown in Fig. 2:

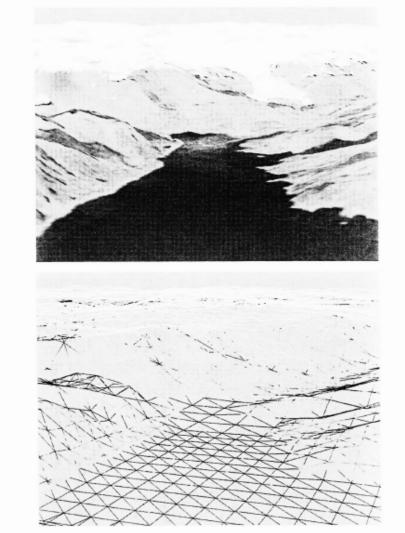

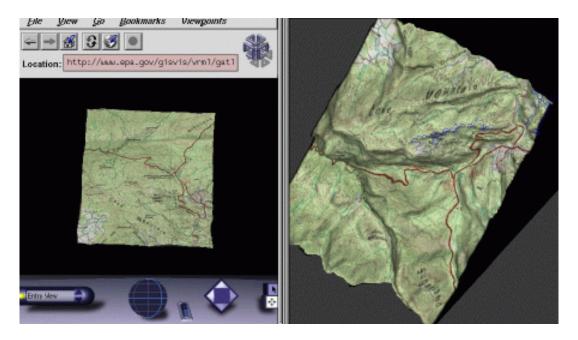

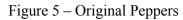

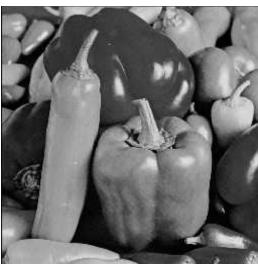

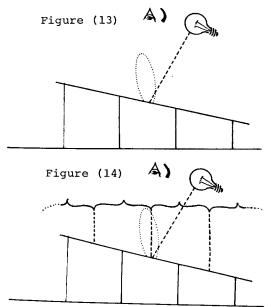

dimensional model of terrain is also known as a "synthetic view." Synthetic view technology can be used in aviation to provide a pilot operating at night or bad weather with a synthesized view of the terrain around them based on actual position (e.g. derived from GPS). Appendix AA, Hansen, J. et al, "Real-time synthetic vision cockpit display for general aviation," AeroSense '99, International Society for Optics and Photonics, 1999, describes such a system. In the figure below, the bottom portion of the figure shows a wire-frame diagram illustrating the three-dimensional model of terrain, while the top image shows the synthetic view created by rendering satellite imagery on the terrain model:

Figure 5. Terrain with extreme amounts of structure can be accommodated with high fidelity. The bottom graphic is a wire frame image of the Alaskan coastline. On the top is the fully rendered scene with imagery.

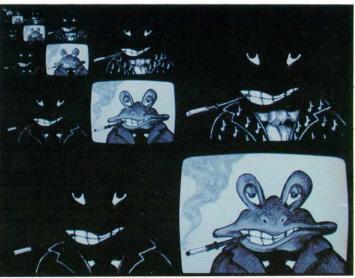

67. Microsoft used a similar technique with its popular Flight Simulator series of computer games, starting with Flight Simulator 1995. Flight Simulator utilized a real-time 3D rendering of terrain features with textures generated from a variety of sources, including satellite imagery. The figure below illustrates a 3D perspective view generated in Flight Simulator 2000, which was actually released in late 1999:

68.

## G. Mip-Maps

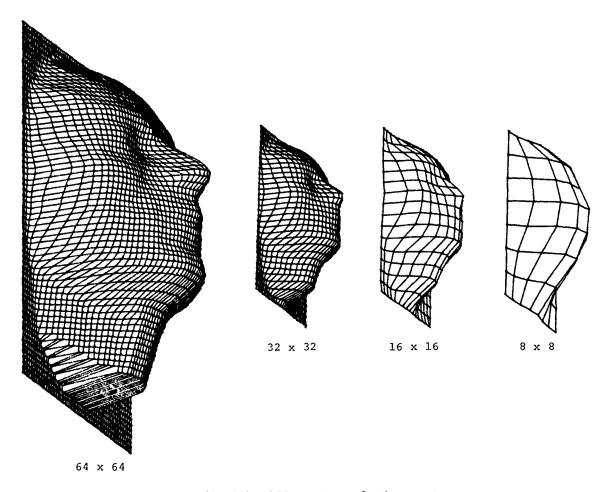

- 69. The provisional applications that the 506 Patent claims priority to described the use of "mip-maps" as "surface textures when rendering a two-dimensional representation of a three-dimensional scene." *See, e.g.*, Ex. 1010 at 7-9. This mip-mapping technology, however, has been used for rendering surface textures since 1979, more than two decades before the filing date of the provisional applications to which the 506 Patent claims priority. App. L at 2, Lance Williams, *Pyramidal Parametrics*, Computer Graphics, vol. 17, no. 3, July 1983.

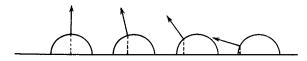

- 70. The term "mip" derives from the Latin phrase "multum in parvo" meaning "many things in a small place." The term was adopted by Lance Williams in his 1983 paper, which indicated that "the mip-mapping technology has been used successfully to bandlimit texture mapping . . . since 1979." *Id.* Mip-

71. An illustration of the mipmap pyramid is shown below. *See* Photospector Blog, <a href="http://photospector.com/gigapixels/">http://photospector.com/gigapixels/</a>.

<sup>&</sup>lt;sup>1</sup> Available online at

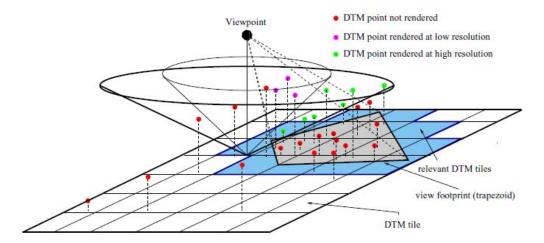

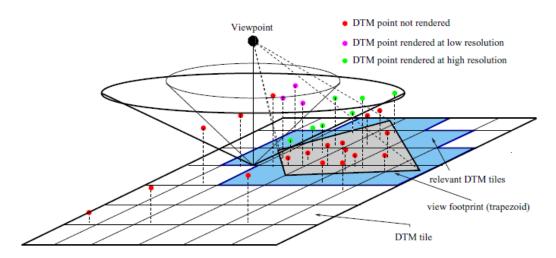

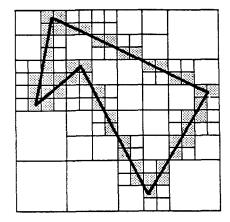

72. By the late 1990s, mipmaps were commonly used in 3D graphics applications, among other purposes, to render object textures at varying levels of detail based on the proximity of the object to the simulated viewpoint. For example, it would ordinarily be preferable to display an object in close proximity to the viewpoint at a high level of detail where the display is capable of showing a high level of texture detail, whereas for more distant objects a lower level of resolution is preferable because the display screen is unlikely to be capable of displaying the highest-resolution texture at a great distance, and because lower-resolution textures

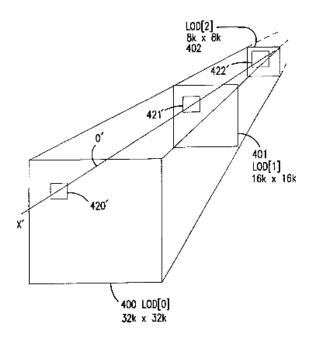

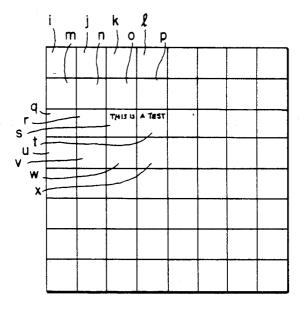

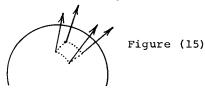

require far less system resources and bandwidth to retrieve, load and render. U.S. Patent No. 5,760,783 to Migdal et al ("Migdal," App. BB) is a patent from Silicon Graphics which describes how mipmaps may be used to render textures- including satellite or aerial photographs used as terrain textures for large maps, such as a flight simulator application. App. BB, 9:5-17, 10:14-19. Migdal illustrates how mipmaps at higher levels of detail may be used for points closer to the viewpoint and lower levels of detail for more distant objects. For example, Fig. 4C of Migdal illustrates a perspective view of regions of three different level of detail maps aligned with a center line from an eyesight location:

FIG.4C

- 73. Migdal teaches that Fig. 4C illustrates that the clip-map "contains sufficient texel data to cover larger minified areas in the background of a display where coarser texture detail is appropriate." *Id.* at 10:3-5. In my opinion, this teaching of Migdal is representative of what was already well-known in the art long before the earliest priority date claimed by the 506 Patent: that 3D graphics applications could "mipmaps" or similar level-of-detail pyramids, to render objects closer to the viewpoint at a higher resolution and objects more distant from the viewpoint at a lower resolution.

- 74. Fuller (App. E) also illustrates this principle of using mipmaps to display closer objects at higher resolution and more distant objects at lower resolution. Fuller describes an online system for 2D and 3D visualization of map data, which creates a 3D perspective representation of a landscape using a digital elevation model (DEM), then uses mipmaps of aerial images as the textures. App. E, Fig. 4:

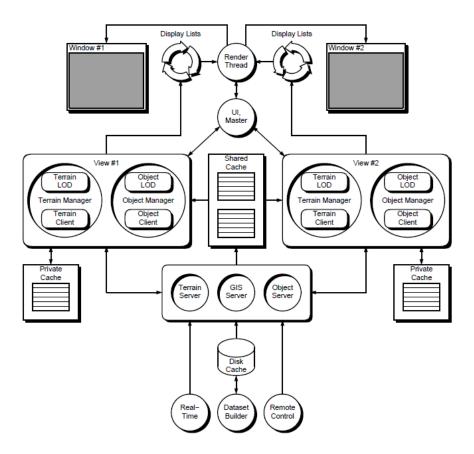

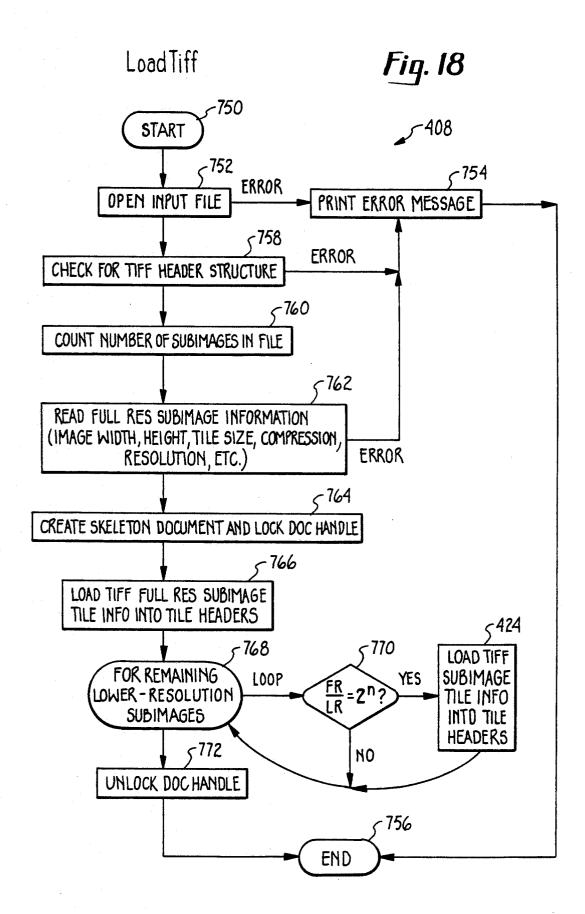

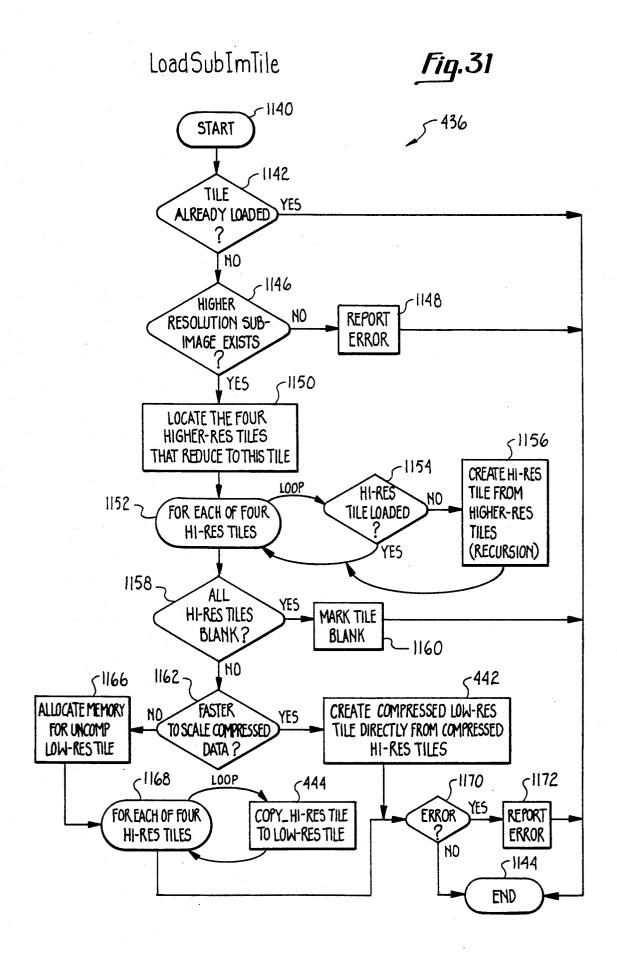

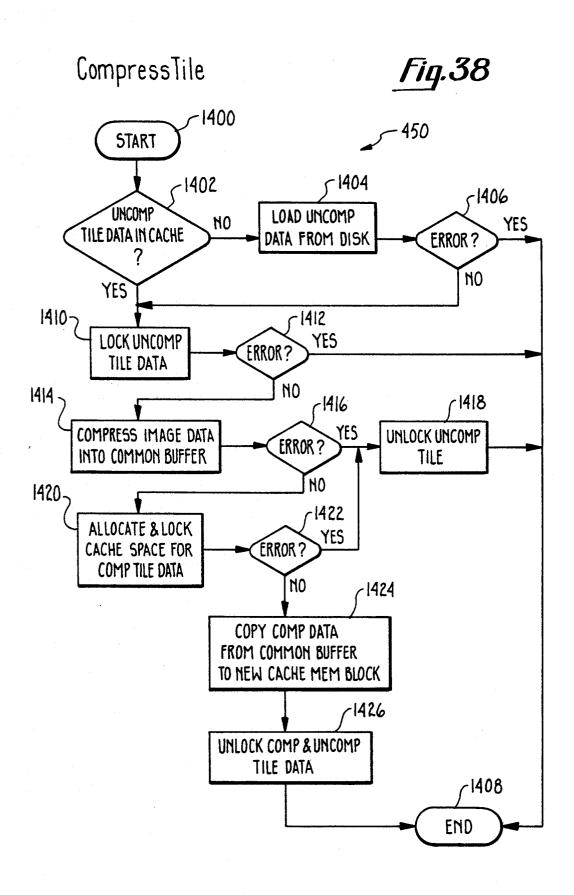

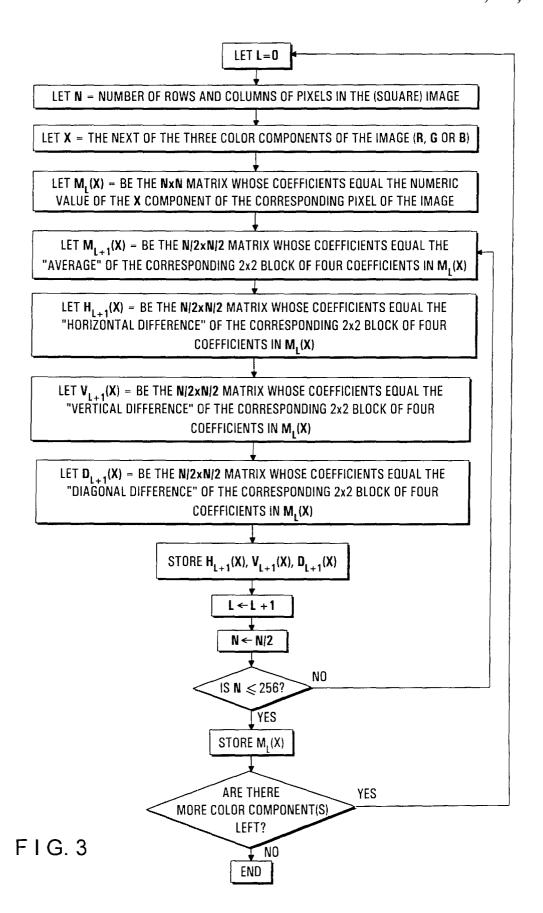

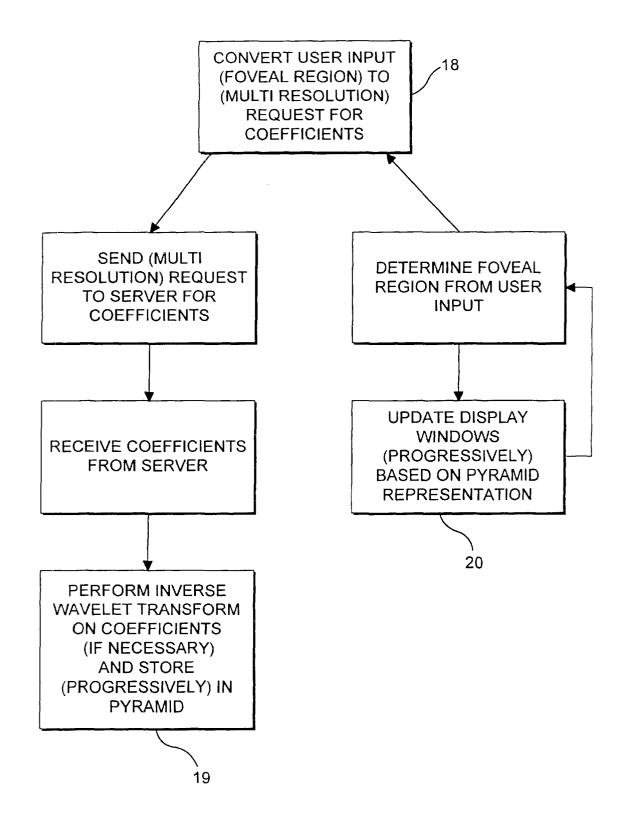

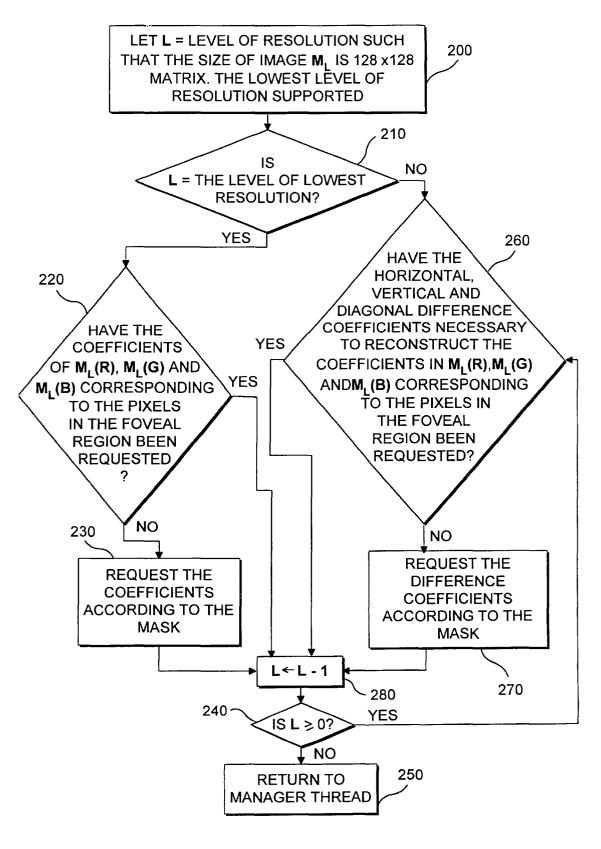

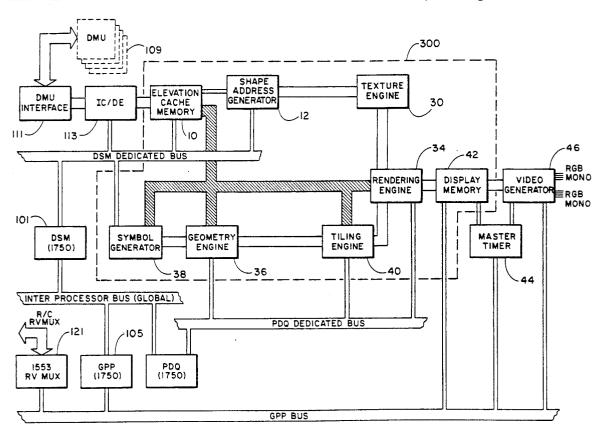

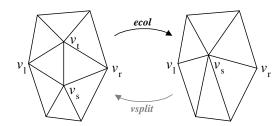

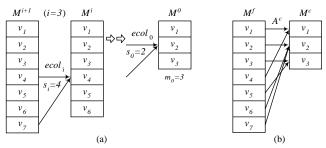

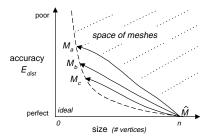

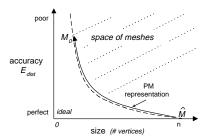

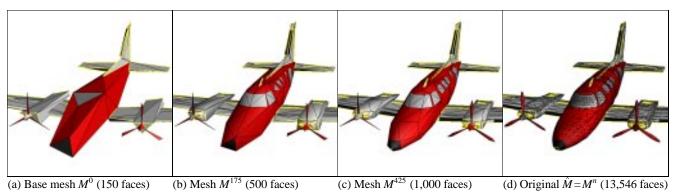

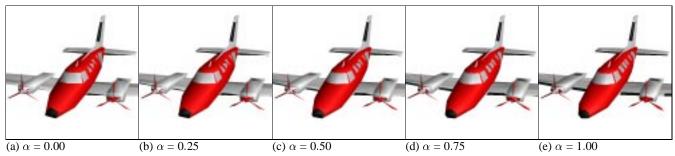

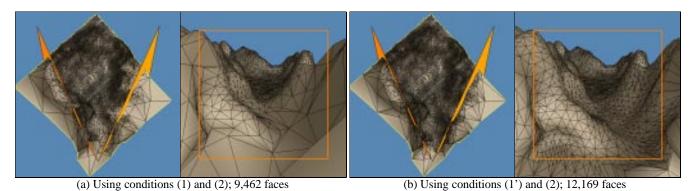

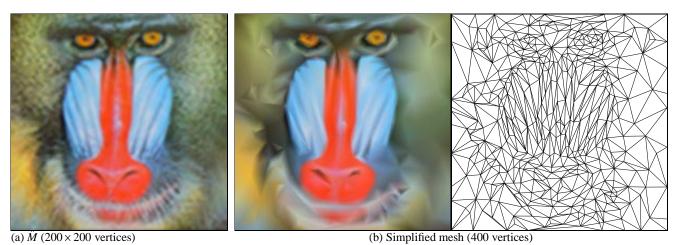

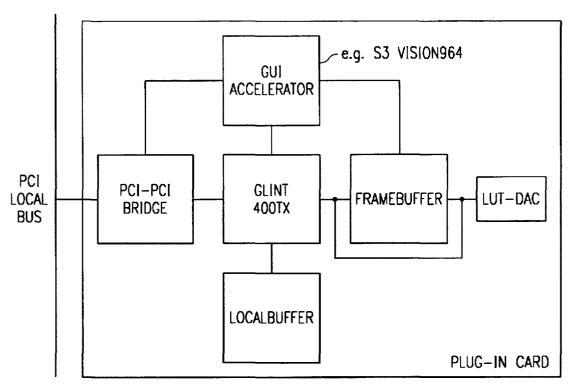

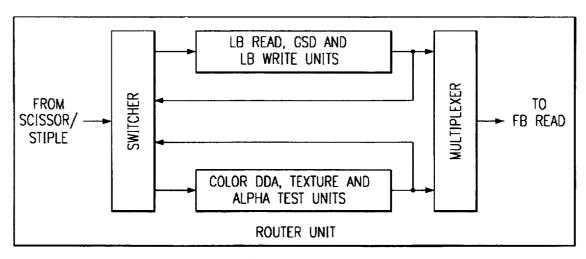

■ Figure 4. Mapping an ortho-image onto its digital elevation model. (Source: SRI International)