- 4. Checklists

- 5. Emergency procedures

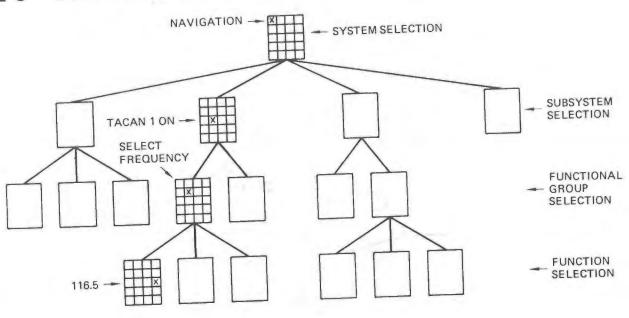

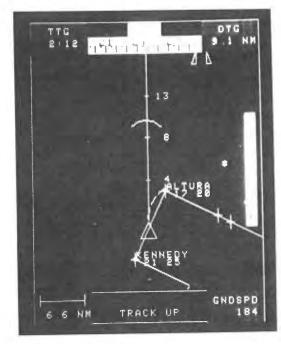

- 6. Data from nav systems

- 7. Diagnostics

- 8. Backup for EICAS displays

## EICAS (Engine Instrumentation and Crew Alerting Systems)

EICAS systems are currently available for the 757/767 and the Airbus 300 and 310. To date EICAS has not been certified in a general aviation aircraft though all of the avionics vendors are working on systems for specific aircraft types. There are several issues with EICAS:

- 1. Is there sufficient panel space for two tubes?

- 2. Will the airframe support the weight and power penalty that EICAS brings with it?

- 3. During engine start, how will the system be powered?

- 4. Can the reversionary display tube be used as an MFD when not needed for EICAS?

- 5. What should be displayed (all parameters, only the essential engine parameters, all warnings of only the noncritical advisories)?

From the list above, it can be seen that the application of EICAS in general aviation aircraft needs careful study and perhaps some new technology before it can achieve the same level of acceptance as EFIS. The most promise lies in the integration of the entire cockpit by an all new system. In fact, this is the direction that all of the avionics vendors are headed.

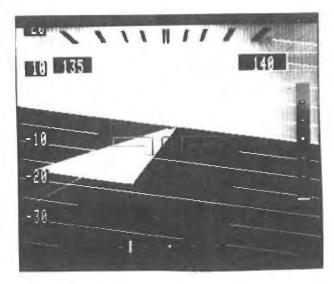

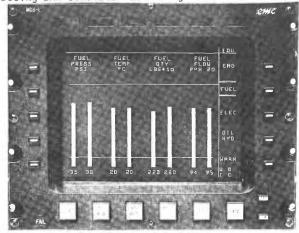

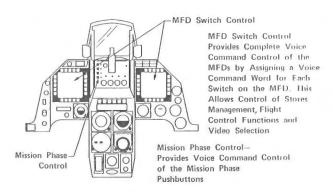

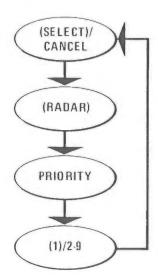

Fig. 17 Engine Instruments

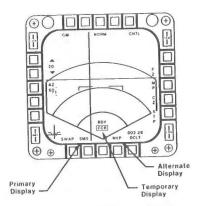

Fig. 18 Crew Alerting Systems

## Future Directions

It is obvious that the shell has only been cracked in the application of CRT's to the business aviation cockpit. Currently, work is going on in several areas:

- 1. Side by side 8"x8" tubes

- 2. Integrated symbol generators

- 3. High speed CMOS to reduce heat

- Fully integrated avionics shipsets that share a great deal of their hardware.

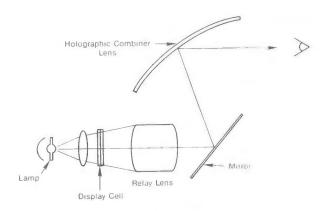

- 5. Three dimensional displays

- 6. Voice entry systems

- 7. Integrated FMS and EFIS systems

- 8. CRT (stand-alone) air data instruments

- 9. Raster only high resolution tubes

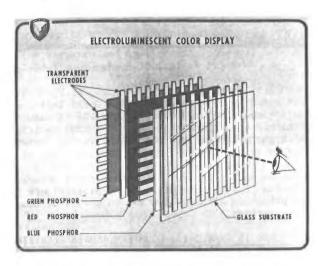

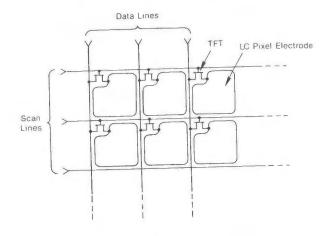

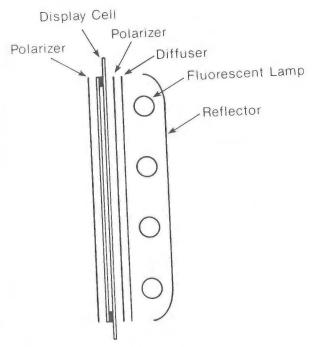

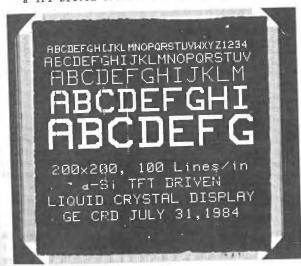

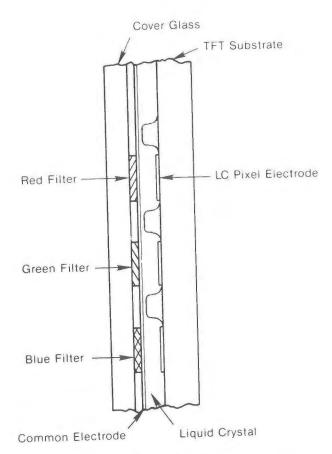

- 10. Liquid crystal and other "flat plate" displays

General aviation avionics finds its way into many other markets. It is typically an evolutionary rather than revolutionary growth. When Boeing developed the all-digital shipset, general aviation systems engineers were literally green with envy because they recognized the advantages of this type of change.

At this time, the first all-digital general aviation aircraft (the SF-340 and the BAe-800) have been certified and are starting the payoff period that EFIS initiated in 1982. The future is exciting, to say the least, now that the core systems are all-digital.

## References

(1) Robert J. Tibor, John C. Hall, "Flight Management Systems III Where Are We Going And Will It Be Worth It," Collins Air Transport Division, Rockwell International

## 8

# SESSION 8 FAULT TOLERANT AVIONICS

## Chairmen:

Billy L. Dove NASA Langley Research Center

Dennis B. Mulcare Lockheed-Georgia Co.

This session addresses the application of fault tolerant technologies to digital avionics, including architectural concepts and software techniques used to achieve fault tolerance.

Jaynarayan H. Lala<sup>1</sup>

The Charles Stark Draper Laboratory, Inc. Cambridge, Massachusetts 02139

#### ABSTRACT

The Advanced Information Processing System (AIPS) is designed to provide a fault tolerant and damage tolerant data processing architecture for a broad range of aerospace vehicles. This paper describes the AIPS concept and its operational philosophy. A proof-of-concept (POC) system is now in the detailed design phase. The second half of the paper describes the architecture of the POC system building blocks.

#### 1.0 INTRODUCTION

-21

The Advanced Information Processing System (AIPS) is designed to provide a fault tolerant and damage tolerant data processing architecture that meets aeronautical and space vehicle application requirements. The requirements for seven different applications are described in the 'AIPS System Requirements' [1]. The requirements can be divided into two categories: quantitative and qualitative. Examples of the former are processor throughput, memory size, transport lag, mission success probability, etc. Examples of the latter are graceful degradation, growth and change tolerance, integrability, etc. The AIPS architecture is intended to satisfy the quantitative requirements and also have attributes that make it responsive to the qualitative requirements.

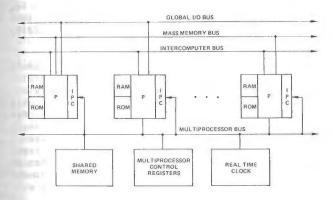

The system is comprised of hardware 'building blocks' which are fault tolerant processing elements, a fault and damage tolerant intercomputer network and an input/output network, and a fault tolerant power distribution system. A network operating system ties these elements together in a coherent system.

The system is managed by a Global Computer that allocates functions to individual processing sites, performs system level redundancy management and reconfiguration, and maintains knowledge of the system state for distribution to the component elements. The system management functions may be reassigned to an alternating processing site in-flight. Redundancy management, task scheduling, and other local services at individual processing sites are handled by local operating systems. The network operating system links local operating systems together for such functions as intertask communications.

The following sections define the AIPS in greater detail. Section 2 is a conceptual definition of the system and its operational philosophy. Section 3 is a more specific description of the proof-of-concept (POC) system configuration, the AIPS building blocks, and their architecture. For a more complete description of the AIPS system please see 'AIPS System Specification' [2].

The AIPS architecture permits application designers to select an appropriate set of the building blocks and system services and configure a specific processing system for their application. The application designer need not include all the building blocks that are present in the POC system. The number and type of building blocks and their configuration will be determined by the specific applications requirements.

## 2.0 AIPS CONCEPTS

#### 2.1 OVERVIEW

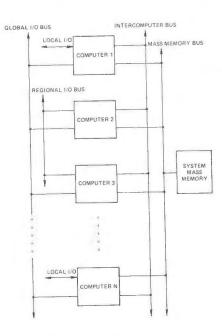

The Advanced Information Processing System consists of a number of computers located at processing sites which may be physically dispersed throughout the vehicle. These processing sites are linked together by a reliable and damage tolerant data communication bus, called the Intercomputer Bus or the IC bus.

A computer at a given processing site may have access to varying numbers and types of Input/Output (I/O) buses. The I/O buses may be global, regional or local in nature. Input/Output devices on the global I/O bus are available to all or at least a majority of the AIPS computers. Regional buses connect I/O devices in a given region to the processing sites located in their vicinity. Local buses connect a computer to the I/O devices dedicated to that computer. Additionally, there may be memory mapped I/O devices that can be accessed directly by a computer similar to a memory location. Finally, there is a system Mass Memory that is directly accessible from all computers in the system on a dedicated multiplex Mass Memory (MM) bus.

Input/Output devices on the global I/O bus are available system wide. The global I/O bus is a time division multiple access (TDMA) contention bus. The intercomputer (IC) bus is used to transmit commands and data between computers. The IC bus is also a TDMA contention bus.

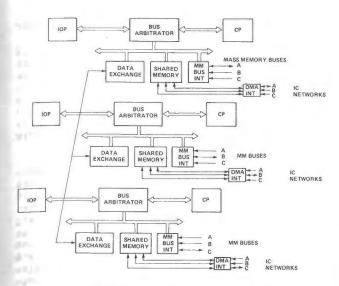

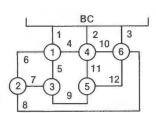

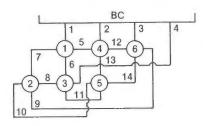

Figure 1 shows a simplified system level diagram of the AIPS architecture.  $\,$

Computers at various AIPS processing sites are General Purpose Computers (GPCs) of varying capabilities in terms of processing throughput, memory, reliability, fault tolerance, and damage tolerance. Throughput may range from that of a single microprocessor to that of a large multiprocessor. Memory size will be determined by application requirements. Reliability, as measured by probability of failure due to random faults, ranges from 10<sup>-4</sup> per hour for a

Member AIAA, IEEE.

Copyright © American Institute of Aeronautics and Astronautics, Inc., 1984. All rights reserved.

simplex processor to 10<sup>-10</sup> per hour for a multiprocessor that uses parallel hybrid redundancy. For those functions requiring fault masking a triplex level of redundancy is provided. For low criticality functions or noncritical functions, the GPCs may be duplex or simplex. Parallel hybrid redundancy is used for extremely high levels of fault tolerance and/or for longevity (long mission durations). GPCs can also be made damage tolerant by physically dispersing redundant GPC elements and providing secure and damage tolerant communications between these elements. Within AIPS, computers of varying levels of fault tolerance can coexist such that less reliable computers are not a detriment to higher reliability computers.

The overall framework in which AIPS operates can be characterized as a limited form of a fully distributed multicomputer system. A fully distributed fault and damage tolerant system must satisfy several requirements. The following subsections describe these requirements and characterize the AIPS architecture in the context of these requirements.

#### 2.2 FUNCTION MIGRATION

A fully distributed system must have a multiplicity of resources which are freely assignable to functions on a short-term basis [3]. AIPS has multiple processing sites; however, they are not freely assigned to functions on a short-term basis. During routine operations the General Purpose Computers at various processing sites are assigned to perform a fixed set of functions, each computer doing a unique set of tasks. However, in response to some internal or external stimulus, the computers can be reassigned to a different set of functions. This results in some functions migrating from one processing site to another site in the system. Under certain conditions, it may also result in some functions being suspended entirely for a brief time period or for the remainder of the mission. In AIPS this form of limited distributed processing is called semi-dynamic function migration.

The internal stimuli that result in function migration may consist of detection of a fault in the system, a change in the system load due to a change in mission phase, etc. An example of an external stimulus is a crew initiated reconfiguration of the system.

## 2.3 RESOURCE TRANSPARENCY

Another characteristic of a fully distributed system is that the multiplicity of resources should be transparent to the user. To a large extent, this is true in the AIPS. Function migration is transparent to the function and the person implementing that function in software. Interfunction communication is handled by the operating system such that the location of the two communicating functions is also transparent to both. The two functions could be collocated in a GPC or they may be executing in different GPCs. Indeed, at one time they may be collocated, while at a later time one of them may have been migrated to another site. This transparency is achieved through a layered approach to interfunction communication. One of these layers determines the current processing site of the function to which one wishes to communicate. If it is another GPC, another layer in the communication hierarchy is invoked that takes care of appropriate IC bus message formatting and interface to the bus transmitters and

Figure 1. AIPS Architecture: A Software View

receivers, that is, the physical layer. This layered approach is responsible for hiding the existence of multiple computers from the applications programmer.

#### 2.4 SYSTEM CONTROL

Another characteristic of a totally distributed system is that the system control is through multiple cooperating autonomous operating systems. The AIPS operational philosophy differs considerably in this regard. The overall AIPS system management and control authority is vested in one GPC at any given time. This GPC is called the Global Computer. All other GPCs are subservient to this GPC as far as system level functions are concerned. However, all the local functions are handled quite independently by each computer. This philosophy is more akin to a hybrid of hierarchical and federated systems. This is explained in the following.

Under normal circumstances each GPC operates fairly autonomously of other computers. Each GPC has a Local Operating System that performs all the functions necessary to keep that processing site operating in the desired fashion. The local operating system is responsible for an orderly start and initialization of the GPC, scheduling and dispatching of tasks, input/output services, task synchronization and communication services, and resource management. It also is responsible for maintaining the overall integrity of the processing site in the presence of faults. This involves fault detection, isolation, and reconfiguration (FDIR). The local operating system performs all of the redundancy management functions including FDIR, background self tests, transient and hard fault analysis, and fault logging.

The services provided by local operating systems at various processing sites are similar although they may differ in implementation. For example, the multiprocessor version of the operating system must take into account the multiplicity of processors

for task scheduling. Similarly, it must also consider the more complex task of redundancy management and cycling of spare units. The uniprocessor operating system can also have different variations depending upon the level of redundancy and the I/O configuration.

The Local Operating System in each computer interfaces with the Network Operating System. The Network Operating System is responsible for system level functions. These include an orderly start and initialization of various buses and networks, communication between processes executing in different computers, system level resource management, and system level redundancy management. System level resources are the GPCs, the I/O, IC, and the MM buses, and the shared data and programs stored in the mass memory or in some other commonly accessible location. System redundancy management includes FDIR in the I/O and IC node networks, correlation of faults in GPCs (both transient and hard faults), reassignment of computers to functions (function migration), and graceful degradation in case of a loss of a processing site.

Some of the functions of the Network Operating System are centralized the Global Computer. The Global Computer is responsible for system start, resource management, redundancy management, and function migration. It needs status knowledge of all processing sites and it must be able to command other GPCs to perform specific functions. This communication is accomplished via the Network Operating System, a portion of which is resident in each computer. The Global Computer does not participate in every system level transaction. Some of the system level functions performed by the Network Operating System may involve only a pair of nonglobal GPCs.

One of the GPCs is designated to be the Global Computer at the system bootstrap time. However, this designation can be changed during system operation by an internal or an external stimulus.

## 2.5 DATA BASE

Another important attribute of a distributed system is the treatment of the data base. The data base can be completely replicated in all subsystems or it can be partitioned among the subsystems. In addition, the data base directory can be centralized in one subsystem, duplicated in all subsystems, or partitioned among the subsystems. The AIPS approach is a combination of these.

For the mass memory data base, all GPCs will contain a directory of the MMU contents. This can be implemented as a 'directory to the directory' in order to limit the involvement of GPCs in the directory change process. The MMU directory will be static over extended intervals.

The data base that reflects the global system state will be maintain ed by the Global Computer in its local memory. A copy will be maintained by any alternate Global Computer, also in local memory.

The data base that reflects the distribution of functions among GPCs will be contained in all GPCs.

## 2.6 FAULT TOLERANCE

There is a considerable amount of hardware redundancy and complexity associated with each of the elements shown in Figure 1. This redundancy

allows each hardware element to be reliable, fault tolerant, and damage tolerant. From a software viewpoint, however, this underlying complexity of the system is transparent. This is true not only in the context of the applications programs but for most of the operating system as well; however, those elements of the operating system that are concerned with fault detection and recovery and other redundancy management functions have an intimate knowledge of the underlying complexity.

Hardware redundancy in the AIPS is implemented at a fairly high level, typically at the processor, memory, and bus level. There are two fundamental reasons for providing redundancy in the system: one, to detect faults through comparison of redundant results, and two, to continue system operation after component failures. Processors, memories, and buses are replicated to achieve a very high degree of reliability and fault tolerance. In some cases coded redundancy is used to detect faults and to provide backups more efficiently than would be possible with replication.

The redundant elements are always operated in tight synchronism which results in exact replication of computations and data. Fault detection coverage with this approach is one hundred per cent once a fault is manifested. To uncover latent faults, temporal and diagnostic checks are employed. Given the low probability of latent faults, the checks need not be run frequently.

Fault detection and masking are implemented in hardware, relieving the software from the burden of verifying the correct operation of the hardware. Fault isolation and reconfiguration are largely performed in software with some help from the hardware. This approach has flexibility in reassigning resources after failures are encountered, and yet it is not burdensome since isolation and reconfiguration procedures are rarely invoked.

## 2.7 DAMAGE TOLERANCE

One of the AIPS survivability related requirements is that the information processing system be able to tolerate those damage events that do not otherwise impair the inherent capability of the vehicle to fly, be it an aircraft or a spacecraft.

The requirement for damage tolerance will be applied to redundant GPCs, intercomputer communications, and to communication links between GPCs and sensors, effectors, and other vehicle subsystems.

The internal architecture of the redundant computers supports the damage tolerance requirement in several ways. The links between redundant channels of a computer are point-to-point. That is, each channel has a dedicated link to every other channel. Second, these links can be several meters long. This makes it possible to physically disperse redundant channels in the target vehicle. The channel interface hardware is such that long links do not pose a problem in synchronizing widely dispersed processors.

For communication between GPCs and between a GPC and I/O devices a damage and fault tolerant network is employed. The basic concept of the network is as follows.

The network consists of a number of full duplex links that are interconnected by circuit switched

nodes to form a conventional multiplex bus. In steady state, the network configuration is static and the circuit switched nodes pass information through them without the delays which are associated with packet switched networks. The protocols and operation of the network are identical to a multiplex bus. Every transmission by any subscriber on a node is heard by all the subscribers on all the nodes just as if they were all linked together by a linear bus.

The network performs exactly as a virtual bus. However, the network concept has many advantages over a bus. First of all, a single fault can disable only a small fraction of the virtual bus, typically a link connecting two nodes, or a node. The network is able to tolerate such faults due to a richness of interconnections between nodes. By reconfiguring the network around the faulty element, a new virtual bus is constructed. Except for such reconfigurations, the structure of the virtual bus remains static.

The nodes are sufficiently smart to recognize reconfiguration commands from the network manager which is one of the GPCs. The network manager can change the bus topology by sending appropriate reconfiguration commands to the affected nodes.

Second, weapons effect induced damage or other damage caused by electrical shorts, overheating, or localized fire would affect only subscribers in the damaged portion of the vehicle. The rest of the network, and the subscribers on it, can continue to operate normally. If the sensors and effectors are themselves physically dispersed for damage tolerance or other reasons and the damage event does not affect the inherent capability of the vehicle to continue to fly, then the control system would continue to function in a normal manner or in some degraded mode as determined by sensor/effector availability. The communication mechanism, that is, the network itself, would not be a reliability bottleneck.

Third, fault isolation is much easier in the network than in multiplex buses. For example, a remote terminal transmitting out of turn, a rather common failure mode, can be easily isolated in the network through a systematic search where one terminal is disabled at a time. This, in fact, is a standard algorithm for isolating faults in the network.

Fourth, the network can be expanded very easily by adding more nodes. In fact, nodes and subscribers to the new nodes (I/O devices or GPCs) can be added without shutting down the existing network. In bus systems, power to buses must be turned off before new subscribers or remote terminals can be added.

Finally, there are no topological constraints which might be encountered with linear or ring buses.

## 2.8 SOURCE CONGRUENCY

An important consideration in designing AIPS is the interface between redundant and simplex elements. This interface design is crucial in avoiding single point faults in a redundant system. One must perform source congruency operations on all simplex data coming into a redundant computer. It is not

sufficient to distribute simplex data to redundant elements in one step. The redundant elements must exchange their copy of the data with each other to make sure that every element has a congruent value of the simplex data. The AIPS architecture not only takes this requirement into account but also provides efficient ways of performing simplex source congruency through a mix of hardware and software. The simplex to redundant interface is also the place where the applications programmer gets involved in the processor redundancy and the applications code complexity multiplies. The AIPS processor level architecture is designed such that it separates the source congruency and computational tasks into two distinct functional areas. This reduces the applications code complexity and aids validation.

#### 2.9 MASS MEMORY

The mass memory in AIPS provides the following capabilities.

- 1. System Cold Start/Restart.

- 2. Function Migration Support.

- Overlays for local memory of General Purpose Computers.

- 4. System Table Backup.

- 5. Storage for system-wide common files.

- 6. Program Checkpointing.

## 3.0 PROOF-OF-CONCEPT SYSTEM

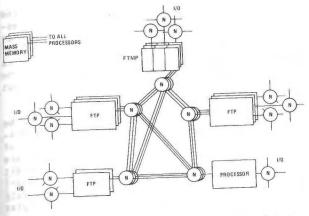

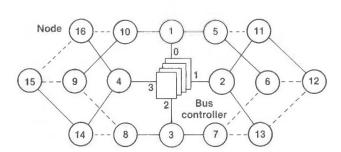

To demonstrate feasibility of the Advanced Information Processing System concept described in the preceding sections, a laboratory proof-of-concept system will be built. Such a system is now in the detailed design phase. The POC system configuration is shown in Figure 2. It consists of five processing sites which are interconnected by a triplex circuit switched network. Four of the five GPCs are uniprocessors, one simplex, one duplex, and two triplex processors. The fifth GPC is a multiprocessor that uses parallel hybrid redundancy. The redundant GPCs are to be built such that they can be physically dispersed for damage tolerance. Each of the redundant channels of a GPC could be as far as 5 meters from other channels of the same GPC.

Each of the triplex fault tolerant processors (FTPs) and the fault tolerant multiprocessor (FTMP) interfaces with three nodes of the Intercomputer (IC) node network. The duplex and the simplex processors interface with two and one nodes, respectively.

The mass memory is a highly encoded memory that interfaces with the GPCs on a triplex multiplex bus.

The Input/Output is mechanized using a 16 node circuit switched network that interfaces with each of the GPCs on 1 to 6 nodes depending on the GPC redundancy level.

Redundant system displays and controls are driven by the Global Computer and interface through the  ${\rm I/O}$  network.

Each GPC has a Local Operating System and a portion of the Network Operating System. For the proof-of-concept system, initially the FTMP will be

Figure 2. AIPS Proof-of-Concept System

Configuration

the Global Computer.

# 3.1 ARCHITECTURE OF AIPS BUILDING BLOCKS

Architecture of the major hardware building blocks of the AIPS Proof-of-Concept System configuration is described in the following sections.

## 3.1.1 Fault Tolerant Processor

The architectural description of the FTP is divided into three sections: Software View, Hardware View, and External Interfaces.

## 3.1.1.1 Fault Tolerant Processor: Software View

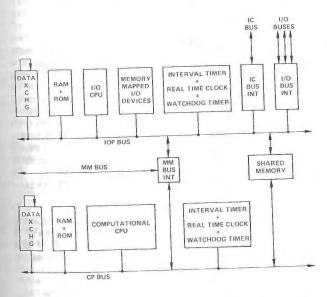

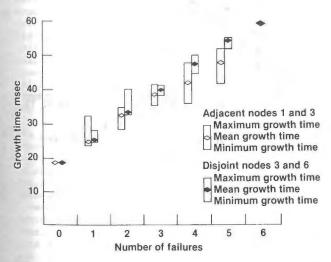

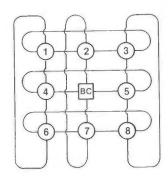

The FTP or the uniprocessor architecture from a software viewpoint appears as shown in Figure 3.

Figure 3. Fault Tolerant Processor

Architecture: Software View

The uniprocessor can be thought of as consisting of two separate and rather independent sections: the computational core and the Input/Output channel.

The computational core has a conventional processor architecture. It has a CPU, memory (RAM and ROM), a Real Time Clock, and interval timer(s). The Real Time Clock counts up and can be read as a memory location (a pair of words) on the CP bus. Interval timers are used to time intervals for scheduling tasks and keeping time-out limits on applications tasks (task watchdog timers). An interval timer can be loaded with a given value which it immediately starts counting down and when the counter has been decremented to zero, the CPU is interrupted with a timer interrupt. A watchdog timer is provided to increase fault coverage and to fail-safe in case of hardware or software malfunctions. The watchdog timer resets the processor and disables all its outputs if the timer is not reset periodically. The watchdog timer is mechanized independently of the basic processor timing circuitry.

There also appears on the processor bus a set of registers, called the data exchange registers. These are used in the redundant fault tolerant processor to exchange data amongst redundant processors. From a software viewpoint, this is the only form in which hardware redundancy is manifested.

On a routine basis the only data that needs to be exchanged consists of error latches and cross channel comparisons of results for fault detection. These operations can be easily confined to the program responsible for Fault Detection, Isolation, and Reconfiguration. Voting of the results of the redundant computational processors is performed by the Input/Output processors. Therefore, the remaining pieces of the Operating System software and the applications programs need not be aware of the existence of the data exchange registers. The task scheduler and dispatcher, for example, can view the computational core as a single reliable processor.

The other half of the processor is the Input/Output channel. The I/O channel has a CPU (same instruction set architecture as the CP), memory (RAM and ROM), a Real Time Clock, and an Interval Timer (s). This part of the I/O channel is identical to the CP except that it has less memory than the CP.

The IOP has interfaces to the intercomputer bus, one or more I/O buses, and memory mapped I/O devices. The CP and the IOP also have a shared interface to the system mass memory. These external interfaces of the FTP will be discussed in the next two sections.

The IOP and CP exchange data through a shared memory. The IOP and CP have independent operating systems that cooperate to assure that the sensor values and other data from Input devices is made available to the control laws and other applications programs running in the CP in a timely and orderly fashion. Similarly, the two processors cooperate on the outgoing information so that the actuators and other output devices receive commands at appropriate times. This is necessary to minimize the transport lag for closed loop control functions such as flight control and structural control.

The CP and IOP actions are therefore synchronized to some extent. To help achieve this synchronization in software, a hardware feature has been provided. This feature enables one processor to interrupt the other processor. By writing to a reserved address in shared memory the CP can interrupt the IOP and by writing to another reserved location the IOP can interrupt the CP. Different

meanings can be assigned to this interrupt by leaving an appropriate message, consisting of commands and/or data, in some other predefined part of the shared memory just before the cross-processor interrupt is asserted.

For routine flow of information in both directions, the shared memory will be used without interrupts but with suitable locking semaphores to pass a consistent set of data. The interrupts can be used to synchronize this activity as well as to pass time critical data that must meet tight response time requirements. In order to assure data consistency it is necessary that while one side is updating a block of data the other side does not access that block of data. This can either be implemented through semaphores in software or through double buffering. Hardware support for semaphores, in the form of test & set instruction, is provided in the IOPs and CPs.

There are many attractive features of this architecture from an operational viewpoint. The most important of these is the decoupling of computational stream and the input/output stream of transactions. The computational processor is totally unburdened from having to do any I/O transaction. To the CP all I/O appears memory mapped. And this not only includes I/O devices but also all other computers in the system as well. That is, each sensor, actuator, switch, computer, etc. to which the FTP interfaces can simply be addressed by writing to a word or words in the shared memory.

Data from other processing sites is received by each IOP on the redundant IC buses, hardware voted, and then deposited in their respective shared memories. Simplex source data such as that from I/O devices, local processors, etc. is received by the single I/O processor that is connected to the target device. This data is then sent to the other two I/O processors using the IOP data exchange hardware. The congruent data is then deposited in all three shared memory modules. In either case, the computational processors obtain all data from outside that has already been processed for faults and source congruency requirements by the I/O processors.

The data exchange mechanism appears to the software as a set of registers on the processor bus. Data exchange between redundant processors takes place one word at a time. Two types of data exchanges are possible: a simplex exchange or a voted exchange. The purpose of a simplex exchange is to distribute congruent copies of data that is available only in one channel of the FTP to all other channels. The purpose of a voted exchange is to compare and vote computational results produced by redundant processors. In the FTP architecture, these exchanges are mechanized as follows.

To perform a voted exchange, each processor writes the value to be voted in a transmit register called X\_V. Writing to this register initiates a sequence of events in hardware which culminates with the voted value being deposited in the receive register of each processor. The processor can read the receive register at this point to fetch the voted value. The whole transaction takes of the order of 5 microseconds. The hardware is designed to lock out access to the receive register while the exchange is in progress. If the processor tries to read the receive register before the transaction has completed, the processor hangs up. As soon as the data

becomes available, the processor is released and the register read cycle completes normally. The processor wait is transparent to the software. It is not necessary to time the interval between writing of the transmit register and reading of the receive register in software. The two operations can be performed as a sequence of two instructions without an intermediate wait.

To perform a simplex exchange, the data to be transmitted is written to one of the simplex transmit registers. In the triple redundant version of the FTP there are three such registers. They are called X\_A, X\_B, and X\_C. X\_A is used to transmit simplex data from channel A to all others. Similarly X\_B transmits data from B and X\_C transmits data from C. Writing to one of these registers initiates a sequence of events in hardware which culminates with a congruent copy of the data word being deposited in the receive register of each processor. The receive register can be read at this point by each processor to fetch the congruent copy of the simplex data.

It has been pointed out earlier that the software appearance of the redundant FTP is the same as that of a simplex processor. All redundant processors have identical software and execute identical instructions at all times. This architecture is carried forth in the data exchange hardware and software as well. The data exchange hardware is designed such that all redundant processors execute identical instructions when exchanging data. As an example, consider a simplex source transmission from channel A. Assume that channel A has a sensor value in its internal memory location, called MEMORY, that it needs to send to channels B and C. This requires execution of the following sequence of four instructions:

1 LOAD RO, MEMORY 2 STORE RO, X\_A 3 LOAD RO, X\_R 4 STORE RO, MEMORY

The data to be transmitted is fetched from memory (instruction 1) and written to transmit register X\_A (instruction 2). All three processors execute these instructions. However, only processor A's value is transmitted to the receive register of A, B, and C. Transmissions from B and C are ignored by the hardware. This will be explained in the next section which deals with the FTP architecture from a hardware viewpoint. In instruction 3 all processors read their receive register (X\_R) to accept the congruent value of the data transmitted by A. In instruction 4 this value is transferred to an internal memory location.

Voted data exchange requires a similar sequence of instructions. The only difference is that in instruction 2, rather than storing the value in one of the simplex transmit registers, it is stored in the voted exchange register, X\_V.

## 3.1.1.2 Fault Tolerant Processor: Hardware View

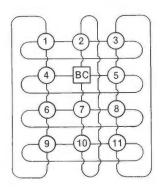

The triplex FTP architecture from a hardware view-point appears as shown in Figure 4.

There are three identical hardware channels. Each channel has a computational processor, an I/O processor, and some hardware that is shared by the CP and the IOP. The internal details of the CP and the IOP such as the CPU, memory, timers, etc., have

Figure 4. Fault Tolerant Processor

Architecture: Hardware View

been described in the preceding section. They are not shown in Figure 4 so that other details such as the redundancy dimension be shown more clearly.

The common hardware consists of a shared memory, the data exchange registers, and the mass memory interface. The shared memory is used exchange information between the CP and the IOP while the data exchange registers are used to exchange information between redundant copies of the CP or IOP. Common hardware access conflicts between the CP and the IOP are resolved by a bus arbitrator. The bus arbitration logic is designed such that each channel resolves the conflict in favor of the same processor (that is, either the IOP or the CP) deterministically. This is necessary to maintain tight synchronism between redundant copies of processors. This is only one of several conditions necessary for synchronous operation. Stated in more general terms, two hardware conditions are necessary. First of all there should be a common time base that is used by all channels for timing events. Second, all timing events should be deterministic in nature. If these two hardware conditions are met, the redundant channels can be synchronized. Once they are synchronized, they will stay synchronized if all channels execute identical software.

To obtain a common time base, the oscillators in redundant channels are phase locked to each other. To assure that all timing events are deterministic, it is necessary to use a synchronous bus internal to each processor. As an example, when a CPU references a memory location on the bus the memory cycle should complete in a fixed time interval. This does not necessarily imply that all memory cycles should take the same time. It is possible in the FTP architecture to mix different types of memories, such as PROM and RAM, which may have different access times. The only necessary condition is that access to a given location always take the same length of time. This also applies to any I/O activity performed by the processor. The hardware is built such that when a processor accesses a device available in only one channel the other processors wait the same length of time.

A very important aspect of the FTP architecture is the interconnection hardware between redundant channels. This hardware serves three purposes. First of all, it provides a path for distributing simplex data available in only one channel to all other channels. Second, it provides a mechanism for comparing results of the redundant channels. And third, it provides a path for distributing and comparing timing and control signals such as the fault tolerant clock and external interrupts.

To distribute simplex data from one channel to all others without introducing single point faults in the design, it is necessary to adhere to source congruency requirements. One of these dictates that in order to tolerate single faults it is necessary to provide four fault containment regions. In the triplex FTP architecture six fault containment regions are provided. The triplex processor provides the basic three fault containment regions. Three additional regions are provided in the form of interstages which receive data from processors and rebroadcast them back to processors. The interstages are mechanized such that they have independent voltage and timing reference. This assures that faults in processors would not propogate to interstages and vice versa. Since an interstage is essentially a buffer with receivers and transmitters, it is relatively a small and simple piece of electronics. It is, therefore, much more convenient to provide three additional fault containment regions rather than just one as required for source congruency. It also makes the FTP architecture symmetric.

As explained in the preceding section, the data exchange hardware appears as a set of five registers on the processor bus. Four of these (X\_A, X\_B, X\_C, and X\_V) are the transmit registers and the fifth one is the receive register,  $X\_R$ . For simplex source exchanges, say, a 'from A' exchange, data in X\_A register in channel A is transmitted to the three interstages. The interstages rebroadcast this data to every processor. The three copies received by each processor are voted in hardware on a bit-by-bit basis. The voted result is deposited in X\_R. for voted exchanges, each channel writes the data to be voted in X V register. Writing to X V results in the data being transmitted to the channel's own interstage. The second half of the operation is the same as for simplex exchange. In both cases, the exchange hardware masks any single faults while voting on three copies and also records the source of fault in an error latch. The error latch can be read by software as a memory location.

# 3.1.1.3 Fault Tolerant Processor: External Interfaces

The external devices that interface with the FTP are the mass memory, the Intercomputer network, and the  $\rm I/O$  network.

Figure 4 shows the interface between a triplex FTP and the triply redundant mass memory bus. This interface hardware is shared in each channel by the CP and the IOP. Each channel of the FTP is enabled on one of the three buses. The FTP transmits commands and data synchronously on three buses to the mass memory where they are received and voted in hardware. The interface hardware performs the necessary parallel to serial data conversion, appends cyclic redundancy check byte (CRC), and transmits serial data on the bus. Each processor channel listens to all three mass memory buses. Data received

from the mass memory is voted in hardware on a bit-by-bit basis. Any disagreements on the mass memory bus are recorded in error latches for later analyis by software. Any CRC failures are also recorded separately. Voted data is then converted from serial to parallel format.

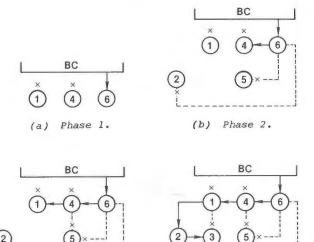

Figure 5 shows the interface between a triplex FTP and the triply redundant Intercomputer Network.

Figure 5. FTP Interface to IC and I/O Networks

The IC network interface is dedicated to the I/O processor. Other than that, it is very much like the mass memory interface. Each IOP listens to all three IC networks but can transmit on only one IC network. The IC network interface circuitry is responsible for parallel to serial data conversion, resolving network contention, and transmitting data on the network. In the other direction, the network interface hardware listens to three bit streams, deskews them, votes and masks single faults and converts the voted bit stream from serial to parallel. It stores any disagreements on the networks in error latches or registers. Non compliance with the network protocol is also recorded separately for each of the three networks.

An IOP also interfaces to one or more I/O networks. This interface is different from the IC network interface to the extent that the I/O networks may not be redundant. Redundant I/O networks interface with the FTP the same way as the IC network nodes. For simplex I/O networks, it is necessary that when the processor is communicating with an I/O device all other processors execute the same software and wait identical lengths of time to stay synchronized. Also, any data received from the I/O devices must be distributed to all other processors using the data exchange registers. Although an I/O network may not be redundant, an FTP may have more than one connection to an I/O network through multiple IOPs.

An I/O network may be dedicated so that only those I/O devices that are used solely by this FTP are on this network. Or the I/O network may be a shared network that connects multiple computers to shared I/O devices.

Finally, an IOP may also have local dedicated I/O devices that can be accessed directly by the IOP as memory locations. The memory mapped I/O may consist of local switches, discretes, A/Ds, D/As and interrupt driven devices. This interface differs from dedicated I/O bus interface in the sense that I/O signals on the bus may be already conditioned and processed by a local processor and the IOP

interfaces through this bus to the local processor which may control a number of I/O devices.

Although it is possible to interface interrupt driven I/O devices to the IOPs, none will be included in the proof-of-concept system.

An IOP may transmit on an IC bus, a shared I/O bus, or a dedicated I/O bus only if it is enabled to do so by a majority of the IOPs. An IOP can also disable itself any time.

The interface of an FTP to the IC buses is somewhat different if the FTP redundancy level is not the same as the IC redundancy level. For example, if the FTP is a duplex system rather than a triplex then there will be only two IOPs, one IOP per channel. Each IOP will listen to and vote on all three IC buses and it will transmit on one IC bus. Transmissions from duplex processors will, therefore, be heard only on two out of three buses. Similarly, simplex processors will listen to all buses but will transmit on only one bus. Voting logic in the bus interface circuits is suppressed when the transmitting processor is simplex. It is necessary to rely on compliance with bus protocol to detect errors.

The next topic of discussion is the interface of the system in degraded mode. The FTP can degrade in 3 ways, failure of an IOP, failure of a CP, and the failure of the shared hardware.

When an IOP fails, the IC bus interface would degrade from triplex to a duplex configuration. Each of the other two IOPs would listen to all three IC buses but transmissions from this FTP would be heard by other computers only on two buses. At the receiving sites fault masking would be replaced by fault detection. Since there is some inherent coded redundancy in data being transmitted on each bus, one can hope to identify the second fault with fairly high coverage. This would normally be the case when communicating to a dual-redundant computer on the network under normal circumstances.

The other effect of the failure of an I/O processor is the loss of I/O devices attached to that processor. Actually only those I/O devices that were connected only to the failed processor would be lost. If the I/O devices are cross-strapped to other IOPs through the I/O bus, for example, they would still be accessible via the other I/O processors.

Finally, the loss of an IOP also means that the CP attached to that IOP does not have access to any inputs. In other words, failure of any element in a channel can be considered the same as failure of the whole channel. That is, if an IOP, a DPM or a CP fails in a channel one could shut down all the elements in that channel of the FTP. Although this is the most convenient way to operate the system from a system software viewpoint, one can use more sophisticated strategies to obtain reliability from the system. This, however, is achieved at the expense of more complex system software.

Specifically, if an IOP fails then the corresponding CP loses access to data being provided by that IOP through the shared memory. But since the CPs are cross-strapped to each other through data exchange hardware it is possible to provide the target CP the voted value of the inputs to the other two CPs. The same can be done on the IOP side when a CP fails. If the shared memory fails either side can get around the fault by cross-exchanging data. This

will be the POC system operational strategy.

## 3.1.2 Fault Tolerant Multiprocessor

The following two sections describe the software appearance of the multiprocessor and the redundancy and fault tolerance dimension of the machine, respectively.

## 3.1.2.1 Multiprocessor Software Appearance

The multiprocessor discussion is divided into three parts: processors, shared memory, and the external interfaces. These three parts are discussed in the following sections.

3.1.2.1.1 PROCESSORS The multiprocessor architecture from a software viewpoint appears as shown in Figure 6. This figure does not show the redundancy dimension of the computer .: FTMP, from a software viewpoint, appears as a conventional, homogeneous multiprocessor. There are a number of processing elements that have access to a common memory, called the shared memory. Each processor has a local memory which is composed of Read Only Memory (ROM) and Read/Write Memory. Although not all of the programs are always resident in the local memory, they must be loaded there from the shared memory before they can be executed. The local PROM is used to hold the bootstrap loader, cold start and restart programs, frequently executed parts of the operating system, and high frequency applications programs. All other programs are loaded into the RAM on a demand basis.

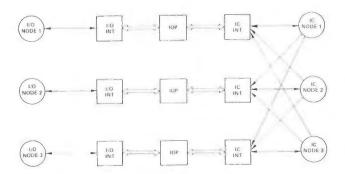

Figure 6. FTMP Architecture: A Software View

Each processor has internal interval timer(s) that can be set to any 16-bit value under program control. The interval timer decrements this count and interrupts the processor when the count reaches zero. Interval timers can be used for scheduling highest frequency tasks and also as task watchdog timers.

Communication between processors can be via the shared memory or it can be via Interprocessor Communication (IPC) Buffers. The shared memory path is the slower of the two paths. The sender can write the message in the shared memory, but it does not arrive at its destination until the receiving processor reads its mail box. An alternative to this is the IPC Buffer. A processor can write to any other processor's buffer. The receiving processor is interrupted when one of the buffer locations is written into. The receiving processor's IPC Interrupt Handler can then read the message in its buff-

er. The buffer length is of the order of 16 words. That is, it is not a large memory array. For large data transfers, shared memory would still be used although one could pass a shared memory pointer using the IPC mechanism.

3.1.2.1.2 SHARED MEMORY: The shared memory can be accessed by the processors using the multiprocessor bus. Contention for the bus amongst multiple processors is resolved in hardware. The hardware also provides the capability to test and set a word in the shared memory in a single atomic operation. Access to data elements that are shared amongst multiple processes can be limited to one process at a time by associating a lock or semaphore with each shared data set.

Although the shared memory appears as a single monolithic unit to the software, it should be noted here that it is, in fact, composed of several segments. Such a segmented shared memory, coupled with dedicated buses from processors to memory units, makes it appear as a multiported memory. All segments of the shared memory can be accessed simultaneously if different processors happen to request access to different segments. This feature should be taken into account when locking data sets in the shared memory.

There are several other elements of the multiprocessor that can be accessed by the processors using the memory bus. One of these is the Real Time Clock (RTC). The Real Time Clock is a 32-bit counter that counts up. The RTC can be set to a given value by writing to its 'memory' address. It can be read as a two word value on the memory bus also. Reading the high order word automatically latches the low order word so that the 32-bit value of the RTC is read as a consistent set.

IPC buffers also appear as shared memory addresses as far as write operations are concerned. They can only be written to on the multiprocessor bus. They can be read only by the host processor on the internal processor bus.

Other registers in the shared memory address space can be grouped under the heading of Multi-processor Control Registers. Their functions include:

- Memory Relocation (Write Only): This assigns a shared memory module to a given address space.

- Triad Identification (Write Only on multiprocessor bus, Read Only on processor bus): This assigns a processor to a triad.

- CPU Control (Write Only on multiprocessor bus, Read Only on processor bus): This controls various CPU operations such as reset, go, etc.

- Bus Selection (Write Only on multiprocessor bus): This tells each processor and memory which buses to listen to.

- Error Latch (Read Only on system bus): It records disagreements on the multiprocessor bus.

3.1.2.1.3 EXTERNAL INTERFACES: External interfaces of the FTMP consist of interfaces to other

GPCs through IC nodes, interface to I/O devices through I/O nodes, and interface to Mass Memory through Mass Memory buses. Not all FTMP processors have all external interfaces. Some processors may, in fact, have none of these interfaces. These processors perform only computational function in the FTMP.

At any given time, one processor triad is assigned to communicate on the IC network. Bus interface hardware performs a bit by bit majority vote on incoming redundant data. Each processor then should have an identical copy of the incoming data. For simplex data, the voting is bypassed and it is necessary to perform source congruency. This is done by simply writing the simplex data into shared memory. Voters in the shared memory perform majority voting on three copies of the word received from the three processors. The voted data then becomes the congruent value of the simplex word.

Mass memory interface is functionally identical to the IC network interface.

The FTMP also has interfaces to one or more I/O networks. The I/O networks may or may not be redundant. One of the processor triads, with approriate I/O interfaces, is assigned to the task of managing I/O devices.

# 3.1.2.2 Multiprocessor Redundancy & Fault Tolerance Features

As alluded to in the previous section, there is a considerable amount of complexity in the hardware that is largely transparent to the software but is responsible for making the machine fault tolerant. This complexity arises from two related features of the multiprocessor. One, every element in the system is replicated to some level. Every major element is at least triplicated, and some have even a higher level of redundancy. Two, all redundant operations must be compared to detect faults and to mask faults where appropriate. The fault detection and masking requires considerable amount of interconnections between redundant elements. These two attributes of the machine, viz., redundancy and intercommunication, are largely responsible for the multiprocessor complexity.

However, the redundant hardware elements are organized in such a fashion that this complexity is not carried over into the software. In fact, the other attribute of the machine, viz., the interconnection of the redundant elements, is what makes the hardware complexity transparent to the user. This should become clearer as the hardware architecture is described in the following sections.

3.1.2.2.1 PROCESSORS: Processor in the multiprocessor, CPs or IOPs, operate in groups of three, called triads. The three members of a triad are tightly synchronized using a fault tolerant clock. (The clock operation is described in another section.) Processor organization is such that any three processors can be formed into a triad with some exceptions such as the constraints that may be introduced by packaging and external bus interface considerations. Other than these constraints, a processor element can be used as a member of a CP triad or an IOP triad. A processor may be a member of a CP triad at one time and it may be a member of an IOP triad at some other time.

Once all the available processors have been

formed into CP and IOP triads, the remaining processors (spares), can be used to 'shadow' normally operating triad members. A shadow processor is tightly synchronized with the three active members of the triad and executes the same instructions as the active members. It listens to all the buses to obtain the same input data as the active members. However, it is not enabled to transmit on any bus.

Each processor has a number of control registers which are either processor specific or triad specific. All of these registers have a 'Write To' address that is an extension of the shared memory address space. They also have a 'Read From' address that is an extension of the processor's local memory address space. An example of a triad specific register is the IPC (Interprocessor Communication) Buffer. An example of a processor specific register is the Triad Identification (ID) Register. Addresses of processor specific registers have a Processor ID field in the 'Write To' address. Addresses of triad specific registers have a Triad ID field in the 'Write To' address.

There are a number of other system control and status registers that are accessed in a manner similar to the processor control registers. Examples of these will be given where relevant.

3.1.2.2.2 SHARED MEMORY: The shared memory in the multiprocessor is triplicated and operates as one contiguous triad. Physically, it is partitioned into several smaller segments and the level of replication is at the segment level. A processor and a shared memory segment are packaged together in a box or Line Replaceable Unit (LRU). They share such items as the fault tolerant clock, LRU power supply, etc.

Associated with each memory segment is a Memory Relocation Register (MRR). This register is analogous to the Processor Triad ID Register in that it allows one to identify the memory triad to which a memory module belongs. The MRR forms the high order part of the address to which the associated memory module responds. The MRR itself has an LRU specific address and can be written to on the multiprocessor bus. Thus, one can group any three memory modules to form a shared memory triad by relocating them to the same address space.

3.1.2.2.3 PROCESSOR-MEMORY INTERFACE: The processors and shared memory segments are fully cross-strapped. Each box or LRU containing a processor and a shared memory is connected to every other LRU using dedicated buses. The processor-shared memory communication works as follows.

Assume there are N LRUs in the multiprocessor. When a processor triad wishes to write shared memory, each member broadcasts appropriate address, data, and commands on its transmit bus. Each member of the target memory triad receives three copies of address, etc. It selects 3-out-of-N transmit buses to listen to this processor triad using information from Bus Select registers. The three copies are then voted by each member of the memory triad and appropriate action (such as storing the data) taken. Any disagreements are latched in the Processor Error Latches indicating the identity of the disagreeing processor.

For a memory read operation, the first half of the transaction is similar to the write operation.

Each member of the memory triad broadcasts the data to the three requesting processors. Each processor in the requesting triad then receives three copies of the data which it votes in hardware and also latches identity of any disagreeing memory unit in its Memory Error Latch.

As indicated earlier there are a number of multiprocessor control and status registers. More examples of these have now been cited (MRR, Error Latches, Bus Select Registers). These registers are assigned addresses in an extended shared memory address space. They can be accessed by any processor triad just as if they were shared memory locations. The interface hardware to select Transmit Buses, vote on incoming processor requests, etc. can be the same hardware that is used to access the shared memory in a given LRU. This not only saves hardware but also makes use of the existing processor-memory 'bus' that cross-straps all LRUs. In fact, this same communication medium can be used to write to the Interprocessor Communication Buffers. Such an arrangement also makes the software appearance of the machine rather straightforward.

3.1.2.2.4 FTMP CLOCKING: The tight synchronization between processor elements is maintained using standard fault tolerant clocking techniques (analog phase locked loop or digital compensation) developed previously. The multiprocessor fault tolerant clock functions as follows.

Each processor and shared memory in every LRU has a common oscillator. Four of these oscillators, called the active elements, are chosen to form the quad-redundant fault tolerant clock. (Four clock elements are necessary to tolerate all single point clock failures). Any four operating oscillators can be chosen as active elements. The active clocks are distributed to every processor and memory LRU in the system. Each active element listens to the other three active clocks and locks itself to the majority. The nonactive clocks phase lock to any three out of four active clocks. If an active elements fails, it is replaced by a previously inactive element. In other words, every clock is sent to every LRU in the system. Since the basic philosophy is to have dedicated paths rather than multiplex buses, there is a dedicated clock bus that goes from every LRU in the system to every other LRU.

Each LRU in effect listens to three active elements and synchronizes itself to the majority. This clock is then used for all internal timing events such as processor clocking, memory clocking, decrementing of the interval timer, and incrementing of the real time clock.

The real time clock is a 32-bit counter. Such a counter exists in every LRU and is accessible on the system memory bus. Real time clocks in all the LRUs respond to the same system memory address. RTC counters always respond to write (or set) requests. Thus all the real time clocks in the FTMP can be set to a given time simultaneously. Once set, they all count up at the same rate since they are clocked by the fault tolerant clock. During normal operation, three of the counters are selected to be active. There is an RTC Select Register in every LRU that determines which three RTCs to listen to. When one of the counters fails, it is replaced by another operating RTC counter by updating all RTC Select Registers in all LRUs.

3.1.2.2.5 EXTERNAL INTERFACES: The multiprocessor interfaces to the external world through three different types of buses. Interface to other General Purpose Computers is via the IC network. Interface to the I/O devices is via the I/O network. And interface to the Mass Memory is via the MM bus.

The IC network is triply redundant and consists of three layers of a circuit switched node network. Three of these nodes, one from each layer, interface with the multiprocessor. On the multiprocessor side one processor triad interfaces with the triplex IC network (also referred to as the IC bus) at any given time. For data transmission, each member of this triad (called the IC triad) transmits on one bus. For receiving data, each IC triad processor listens to all three IC buses, deskews the data and votes on the three copies in hardware. Any bus disagreements trigger IC Error Latches in the processor-bus interface hardware. The identity of the disagreeing bus is stored in the Error Latch. Before performing bit by bit voting on incoming data, each serial data stream is checked for compliance with the bus protocol. Any deviations are recorded in error registers. The error latches and the protocol error registers can be read by a processor triad on the multiprocessor bus. If the data source GPC is not redundant, then voting circuitry is bypassed. Simplex source congruency is performed on the incoming data by writing it to shared memory and reading it back again. Since the IC bus is a contention bus, the FTMP contends for access to the bus with the other GPCs using a distributed arbitration algorithm known as the Laning Poll. One of the FTMP triads that is enabled on the IC bus participates in this poll.

The I/O bus is a single layer, circuit switched network. At any given time, one processor triad (called the IOP triad) is assigned to interface with the I/O network. The IOP triad operates in a fashion similar to the IC triad. However, there is one major difference in that only one IOP processor transmits on the I/O bus at any given time. All three I/O processors listen to the I/O bus and perform source congruency on all incoming data by writing it to the shared memory. Since the I/O bus is a contention bus, they all participate in the bus arbitration by each member listening to the bus but only one of them actually transmitting on the bus. Laning Poll is used to arbitrate I/O bus conflicts.

Interface to the mass memory triplex bus is very much similar to the IC bus interface.

The transmissions from a processor on the IC, I/O and MM buses are gated through enabling gates. The purpose of the enabling gates is to protect the buses from runaway processors that can not otherwise be turned off. The enabling gates allow a processor to transmit only if a majority of the processors agree to do so. Each processor sends an enabling signal to every other processor. These enabling signals are voted upon to create a master enable signal in each LRU. If the multiprocessor is built with some slots initially unoccupied, the master enable signal is created by voting enable signals from only those processors which are present. Each LRU also produces a presence signal to indicate whether it is populated. The presence signal is also helpful in writing FDIR software and therefore should be made available as part of some LRU specific control register.

#### 3.1.3 IC and I/O Networks

The circuit switched nodes of the IC and the I/O networks are identical. For the proof-of-concept system each node will have five identical ports. The node will interface with other nodes, GPCs, and I/O subscribers (displays etc.) through these ports. All ports will be identical in terms of their ability to interface with any of the aforementioned entities.

The Intercomputer communication network for the proof-of-concept system configuration consists of three identical layers of a circuit switched network. Each layer consists of five nodes. Each node services one GPC. Although it is possible to service several GPCs from one node provided the node has enough ports to do this, this is not the case for the POC system configuration.

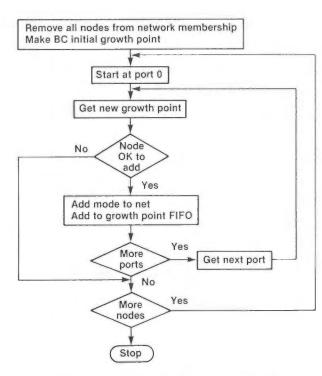

The three layers of the IC network are totally independent and are not cross-strapped to each other. The initial no-fault configuration of the three layers is identical although it does not have to be so. That is, after a link failure in one layer the virtual bus configuration of that layer would change as the network is reconfigured around the failed link. The other two layers do not have to be reconfigured to make their virtual bus path identical to the third one. The fault detection, isolation, and reconfiguration of the IC network are the responsibility of the Global Computer. Nodes keep track of any transmission errors which are protocol related and inform the Global of these errors when queried by the Global. This error data is analyzed by the Global to determine source of transient faults on the network. The nodes also respond to status queries with the status of the node and the ports. Other than this, the nodes are totally passive circuit switching devices. They listen for node reconfiguration commands from all ports whether or not that port is active. Valid reconfiguration commands must be preceded by a Gateman code. Reconfiguration commands are addressed to individual nodes although they are heard by all nodes.

The principles of operation of the I/O network are same as that of the IC network. The I/O network configuration for the POC system consists of a single layer of 16 nodes. This network can be configured either as a single global I/O network or as several regional I/O networks. Both configurations will be used in the POC system to demonstrate the global and regional I/O bus features of the AIPS system. System displays and controls would be attached to the I/O nodes.

## 3.1.4 Mass Memory

The AIPS proof-of-concept system mass memory requirements can be satisfied by Winchester disks, magnetic bubble memory, or Electrically Erasable ROM (EEROM) semiconductor memory. The choice will be made during preliminary design. The mass memory redundancy scheme will depend on this choice. If the decision is to use the disk or the magnetic bubble memory the memory will be replicated. Each copy will interface to the triplex mass memory bus through its own bus interface circuitry. The interface will be responsible for receiving redundant commands, address, and data from GPCs and performing deskewing, voting, and fault detection on the incoming data. Voted data will be stored in the memory.

Each interface would also respond to the memory read requests on one of the three mass memory buses. If the memory is implemented as EEROM, the fault tolerance will be provided through encoding rather than triplication.

The mass memory interfaces will restrict access to mass memory by simplex GPCs to read-only operations. A 'Mass Memory bus hog' capability will also be provided in support of semaphores or locks associated with shared data in the mass memory. A GPC will be able to retain control of the MM bus, after gaining access to it, for multiple memory transactions. One can read a memory location, modify it, and write it back as a single atomic operation.

## 4.0 SUMMARY

An advanced information processing architecture has been defined for a broad range of aerospace vehicles. It is highly fault tolerant and damage tolerant and has a number of other desirable attributes such as graceful degradation, growth, and an ability to accept technology upgrade. A proof-of-concept configuration is in detailed design phase. This will be followed by fabrication, programming, test and evaluation phases to prove key AIPS concepts.

#### LIST OF REFERENCES

- AIPS System Requirements, Report CSDL-AIPS-83-50, C. S. Draper Laboratory, Cambridge, MA, August 1983.

- AIPS System Specification, Report CSDL-C-5709,

C. S. Draper Laboratory, Cambridge, MA, May 1984.

- Philip H. Enslow, Jr., "Distributed Data Processing What Is It?", AGARD-CP-303, ISBN 92-835-0302-3, AGARD Conference Proceedings #303, Norway, 22-25 June 1981.

#### ACKNOWLEDGEMENT

This report was prepared by The Charles Stark Draper Laboratory, Inc. under Contract NAS9-16023, Task Order #84-18, with the Lyndon B. Johnson Space Center of the National Aeronautics and Space Administration. Publication of this report does not constitute approval by the NASA/JSC of the findings or conclusions contained herein. It is published for the exchange and stimulation of ideas.

Ellis F. Hitt\*, and Jeffrey J. Webb\*\*

Battelle Columbus Laboratories

Electronics Department

505 King Avenue

Columbus, Ohio 43201

## Abstract

Fault-tolerant software techniques discussed in this paper are the subject of research at many universities and industry. The research is directed toward further development and enhancement of the known techniques, such as recovery blocks and multi-version programming, development of tools for implementing fault-tolerant software techniques, and development of new techniques. The sources of software faults are described. Descriptions of the primary techniques are followed by an assessment of the current state-of-the-art of fault-tolerant software. Research needed to further the development and application of fault-tolerant software is discussed.

#### Introduction

Fault-tolerant software techniques have been the subject of research for the past decade since it became apparent that the cost and time required to produce fault-free software for complex systems using conventional development and testing methods still did not result in software completely free of faults. Fault-tolerant software design techniques have been developed to be used in the design and development of software and hardware required for implementing the techniques. A software fault is defined as a design defect in the software, where the term "design defect" encompasses all deficiencies introduced during the software life cycle.

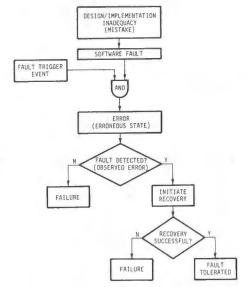

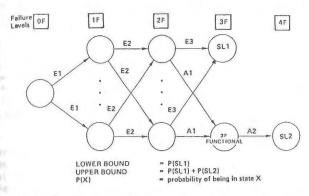

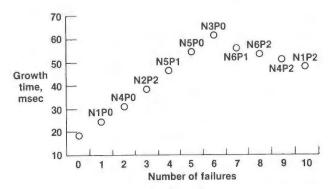

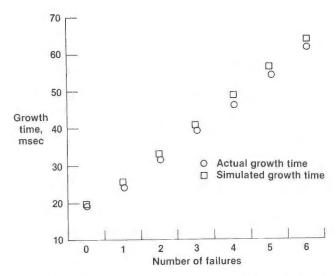

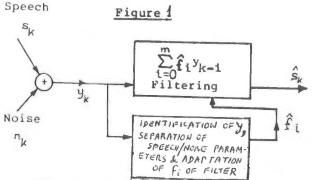

The software faults which the fault-tolerant software is to detect and recover from may be due to incorrect specification, incorrect algorithm, incorrect logic, coding and other mistakes. Manifestation of the software fault places the system in an erroneous state which may cause the system to fail. A failure occurs whenever the external behavior of a system does not conform to that prescribed by the system specifications (1). Figure 1 represents the relationship between fault-tolerant software events.

Software fault tolerance is the ability of a system to provide uninterruptible operation in the presence of software faults through multiple implementations (i.e., redundancy) of a given functional process.

## Background

It is extremely expensive to produce fault-free software. The primary methods used to attempt to produce fault-free software are based upon the principles of structured design and programming followed by extensive testing. One of the problems with this approach is that of determining when all of the software faults have been found and corrected so that the software can be

FIGURE 1. FAULT TOLERANT SOFTWARE EVENT RELATIONSHIPS

delivered and put into operational use. Many attempts have been made to develop a model which can be applied to the software and results gathered from tests to estimate and measure the number of faults remaining in the program. These attempts have resulted in most models being

immediately subjected to criticism since they do not fit a software development effort other than the specific one from which the data was collected to demonstrate the model. Nevertheless, model development efforts continue and are being made a part of formal software quality assurance programs (2,3).

To date, software faults are still being found in operational digital systems developed using the methods described in the previous paragraph. Consequently, operational phase software maintenance has become a fact of life with significant effort required for locating and correcting residual software faults still present from the development phase as contrasted with the effort devoted to the addition of new functions. In the process of removing the residual software faults, additional faults are often introduced which cause a repeat of the fault location and correction steps in a seemingly endless process. If it were truly possible to produce fault-free software, the operational phase effort could be completely devoted to the addition of software implemented functions required by changes in the operational mission requirements. Unfortunately, this is not the case today.

<sup>\*</sup>Projects Manager, \*\*Research Scientist, Member of the IEEE

Copyright © American Institute of Aeronautics and Astronautics, Inc., 1984. All rights reserved.

## Statement of the Problem/Requirements

Software faults exist and are manifested as errors. The effort required for locating and correcting these errors has resulted in high software life cycle costs. Software life cycle costs must be controlled and even reduced and reliability increased.

Software must not cause loss of life, vehicle, or systems functions in real-time digital systems. Software must provide the functions needed to safely accomplish the mission at all times. In order to meet this requirement while minimizing software life cycle costs, new approaches to software development and new tools are required. Fault-tolerant software is one such approach whose time has come.

## Sources of Software Faults

The success of any fault-tolerant software technique is critically dependent upon the effectiveness of the employed error detection techniques (1). If an erroneous state is not detected, the fault causing this error will not be tolerated. An understanding of the underlying source of faults can be an aid in designing and analyzing error detection techniques.

A software fault is a design defect which is directly or indirectly caused by a human mistake and can occur in every phase of the software life-cycle. Faults in a system specification, e.g., imprecisely stated or missing functions, are due to a human's inability to correctly translate a problem into a description of a system-level solution. These faults are propagated and new faults are introduced into the subsequent software specification, software design, source code, and object code. With the increased usage of software tools, the number of faults that are directly introduced by the software engineer can potentially be decreased. However, the tool itself can insert an indirect fault (referred to as indirect because a human originally programmed the tool). Past occurrences of this have been mainly restricted to compiler bugs. Indirect faults may increase with the use of automated tools and, like compiler bugs, may be extremely difficult to detect and isolate.

## Methods of Handling Faults

Methods for handling software faults can be separated into fault prevention and fault-tolerant techniques (4,1). Fault prevention methods include design methodologies for dealing with the complexity of hardware and software, the use of highly reliable components, and comprehensive testing. Usually, fault prevention methods are utilized prior to system deployment. Fault-tolerant software techniques attempt to automatically overcome software faults without external intervention. The primary usefulness of fault-tolerant software techniques is to handle faults that remain after the system is in operation, but it is also useful in detecting system specification and software faults during development.

The process or steps that a fault-tolerant system goes through have been described in different terms (5,4,1). We will follow the terminology of Reference 1 for purposes of illustration.

The four steps of a fault-tolerant system are: Error detection, damage assessment, recovery, and fault treatment. The capability to detect errors is the crux of any fault-tolerant technique. Since it is doubtful that any error detection technique will occur concurrently with the encountering of a software fault, an assessment of the extent of damage (i.e., changes in state information) must take place prior to attempting error recovery. Often, damage assessment assumptions are a part of the design of the fault-tolerant software system. Error recovery returns the system from a erroneous to a correct state. Finally, fault treatment attempts to eradicate the source of all this trouble, the fault itself, and return the system to service.

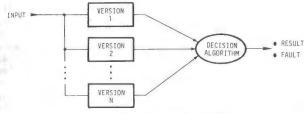

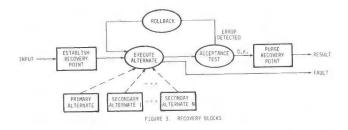

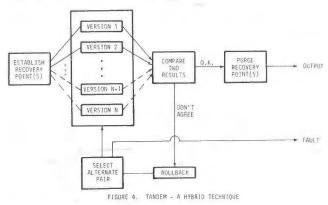

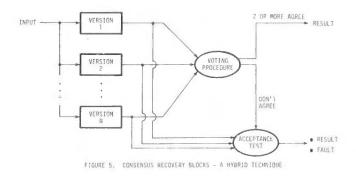

## Fault-Tolerant Software Techniques