# AIAA/IEEE 6<sup>TH</sup> DIGITAL AVIONICS SYSTEMS CONFERENCE

For permission to copy or republish, contact the American Institute of Aeronautics and Astronautics, 1633 Broadway, New York, NY 10019

BOEING Ex. 1031, p. 1

DODLEY KNOX LIBRARY NAVAL POSTGRADUATE SCHOOL MONTEREY, CALIFORNIA 93943-5006 PROCEEDINGS

OF THE

AIAA/IEEE

6th

# **DIGITAL AVIONICS**

# SYSTEMS CONFERENCE, 6#4, 1984.

DECEMBER 3-6, 1984/BALTIMORE, MARYLAND

AMERICAN INSTITUTE OF AERONAUTICS AND ASTRONAUTICS • TECHNICAL COMMITTEE — DIGITAL AVIONICS

INSTITUTE OF ELECTRICAL AND ELECTRONIC ENGINEERS • AEROSPACE AND ELECTRONICS SYSTEMS SOCIETY

ī.

# THE CONFERENCE AT A GLANCE

| MONDAY, DECEMBER 3                                                                                                                                                                                   | TUESDAY, DECEMBER 4                                                                                                                                                                                                                                                                                                                     | WEDNESDAY, DECEMBER 5                                                                                                                                                                                                                                                                                                                                                                                            | THURSDAY, DECEMBER 6                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:00-12:00<br>TUTORIALS<br>A. Introduction to Digital<br>Avionics. (307)<br>B. Introduction to ADA <sup>™</sup> .<br>(308)<br>C. Digital Signal<br>Processing. (309)<br>TL<br>695                    | 9:00-12:00<br>PLENARY SESSION<br>TOPIC: Digital Avionics<br>Requirements for the<br>1990s<br>SPEAKERS:<br>B.A. Zempolich<br>P.O. Brown<br>R.N. Longuemare<br>E.C. Machacek                                                                                                                                                              | <ul> <li>9:00-12:15</li> <li>TECHNICAL SESSIONS</li> <li>6. Systems and Software-<br/>Development and Evalu-<br/>ation Tools. (307)</li> <li>7. General Aviation Avionics.<br/>(301)</li> <li>8. Fault Tolerant Avionics.<br/>(308)</li> <li>9. Signal Processing. (310)</li> <li>10. Crew Systems-Advanced</li> </ul>                                                                                           | <ul> <li>9:00-12:15</li> <li>TECHNICAL SESSIONS</li> <li>16. Systems and Software-<br/>ADA™. (307)</li> <li>17. On-Board Monitoring<br/>and Test. (301)</li> <li>18. VLSI Design and Testing<br/>(308)</li> <li>19. Data Link Systems<br/>Applications. (309)</li> <li>20. Merged Digital Map</li> </ul>                                                  |

| D 56<br>1984<br>OPEN                                                                                                                                                                                 | 12:00-2:00<br>LUNCHEON<br>Dutch Treat in Exhibit Area<br>(Hall C)                                                                                                                                                                                                                                                                       | Control and Display<br>Technology. (309)<br>12:15-2:15<br>LUNCHEON<br>Digital Avionics Award<br>(Hall C)                                                                                                                                                                                                                                                                                                         | Techniques. (310)<br>12:15-2:15<br>LUNCHEON<br>Speaker - Jack Jackson<br>(Hall C)                                                                                                                                                                                                                                                                         |

| 2:00-5:00<br>TUTORIALS<br>D. Voice Interactive<br>Systems Applications<br>and Implementation.<br>(307)<br>E. ADA™ for Project<br>Managers. (308)<br>F. Overview of Artificial<br>Intelligence. (309) | <ul> <li>2:15-5:30</li> <li>TECHNICAL SESSIONS <ol> <li>Systems and Software-Development Methods. (307)</li> <li>Commercial Transport Avionics. (301)</li> <li>Advanced Avionic Sensor Systems. (308)</li> <li>Crew Systems-Human Factors-Artificial Intelligence. (309)</li> <li>Digital Flight Controls. (310)</li> </ol> </li> </ul> | <ul> <li>2:15-5:30</li> <li>TECHNICAL SESSIONS</li> <li>11. Systems and Software-<br/>Verification and Test<br/>Techniques. (307)</li> <li>12. Rotorcraft Avionics. (301)</li> <li>13. Data Bus-Concepts and<br/>Practices. (308)</li> <li>14. Crew Systems-Systems,<br/>Development and<br/>Integration. (309)</li> <li>15. Communication, Naviga-<br/>tion, and Identification<br/>Terminals. (310)</li> </ul> | <ul> <li>2:15-5:30</li> <li>TECHNICAL SESSIONS</li> <li>21. Advanced Digital<br/>Integrated Circuits. (307)</li> <li>22. Airborne Separation<br/>Assurance. (308)</li> <li>23. The All Electric Airplane<br/>(309)</li> <li>24. Standardized Modular<br/>Avionics. (310)</li> <li>25. Digital Propulsion<br/>Control and Monitoring.<br/>(301)</li> </ul> |

| OPEN                                                                                                                                                                                                 | EVENING<br>6:00-8:00<br>EXHIBITORS RECEPTION<br>Hors d'Oeuvres<br>Cash Bar<br>(Hall C)                                                                                                                                                                                                                                                  | EVENING<br>6:00-8:00<br>PANEL DISCUSSIONS<br>A. National Airspace<br>Systems Plan. (307)<br>B. VHSIC Insertion and<br>Its Implications. (309)                                                                                                                                                                                                                                                                    | EVENING<br>CRAB FEAST<br>Relaxed Evening<br>Casual Attire                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                      | 12:00-8:00<br>EXHIBITS OPEN                                                                                                                                                                                                                                                                                                             | 9:00-8:00<br>EXHIBITS OPEN                                                                                                                                                                                                                                                                                                                                                                                       | 9:00-2:00<br>EXHIBITS OPEN                                                                                                                                                                                                                                                                                                                                |

Ada is a registered trademark of the U.S. Government, Ada Joint Program Office

# TECHNICAL SESSIONS DUDLEY KNOX LIBRADY

NAVAL POSTGRADUATE SCHOOL

| SYSTEMS AND SOFTWARE — DEVELOPMENT METHODS                 | MONTEREY, CALIFORNIA | 1  |

|------------------------------------------------------------|----------------------|----|

| COMMERCIAL TRANSPORT AVIONICS                              |                      | 2  |

| ADVANCED AVIONIC SENSOR SYSTEMS                            |                      | 3  |

| CREW SYSTEMS — HUMAN FACTORS AND ARTIFICIAL INTELLIGENC    | E                    | 4  |

| DIGITAL FLIGHT CONTROLS                                    |                      | 5  |

| SYSTEMS AND SOFTWARE DEVELOPMENT AND EVALUATION TO         | OLS                  | 6  |

| GENERAL AVIATION AVIONICS                                  |                      | 7  |

| FAULT TOLERANT AVIONICS                                    |                      | 8  |

| SIGNAL PROCESSING                                          |                      | 9  |

| CREW SYSTEMS - ADVANCED CONTROL/DISPLAY TECHNOLOGY .       |                      | 10 |

| SYSTEMS AND SOFTWARE - VERIFICATION AND TEST TECHNIQUE     | S                    | 11 |

| ROTORCRAFT AVIONICS                                        |                      | 12 |

| DATA BUS CONCEPTS AND PRACTICES                            |                      | 13 |

| CREW SYSTEMS — SYSTEMS DEVELOPMENT AND TEST                |                      | 14 |

| COMMUNICATION, NAVIGATION, AND IDENTIFICATION (CNI) TERMIN | ALS                  | 15 |

| SYSTEMS AND SOFTWARE — ADA™                                |                      | 16 |

| ON-BOARD MONITORING AND TEST                               |                      | 17 |

| VLSI DESIGN AND TESTING                                    |                      | 18 |

| DATA LINK SYSTEMS APPLICATIONS                             |                      | 19 |

| MERGED DIGITAL MAP TECHNIQUES                              | ]                    | 20 |

| ADVANCED DIGITAL INTEGRATED CIRCUITS                       |                      | 21 |

| AIRBORNE SEPARATION ASSURANCE                              | ]                    | 22 |

| ALL ELECTRIC AIRCRAFT                                      |                      | 23 |

| STANDARDIZED MODULAR AVIONICS                              |                      | 24 |

| DIGITAL PROPULSION CONTROL AND MONITORING SYSTEMS          |                      | 25 |

## **TABLE OF CONTENTS**

1

6

6

## SESSION 1: SYSTEMS AND SOFTWARE — DEVELOPMENT METHODS

#### Chairmen:

G. Henley Intermetrics Inc., Cambridge, MA

P.E. Gartz Boeing Commercial Airplane Co. Seattle, WA

#### AIAA-84-2598-CP Developing Safe Software for Critical Airborne Applications W.B. Noble, Hughes Aircraft Co., Ground Systems Group

#### AIAA-84-2595-CP

#### The Use of Structured Methods in the Development of Large Software-Based Avionics Systems

D.J. Hatley, *Lear Siegler Inc., Instrument* Avionics Div.

#### AIAA-84-2600-CP

| A Conceptual Design Methodology Used to |   |

|-----------------------------------------|---|

| Design a Support Computer Program       | 1 |

| J.A. Mozier, D.J. Berg and R.L. Young,  |   |

| McDonnell Douglas Corp.,                |   |

#### SESSION 2: COMMERCIAL TRANSPORT AVIONICS

#### Chairmen:

R.L. Heimbold Lockheed Corp. Burbank, CA

J.H. Shannon *Douglas Aircraft Co. Long Beach, CA*

#### AIAA-84-2602-CP

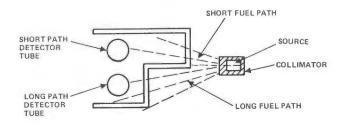

| Digital Fuel Quantity Indicating System for                   |    |

|---------------------------------------------------------------|----|

| Aircraft                                                      | 21 |

| R.L. Newport, D.J. Nelson and M.T. Manfred,<br>Honeywell Inc. |    |

| AIAA-84-2603-CP                                               |    |

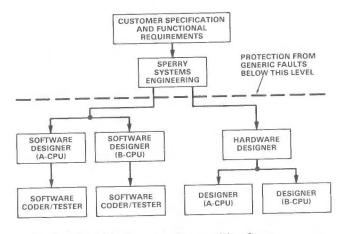

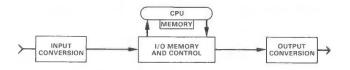

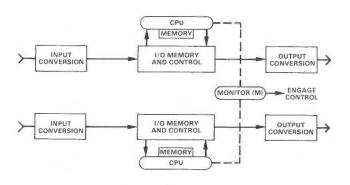

| Architectural Solutions to Safety Problems of                 |    |

| Digital Flight-Critical Systems for Commercial                |    |

| Transports               | 28 |

|--------------------------|----|

| L.J. Yount, Sperry Corp. |    |

### AIAA-84-2604-CP

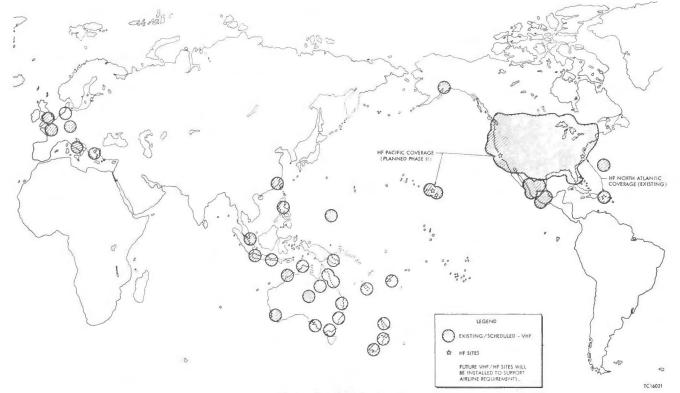

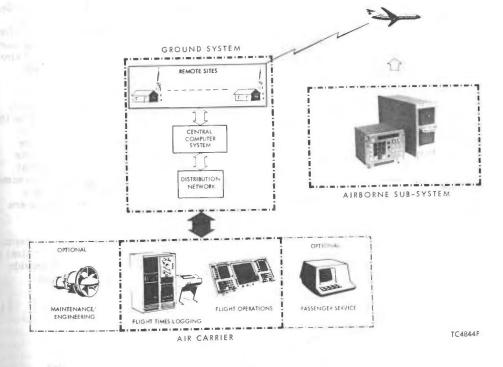

| Applications of Air-Ground-Air Digital                                      | 20     |

|-----------------------------------------------------------------------------|--------|

| Communication System ACARS/AIRCOM<br>C.A. Bennett, <i>Teledyne Controls</i> | <br>36 |

#### AIAA-84-2605-CP

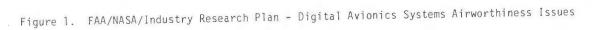

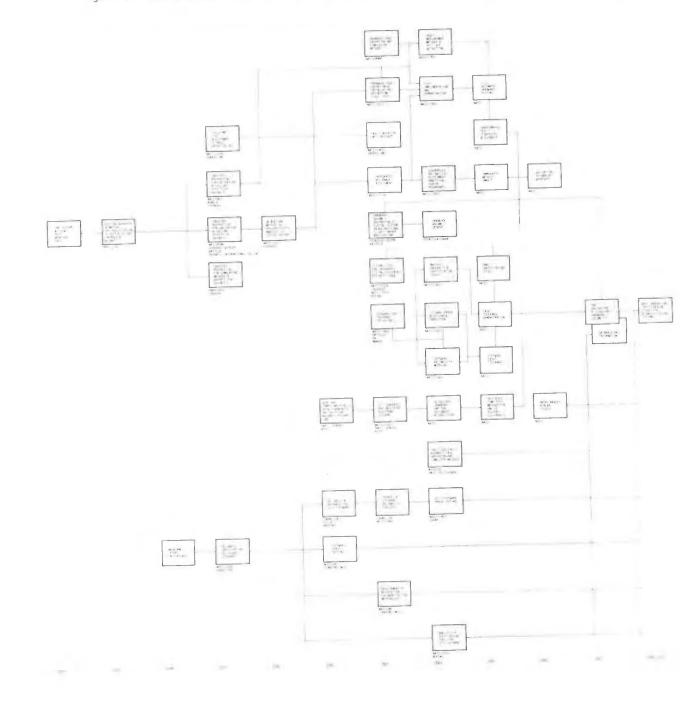

| An Overview of the Digital Avionics<br>Assessment Activities Being Conducted by the<br>Federal Aviation Administration at NASA-Ames<br>Research Center<br>W. Larsen, NASA Ames Research Center,<br>and D. Eldredge and E. Hitt, Battelle<br>Columbus Labs, and D. Mulcare and W.<br>Ness, Lockheed-Georgia Co. | 40 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| AIAA-84-2606-CP<br>Recent Advances in Aircraft On-Board Weight<br>and Balance Systems<br>J.P. O'Brien, Sundstrand Data Control Inc.                                                                                                                                                                            | 47 |

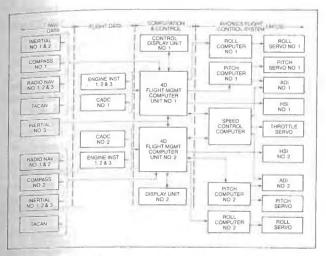

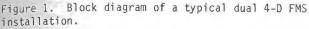

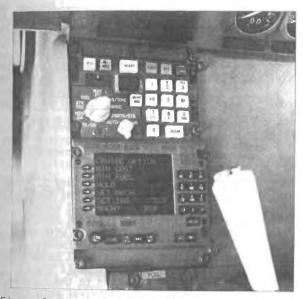

| AIAA-84-2607-CP<br>TIME FLIES, An In-Service Evaluation of a 4-D                                                                                                                                                                                                                                               | EA |

Flight Management System

54

D.A. Moor, Lockheed-California Co.

#### SESSION 3: ADVANCED AVIONIC SENSOR SYSTEMS

#### Chairmen:

E.A. Hopper Westinghouse Dayton, OH

R.B. Longbrake ASD/ENA Wright-Patterson AFB, OH

#### AIAA-84-2613-CP

| Imaging Sensor Autoprocessor<br>S.C. Sawtelle and R.J. Jennewine,<br>AFWAL/AARI, Wright-Patterson AFB                                                   | 60 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| AIAA-84-2610-CP<br>Infrared Search and Track System<br>Development<br>W.E. Moore, M. Spector and V.D. Best,<br><i>AFWAL/AART, Wright-Patterson AFB</i>  | 65 |

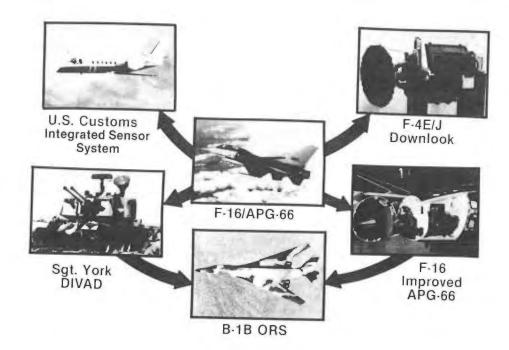

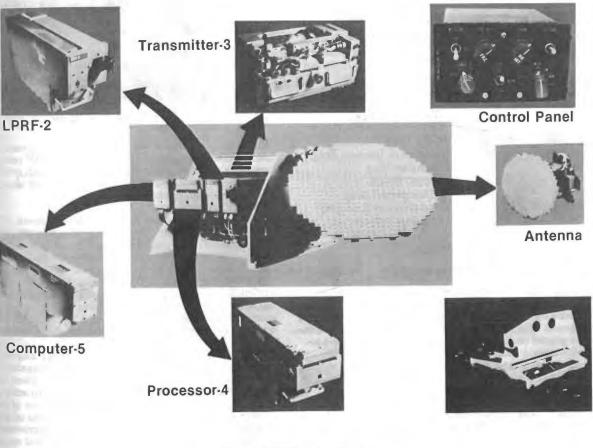

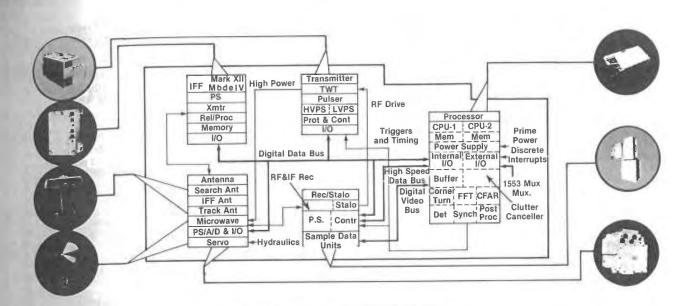

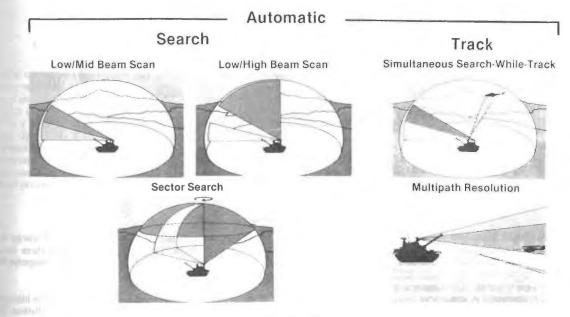

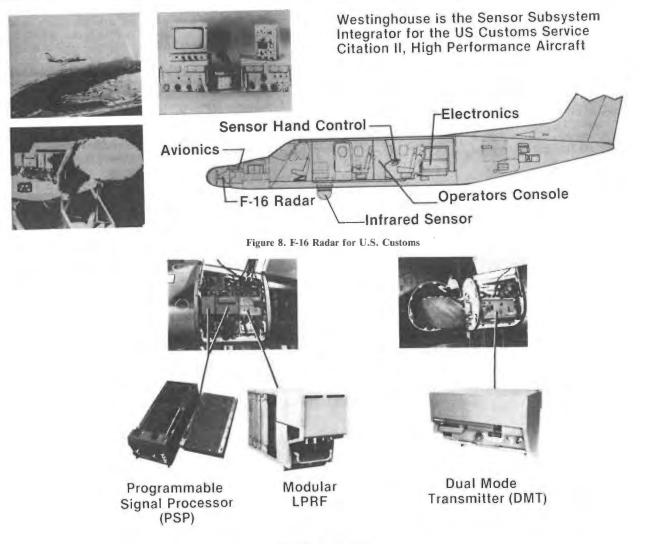

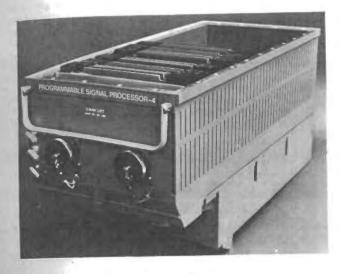

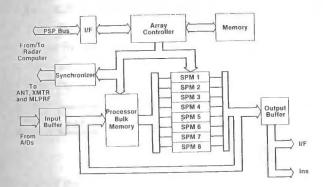

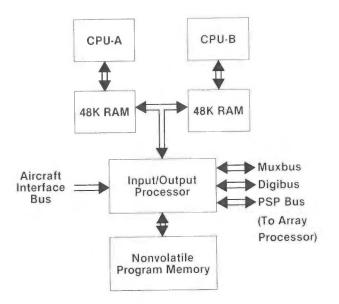

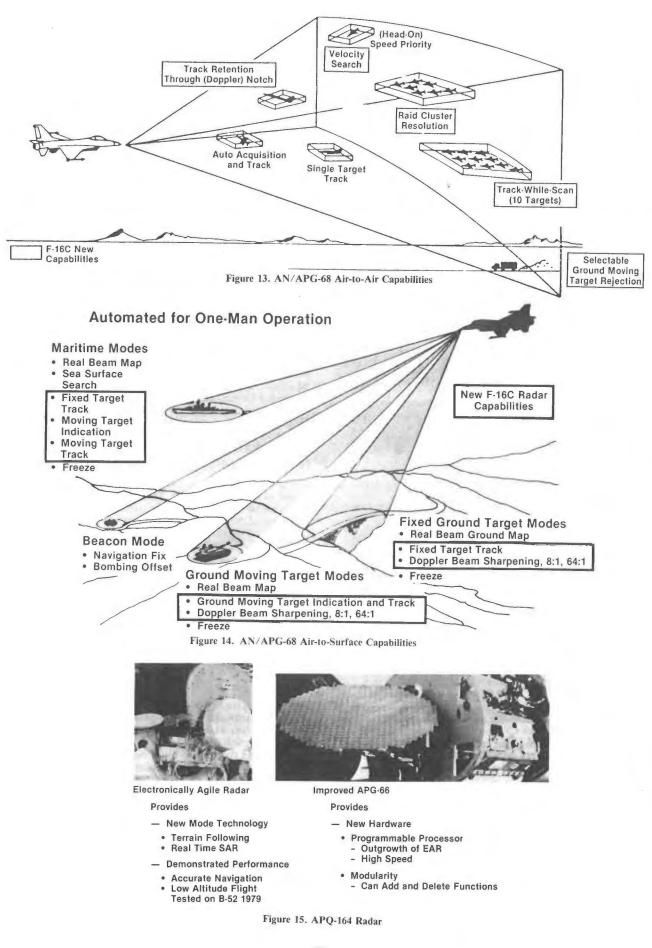

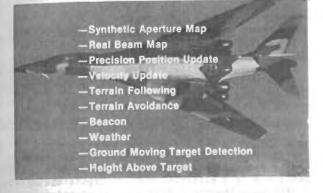

| AIAA-84-2609-CP<br>The APG-66 Radar and Its Derivative<br>Applications<br>L.J. Kuchinski and T.R. Patton, <i>Westinghouse</i><br><i>Electric Corp.</i>  | 68 |

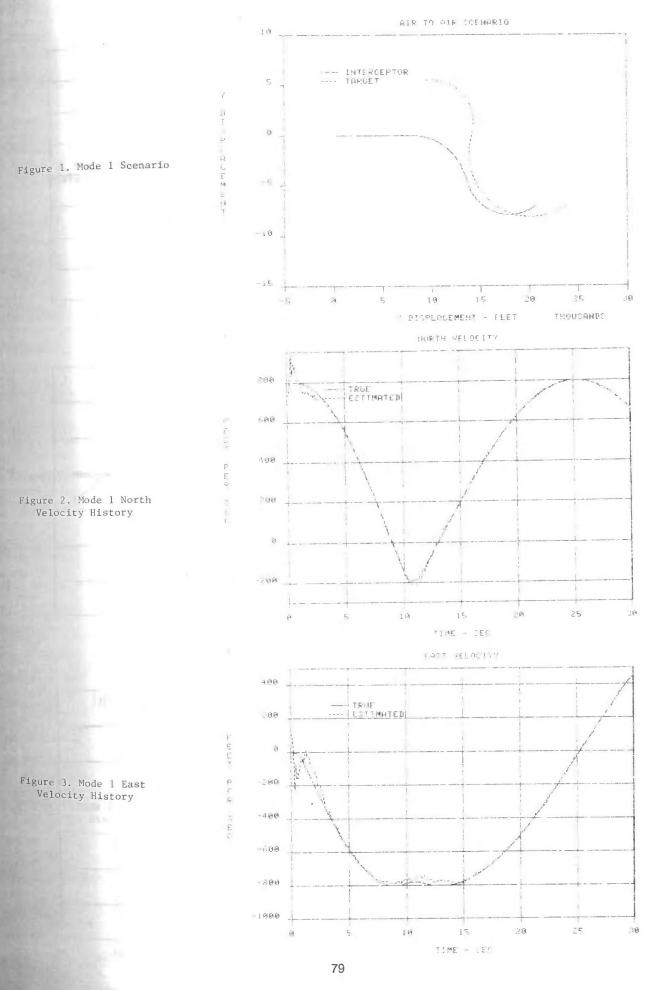

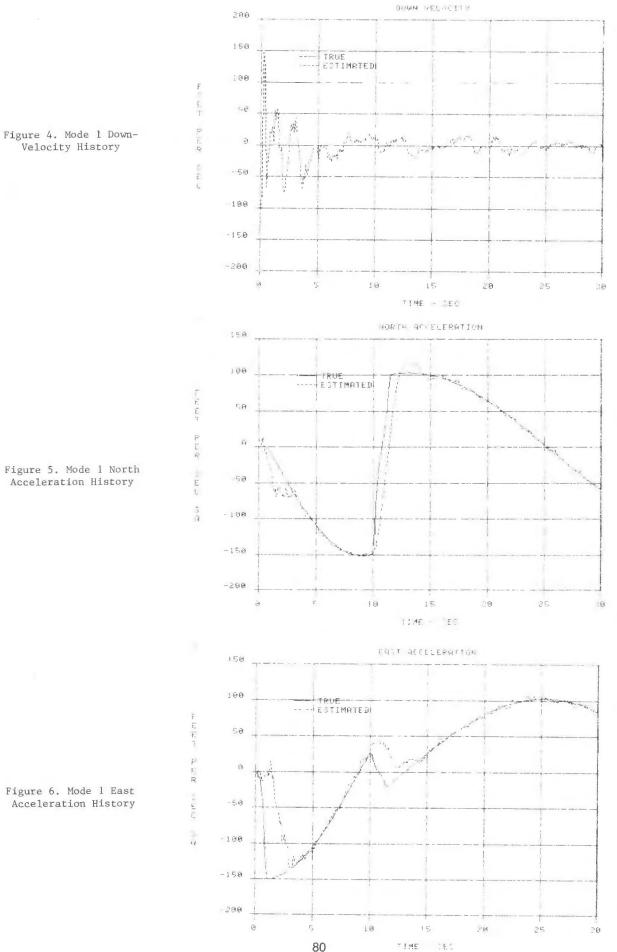

| AIAA-84-2614-CP (Alternate)<br>Integrated Tracking Software for Multimode<br>Operation<br>J.L. Farrell and D.A. Hedland, Westinghouse<br>Electric Corp. | 76 |

#### SESSION 4: CREW SYSTEMS: HUMAN FACTORS AND ARTIFICIAL INTELLIGENCE

#### Chairmen:

R.N. Bretoi NASA Ames Research Center Moffett Field, CA

D. Cole Air Force Aerospace Medical Reesearch Lab. Wright-Patterson AFB, OH

#### AIAA-84-2616-CP

| The Evaluation of Display Symbology: A      |    |

|---------------------------------------------|----|

| Chronometric Study of Visual Search         | 84 |

| R. Remington, NASA Ames Research            |    |

| Center, and D. Williams, Psycho Linguistics |    |

| Institute                                   |    |

| AIAA-84-2617-CP                             |    |

| Artificial Intelligence Implications for    |    |

| Advanced Pilot/Vehicle Interface Design     | 90 |

| K   Manuall and IA Davia Canaral            |    |

K.J. Maxwell and J.A. Davis, *General Dynamics Fort Worth Div.*

#### AIAA-84-2619-CP

### Model-Based Reasoning in Expert Systems: An Application to Enroute Air Traffic Control

S.E. Cross, Air Force Institute of Technology, Wright-Patterson AFB

AIAA-84-2620-CP

#### Mission Scenarios for Cockpit Automation Technology

Technology

102

G.G. Kuperman and P.V. Kulwicki, Air Force

Aerospace Medical Research Lab., Wright

Patterson AFB

#### SESSION 5: DIGITAL FLIGHT CONTROLS

#### Chairmen:

C.R. Abrams Naval Air Development Center Warminster, PA

G. Vetsch McDonnell Douglas Corp. St. Louis, MO

| AIAA-84-2622-CP                            |     |

|--------------------------------------------|-----|

| Backup Modes for the F/A-18 Digital Flight |     |

| Control System                             | 108 |

| H.E. Harschburger, B. Glaser and J.R.      |     |

| Hammel, McDonnell Douglas Corp.            |     |

### AIAA-84-2623-CP

### Integrated Flight Control/Navigation

Sensors ..... R.É. Ebner and S.Y. Wei, *Litton Systems Inc.*

#### AIAA-84-2624-CP

####

Multivariable Control System DesignTechniques: An Application to a Short TakeOff and Landing Aircraft132R.J. Landy and D.B. Kim, McDonnell AircraftCo.

#### AIAA-84-2627-CP

## SESSION 6: SYSTEMS AND SOFTWARE — DEVELOPMENT AND EVALUATION TOOLS

#### Chairmen:

95

E. Waltz Bendix Communications Div. Baltimore, MD

D. Brown General Dynamics Fort Worth, TX

#### AIAA-84-2629-CP

Development of a Support Software System for

Real-Time HAL/S Applications

151

R.S. Smith, NASA Langley Research Center

151

#### AIAA-84-2633-CP

#### AIAA-84-2635-CP

Development Tools - Case Study for LargeSystems167K. Hornbach, Lear-Siegler/Instrument Div.

### AIAA-84-2631-CP

Multi-Sensor Surveillance Performance

Evaluation Tool

175

C.L. Bowman and G. Snashall, Verac Inc.

#### **SESSION 7: General Aviation Avionics**

#### Chairman:

M.W. Kelly Beech Aircraft Corp. Wichita, KS

#### AIAA-84-2637-CP

General Aviation Data Bus Update ..... 180 D.L. Stanislaw, *Cessna Aircraft Co.*

VII

116

#### AIAA-84-2639-CP

Systems Concept for Speech TechnologyApplication in General Aviation184R.A. North, Honeywell SystemsResearch Center and H. Bergeron, NASALangley Research Center

#### **SESSION 8: Fault Tolerant Avionics**

#### Chairmen:

B.L. Dove NASA Langley Research Center Hampton, VA

D.B. Mulcare Lockheed-Georgia Co. Marietta, GA

AIAA-84-2644-CP Advanced Information Processing System ..... 199 J.H. Lala, *Charles Stark Draper Lab.*

#### AIAA-84-2646-CP

#### AIAA-84-2647-CP

Evaluation Methodologies for an AdvancedInformation Processing System217R.S. Schabowsky Jr., E. Gai, P. Motyka,J.H. Lala, and B.K. Walker, Charles StarkDraper Lab.

### AIAA-84-2648-CP

Validation Methodology for Fault Tolerant

Clock Synchronization

225

S.C. Johnson and R.W. Butler, NASA Langley

Research Center

#### AIAA-84-2650-CP (Alternate) UltraReliable Fault-Tolerant Control

#### SESSION 9: Signal Processing

#### Chairmen:

G.J. Palatucci U.S. Naval Air Development Center Warminster, PA

B. Bjerede *Linkabit Corp. San Diego, CA*

#### AIAA-84-2651-CP

Signal Processing Using Digital Lattice

Filters

247

L. Chin, Naval Air Development Center

#### AIAA-84-2652-CP

Application of Digital Signal Processing to aLow Rate Communications ReceiverR.G. Henderson and P. Lafrance, The MITRECorp.

#### AIAA-84-2653-CP

The Impact of Advanced ComputationalTechniques on Digital Avionics SignalProcessor PerformanceW.M. Vojir, Grumman Aerospace Corp.

#### AIAA-84-2654-CP

Self Adaptive Filtering of Environmental Noises

from Speech

263

D. Graupe, J. Grosspietsch and S. Basseas,

IntelliTech Inc.

#### AIAA-84-2655-CP

#### AIAA-84-2656-CP

#### SESSION 10: CREW SYSTEMS: ADVANCED CONTROL/DISPLAY TECHNOLOGY

#### Chairman:

J.J. Hatfield NASA Langley Research Center Hampton, VA

#### AIAA-84-2657-CP

#### Software Controlled Display/Pushbutton ..... 285 D.A. Nicholson, *MICRO SWITCH Div. of Honeywell* and R.J. Spiger, *Boeing Aerospace Co.*

#### AIAA-84-2663-CP

| <b>Recent Advances in Electroluminescent</b> | ×   |

|----------------------------------------------|-----|

| Displays Applicable to Future Crew-Station   |     |

| Interfaces                                   | 291 |

| M.R. Miller and E. Schlam, U.S. Army-        |     |

| ERADCOM, and J.B. Robertson and J.J.         |     |

| Hatfield, NASA Langley Research Center       |     |

|                                              |     |

### AIAA-84-2659-CP

| $\alpha$ -Si Addressed Liquid Crystal Aircraft | - 7 |

|------------------------------------------------|-----|

| Display                                        | 296 |

| D.E. Castleberry, J.E. Bigelow, H.G. Parks,    |     |

| W.W. Piper and G.E. Possin, General Electric   |     |

| Co.                                            |     |

|                                                |     |

#### AIAA-84-2660-CP

J.C. Ruth, *McDonnell Douglas Electronics Co.*

## SESSION 11: SYSTEMS AND SOFTWARE VERIFICATION AND TEST TECHNIQUES

#### Chairmen:

E.A. Delanty The Boeing Co. Seattle, WA

J.G. Weber VERAC Inc. San Diego, CA

#### AIAA-84-2669-CP

| Verification Techniques for Improving Software |     |

|------------------------------------------------|-----|

| <b>Quality Through Automated Requirements</b>  |     |

| Data Bases                                     | 309 |

| G. Lueders, Sperry Corp., Flight Systems Div.  |     |

|                                                |     |

#### AIAA-84-2667-CP

| Automated Benchmark Generation Based          |     |

|-----------------------------------------------|-----|

| Upon a Specification Language                 | 312 |

| N. Rajan, S.E. Feteih, Stanford Univ., and J. |     |

| Saito, NASA Ames Research Center              |     |

#### AIAA-84-2665-CP

| Automated Software Test System for The 737- |     |

|---------------------------------------------|-----|

| 300 Flight Management Computer              | 319 |

| S.C. Runo, The Boeing Co.                   |     |

#### AIAA-84-2664-CP

| A Method for Testing a Digital Flight Control<br>System Without the Use of Ground Support |     |  |

|-------------------------------------------------------------------------------------------|-----|--|

| Equipment                                                                                 | 325 |  |

| H.E. Hansen, McDonnell Aircraft Co.                                                       |     |  |

#### AIAA-84-2666-CP Real Time Data Processing for Avionics

# Testing on the A-6E 332 P.T. Richards and J. Lehmann, Grumman Data Systems Corp.

#### AIAA-84-2670-CP (Alternate)

#### Safety of Flight and Qualification Testing for

#### AIAA-84-2726-CP

Executable Assertions and Flight Software .... 346 A. Mahmood, D.M. Andrews and E.J. McCluskey, *Center for Reliable Computing, Stanford Univ.*

#### **SESSION 12: Rotorcraft Avionics**

#### Chairmen:

D.G. Denery NASA Ames Research Center Moffett Field, CA

G. Stech Avionics Research and Development Activity Fort Monmouth, NJ

#### AIAA-84-2672-CP

#### AIAA-84-2673-CP

Evaluation of a Real-Time Predictive Guidance Law for Landing VTOL Aircraft at Sea ...... 359 C.H. Paulk Jr., NASA Ames Research Center, and A.V. Phatak, Analytical Mechanics Associates Inc.

#### AIAA-84-2674-CP

Digital Avionics and Flight Path DirectorFunctions of the HH-60 HelicopterF.G. Kilmer, R.L. Kilmer and B.A. Thalacker,IBM Federal Systems Div.

#### AIAA-84-2676-CP

Application of Differential GPS to Civil

Helicopter Terminal Guidance

379

R.P. Denaro, TAU Corp.

379

#### AIAA-84-2621-CP

Pilot Command Interfaces for Discrete Control of Automated Nap-of-the-Earth Flight ...... 386 S.J. Mountford, R. Penner and P. Bursch, *Honeywell SRC/MMS*

## SESSION 13: DATA BUS CONCEPTS AND PRACTICES

#### Chairmen:

R.M. Hartman McDonnell Douglas Astronautics Co. Huntington Beach, CA

M.A. Geyer Westinghouse Electric Corp. Baltimore, MD

#### AIAA-84-2679-CP

Standard Computer Bus for MIL-STD-1750A

Avionics Computer

393

S. Levy and D. Penn, Israel Aircraft

Industries, and E. Loker, Elbit Computers

Ltd.

####

#### AIAA-84-2682-CP

Data Bus Interface MIL-STD-1553B/ARINC561J. Spieth, ASD, U.S. Air Force

#### AIAA-84-2757-CP

#### AIAA-84-2756-CP

High-Speed Bus Structures forMultiprocessingQ.E. Dolecek, The Johns Hopkins Univ.

#### SESSION 14: CREW SYSTEMS: SYSTEMS DEVELOPMENT AND TEST

#### Chairman:

W.D. Smith Boeing Commercial Airplane Co. Seattle, WA

#### AIAA-84-2686-CP An Advanced Media Interface for Control of Modern TransportAircraft Navigational

Systems

421

D.R. Jones, R.V. Parrish and L.H. Person,

421

NASA Langley Research Center, and J.L.

100

Old, Research Triangle Institute

100

####

#### AIAA-84-2688-CP

#### AIAA-84-2689-CP

#### SESSION 15: COMMUNICATION, NAVIGATION, AND IDENTIFICATION (CNI) TERMINALS

#### Chairmen:

D.B. Cox, Jr. *C.S. Draper Lab. Cambridge, MA*

F.W. Smead ITT Avionics Nutley, NJ

AIAA-84-2693-CP Customizing ICNIA for Specific Applications ...... WITHDRAWN F.W. Smead, *ITT Avionics*

#### AIAA-84-2691-CP

#### AIAA-84-2698-CP (Alternate)

#### SESSION 16: SYSTEMS AND SOFTWARE: ADA™

#### Chairmen:

D.B. Mulcare Lockheed-Georgia Co. Marietta, GA

T.V. McTigue *McDonnell Aircraft Co. St. Louis, MO*

#### AIAA-84-2701-CP

XIII

**Exhibitors**

W.W. GAERTNER RESEARCH INC.

SCI SYSTEMS, INC.

## \* AMERICAN ASSOCIATION FOR THE ADVANCEMENT OF SCIENCE

.

DIGITAL TECHNOLOGY, INC.

## \* IEEE-AEROSPACE AND ELECTRONIC SYSTEMS SOCIETY

#### AIAA-84-2702-CP

Real Life Considerations of ADA™ Runtime Organizations for Real-Time Applications ..... 472 J.M. Kamrad II, *Alsys*

#### SESSION 17: ON-BOARD MONITORING AND TEST

#### Chairmen:

L.M. Carrier Jr. Rockwell International Corp. Lakewood, CA

D. Pieratt ASD/BIEE Wright-Patterson AFB, OH

#### AIAA-84-2706-CP Maintenance Assist Functions Embedded Within the 737-300 Flight Management

#### AIAA-84-2709-CP Integrated On-Board Monitoring and Test Concepts

Concepts

492

P.C. Jenkins and C.J. Ong, Rockwell

International Corporation

#### AIAA-84-2708-CP

Avionics Hardware Design for Testability ..... 498 B.L. Ferrell and S.L. Over, *General Dynamics Fort Worth Div*.

#### AIAA-84-2677-CP

Remote Maintenance Monitoring Using a

Digital Data Link

503

D. Dowling and R.A. Lancaster, ARINC

Research Corp.

#### AIAA-84-2705-CP

Crash Survivable Flight Data Recorder ...... 508 G.E. Davis, *General Dynamics Fort Worth Div.*

#### SESSION 18: VLSI DESIGN AND TESTING

#### Chairman:

C.H. Huang Lockheed Research and Development Div. Palo Alto, CA

#### AIAA-84-2712-CP

#### AIAA-84-2711-CP

Gate Array, Standard Cell, and Fully Custom:

Building Blocks for the Digital Avionics

Designer

517

H.L. Owen III and M.T. Kopp, Georgia

Institute of Technology

#### AIAA-84-2713-CP

#### SESSION 19: DATA LINK SYSTEMS APPLICATIONS

#### Chairmen:

D.G. Botha AFWAL/AAAI Wright-Patterson AFB, OH

D.G. Evans PME/PMA Washington, DC

#### AIAA-84-2716-CP

The Navy's Tactical Data Network ...... 531 W.J. Schoppe, *Naval Air Development Center*

### AIAA-84-2719-CP

#### SESSION 20: MERGED DIGITAL MAP TECHNIQUES

#### Chairman:

J.W. Weber Hughes Aircraft Co. Los Angeles, CA

#### AIAA-84-2724-CP

Data Compression Techniques Digital Map ... 549 P.L. Poehler, *DBA Systems Inc.*

#### AIAA-84-2723-CP

A Terrain Data/Digital Map System for LHX ... 557 G.O. Burnham, C. Benning and R.L. Rivard, *Texas Instruments Inc.*

## SESSION 21: ADVANCED DIGITAL INTEGRATED CIRCUITS

#### Chairmen:

D.B. McBrayer LTV Vought Missiles and Advanced Programs Dallas, TX

W.R. Hutchins Sanders Associates Nashua, NH

|   | FAIRCHILD INDUSTRIES |

|---|----------------------|

|   |                      |

|   |                      |

|   |                      |

|   |                      |

|   | •                    |

|   |                      |

|   |                      |

|   |                      |

|   |                      |

|   |                      |

|   |                      |

| [ |                      |

|   |                      |

|   |                      |

|   |                      |

### AIAA-84-2730-CP

#### VLSI Chip Set for High-Performance Avionic

#### SESSION 22: AIRBORNE SEPARATION ASSURANCE

#### Chairmen:

F.S. Chandler Sperry Dalmo Victor Inc. Belmont, CA

J.J. Fee Federal Aviation Administration Washington, DC

### AIAA-84-2734-CP

| Evolution of the Collision Avoidance         |     |

|----------------------------------------------|-----|

| System in the Cockpit                        | 573 |

| W.L. Hyland, Federal Aviation Administration |     |

#### AIAA-84-2738-CP

Enhanced TCAS-II Tracking Accuracy ...... 577 A.I. Sinsky and J.E. Reed, *Allied Bendix Aerospace, Bendix Communications Div.,* and J. Fee, *Federal Aviation Administration*

#### AIAA-84-2737-CP

| New Concepts in Collision Avoidance Logic   | 586 |

|---------------------------------------------|-----|

| W.D. Love and A.D. Zeitlin, The MITRE Corp. |     |

#### AIAA-84-2736-CP Improved TCAS I for Pilot Warning

J.D. Welch and W.H. Harman, *M.I.T. Lincoln Lab*.

#### AIAA-84-2735-CP

Secondary Surveillance Radar Mode S -Potential Applications and FutureRequirements in EuropeR.C.G. Jenyns and M.E. Cox, EuropeanOrganization for the Safety of Air Navigation

#### SESSION 23: ALL ELECTRIC AIRCRAFT

#### Chairman:

C.R. Spitzer NASA Langley Research Center Hampton, VA

#### AIAA-84-2739-CP Deja-Vu of All Electric/All Digital Aircraft ..... 606 M.J. Cronin, Lockheed-California Corp.

#### AIAA-84-2740-CP

| An Assessment of the 1990 Digital/Electric |     |  |

|--------------------------------------------|-----|--|

| Airplane                                   | 615 |  |

| G.E. Tagge, Boeing Commercial Airplane Co. |     |  |

### AIAA-84-2742-CP

| A Minimum Interruption AC Electric Power |     |

|------------------------------------------|-----|

| Generating System for Avionics           | 619 |

| B.R. Mehl and G.R. Pierce, Sundstrand    |     |

## SESSION 24: STANDARDIZED MODULAR AVIONICS

#### Chairmen:

R.K. Ricker USAF Wright-Patterson AFB, OH

J.A. Wyatt Dept. of Defense (OUSDRE) Falls Church, VA

#### AIAA-84-2745-CP

#### AIAA-84-2747-CP

#### AIAA-84-2749-CP

High Density Modular Avionics Packaging .... 634 F.J. Poradish, *Texas Instruments Inc.*

#### AIAA-84-2746-CP

Modular Avionics Packaging

Standardization

641

M.L. Austin and J.K. McNichols, Naval

Avionics Center

#### AIAA-84-2748-CP

#### SESSION 25: DIGITAL PROPULSION CONTROL AND MONITORING SYSTEMS

#### Chairmen:

J.C. Richards General Electric Co. Cincinnati, OH

P. Adams AFWAL/POTC Wright-Patterson AFB, OH

AIAA-84-2753-CP

#### Accuracies of Digital Engine Monitoring

Proven by Performance653J. Bluish, Allied Bendix Aerospace, and J.<br/>Balazic, Boeing Commercial Airplane Co.

#### AIAA-84-2754-CP

The F110 Engine Monitoring System ...... 661 M.J. Ashby and R.J.E. Dyson, *General Electric Co.*

# **MESSAGE FROM THE CHAIRMAN**

IRVING R. REESE Boeing Commercial Airplane Co.

Welcome to Baltimore and the AIAA/IEEE 6th Digital Avionics Systems Conference, otherwise known as the "6th DASC." It has been only one short year since the 5th DASC in Seattle. Yet, the 6th DASC will have even more technical sessions, panel discussions and exhibits than ever before. This, I believe, is indicative of the exciting progress we are experiencing in digital avionics.

Digital avionics are contributing to higher performance, new mission capabilities, improved crew interface and greater reliability for both military and civil aircraft. Several of these realized benefits were reported at the 5th DASC in Seattle last year. However, this is not a time to rest on our laurels. Even greater challenges and opportunities lie ahead.

Randy Moore and the Technical Program Committee have prepared a full agenda of tutorials, technical sessions and expert panel discussions designed to educate, share information and stimulate debate.

An outstanding array of technical exhibits will provide a rich opportunity to see, hear and operate state-of-the-art equipment and components. You would need a large travel budget to see even a fraction of this technology in its normal environment...so plan to spend a few hours browsing and talking with exhibitors.

The technical and exhibits programs are complemented by social events where you can visit with your colleagues in a relaxed atmosphere. A program of tours and information on local activities will make the 6th DASC memorable for spouses, too.

On behalf of the conference committee, participants and the sponsoring societies — welcome to the 6th DASC.

# **EXECUTIVE COMMITTEE**

#### **GENERAL CHAIRMAN**

Irving R. Reese Boeing Commercial Airplane Co.

#### EXECUTIVE VICE CHAIRMAN Johnnie L. Pearson

Westinghouse Electric Corp.

#### **TECHNICAL PROGRAM CHAIRMAN**

Randal K. Moore General Dynamics, Fort Worth Div.

### DEPUTY EXECUTIVE VICE CHAIRMAN

John G. Gregory Westinghouse Electric Corp.

#### **FINANCE CHAIRMAN**

Frank W. Smead ITT Avionics

PUBLICITY CHAIRMAN Frank C. White Aviation Consultant

DEPUTY PUBLICITY CHAIRMEN Wendie Chapman FAA

Arthur D. McComas Allied Bendix Aerospace SECRETARY William L. Hyland FAA

PUBLICATIONS CHAIRMAN Jean M. Eason General Dynamics, Fort Worth Div.

EXHIBITS CHAIRMAN Harold H. Fink ARINC AEEC

ARRANGEMENTS CHAIRMAN Ralph D. Ormsby Allied Bendix Aerospace

SPECIAL EVENTS CHAIRMAN Richard D. Porter Westinghouse Electric Corp.

# **DIGITAL AVIONICS SYSTEMS CONFERENCES**

#### THE HERITAGE

| AIAA 1ST DIGITAL AVIONICS SYSTEMS CONFI | ERENCE   |

|-----------------------------------------|----------|

| APRIL 2-4, 1975                         | BOSTON   |

| General Chairman: C. Eric Ellingso      | n, Mitre |

AIAA 2ND DIGITAL AVIONICS SYSTEMS CONFERENCE NOVEMBER 2-4, 1977 LOS ANGELES General Chairman: William M. Pulford, *Bendix*

- IEEE/AIAA 3RD DIGITAL AVIONICS SYSTEMS CONFERENCE NOVEMBER 6-8, 1979 FT. WORTH General Chairman: Daniel S. Goldin, *TRW*

- AIAA/IEEE 4TH DIGITAL AVIONICS SYSTEMS CONFERENCE NOVEMBER 16-19, 1981 St. LOUIS General Chairman: John C. Ruth, *General Dynamics*

- IEEE/AIAA 5TH DIGITAL AVIONICS SYSTEMS CONFERENCE OCTOBER 31-NOVEMBER 3, 1983 SEATTLE General Chairman: Cary R. Spitzer, NASA

| Technical Program |                                  |                                                                                                                          | Ext                                                                                                                                                                 | Exhibits Tutorials                                                                                                                                                                                        |                                                                                                                                                                                                                                                             | Itorials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sessions          | Paid                             | & Other                                                                                                                  | Firms                                                                                                                                                               | Booths                                                                                                                                                                                                    | Courses                                                                                                                                                                                                                                                     | Registratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9                 | 175                              | -                                                                                                                        | -                                                                                                                                                                   | -                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15                | 228                              | -                                                                                                                        | -                                                                                                                                                                   | -                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16                | 396                              | 210                                                                                                                      | 14                                                                                                                                                                  | 29                                                                                                                                                                                                        | _                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 23                | 494                              | 650                                                                                                                      | 37                                                                                                                                                                  | 56                                                                                                                                                                                                        | 6                                                                                                                                                                                                                                                           | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 05                | DEE                              | 005                                                                                                                      | 22                                                                                                                                                                  | 61                                                                                                                                                                                                        | 6                                                                                                                                                                                                                                                           | 285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   | <b>Sessions</b><br>9<br>15<br>16 | Sessions         Paid           9         175           15         228           16         396           23         494 | Sessions         Paid         Exhibits           9         175            15         228            16         396         210           23         494         650 | Sessions         Paid         Exhibits         Firms           9         175             15         228             16         396         210         14           23         494         650         37 | Sessions         Paid         Exhibits<br>& Other         Firms         Booths           9         175              15         228              16         396         210         14         29           23         494         650         37         56 | Yogram         Exhibits         Exhibits         Firms         Booths         Courses           9         175         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - |

### THE HISTORY

The Conference began in the fall of 1973 when discussions among key members of the AIAA Technical Committee in Communications surfaced a need for a conference to address emerging digital avionics technologies.

A proposal was generated and sent to the AIAA headquarters staff to try an experiment by having a conference called the Digital Avionics Systems Conference, to be held in the Spring of 1975 in Boston, Massachusetts.

There was a very strong interest by personnel from Mitre, Draper Labs, Lincoln Labs and Bendix to pull together the elements of this first conference. The conference that year was very modest in the number of presentations, speakers, and attendees. The proceedings were a very meager collection of papers and the motivation of the conference was to provide for very good presentations and open "birds of a feather" discussion periods. The concensus of the people attending was that this conference should become a permanent structure within the AIAA. The AIAA Technical Activities Committee concurred and decided that in 1977 a second conference should be held. An innovative feature of the 1977 conference, which was then called the Second Digital Avionics Systems Conference, was the addition of an exhibits program. There were four exhibits displayed in the hallways of the conference hotel. They were small but demonstrated the value of an exhibits program to complementing a very good technical program.

Another landmark decision was made to include the IEEE as a silent junior partner in the 1977 confer-This partnership proved to be so successful ence. that following the second conference, a representative of the IEEE (AESS) met with the AIAA Technical Committee on Communications and the conference organizers to discuss the role of the IEEE in future conferences. The final result of these meetings was a signed memorandum of understanding between the IEEE (AESS) and the AIAA Technical Committee on Communications to jointly sponsor the Digital Avionics Systems Conference in the future. Conferences would continue to be every two years, however, the overall conference responsibility, administrative, and financial, would alternate between the two societies. The Technical Program would always be the responsibility of the Society which was not responsible for the overall conference and, to help ensure continuity of the conference function, the technical program chairman of one conference would become the general conference chairman next conference.

The Third Digital Avionics Systems Conference occurred in the fall of 1979 in Fort Worth, Texas, and was the first of the IEEE run conferences with AIAA pulling together the technical program. This was a very interesting experiment and brought a new flavor and mode of operation to the conference.

Another novel feature of the Third DASC was a full commitment to an extensive large-scale exhibits program highlighting larger contractor exhibits. There were 15 exceptional exhibits, which provided an excellent balance to the technical program. This success put in motion the game plan for including the exhibits program as an integral part of the conference in the future. The exhibitors themselves, although expressing concern at first that this was a loss leader investment, were exceptionally delighted with the quantity and quality of people attending their exhibits, and 14 of the 15 expressed an immediate interest to be included in the next conference. Over 600 people attended the exhibits and shows, and the number of technical sessions supported a full three-day program with an evening panel session.

n

The Digital Avionics Systems Conference was now in full stride. The fifth conference occurred in Seattle and was highly successful. Over 600 people attended the five parallel technical sessions and more than 60 exhibit booths were filled. The digital avionics community was waiting for this meeting to occur and anticipated it well. A decision was made at this time to hold the 6th DASC one year later in Baltimore. This accelerated schedule took the DASC out of sync with the closely related computers in Aerospace Conference. Westinghouse, FAA, and Bendix follow Boeing as the industrial aerospace sponsors and everything points to an unbelievably successful 1984 Sixth Digital Avionics Systems Conference.

The Fourth Digital Avionics Systems Conference was in 1981 in St. Louis, Missouri. McDonnell Douglas acted as a local industrial sponsor. History had already taught the conference committee some very valuable lessons concerning the industrial support for conferences. In addition to willing and energetic volunteers, the presence of a large aerospace company to provide resources to support the conference was invaluable. General Dynamics provided this influence in Fort Worth, and Boeing had already agreed to support the conference in 1983 in Seattle. The conference had made its breakthrough. Over 1,000 people attended the excellent exhibits provided by over 30 companies. There were almost 500 paid registered attendees at the conference. As usual, another innovative feature was attempted. Six 3-hour tutorials were held on the day before the actual start of the conference. The tutorials presented information on relevant digital avionics topics and proved to be very successful.

# MESSAGE FROM THE TECHNICAL PROGRAM CHAIRMAN

Randal K. Moore General Dynamics, Fort Worth Div.

Welcome to the 6th Digital Avionics Systems Conference. Please permit me a few paragraphs to outline for you this year's technical program.

The tutorials will repeat some past favorites, sometimes with new instructors and different material. In addition, there will be expanded coverage of Ada<sup>™</sup>, as well as new topics in voice systems and artificial intelligence. Sylvia Blair has done an excellent job of obtaining tutorials that will be both interesting and informative.

The plenary session on Tuesday morning will take a forward look at digital avionics from four different perspectives. The plenary session theme "Digital Avionics Requirements for the 1990's" would be just as appropriate for the entire conference. The aircraft of the next decade will be built upon the lessons we learn today and the technologies now emerging.

As in the past, we have attempted to strike a balance between defense, commercial, and general aviation interests. This is reflected in the technical sessions, the plenary session, and particularly in the panel sessions. Ken Chow and Stew Baily have organized two superb panel discussions in order to better address different areas of current concern — VHSIC insertion for the defense community and the National Airspace Systems Plan for commercial and general aviation.

I am confident that the twenty-five different technical sessions will provide many papers to capture your interest. The session organizers, authors, and speakers have done a tremendous job. The papers cover technologies and end-item applications, components and systems, software and hardware, fixed-wing airplanes and rotorcraft. Yet, there is method to the diversity, and your selective attendance at the technical sessions will let you choose a view of digital avionic systems as wide or as narrow as you might wish.

I am proud to have been associated with the many people who contributed their time and talents to the 6th DASC technical program. I think you will agree that their contributions are reflected by the excellence of the result. Please join me as I say "Thanks" for a job well done.

Randal K. Moore Technical Program Chairman 6th DASC

# TECHNICAL PROGRAM COMMITTEE

TECHNICAL PROGRAM CHAIRMAN Randal K. Moore General Dynamics, Fort Worth Div.

#### DEPUTY TECHNICAL PROGRAM CHAIRMEN

AIAA

K.K. Chow Lockheed R&D Div.

IEEE

Stewart Baily ARINC Research Corp.

TUTORIALS

Sylvia H. Blair General Dynamics, Fort Worth Div.

# **TUTORIALS PROGRAM**

The 6th DASC tutorials provide relevant and informative sessions on topics of concern to engineers and managers. These six sessions cover many of the latest developments in the avionics industry. The

#### INTRODUCTION TO DIGITAL AVIONICS

Richard A. Maher VERAC, Inc.

Mr. Maher is currently Assistant Manager of the Avionics Group at VERAC Inc. in San Diego CA. He has over 25 years experience in development, evaluation, and the support of missile and avionic systems employing extensive use of advanced digital technologies. For the past 10 years at TRW, he was responsible for the development of advanced avionics concepts for electronic warfare and integrated avionics. Recent avionics program experience includes DAIS/-Pave Pillar, EW Area Reprogramming Capability (ARC), ICNIA, INEWS, and several VHSIC technology insertion applications.

Dr. John G. Weber VERAC, Inc.

Dr. Weber is manager of the Advanced Avionics Systems Department at VERAC Inc. San Diego CA. He has over 20 years experience in the design, development, and testing of digital systems. His design and development experience has been principally associated with the field of digital avionics. He was the chief designer and program manager for the Digital Avionics Information System (DAIS) Program where he made major contributions in developing a number of current avionics standards. His testing experience has involved data reduction and analysis for the Minuteman ICBM program and the development of the integration facility for avionics support testing (IFAST) for the Air Force Flight Test Center.

#### Course Description -

This course provides an overview and orientation to digital avionics systems architecture, hardware/software elements and support systems including: technology application areas; software discipline; interface standardization efforts; and developments in real time simulation support systems. The course will begin with a historical summary of digital avionics; describe on-going programs to demonstrate systems architecture and interface standards; and discuss future trends in avionics technology including VHSIC processing, software, voice interactive systems, artificial intelligence, and reprogrammable support systems. material is introductory in nature to provide a foundation from which the student can evolve toward his ow specific applications.

#### VOICE INTERACTIVE SYSTEMS APPLICATIONS AND IMPLEMENTATION

Dr. John C. Ruth McDonnell Douglas Electronics (

Dr. John C. Ruth is presently the Vice President McDonnell Douglas Electronics Company, Marketing ar New Business Development where he is responsible f market and advanced program planning/development ar sales. Prior to moving to MDEC, he worked at Gener Dynamics, Fort Worth Division where he was responsible f advanced avionics new business development plans ar strategies. Dr. Ruth is retired from the Air Force where t served in numerous management positions dealing wi digital avionics including Director of the Digital Avionic Information Systems (DAIS) Program Office of the Air Forc Avionics Lab.

Carolyn A. Moore VERAC, Inc.

Ms. Carolyn A. Moore is presently the task manager for t Avionics Displays and Control Simulator at Verac Inc. She responsible for the rapid prototyping system design simul tor for the F-16 C/D Program. Prior to coming to Verac, s was the senior design engineer for Phase I and Phase II AF F-16 Voice Command Program at General Dynamics, Fr Worth Division. She also served on the F-16 program as t Up-Front Controls Element Manager.

#### Course Description -

The concept of the "pilot as a manager" evolves as avi nic systems become more and more sophisticated. The pi will not only need to monitor and direct the various fun tions, but will need to access data or ask a subsystem relational data. This tutorial addresses three distinct areas voice interactive systems, starting with the reasons for t use of interactive voice recognition and synthesis as a v ble tool in current and advanced aircraft. Next, various typ of voice applications will be discussed, including a br history of the AFTI/F-16 Phase I flight test effort anc discussion on possible interactive voice applications advanced aircraft. Finally, a detailed systems approach how interactive voice systems can be implemented in current and future aircraft systems will be described.

#### INTRODUCTION TO ADA<sup>™</sup>

#### Richard E. Bolz Modern Programming Languages

Mr. Richard E. Bolz was an Associate Professor of Computer Science for the Air Force Academy in Colorado Springs for ten years. He was the code developer of the model course for the Department of Defense for Software Engineering with Ada<sup>TM</sup>. He has been teaching Ada<sup>TM</sup> for the last four years and is a member of AdaTech and Ada<sup>TM</sup> / Jovial User's Group. Mr. Bolz has presented this tutorial on numerous occasions including for Adatech and the Aerospace Engineering Conference and Show with excellent results.

#### Course Description -

This course introduces Ada<sup>™</sup>, the Department of Defense's new programming language. The purpose of the course is not to teach the language in detail, but rather to provide a flavor for the power and form of the language in the perspetive of modern software methodologies. The session begins with a brief history of the language, followed by detailed examples of packages, exception handlers, generic units, representation specification, and tasking.

#### **DIGITAL SIGNAL PROCESSING**

es

e

E1

rt

ie

0

ot

C-

or

of

he

ia-

es

ief

1 a

for

, of

ur-

Dr. Leonard Chin Naval Air Development Center

Dr. Chin has been with the Navy Department since 1967, working on a wide range of systems research and development projects including estimation, control, and digital signal processing of self-contained navigation systems for submarine, surface ship, and aircraft. Project assignments have included work on Global Positioning Systems (GPS) and Joint Tactical Information Distribution System (JTIDS).

Course Description -

The main objective of this tutorial is to present an overview of digital signal processing (DSP) techniques and applications with emphasis on the understanding of fundamental concepts and practical utilizations. The building blocks from which DSP techniques were developed will be reviewed first. This is followed by a comprehensive survey of familiar DSP techniques. Next an overview of DSP applications will be presented, encompassing topics such as filtering, spectral analysis, detection, signal reconstruction, image processing, etc. Finally for completeness, a brief report on future trends in DSP techniques and applications will be made.

#### **ADA™ FOR PROJECT MANAGERS**

Anthony B. Gargaro Computer Sciences Corp.

Mr. Anthony B. Gargaro is a lead scientist with Computer Sciences Corporation (CSC) Defense Systems Division and has been a principal contributor to the Ada<sup>™</sup> program since 1978. Mr. Gargaro has participated in activities in both the implementation and use of the Ada<sup>™</sup> language for some years. Currently, he is the vice chairperson of SIGAda and a member of the KAPSE interface team from industry and academia. He has presented this tutorial on many occasions, including to Adatech national conferences.

Course Description -

This course will address what a project manager, who is implementing a program using Ada<sup>™</sup>, needs to know about the language and how to get the most out of Ada<sup>™</sup>. Emphasis will be placed on software productivity and developing quality programs, including presentation, abstraction, encapsulation, synthesis, instantiation, synchronization, and representation. Ada<sup>™</sup> is such a powerful programming language that without an adequate understanding, a project manager could find the program managing the manager. With understanding, Ada<sup>™</sup> can simplify the complexity of managing the program and reduce the cost of implementing the application.

#### OVERVIEW OF ARTIFICIAL INTELLIGENCE

Dr. William B. Gavarter Research Scientist

Dr. Gavarter has spent several years developing an indepth overview of artificial intelligence (Al) and robotics. He has just published a book entitled "Intelligent Machines", Prentiss Hall, covering this material. He was formerly the manager of Automation Research at NASA Headquarters and is now doing research and development on expert systems for NASA Ames Research Center. Dr. Gavarter is a past chairman of the Washington D.C. Chapter of IEEE, Systems, Man, and Cybernetics Society. He is published extensively on Al and robotics.

#### Course Description -

Artificial Intelligence is an emerging technology that has recently attracted considerable publicity. Al is a discipline devoted to developing and applying conceptual approaches to intelligent behavior, or simply put, it's an approach to developing smart computers. Many Al groups and organizations have been formed and applications are under development. This tutorial will provide an overview of Artificial Intelligence which will cover the foundation of Al, the techniques utilized, the applications, the participants, and finally, the state of the art and future trends.

Ada is a registered trademark of the U.S. Government, Ada Joint Program office

# PLENARY SESSION

# "DIGITAL AVIONICS REQUIREMENTS FOR THE 1990'S ..."

## ".... TECHNOLOGY INSERTION ROADMAP"

Bernard A. Zempolich Naval Air Systems Command Headquarters

Since joining the Naval Air Systems Command in 1963, Mr. Zempolich has held positions of increasing responsibility in the areas of computer systems and related software. He is currently acting director of the avionics division at NavAir and technical manager for advanced developments in computer technology, hardware, software, integrated avionic systems and artificial intelligence.

Mr. Zempolich has a bachelors degree in electrical engineering from Catholic University of America. He graduated with distinction from the Industrial College of the Armed Forces and currently teaches computer science at the University of Maryland. Todays advances toward smarter, faster, more modular avionics are pushing the system integrator role into the spotlight. Mr. Zempolich will discuss the integration of avionics with consideration of technology, information fusion, and advanced system architecture impacts. The talk will address key issues such as fault tolerance and reconfiguration, integration of subsystems from an electronic/mechanical viewpoint, and the utilization of VLSI components.

### "... TOTAL WEAPON SYSTEM VIEW"

Phillip O. Brown McDonnell-Douglas Corp.

Mr. Brown is Chief Program Engineer, Electronic Systems. He holds a BSEE, MSEE, and Professional Degree in Electrical Engineering from the University of Missouri at Rolla. As ASA Project Manager, Mr. Brown also has cognizance of VHSIC insertion (Pave Sprinter) and related IRAD effort. His previous areas of responsibility have been in the avionics systems associated with advanced USAF and USN aircraft; and with electronic attack and radiating sybsystem technologies for advanced concepts. Mr. Brown had direct responsibility for the F-15 avionics system performance analyses, as well as the development of equations for the integrated control of sensors, displays, and weapons in the many modes required for weapon system effectiveness. Mr. Brown is Chairman, Avionics Section of the Air Armament Division of the American Defense Preparedness Association, a member of the IEEE, Tau Beta Pi, Eta Kappa Nu, and the Academy of Electrical Engineers at University of Missouri at Rolla.

An Avionics System definition derived from Weapon System Mission Requirements and the subsequent development of the Weapon System is of vital interest to the aircraft prime inasmuchas the total Weapon System Performance Responsibility resides with the prime. This interest is brought about by the strong effect the Avionics System has on the performance, availability, combat effectiveness, and life cycle cost associated with the Weapon System. Key to countering the 1990's threat while remaining compatible with the projected economics and human resources available will be the on-board digital Avionics Systems. This presentation addresses the significance of the 1990 digital avionics in the areas of: 1) Development - hardware/software complexity, testability; 2) Production - new technology integration, standardization; 3) Supportability - on-off aircraft maintenance, reduced spares types; and 4) Affordability - all of the previous areas.

XXVIII

## "... THE FUTURE OF DEFENSE AND SPACE SYSTEMS"

**R. Noel Longuemare** Westinghouse Electric Corp.

Since joining Westinghouse in 1952, Mr. Longuemare has held positions in design engineering, line and project management, and has played a leading role in the development of modern radar and avionics systems for airborne and land mobile applications.

He was heavily involved in managing the introduction of digital computers and digital signal processors into these systems, and in formulating the systems architecture and philosophy for the Westinghouse Modular Radar Series now successfully implemented on several frontline Westinghouse programs.

His current management responsibilities include the development of advanced sensors and avionic systems, as well as key technology programs such as VHSIC and advanced signal processing. He is also responsible for managing the engineering department at the Westinghouse Defense complex near BWI Airport. He holds 8 patents and 17 patent disclosures, and is active in numerous technical and industrial societies in the avionics and military electronics field.

Mr. Longuemare holds a BSEE from the University of Texas at El Paso and an MSE from Johns Hopkins University. He has also completed the Stanford University executive program.

As we move into next generation Avionic Systems for the Department of Defense and other Government Agencies we see requirements for unattended systems, faster system reaction times, lower life cycle costs, shorter concept-todeployment times, and fault reconfigurable systems for greater operational availability. These requirements demand new architectural approaches beyond those of todays digital Avionics Systems. New information flow concepts for interconnecting computing and processing subsystems, sensors, control and displays must be developed. Studies underway indicate the need for several levels of bussing, some with bandwidths several orders of magnitude higher than todays bussing speeds. To lower life cycle costs, standard modules compatible with generic system functions and partitioned to permit built in fault tolerance through rapid reconfigurable functions, will evolve. A major thrust will be the development of survivable systems emphasizing sensor fusion and integrated functions using a common processing approach.

Eugene C. Machacek Rockwell International

(n) (n)

s al

# **1<sup>ST</sup> DIGITAL AVIONICS SYSTEMS AWARE**

### CITATION

Spradlin, Sutcliffe, Peak and McDonald were the senior managers in the 767 Flight Management Systems Program organization. They were responsible for leading the combined project Engineering and Staff Task Force that directed the specification, design, development, test and certification of the new 757/767 digital avionics subsystems.

Richard E. Spradlin Chief Design Engineer-Avionics/ Everett Division

Dick joined Boeing in 1954. He has held staff positions on the SST, 707, 727, 737. He is currently Senior Staff manager responsible for the design, development and certification of Flight Management Systems for the 757 and 767 airplane.

Richard A. Peal Chief Design Engineer - Avionic Renton

During his 27 years of service, Dick has worked on the following programs: B52, WS-324A, C5A, SST, 707/727/737, 747, 757 and 767. He was Senoir Project engineer on the FMS Systems, E/E Systems, and Flight Deck.

Peter L. Sutcliffe Chief Design Engineer-FMS/ Avionics

Peter joined Boeing in 1974 as Manager of Advanced design. In 1980, he became Deputy Manager-Systems Integration of 757/767 Flight Management Systems and later became Program Manager-757/767 Flight Management Systems.

Robert E. McDonald Director-Engineering Research

During his 25 years at Boeing, Bob has worked of the 747 Program as Chief of Test and Director Techni cal Integrity-New Airplane Program. In 1979 Bob wa assigned as Chief Engineer responsible for develop ment of a common Flight Management System for th 757 and 767.

757/767 Flight Dec

XXX

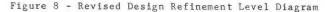

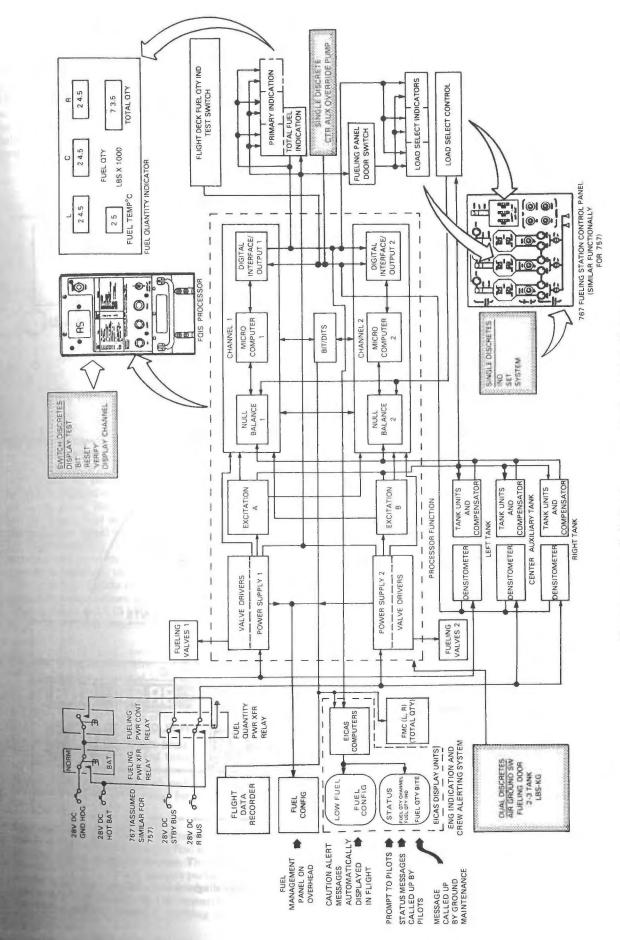

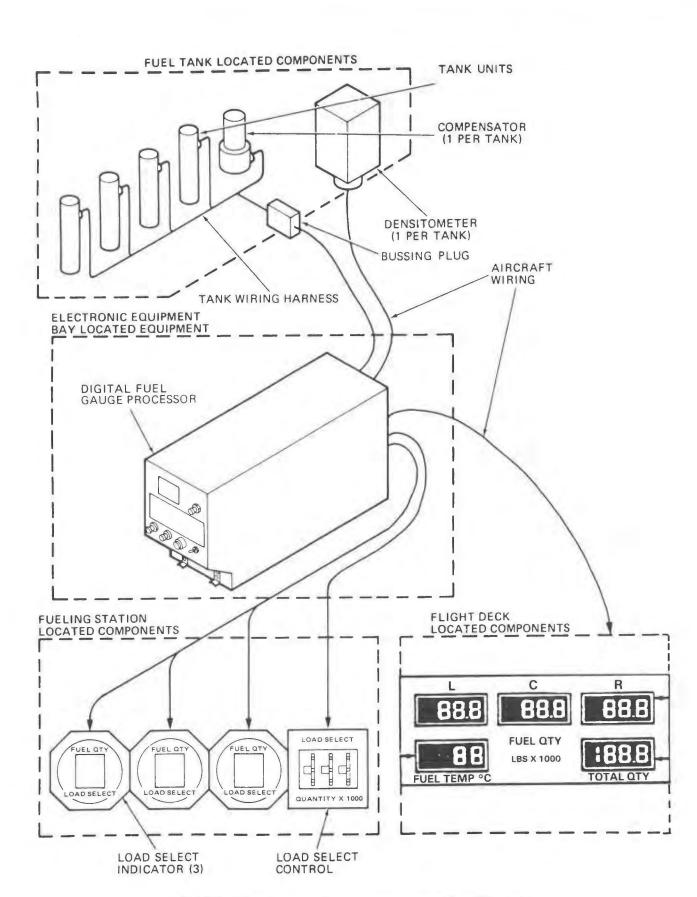

# PANEL DISCUSSION NATIONAL AIRSPACE SYSTEMS PLAN —