## United States Patent [19]

Riseman

4,169,000 [11]

Sep. 25, 1979 [45]

| [54] | METHOD OF FORMING AN INTEGRATED |

|------|---------------------------------|

|      | CIRCUIT STRUCTURE WITH          |

|      | FULLY-ENCLOSED AIR ISOLATION    |

| [75] | Inventor: | Jacob | Riseman, | Poughkeepsie, | N.Y. |

|------|-----------|-------|----------|---------------|------|

|------|-----------|-------|----------|---------------|------|

| [73] | Assignee: | International | <b>Business</b> | Machines |

|------|-----------|---------------|-----------------|----------|

|      | _         | Cornoration.  | Armonk.         | N.Y.     |

[21] Appl. No.: 904,713

[22] Filed: May 10, 1978

### Related U.S. Application Data

| [62] | Division  | of | Ser. | No. | 719,888, | Sep. | 2, | 1976, | Pat. | No. |

|------|-----------|----|------|-----|----------|------|----|-------|------|-----|

|      | 4,106,050 | ). |      |     |          |      |    |       |      |     |

| [51] | Int. Cl. <sup>2</sup> | <br>H01L | 21/306; | H01L     | 21/76   |

|------|-----------------------|----------|---------|----------|---------|

| řeo. | TIC CI                |          | 140 /10 | 7. 20 /6 | 76 337. |

| [52] |               | 148/187; 29/576 W;           |

|------|---------------|------------------------------|

|      |               | ; 148/175; 156/645; 156/648; |

|      | 156/659; 156, | /662; 357/49; 357/50; 357/55 |

[58] Field of Search ...... 148/1.5, 175, 187; 156/645, 648, 657, 659, 662; 29/576 W, 580, 589; 357/47, 49, 50, 55

[56] References Cited

## U.S. PATENT DOCUMENTS

| 3,300,832 | 1/1967 | Cave |  | 357/49 | X |

|-----------|--------|------|--|--------|---|

|-----------|--------|------|--|--------|---|

| 3,332,137 | 7/1967 | Kenney         | 29/589 X |

|-----------|--------|----------------|----------|

| 3,341,743 | 9/1967 | Ramsey         | 357/49 X |

| 3,343,255 | 9/1967 | Donovan        |          |

| 3,381,369 | 5/1968 | Stoller        | 29/580   |

| 3,489,961 | 1/1970 | Frescura et al | 357/49 X |

| 3,689,992 | 9/1972 | Schutze et al  | 29/580 X |

| 3,787,710 | 1/1974 | Cunningham     | 357/49 X |

Primary Examiner-R. Dean Assistant Examiner-W. G. Saba

Attorney, Agent, or Firm-Theodore E. Galanthay

#### **ABSTRACT** [57]

A method for forming a fully-enclosed air isolation structure which comprises etching a pattern of cavities extending from one surface of a silicon substrate into the substrate to laterally surround and electrically isolate said plurality of substrate pockets, and then forming a first layer of silicon dioxide on said first substrate surface. Next, a planar second layer comprising silicon dioxide is formed over a second silicon substrate, after which this planar layer is fused to said silicon dioxide layer to thereby fully enclose said cavities. Then, the second silicon substrate is removed.

### 7 Claims, 8 Drawing Figures

FIG. 4A

FIG. 5

FIG. 6

FIG. 7

2

## METHOD OF FORMING AN INTEGRATED CIRCUIT STRUCTURE WITH FULLY-ENCLOSED AIR ISOLATION

This is a division of application Ser. No. 719,888 filed 9/2/76, now U.S. Pat. No. 4,106,050.

### BACKGROUND OF THE INVENTION

The present invention relates to integrated circuit 10 structures and more particularly to dielectric isolation in such integrated circuit structures, particularly by air-isolation.

The form of most existing integrated circuits is the so-called monolithic form. Such a structure contains 15 great numbers of active and passive devices in a block or monolith of semiconductor material. Electrical connections between these active and passive devices are generally made on a surface of the semiconductor block of material. Until recently, junction isolation has been 20 by far the most widely practiced manner of isolating devices or circuits in the integrated circuit from each other. For example, active P-type diffusions are customarily used to isolate conventional FET and bipolar devices from one another and from other devices such as 25 the resistors and capacitors. Such junction isolation is also used in integrated circuits utilizing field effect transistor devices. More detailed descriptions of junction isolation may be found in U.S. Pat. Nos. 3,319,311; 3,451,866; 3,508,209 and 3,539,876.

Although junction isolation has provided excellent electrical isolation in integrated circuits which have functioned very effectively over the years, at the present stage of the development of the integrated circuit art, there is an increasing demand in the field of digital 35 integrated circuits for faster switching circuits. It has long been recognized that the capacitive effect of the isolating P-N junctions has a slowing effect on the switching speed of the integrated circuits. Until recently, the switching demands of the integrated circuits 40 have been of a sufficiently low frequency that the capacitive effect in junction isolation has presented no major problems. However, with the higher frequency switching demand which can be expected in the field in the future, the capacitive effect produced by junction 45 isolation may be an increasing problem. In addition, junction isolation requires relatively large spacing between devices, and, thus, relatively low device densities which is contrary to higher device densities required in large scale integration. Junction isolation also tends to 50 give rise to parasitic transistor effects between the isolation region and its two abutting regions. Consequently, in recent years there has been a revival of interest in integrated circuits having dielectric isolation instead of junction isolation. In such dielectrically isolated cir- 55 cuits, the semiconductor devices are isolated from each other by insulative dielectric materials or by air.

Conventionally, such dielectric isolation in integrated circuits has been formed by etching channels in a semi-conductor member corresponding to the isolation regions from the back side of the member, i.e., the side opposite to the planar surface at which the devices and wiring of the integrated circuit are to be formed. This leaves an irregular or channeled surface over which a substrate back side, usually a composite of a thin dielectric layer forming the interface with the semiconductor member covered by a thicker layer of polycrystalline silicon is deposited. Alternatively, the polycrystalline

silicon need not be deposited in which case, the channels would provide air-isolation. Next, the other or planar surface of the semiconductor member may be either mechanically ground down or chemically etched 5 until the bottom portions of the previously etched channels are reached. This leaves the structure wherein a plurality of pockets of semiconductor material surrounded by a thin dielectric layer are either supported on a polycrystalline silicone substrate and separated from each other by the extensions of the polycrystalline substrate or in the absence of the polysilicon, a structure in which the pockets of semiconductor material are, in effect, "air-isolated" from each other. While such structures provide an essentially flat and thus wirable planar surface of coplanar pockets of semiconductor material, such integrated circuit structures have limited utility with integrated circuits of high device densities. This is due to the fact that the etched channels which correspond to the isolation regions must be formed from the back side of the integrated circuit substrate and etched until the level of the active planar surface of the substrate is reached.

It is recognized in the art that when etching from the back side of an integrated circuit member the etching must be made to greater depth than when etching directly from the planar front surface in order to insure uniform lateral isolation. It is also recognized that when etching through a member, the extent of lateral etching will be substantially the same as the depth of etching. Accordingly, when etching channels from the back side of the substrate, so much lateral "real estate" is consumed on the wafer that such an approach has very limited practicality in high density integrated circuits.

On the other hand, if the etching to form the channels in the above dielectric isolation or air-isolation structure is carried out from the active or front surface of the integrated circuit, only limited lateral etching is necessary to reach practical isolation depths. However, the result is an essentially corrugated active surface rather than a planar one. Such a corrugated active surface is, of course, difficult to wire, i.e., form integrated circuit metallurgy interconnections by conventional photolithographic integrated circuit fabrication techniques.

Another approach which has been utilized for forming lateral dielectric isolation in the art involves the formation of recessed silicon dioxide lateral isolation regions, usually in the epitaxial layer where the semiconductor devices are to be formed, through the expedient of first selectively etching a pattern of recesses in the layer of silicon, and then thermally oxidizing the silicon in the recesses with appropriate oxidation blocking masks, e.g., silicon nitride masks, to form recessed or inset regions of silicon dioxide which provide the lateral electrical isolation. Representative of the prior art teaching in this area are U.S. Pat. No. 3,648,125 and an article entitled, "Locos Devices", E. Kooi et al, Philips Research Report 26, pp. 166–180 (1971).

While this approach has provided both planarity at the active device integrated circuit surface as well as good lateral dielectric isolation, it has encountered some problems. Originally, the art applied the silicon nitride masks directly onto the silicon substrates. This gave rise to problems associated with high stresses created on the underlying silicon substrate by the silicon nitride-silicon interface. Such stresses were found in many cases to produce dislocations in the silicon substrate which appear to result in undesirable leakage current pipes and otherwise adversely affect the electri-

4

cal characteristics of the interface. In order to minimize such interface stresses with silicon nitride layers, it has become the practice in the art to form a thin layer of silicon dioxide between the silicon substrate and the silicon nitride layer. During such thermal oxidation, 5 there is a substantial additional lateral penetration of silicon oxide from the thermal oxidation beneath the silicon nitride. This lateral penetration is greatest at the mask-substrate interface to provide a laterally sloping structure known and recognized in the prior art as the 10 undesirable "bird's beak".

The publications, "Local Oxidation of Silicon; New Technological Aspects", by J. A. Appels et al, Philips Research Report 26, pp. 157-165, June 1971, and "Selective Oxidation of Silicon and its Device Application", E. Kooi et al, Semiconductor Silicon 1973, published by the Electrochemical Society, Edited by H. R. Huff and R. R. Burgess, pp. 860-879, are representative of the recognition in the prior art of the "bird's beak" problems associated with silicon dioxide-silicon nitride 20 composite masks, particularly when used in the formation of recessed silicon dioxide by thermal oxidation. Because of such "bird's beak" problems, the art has experienced some difficulty in achieving well-defined lateral isolation boundaries.

In addition, while, as previously mentioned, air isolation has been used in the prior art in integrated circuits, no practical approach has been developed for the application of air isolation to high density, large scale integrated circuits.

### SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to provide an air-isolated integrated circuit structure with a planar wirable surface.

It is another object of the present invention to provide an air-isolated integrated circuit structure in which the air isolation regions are of minimal dimensions so that the integrated circuit structure is adaptable to high-device density integrated circuits.

It is a further object of the present invention to provide an air-isolated integrated circuit structure in which both the upper and lower surfaces of the structure are planar.

It is yet a further object of the present invention to 45 provide a dielectrically isolated integrated circuit structure in which both upper and lower surfaces are planar and which is substantially free from stresses created by changes in volume in the semiconductor material during integrated circuit fabrication heating steps.

It is an even further object of the present invention to provide a method for fabricating an integrated circuit structure having the above described advantages.

In accordance with the present invention, there is provided an integrated circuit member comprising a 55 semiconductor substrate having formed therein a pattern of cavities extending from one surface of the substrate into the substrate and fully enclosed within the member, a plurality of pockets of semiconductor material extending from said surface laterally surrounded 60 and electrically insulated by said cavities and a planar layer of electrically insulative material on the surface.

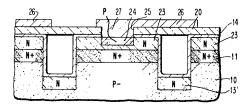

The integrated circuit member is formed by a fabrication method comprising first etching a pattern of cavities extending from one surface of a first silicon sub-65 strate into the substrate; the cavities laterally surround and electrically isolate the plurality of silicon substrate pockets. Next, a first layer of silicon dioxide is formed

on this first substrate surface. There is also formed over a second silicon substrate a planar second layer comprising a glass, and preferably a siliceous glass. The glass composition may be any conventional glass composition including those described in Volume 10, pp. 533-546, of the Encyclopedia of Chemical Technology, Kirk and Othmer, Second Edition, published in 1966 by Interscience Publishers. However, the silicate glasses, such as those described on pp. 540-545 in the above encyclopedia, have been found to be particularly desirable. The term "siliceous glass" as used in this application, is meant to include all silica-containing glasses including glasses which are substantially unmodified silica (SiO<sub>2</sub>). In addition, among the silicate glasses which may be used are alkali silicate glasses which are modified by Na<sub>2</sub>O, soda-lime glasses, borosilicate glasses, alumino-silicate glasses, and lead glasses. Then, the two substrates are bonded together by fusing the planar layer over the second substrate to the silicon dioxide layer over the first substrate to thereby fully enclose the cavities. Finally, the second silicon substrate is removed from the fused structure.

The resulting structure is one having a planar surface, at which the active devices of the integrated circuit may be subsequently formed, i.e., the surface of the first silicon substrate covered by the planar layer of silicon dioxide. Further, since the cavities have been formed by etching down from this surface rather than the back side surface of the structure, only minimal lateral integrated circuit "real estate" has been consumed in forming such cavities. In addition, the back side surface of the structure remains unetched and thus planar. Finally, because of the fully enclosed air-isolation, the structure has cavities capable of absorbing changes in volume of the silicon material resulting from the application of heat during the processing steps. Thus, heat-induced stresses are minimized.

The foregoing and other objects, features and advantages of the invention will be apparent from the following more particular description of the preferred embodiments of the invention, as illustrated in the accompanying drawings.

### BRIEF DESCRIPTION OF THE DRAWINGS

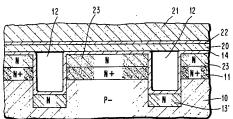

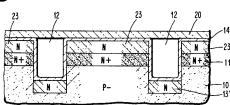

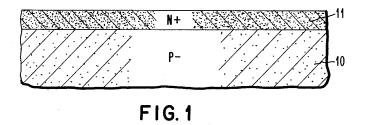

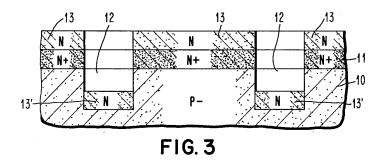

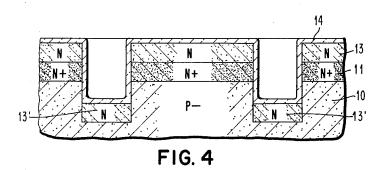

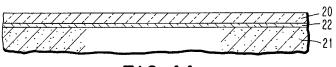

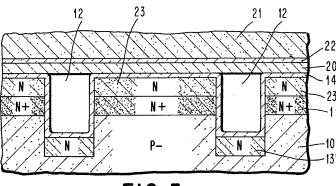

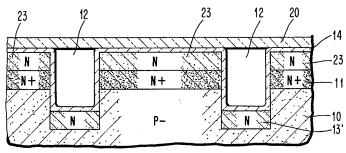

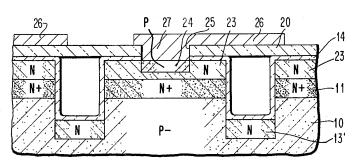

FIGS. 1-7 are diagrammatic sectional views of a portion of an intregrated circuit in order to illustrate the method of forming the preferred embodiment of the present invention.

## PREFERRED EMBODIMENTS OF THE PRESENT INVENTION

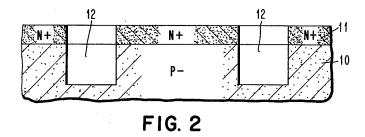

FIGS. 1-7 illustrate the preferred embodiment of the present invention. On a suitable P- wafer 10 having a resistivity of 10 ohm/cm, an N+ region 11 which will subsequently serve as a subcollector is formed by conventional thermal diffusion of impurities as set forth for example in U.S. Pat. No. 3,539,876. When introduced into substrate 10, N+ region 11 has a surface concentration of 10<sup>21</sup> atoms/cm<sup>3</sup>. Region 11 may also be formed by conventional ion implantation techniques.

Then, FIG. 2, a pattern of recesses or cavities 12 are etched in the substrate. This pattern of recesses corresponds to the desired air-isolation pattern for the integrated circuit structure. Recesses 12 are formed by etching utilizing a conventional mask such as a silicon dioxide mask formed by standard photolithographic integrated circuit fabrication techniques which mask has apertures corresponding to the recessed pattern to

# DOCKET

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.