Matsuda et al.

[45]

Dec. 26, 1978

| [54]                               | ISOLATED<br>MATERIAI  | DUCTOR INTEGRATED CIRCUIT<br>THROUGH DIELECTRIC<br>AND A METHOD FOR<br>TURING THE SAME |  |  |  |

|------------------------------------|-----------------------|----------------------------------------------------------------------------------------|--|--|--|

| [75]                               |                       | Takashi Matsuda; Kazuo Niwa;<br>Yasusuke Sumitomo, all of<br>Yokohama, Japan           |  |  |  |

| [73]                               |                       | Tokyo Shibaura Electric Co., Ltd.,<br>Tokyo, Japan                                     |  |  |  |

| [21]                               | Appl. No.:            | 735,784                                                                                |  |  |  |

| [22]                               | Filed:                | Oct. 26, 1976                                                                          |  |  |  |

| [30]                               | Foreign               | Application Priority Data                                                              |  |  |  |

| Oct. 25, 1975 [JP] Japan 50-128773 |                       |                                                                                        |  |  |  |

| [51]                               | Int. Cl. <sup>2</sup> | <b>H01L 27/12;</b> H01L 29/78;<br>H01L 27/02; H01L 29/04                               |  |  |  |

| [52]                               | U.S. Cl               | <b>357/49;</b> 357/23;                                                                 |  |  |  |

| [58]                               | Field of Sea          | 357/41; 357/59; 357/67; 29/571 rch 357/23, 41, 49, 59, 357/67                          |  |  |  |

| [56]                               |                       | References Cited                                                                       |  |  |  |

|                                    | U.S. P                | ATENT DOCUMENTS                                                                        |  |  |  |

6/1965

3,191,061

Weimer ...... 357/41

| 3,381,182<br>3,407,479<br>3,475,664<br>3,514,676<br>3,602,981<br>3,865,649<br>3,874,918 | 4/1968<br>10/1968<br>10/1969<br>5/1970<br>9/1971<br>2/1975<br>4/1975 | Thornton      | 357/49<br>357/42<br>357/49<br>357/42<br>357/49 |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------|------------------------------------------------|

|                                                                                         | _,                                                                   | Nechtow et al | 357/49                                         |

Primary Examiner—William D. Larkins

Assistant Examiner—Gene M. Munson

Attorney, Agent, or Firm—Oblon, Fisher, Spivak,

McClelland & Maier

## [57] ABSTRACT

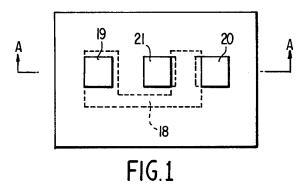

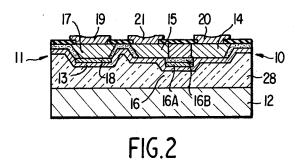

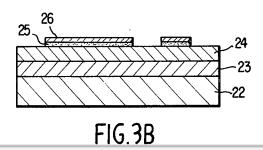

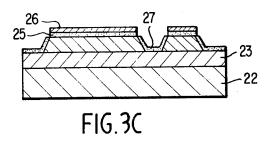

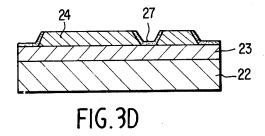

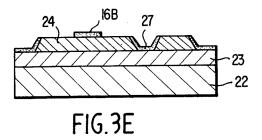

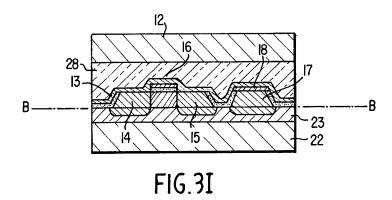

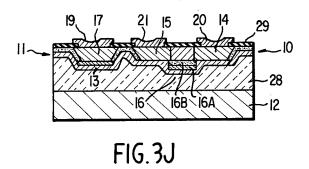

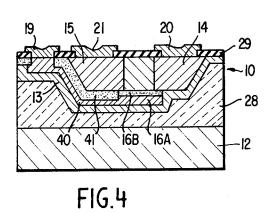

A semiconductor integrated circuit includes first and second island regions, surrounded by a bottomed dishlike dielectric layer formed on one side of a support body. A MOS transistor element is formed in the first island region, whose gate region is located at the bottom side of the island region. The gate electrode is connected to a bottom portion of the second island region, which is used as a gate electrode contact region, in the support body using a interconnection lead. There is a method for manufacturing the above device.

## 6 Claims, 13 Drawing Figures

### SEMICONDUCTOR INTEGRATED CIRCUIT ISOLATED THROUGH DIELECTRIC MATERIAL AND A METHOD FOR MANUFACTURING THE SAME

### BACKGROUND OF THE INVENTION

#### Field of Invention

This invention relates to a semiconductor integrated circuit whose island region is electrically isolated through a dielectric layer, and a method for manufacturing the same.

### Description of the Prior Art

It is known that a digital integrated circuit using 15 Metal Oxide Semiconductor Transistor (hereinafter referred to merely as MOS transistor) is superior to a circuit using bipolar transistors in such points as integration density, power consumption and ease of manufac-

However, in operating speed, the former is inferior to the latter. To overcome this shortcoming of the MOS integrated circuit, namely to increase the operating speed, the SOS (Silicon on Sapphire or Spinel) technique was recently developed. This technique is as fol- 25 lows: after growing a silicon layer having 1 µm thickness on one surface of sapphire monocrystalline substrate by using epitaxial process, a selective etching is made to remove the epitaxial layer selectively, leaving some portions where circuit elements are formed. This 30 technique has some merits as follows compared with the conventional one.

1) High speed of the circuit operation owing to the decrease of parastic capacitance according to the decrease of PN junctions.

2) High integration density of the integrated circuit owing to the decrease of the area of isolation region between circuit elements. However, this SOS technique is accompanied with such inconvenient phenomenon as lattice defects owing to the difference of lattice constant 40 and crystal construction between silicon and sapphire, occurrence of aluminum impurity by reaction of the sapphire substrate with silicon layer and warp of the sapphire substrate owing to the difference of the expansion coefficients of both. These increase the leakage 45 current of the device two to three fold compared with bulk silicon's, which makes the power consumption high. Furthermore, the carrier mobility becomes smaller sharply, and accordingly, the operating speed of is difficult to apply this SOS technique to CMOS (Complementary Metal Oxide Semiconductor) circuit and the Dynamic circuit.

On the other hand conventionally known is a semiconductor integrated circuit in which an electrical insu- 55 manufacturing a semiconductor integrated circuit comlation is made between semiconductor elements using a dielectric layer. A plurality of semiconductor elements of the integrated circuit are arranged at a predetermined interval on one side of a semiconductor polycrystalline layer, and a dielectric layer or insulator separation layer 60 is formed in a manner to insulate the semiconductor elements from the polycrystalline layer. In this integrated circuit, the floating capacitance is very small, so that high break down voltage is obtained. Accordingly the abovementioned technique is especially used in the 65 gion in second island region so as to reach to the bottom bipolar integrated circuit in which the thickness of monocrystalline layer is about 3 µm to 10 µm, so that therefore, the scatter of the thickness is of little matter.

However in the MOS integrated circuit, the thickness of the monocrystalline layer is about 1 µm. Accordingly it is very difficult to make the thickness constant within a scattering value of  $\pm 0.1 \, \mu m$  using a lapping method or an etching process. Therefore, application of this technique to the MOS integrated circuit is very diffi-

Furthermore, in the process where a polycrystalline layer is formed by gas phase growth, at first the size of a polycrystalline particle is small. However it becomes larger and larger with the advance of the polycrystalline growth, which causes a warp of the semiconductor substrate owing to the difference of the expansion coefficient of the polycrystalline layer in the direction of its depth. Furthermore, warping occurs also owing to the difference of expansion coefficient between the polycrystalline layer and the monocrystalline layer in which the semiconductor element is formed. This warp of the semiconductor substrate is difficult to be got rid of, and make the subsequent photoetching process difficult.

For these reasons, the prior art as above mentioned is unsuitable for manufacturing the semiconductor integrated circuit.

#### SUMMARY OF THE INVENTION

This invention overcomes the problems arising from the processing sequence and the construction of the prior art wherein the polycrystalline layer is grown by gas phase.

One object of this invention is to provide a method capable of easily manufacturing a semiconductor integrated circuit isolated through dielectric material.

Another object of this invention is to provide a semiconductor integrated circuit having an island region isolated through dielectric material, and having a MOS transistor element in the island region, whose gate region is located at the bottom side of the island region.

Yet another object of this invention is to provide a semi-conductor integrated circuit without warp of the support body.

Further object of this invention is to provide a semiconductor integrated circuit whose power consumption is small and operating speed is very high.

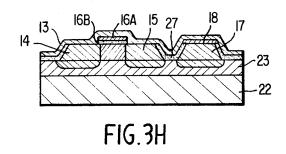

In one aspect of this invention, a semiconductor integrated circuit comprises a support body, at least one bottomed enclosed dielectric layer whose one end is open at one surface of the support body forming an island region, a MOS transistor element in the island the integrated circuit is decreased. For these reasons, it 50 region having source, drain and gate regions, wherein said source and drain regions are formed adjacent to said one surface of the support body and the gate region is formed at a bottom portion of the island region.

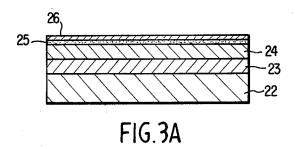

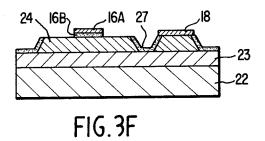

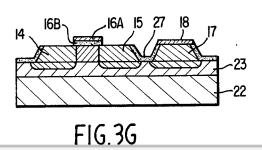

In another aspect of this invention, a method for prises the steps of: forming a mask layer on one side surface of first semiconductor substrate having first conductivity; removing at least two portions of the mask layer; etching the semiconductor substrate down to a predetermined depth through the exposed portions thereof to form first and second mesa regions; forming a gate insulating layer at a portion on the top surface of the first mesa region; forming source and drain regions in the first mesa region and gate electrode contact reof the mesa regions respectively, by diffusing an impurity having second conductivity type forming a gate electrode on said gate insulating layer and an intercon-

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

# API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

## **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

## **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

# **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.