## United States Patent [19]

Rathmann

### [54] BATTERY PACK AND A METHOD FOR MONITORING REMAINING CAPACITY OF A BATTERY PACK

- [76] Inventor: Roland Rathmann, Raiffeisenweg 3, B-85375 Neufahrn, Germany

- [21] Appl. No.: 09/087,306

- May 29, 1998 [22] Filed:

## **Related U.S. Application Data**

- Division of application No. 08/890,665, Jul. 9, 1997, Pat. No. 5,794,592 [62]

- [60] Provisional application No. 60/021,905, Jul. 17, 1996, and provisional application No. 60/034,320, Dec. 20, 1996.

- [51] Int. Cl.<sup>6</sup> ..... H02J 7/00

- 324/427; 324/428 [58] Field of Search ..... ... 320/136, 157,

320/132; 324/427, 428

#### [56] **References Cited**

### U.S. PATENT DOCUMENTS

| 4,040,247 | 8/1977  | Haydon .      |

|-----------|---------|---------------|

| 4,122,359 | 10/1978 | Breikss .     |

| 4,238,839 | 12/1980 | Redfern et al |

| 4,289,836 | 9/1981  | Lemelson .    |

| 4,354,148 | 10/1982 | Tada et al    |

| 4,380,726 | 4/1983  | Sado et al    |

| 4,392,101 | 7/1983  | Saar et al    |

| 4,433,278 | 2/1984  | Lowndes et al |

| 4,455,523 | 6/1984  | Koenck .      |

| 4,553,081 | 11/1985 | Koenck .      |

| 4,709,202 | 11/1987 | Koenck et al  |

| 4,746,854 | 5/1988  | Baker et al   |

| 4,803,416 | 2/1989  | Abiven et al  |

| 4,885,523 | 12/1989 | Koenck .      |

| 4,918,368 | 4/1990  | Baker et al   |

| 4,947,123 | 8/1990  | Minezawa .    |

| 4,961,043 | 10/1990 | Koenck .      |

| 4,965,738 | 10/1990 | Bauer et al   |

| 5,043,651 | 8/1991  | Tamura .      |

| 5,136,246 | 8/1992  | Sakamoto .    |

|           |         |               |

## US005955869A

#### 5,955,869 **Patent Number:** [11]

#### **Date of Patent:** Sep. 21, 1999 [45]

| 5,180,961 | 1/1993  | Tsujino .               |  |

|-----------|---------|-------------------------|--|

| 5,198,743 | 3/1993  | McClure et al           |  |

| 5,200,689 | 4/1993  | Interiano et al         |  |

| 5,206,097 | 4/1993  | Burns et al             |  |

| 5,248,929 | 9/1993  | Burke .                 |  |

| 5,254,928 | 10/1993 | Young et al             |  |

| 5,278,487 | 1/1994  | Koenck .                |  |

| 5,284,719 | 2/1994  | Landau et al            |  |

| 5,287,286 | 2/1994  | Ninomiya .              |  |

| 5,295,078 | 3/1994  | Stich et al             |  |

| 5,315,228 | 5/1994  | Hess et al              |  |

| 5,321,627 | 6/1994  | Reher .                 |  |

| 5,325,041 | 6/1994  | Briggs .                |  |

| 5,341,084 | 8/1994  | Gotoh et al             |  |

| 5,349,282 | 9/1994  | McClure .               |  |

| 5,349,535 | 9/1994  | Gupta.                  |  |

| 5,350,993 | 9/1994  | Toya et al              |  |

| 5,350,996 | 9/1994  | Tauchi .                |  |

| 5,455,499 | 10/1995 | Uskali et al            |  |

| 5,541,489 | 7/1996  | Dunstan .               |  |

| 5,549,671 | 8/1996  | Duley .                 |  |

| 5,565,759 | 10/1996 | Dunstan .               |  |

| 5,606,242 | 2/1997  | Hull et al 320/106      |  |

| 5,614,804 | 3/1997  | Kayano et al            |  |

| 5,617,324 | 4/1997  | Arai .                  |  |

| 5,633,573 | 5/1997  | Van Phouc et al 320/128 |  |

Primary Examiner-Peter S. Wong

Assistant Examiner-Gregory J. Toatley, Jr.

Attorney, Agent, or Firm-Scully, Scott, Murphy & Presser

#### [57] ABSTRACT

A battery pack and a method of monitoring remaining capacity of a battery pack. With this method, two different procedures are used to estimate that remaining capacity. In a first procedure, data generated on the battery pack is used to estimate remaining battery capacity; and in the second procedure, data transmitted to the battery pack from a host device is used to estimate remaining battery capacity. The battery pack switches between these two procedures under defined conditions; and for example, with the preferred embodiment described in detail in the present specification, the battery pack switches from the first procedure to the second procedure when the battery current falls below a threshold value.

### 8 Claims, 58 Drawing Sheets

F I G. I

FIG.5A

FIG.5B

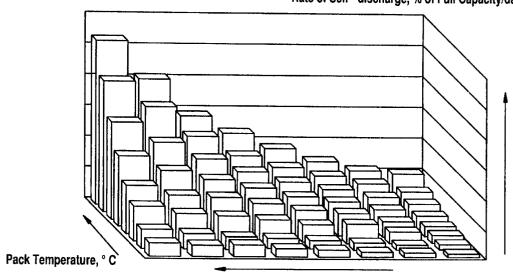

FIG.12B

Rate of Self - discharge, % of Full Capacity/day

Full Capacity, percent of Design Capacity

FIG.13B

Residual Capacity at EOD, % of Full Capacity

## RC\_Oscillator\_adjust

Sheet 25 of 58

5,955,869

Sheet 27 of 58

FIG.36

RC\_Oscillator\_adjust

Sheet 41 of 58

Sheet 50 of 58

Sheet 56 of 58

40

50

## **BATTERY PACK AND A METHOD FOR** MONITORING REMAINING CAPACITY OF A BATTERY PACK

This application is a divisional of application Ser. No. 5 08/890,665, filed Jul. 9, 1997 now U.S. Pat. No. 5,794,592. This application claims benefit of Provisional Application Ser. No. 60/021,905 filed Jul. 17, 1996 and Provisional Application Ser. No. 60/034,320 filed Dec. 20, 1996.

### FIELD OF THE INVENTION

The present invention relates generally to the art of rechargeable batteries and more specifically to a smart battery for use in an intelligent device having power man-15 agement capabilities. The invention is a smart battery apparatus for controlling the operation of rechargeable Lithium Ion (LiIon), Nickel Metal Hydride (NiMH), or Nickel Cadmium (NiCad) batteries, and the like, to enable the reporting of accurate information to the intelligent device for power 20 management and charge control specific to the battery's state of charge and chemistry.

# DESCRIPTION OF THE PRIOR ART

The advent of intelligent portable electronic devices such 25 as notebook computers, video cameras, cellular phones has enabled the development of smart rechargeable batteries that can communicate with the intelligent device to provide accurate information on the battery's present state of charge, and how best to recharge the battery to maintain maximum 30 a single positive power supply that is capable of bipolar battery life, thus enabling the highest number of chargedischarge cycles. A user of such intelligent portable devices utilizing such smart batteries will not only know how much charge is left in the battery, but battery run time at various rates of power consumption. This enables the user to select 35 a mode of operation that will enable maximum service life on the remaining state of charge and, how long the device will continue to operate.

Prior art rechargeable battery units have been provided with means for generating some desired information to their users, including for instance, a charge monitor and fuel gauge such as that disclosed in U.S. Pat. No. 5,315,228 which discloses a method for calculating state of charge and reporting run time to empty to the host computer system.

However, there is a need for a rechargeable power unit that will accurately maintain its own state of charge information even when nominally fully discharged such that a user will have instantaneous access thereof. Moreover, there is also a need for an intelligent rechargeable battery that can provide the user with an accurate prediction of its remaining operating time at various levels of power consumption. The user of such an intelligent device, such as a portable computer, can thus elect to power down a hard disk drive to extend the operation of the portable computer for a longer period of time than would have been possible at the higher rate of power consumption.

## SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to 60 provide a smart battery device for use with a rechargeable battery to be installed in a host computer that will optimize the performance of the rechargeable battery throughout its life cycle.

smart battery device that includes a microprocessor for controlling a rechargeable battery that performs battery 2

capacity calculations for communication to a host computer device or a smart battery charge device.

It is still another object of the instant invention to provide a smart battery device that includes a microprocessor for controlling a rechargeable battery and that provides intelligence in the form of present state of charge and battery charge parameters to a host device for communication to a smart charger.

It is yet still a further object of the instant invention to provide a smart battery device that includes a microprocessor for controlling a rechargeable battery that monitors battery operating parameters such as voltage, current, and temperature to thereby enable either a rapid charging rate or an optimal charging rate from any charged state.

Still yet another object of the instant invention is to provide a smart battery device that includes a microprocessor for controlling a rechargeable battery that calculates predictive data such as the battery's remaining life at the current rate of drain and at alternate rates of drain.

It is still a further object of the instant invention to provide a smart battery device that is an application specific integrated circuit (ASIC) having analog and digital components.

Furthermore, another object of the present invention is to provide a smart battery device that includes an analog to digital (A/D) converter for measuring battery charge parameters such as voltage, current, and temperature.

Yet still another object of the present invention is to provide a smart battery device having an A/D converter with operation for converting both positive and negative analog signals representing battery charge and discharge currents, respectively.

Another object of the instant invention is to provide a smart battery device as above wherein the analog and digital components of the ASIC comprise CMOS semiconductor technology designed for improved accuracy, and high A/D converter resolution with minimal power consumption.

Still another object of the present invention is to provide a smart battery device having a microprocessor such that, when nominally discharged, will place itself in a sleep mode with virtually no power consumption.

Yet a further object of the present invention is to provide a smart battery device that includes a microprocessor with RAM memory, and comprises means for retaining RAM memory contents when the device is in sleep mode.

Yet still a further object of the invention is to provide a smart battery device that comprises short circuit protection means for preserving RAM memory contents when the battery is temporarily short circuited.

Another object of the instant invention is to provide a smart battery device that includes a ROM memory that is manufactured by a process that facilitates the programming 55 of ROM in an upper or respectively later produced layers.

Yet furthermore, an object of the instant invention is to provide a smart battery device that includes a ROM memory device whereby the programming of ROM is effected in a metal mask.

Furthermore, an object of the instant invention is to provide a smart battery device having incorporated therein an error treatment algorithm, for taking into account measurement errors, interpolation from look-up tables, etc., wherein the errors are considered to be a function of time. It is another object of the instant invention to provide a 65 It is contemplated that if a total error is larger than a predetermined value, certain operating modes are disabled, and, in particular, variables are substituted by default values

to result in a smaller error. In case of displayed information, such as LED battery pack display, the error can be additionally taken into account, for e.g., a quantity of: capacity—total error in capacity, may be displayed. If an error that is too big is produced, the end criterion for determining end of 5 charge condition may be changed, for e.g., using -dU instead of the error influenced criterion.

These and other objects of the present invention are attained with a smart battery device which provides electrical power and which reports predefined battery parameters 10 to an external device having a power management system, wherein the battery includes:

(a) at least one rechargeable cell connected to a pair of terminals to provide electrical power to an external device during a discharge mode and to receive electrical power 15 during a charge mode, as provided or determined by said remote device,

(b) a data bus for reporting predefined battery identification and charge parameters to the external device,

(c) an analog means for generating analog signals repre-<sup>20</sup> sentative of battery voltage and current at said terminals, and an analog signal representative of battery temperature at said cell,

(d) a hybrid integrated circuit (IC) having a microprocessor for receiving the analog signals and converting them to <sup>25</sup> digital signals representative of battery voltage, current and temperature, and calculating actual charge parameters over time from said digital signals, said calculations including one calculation according to the following algorithm; <sup>30</sup>

#### $CAP_{rem} = CAP_{FC} - \Sigma I_d \Delta t_d - \Sigma I_s \Delta t + \Sigma \epsilon_c I_c \Delta t_c$

wherein  $\epsilon_c$  is 1 for a LiIon battery, and for a NiMH battery is a function of battery current, temperature, and CAP<sub>rem</sub>; and I<sub>s</sub> is a function of battery temperature and CAP<sub>FC</sub>, the 35 capacity at full charge, for a LiIon battery, and for a NiMH battery is a function of battery temperature and CAP<sub>rem</sub>.

(c) a data memory defined within said hybrid IC for storing said predefined battery identification and actual charge parameters, even when nominally fully discharged, 40 said charge parameters including at least full charge capacity and remaining capacity,

(f) a bus controller defined within said hybrid IC for sending battery messages to said remote device over said data bus, said messages including said predefined battery 45 identification and said actual charge parameters.

Superimposed on this equation is reset logic, to be explained below, that self corrects the value of  $CAP_{FC}$  with a capacity calculation at each full charge (EOC) and each end of full discharge.

Further benefits and advantages of the invention will become apparent from a consideration of the following detailed description given with reference to the accompanying drawings, which specify and illustrate preferred embodiments of the invention.

### BRIEF DESCRIPTION OF THE DRAWINGS

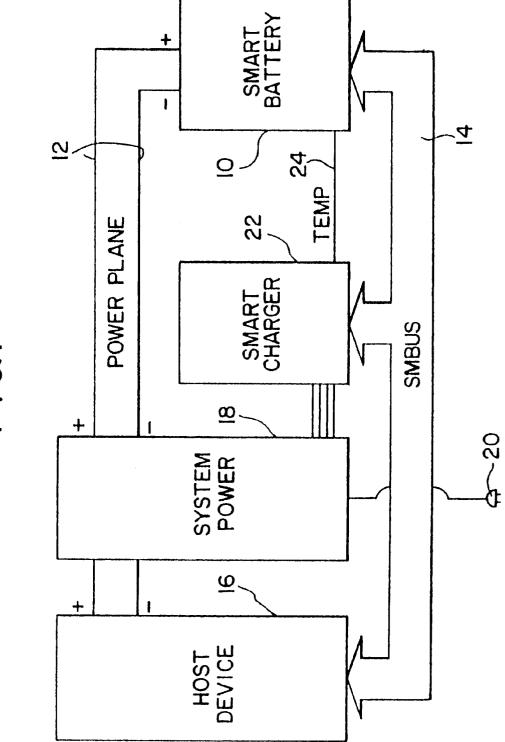

FIG. 1 is a diagrammatic block diagram of a smart battery device connected to a host computer and battery charging device.

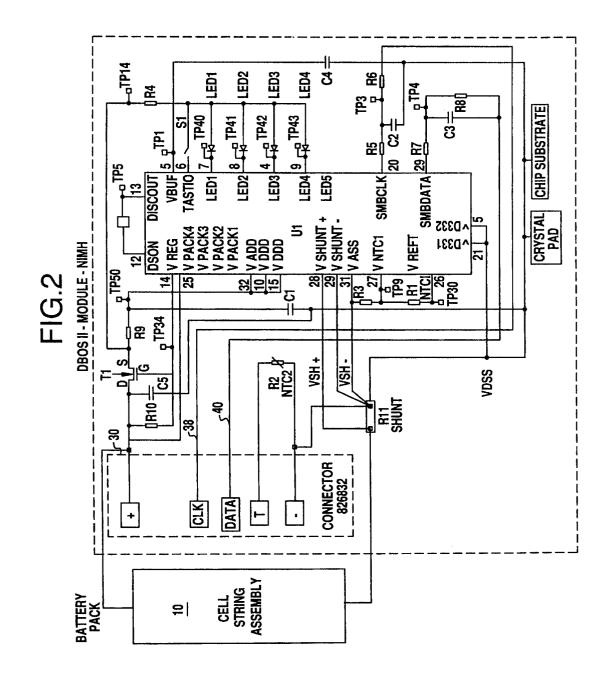

FIG. **2** is a simplified block diagram of the smart battery device and connector, including a pinout diagram of an Application Specific Integrated Circuit (hybrid IC) used in the present invention.

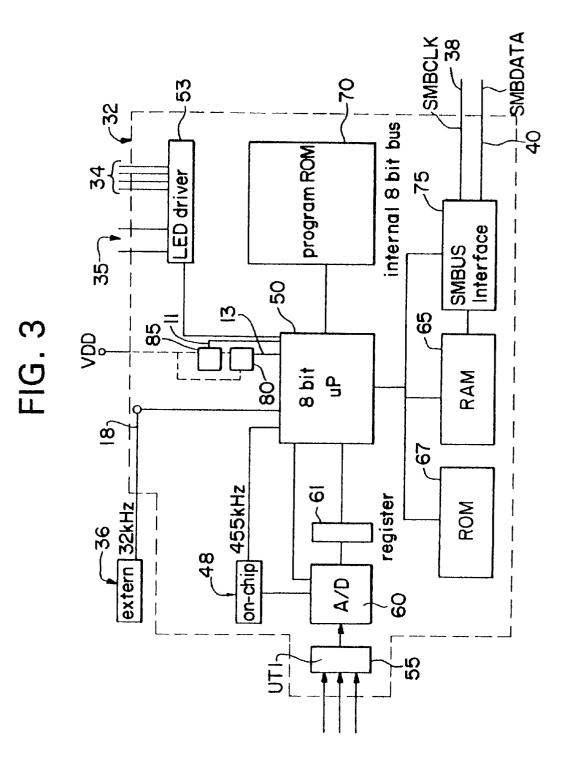

FIG. **3** illustrates a simplified block diagram of the hybrid 65 IC **32** that includes the microcontroller of the smart battery device of the instant invention.

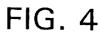

FIG. **4** illustrates a general schematic diagram of the A/D converter **60**.

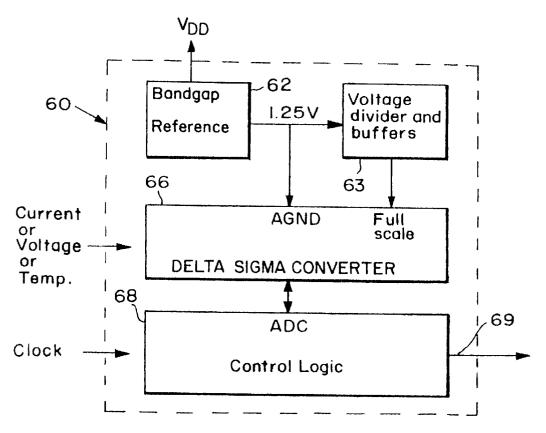

FIG. **5**(*a*) illustrates a schematic sketch of dc voltage shifting circuit arrangement.

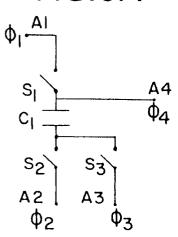

FIG. 5(b) is a second embodiment of the inventive circuit arrangement.

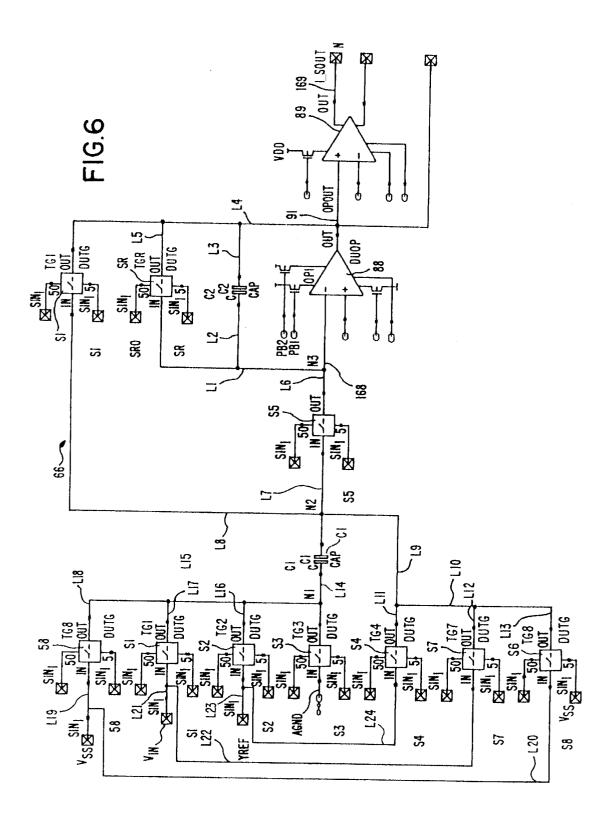

FIG. 6 is a schematic sketch of the circuit arrangement in the A/D converter 60.

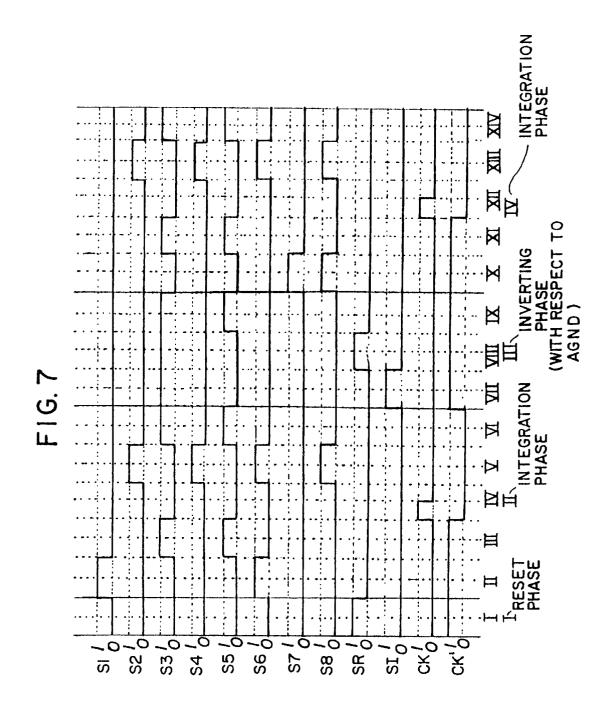

FIG. 7 is a phase diagram in the operation of the A/D converter pursuant to FIG. 6.

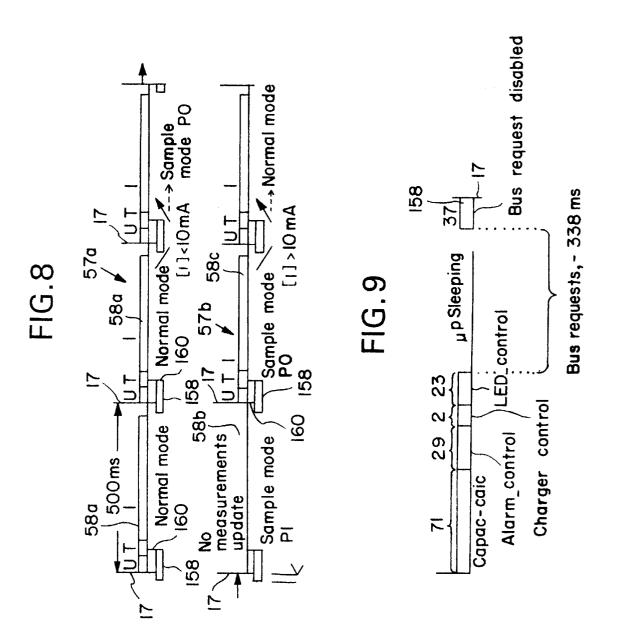

FIG. 8 illustrates the timing of the operating cycles under normal and sample mode operating conditions.

FIG. 9 illustrates the approximate time durations for the various measurements per operating cycle.

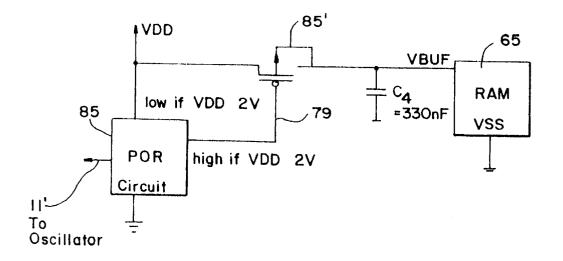

FIG. 10 is a detailed schematic of the power-on reset 85 and RAM de-latching circuit 85'.

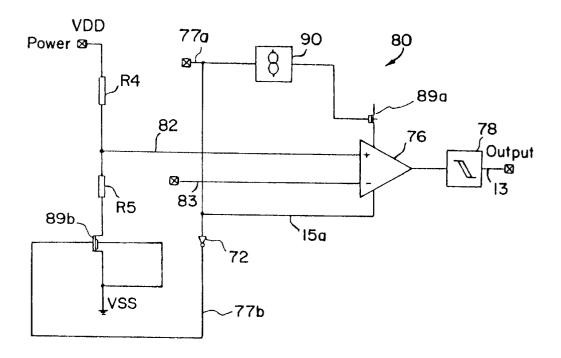

FIG. 11 illustrates a detailed schematic diagram of the comparator wake-up circuit 80.

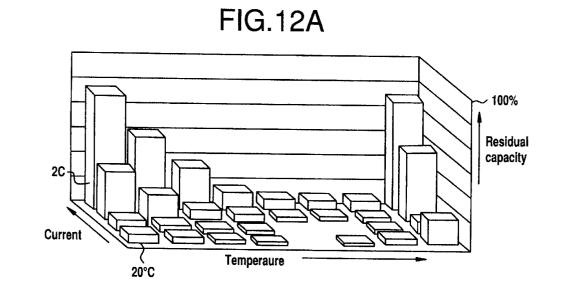

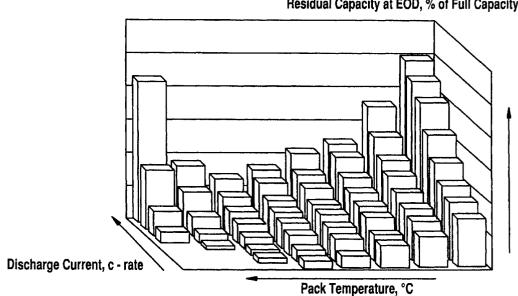

FIG. 12*a* is a three-dimensional graphic representation of look up tables (LUT) that depict predicted residual capacity values as a function of discharging current and temperature for a NiMH battery, and similar look up tables for a LiIon battery are shown in FIG. 12*b*.

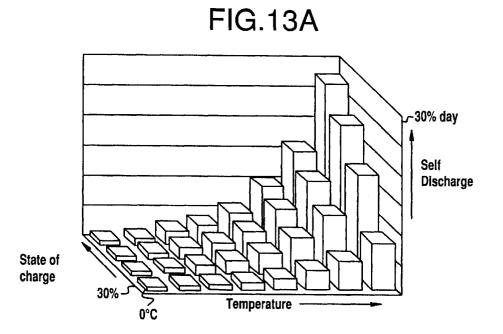

FIG. 13*a* is a three-dimensional graphic representation of look up tables that depict the amount of self-discharge current (vertical axis) as a function of relative battery state of charge and temperature for a NiMH battery, and similar look up tables for a LiIon battery are shown in FIG. 13*b*.

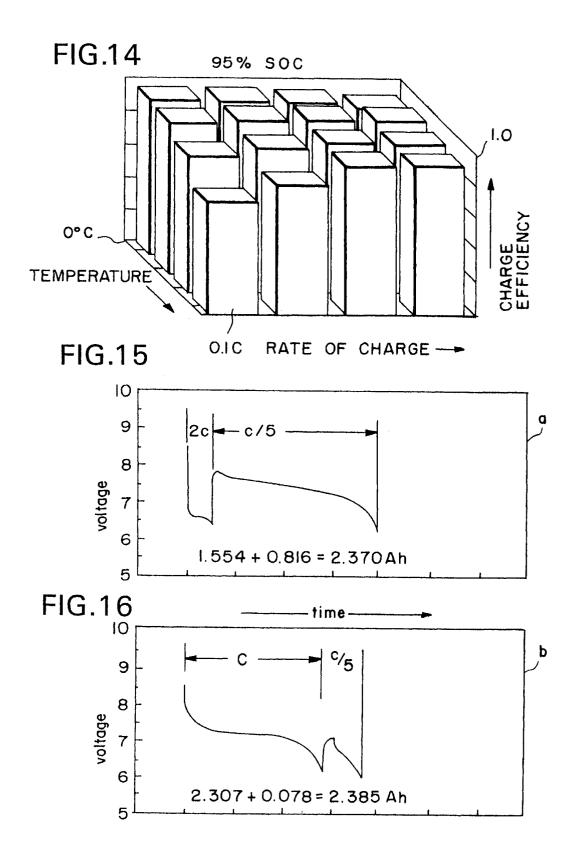

FIG. 14 is a three-dimensional graphic representation of charge efficiency look-up tables showing charge efficiency factors ( $E_c$ ) as a function of relative state of charge, charging current, and temperature for a NiMH battery, and wherein similar look up tables are not required for a LiIon battery which has a charge efficiency of 1.

FIGS. **15** and **16** illustrate two voltage versus time graphs, a and b, comparing calculated battery capacity characteristics at various discharging current rates for a six (6) cell battery pack for a NiMH battery, and similar graphs are available for a LiIon battery.

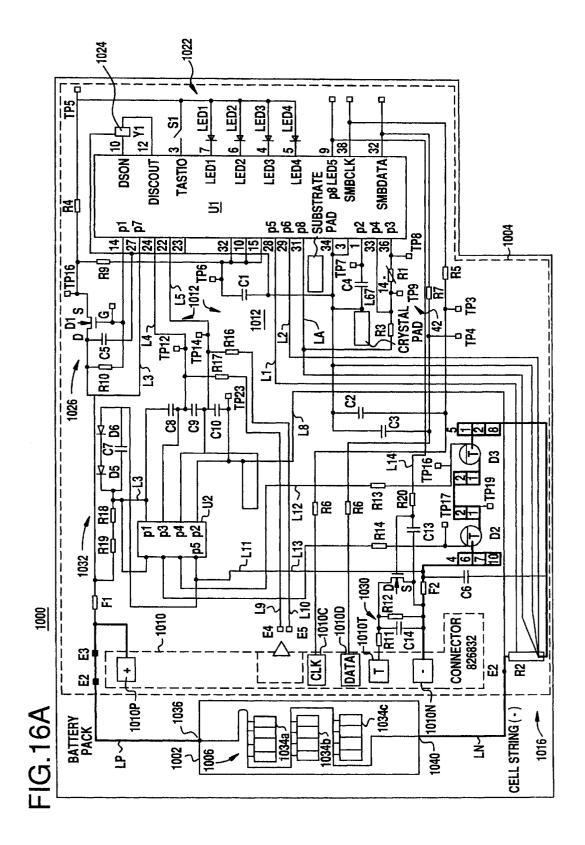

FIG. 16A is a schematic diagram of a battery pack especially well suited for use with lithium ion battery cells.

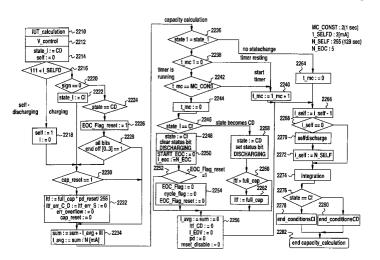

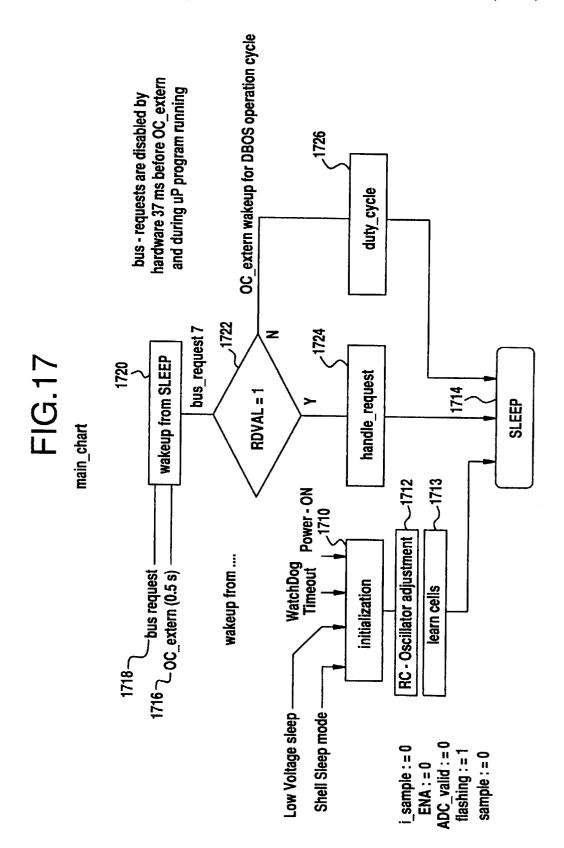

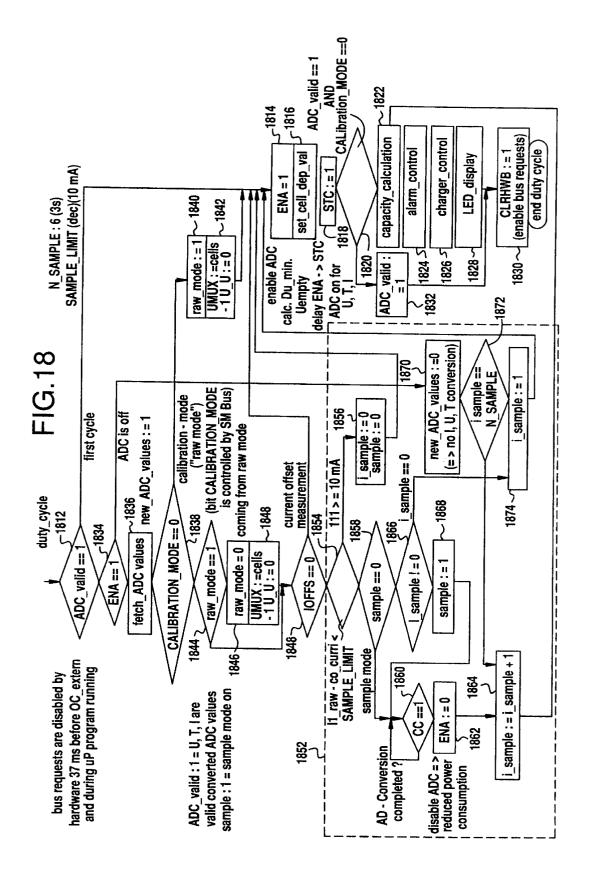

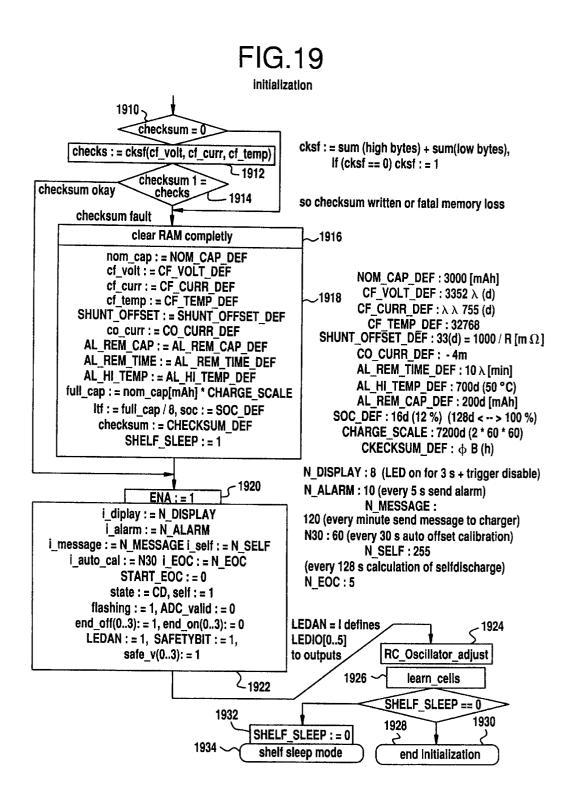

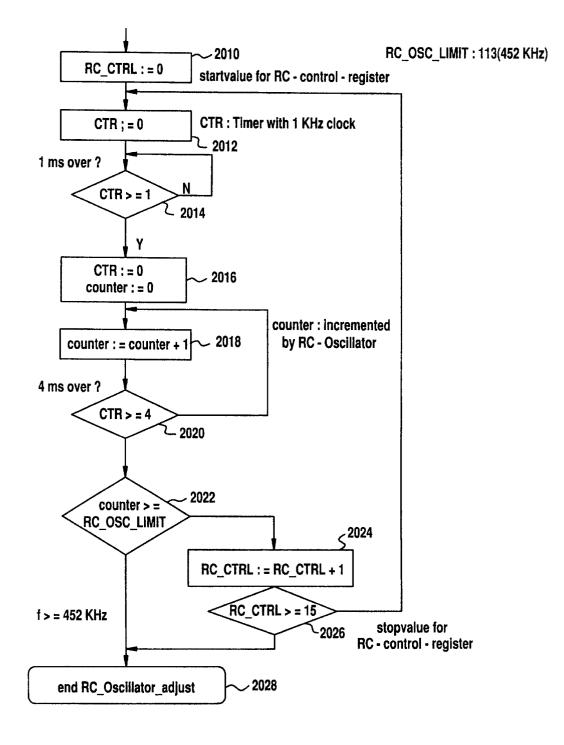

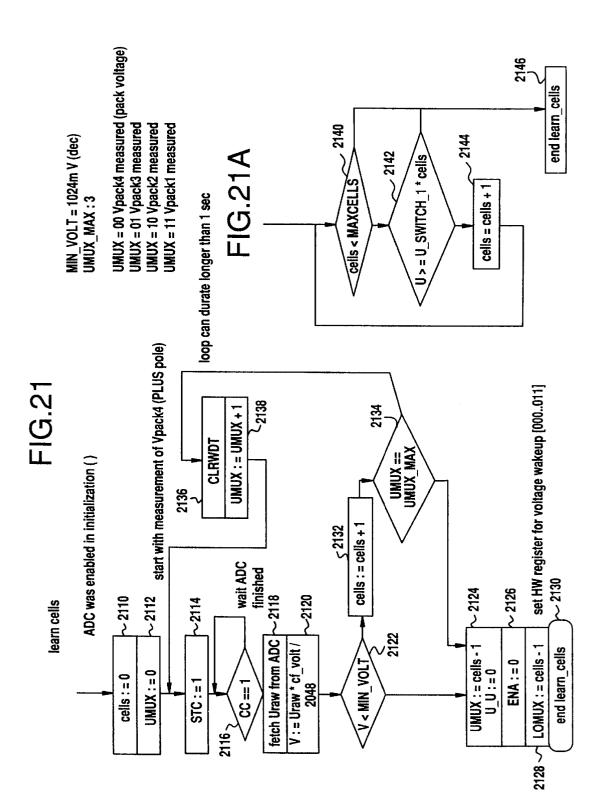

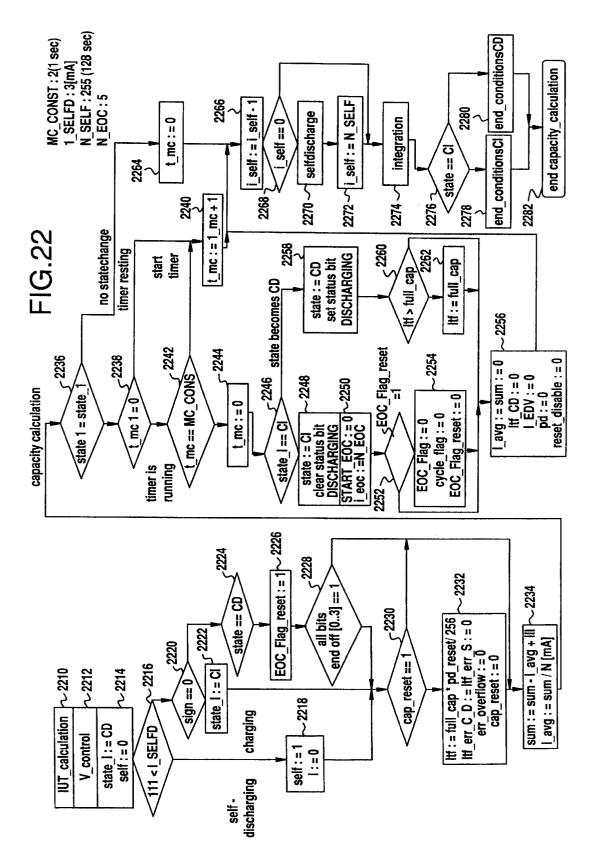

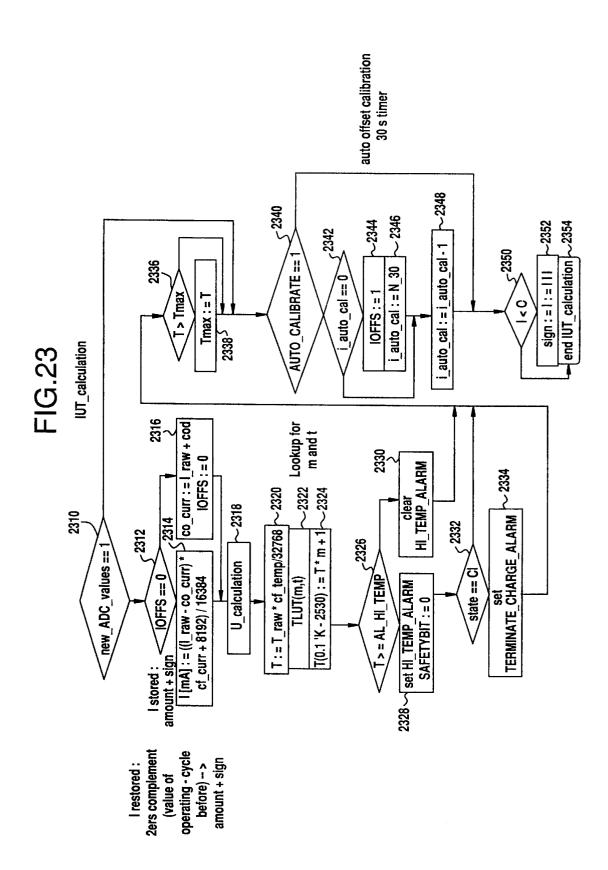

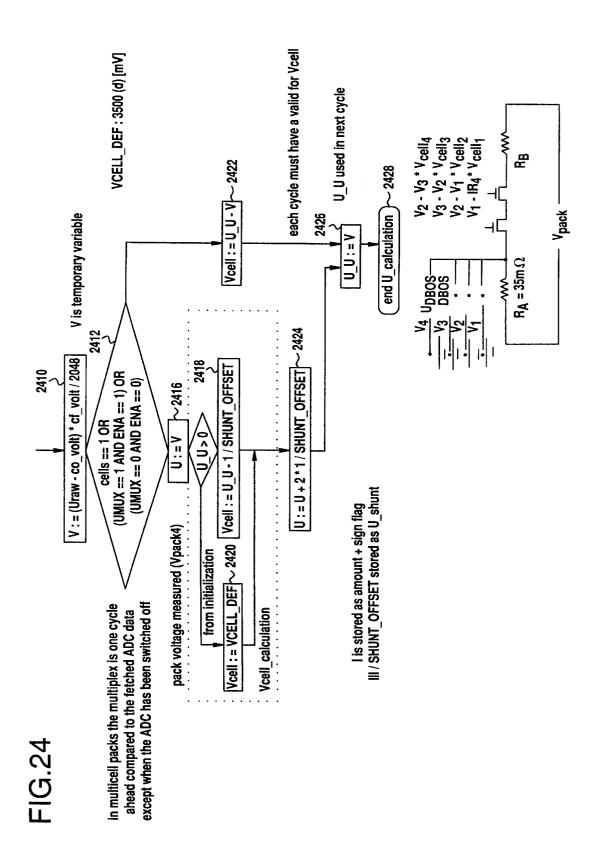

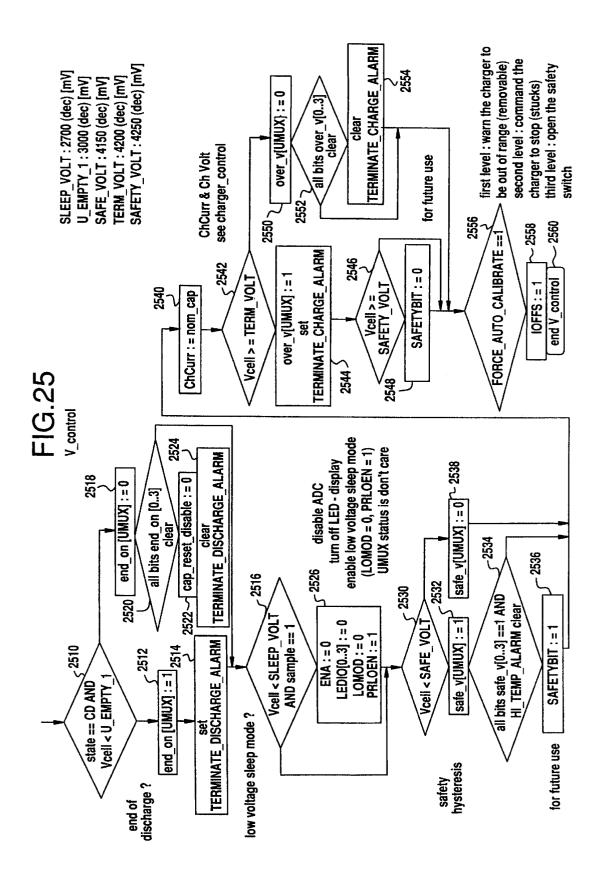

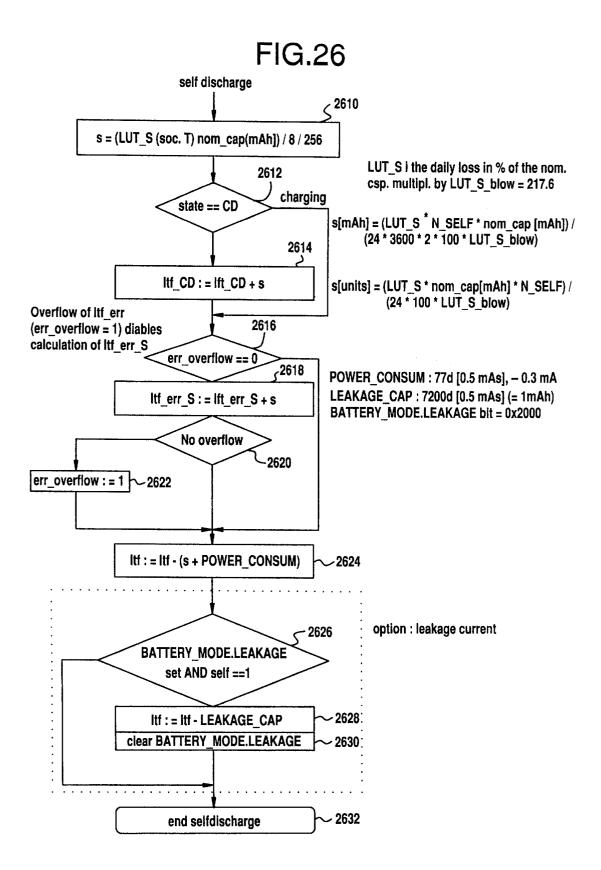

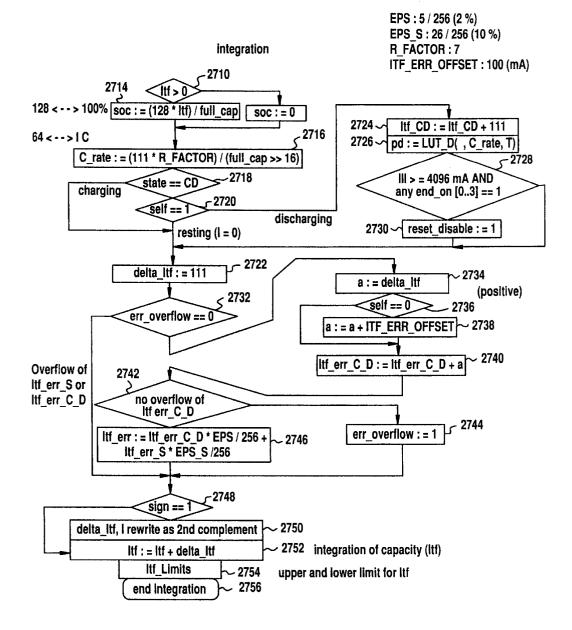

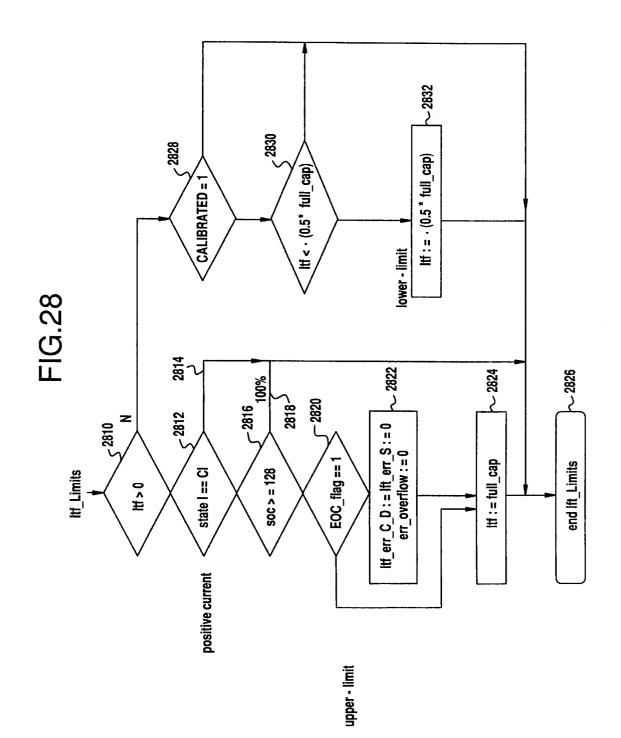

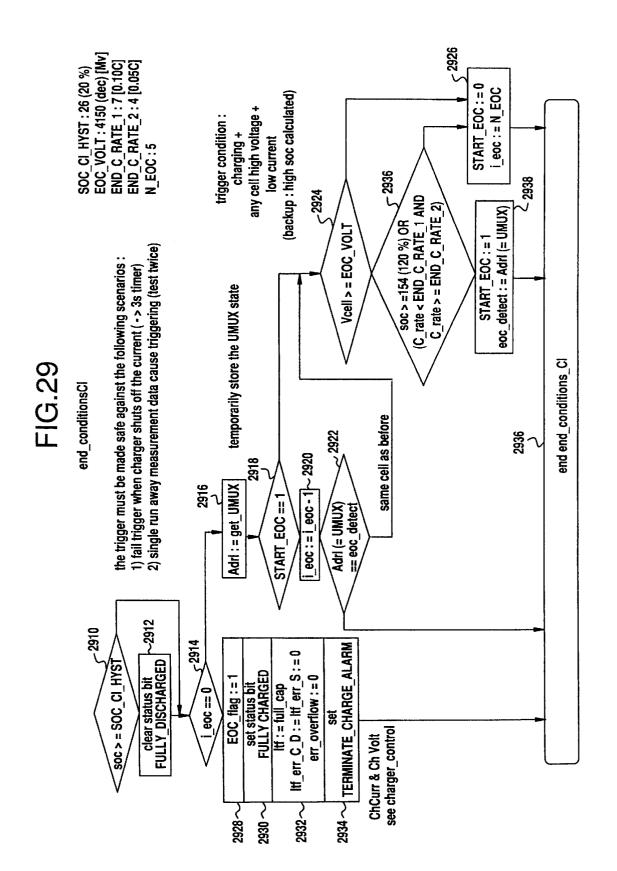

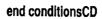

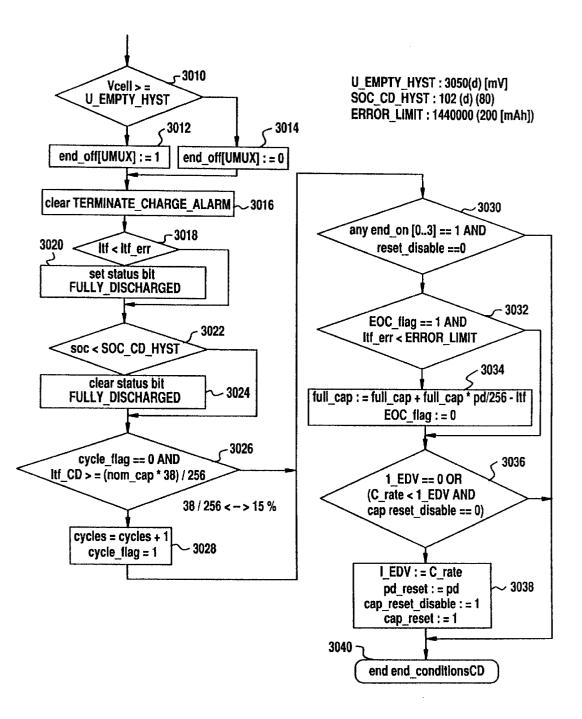

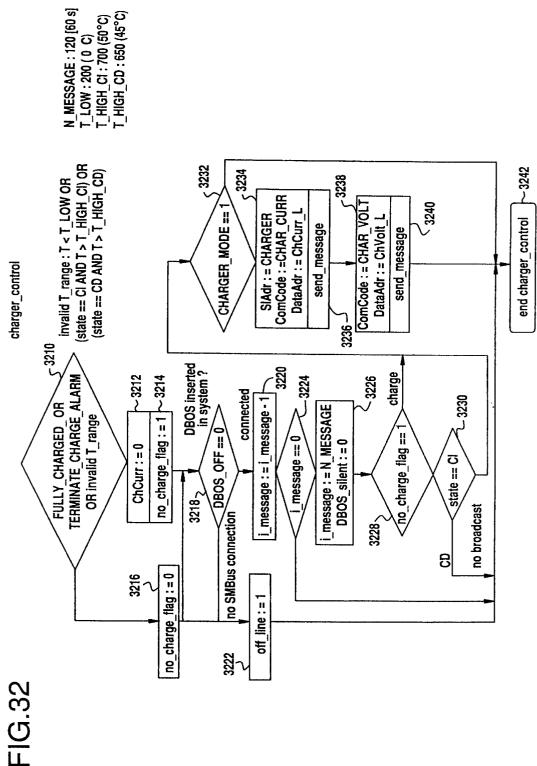

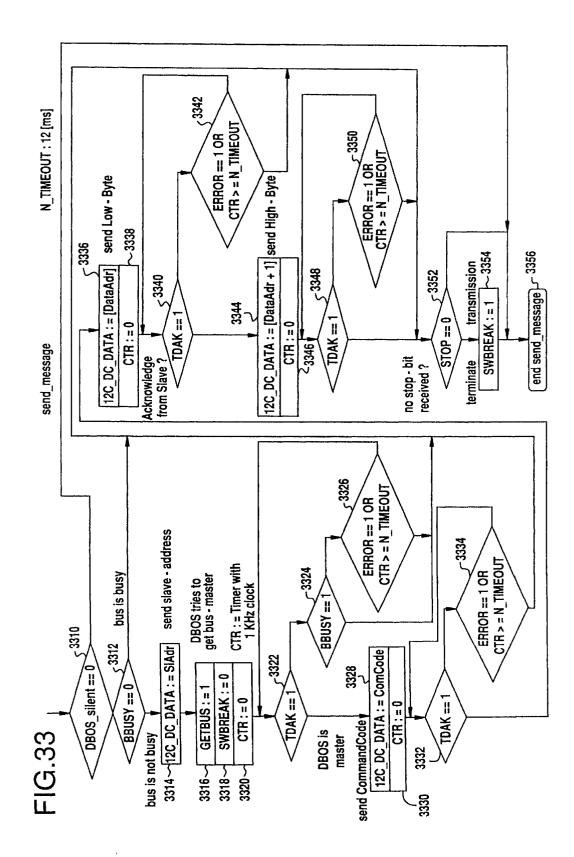

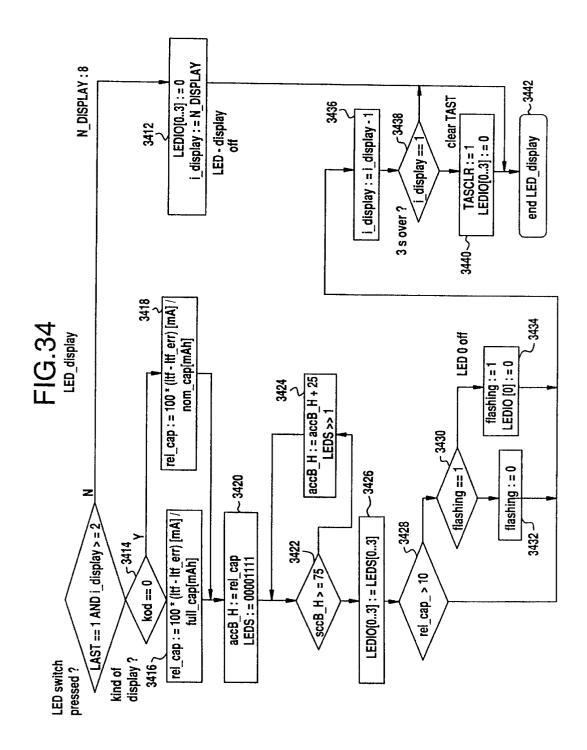

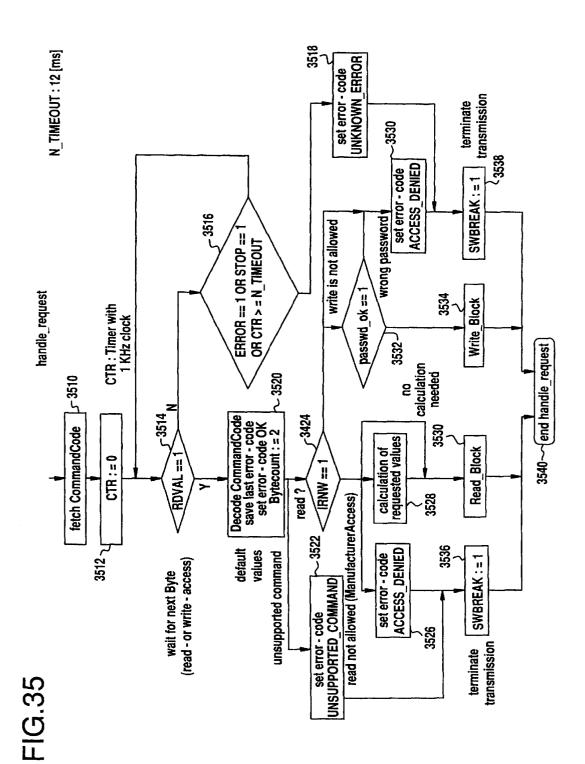

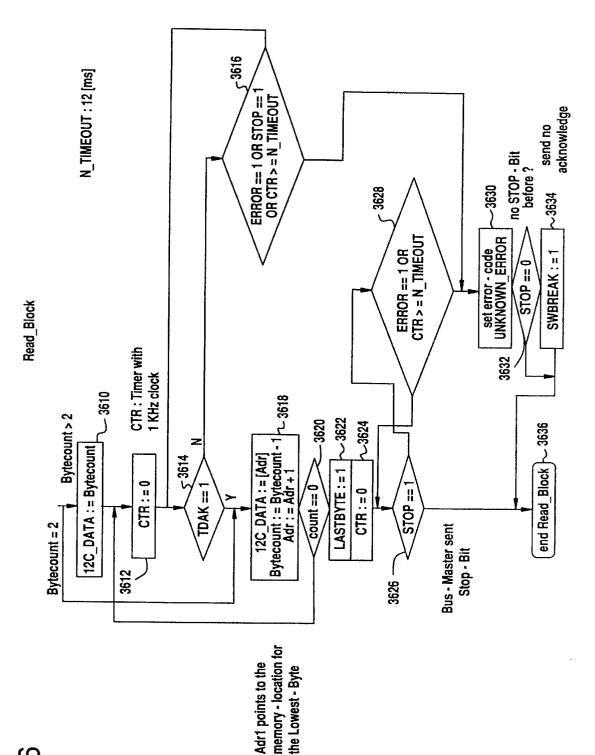

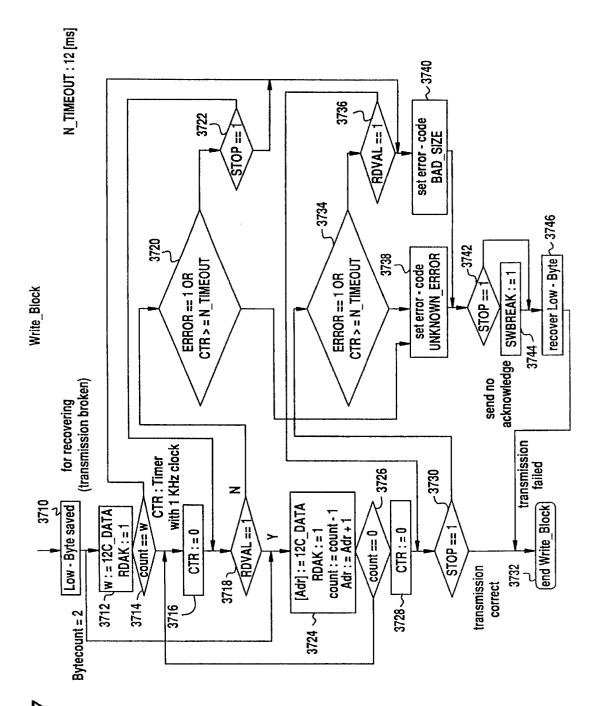

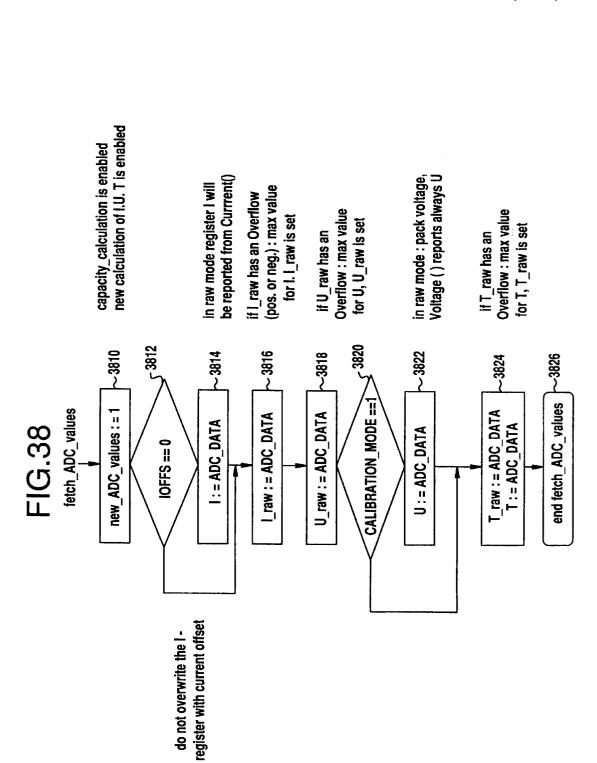

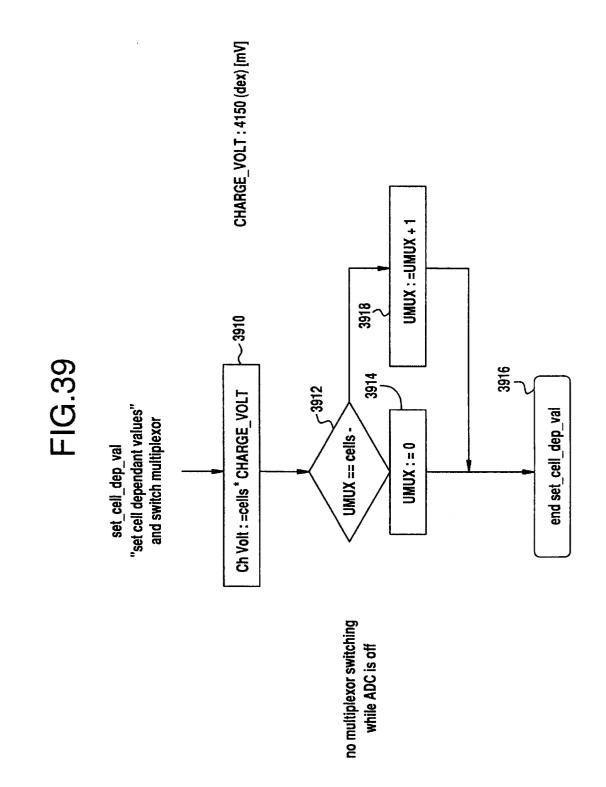

FIGS. **17** through **39** illustrate respectively the following logic flow diagrams or routines for a LiIon battery (with the exception of FIG. **21** a which is for a NiMH battery), main\_chart, duty\_cycle, initialization, RC\_Oscillator\_adjust, learn\_cells, capacity\_calculation, IUT\_calculation, U\_calculation, V\_control, selfdischarge, integration, Itf<sub>13</sub> Limits, end\_conditionsCI, end\_conditionsCD, alarm\_control, Charge\_control, send\_message, LED\_display, handle\_request, Read\_Block, Write\_Block, fetch\_ADC\_values, and set\_cell dep\_val.

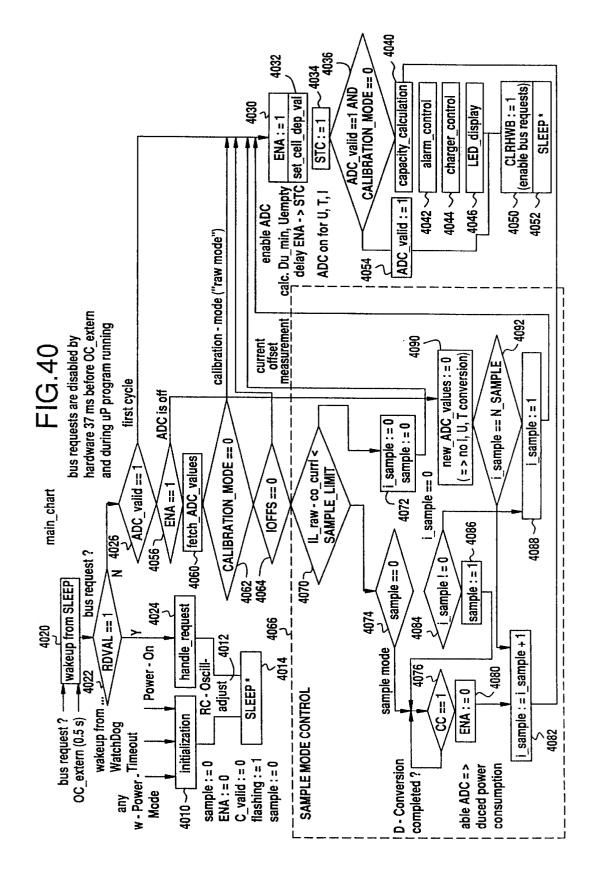

FIG. **40** is a flow chart showing the main operating routine of a program for monitoring and controlling the operation of a battery pack having rechargeable nickel metal hydride battery cells.

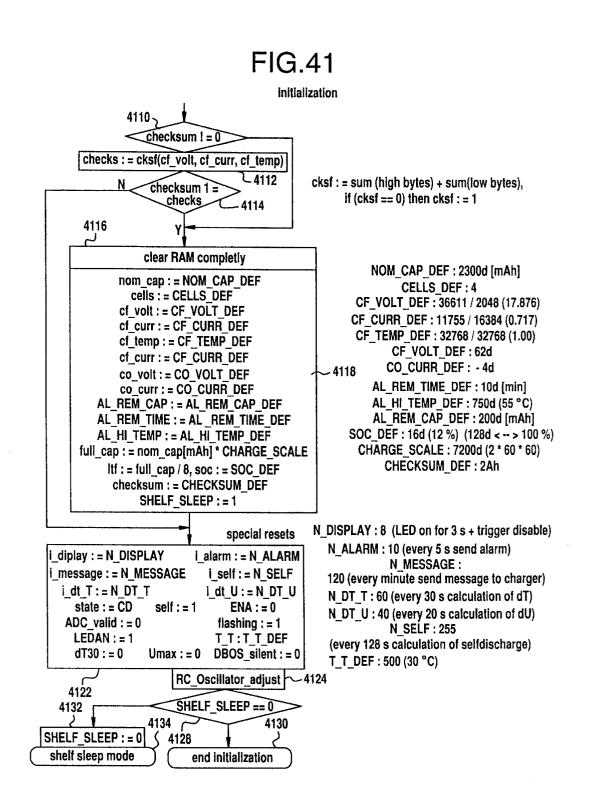

FIG. 41 illustrates an initialization routine of the operating program shown in FIG. 40.

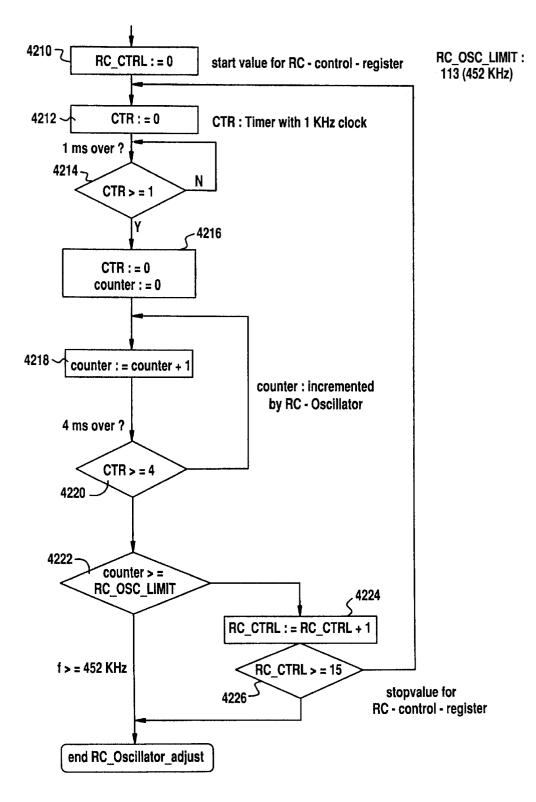

FIG. **42** is as flow chart for a routine used to calibrate an oscillator of the battery pack.

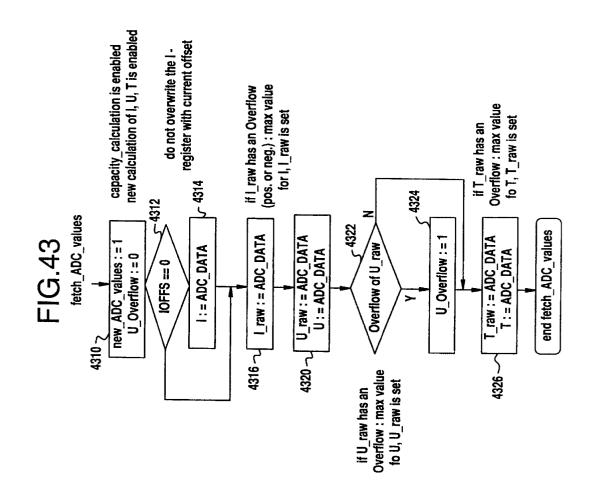

FIG. **43** shows a routine for transferring data values from an analog-to-digital converter to a processor of the battery pack.

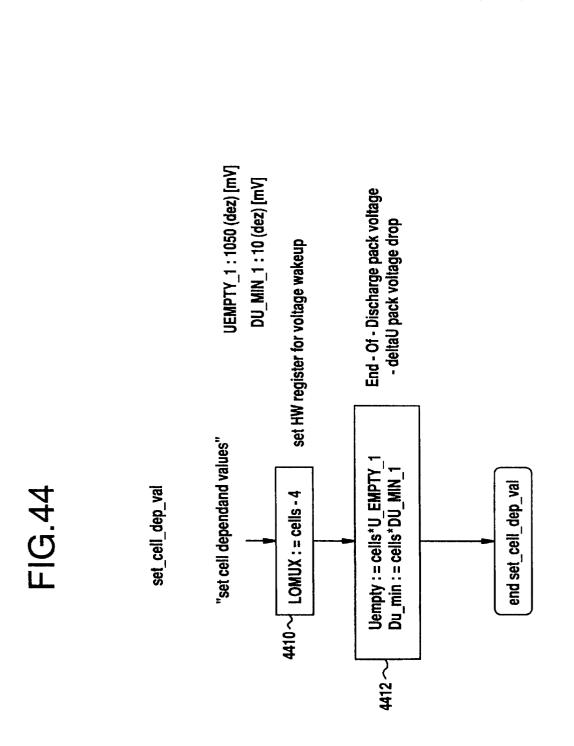

FIG. 44 shows a routine used to determine various values that depend on the number of battery cells in the battery pack.

35

45

50

55

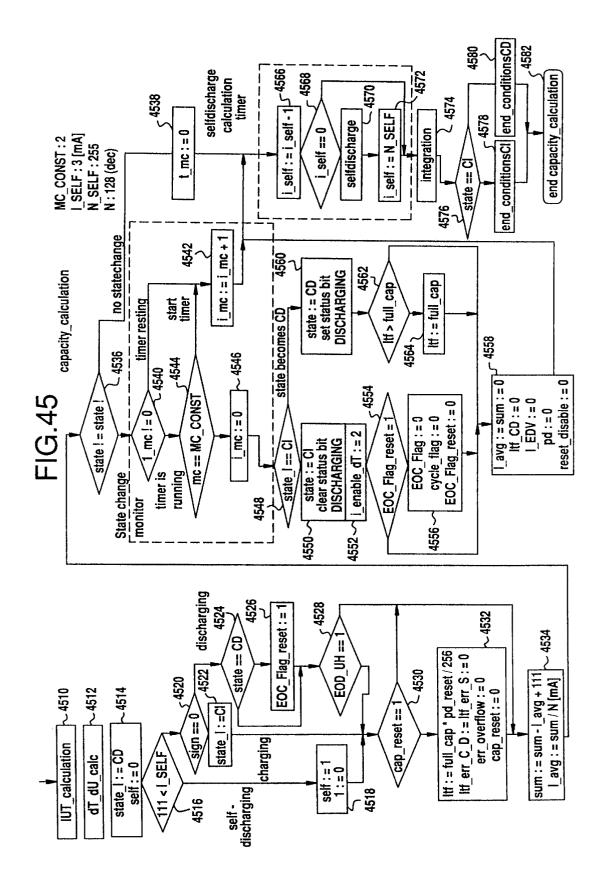

FIG. **45** illustrates a routine for determining the remaining capacity of the battery.

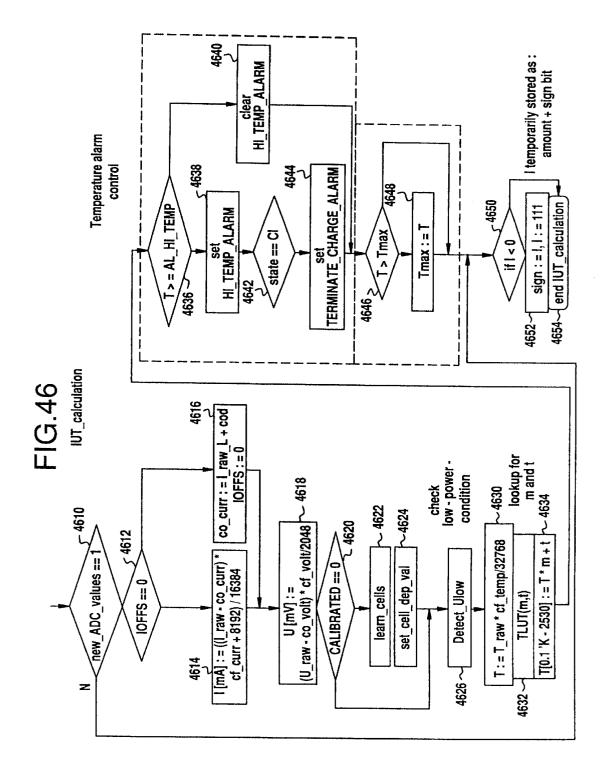

FIG. **46** is a flow chart for a routine used to convert output data of the analog-to-digital converter to data values in preferred units.

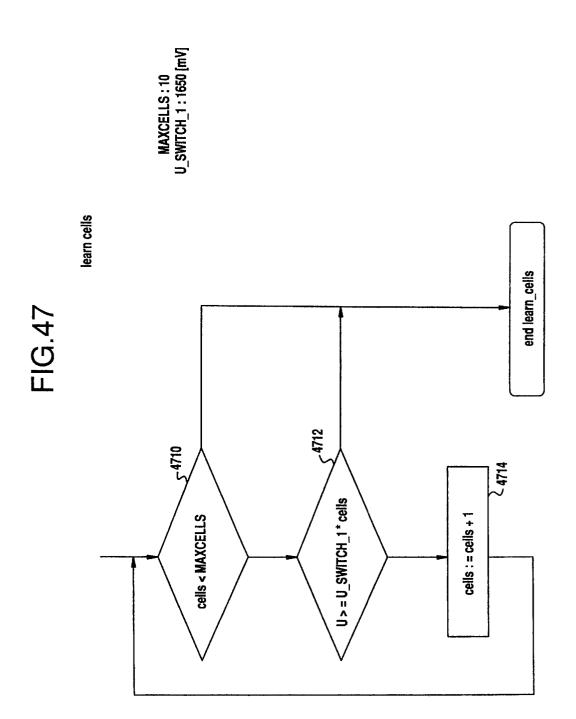

FIG. **47** shows a routine for determining the number of cells in the battery pack.

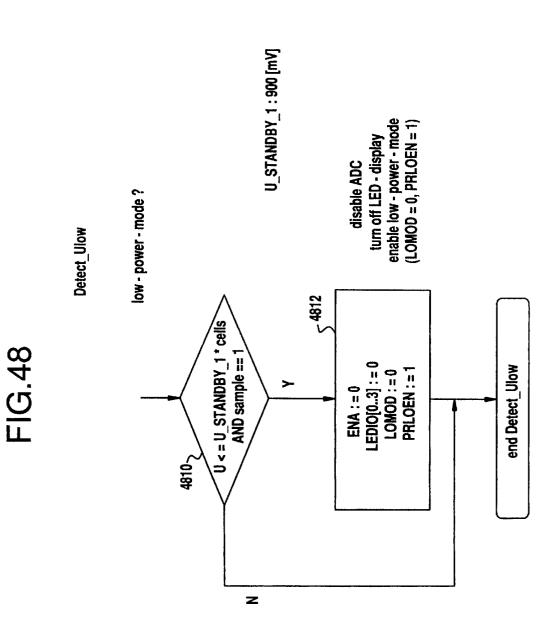

FIG. **48** shows a procedure for determining when the processor of the battery pack enters a low power, or sleep  $_{10}$  mode.

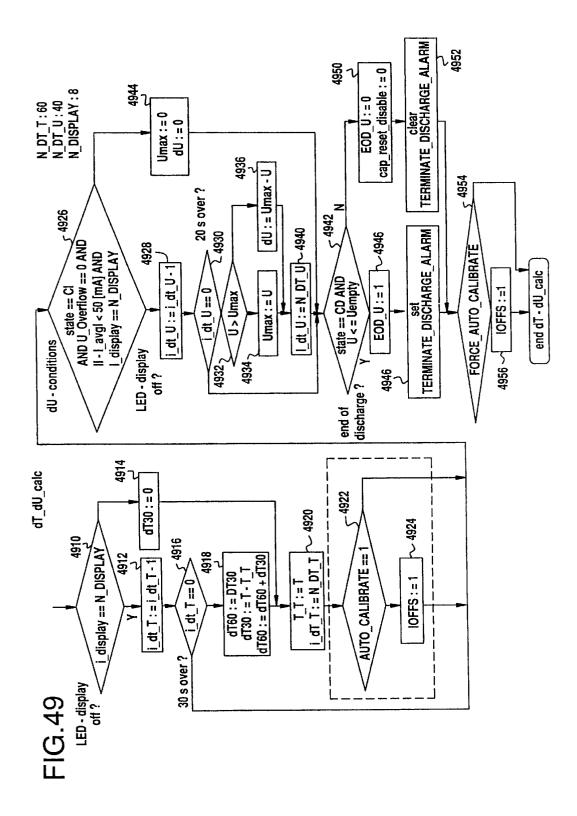

FIG. 49 illustrates a routine for calculating various temperature and voltage values.

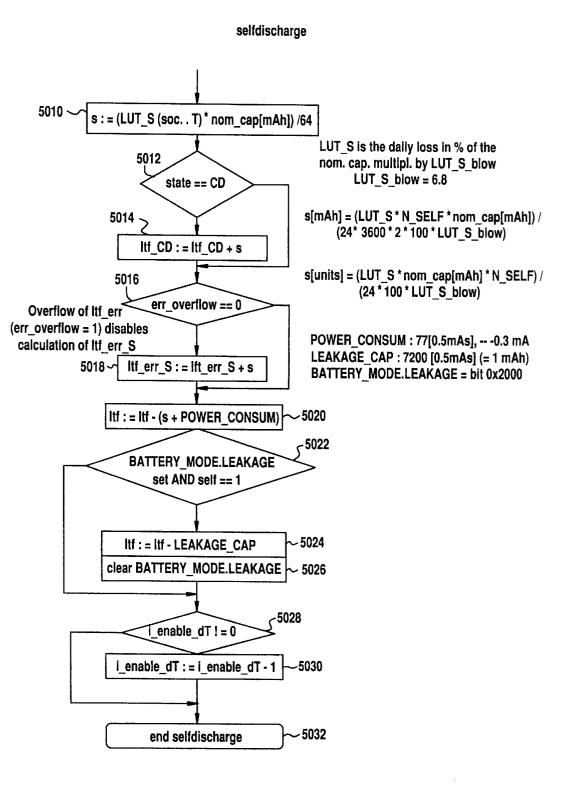

FIG. **50** shows a routine used by the processor to calculate the decrease in battery capacity due to self discharge of the 15 battery cells.

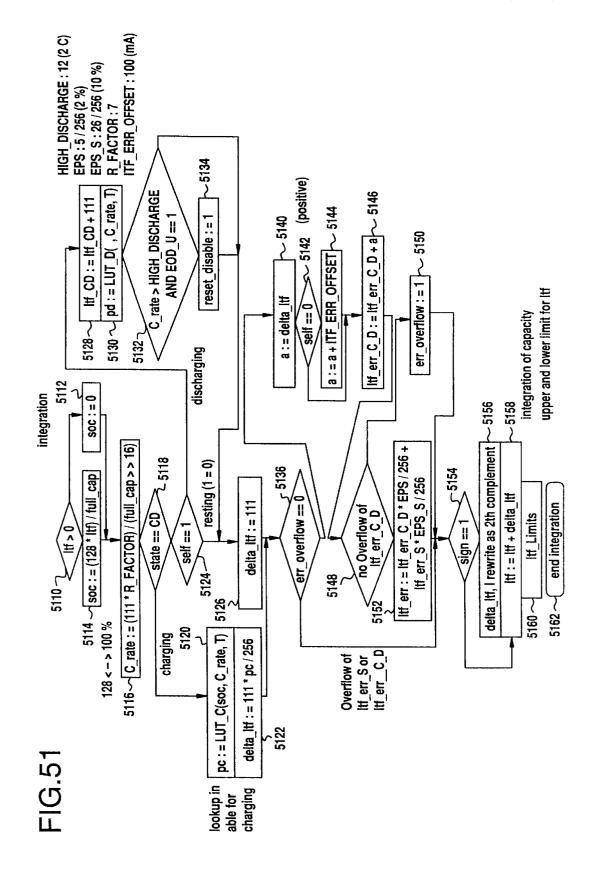

FIG. **51** is a flow chart showing a procedure for calculating changes in the remaining capacity of the battery.

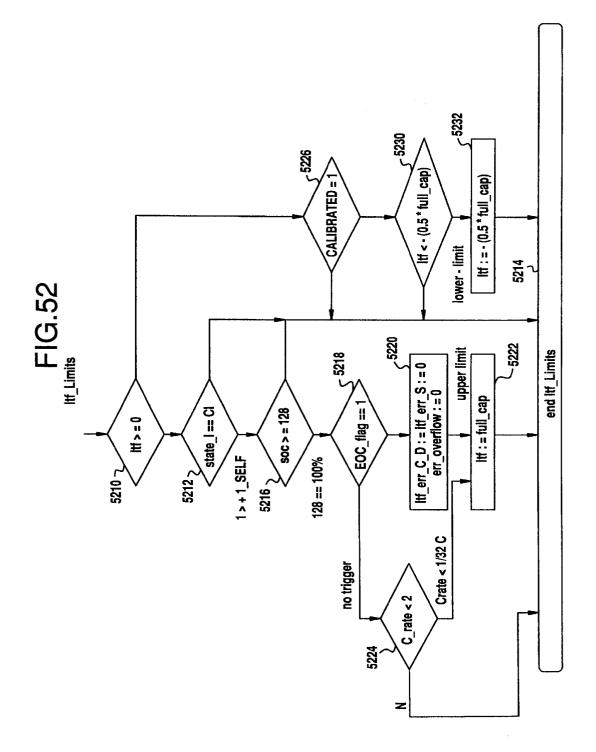

FIG. **52** illustrates a procedure used to determine wheter the remaining battery capacity has reached predefined upper <sup>20</sup> or lower limits.

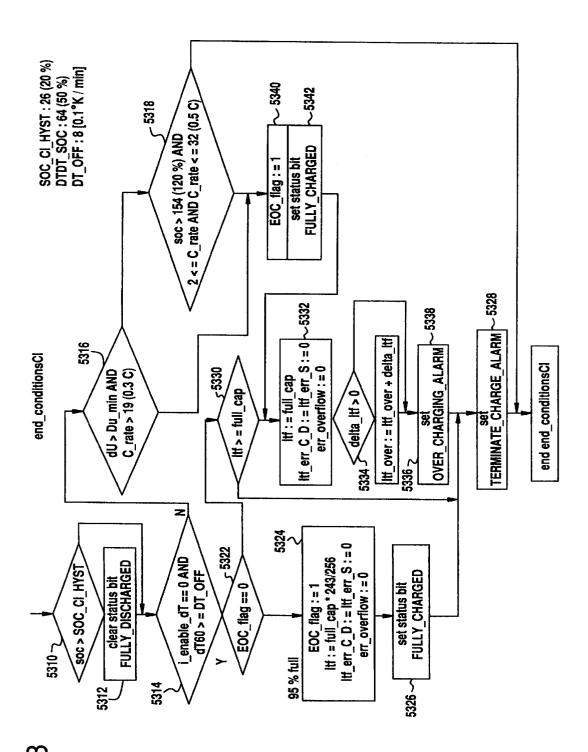

FIG. **53** shows a routine for determining when the battery pack has reached an end of charging.

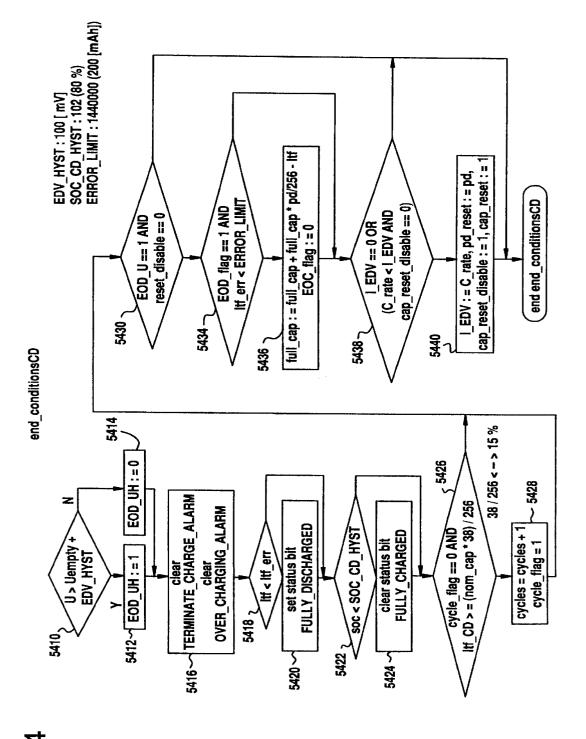

FIG. **54** is a flow chart for a routine for determining when  $_{25}$  the battery pack has reached an end of discharge.

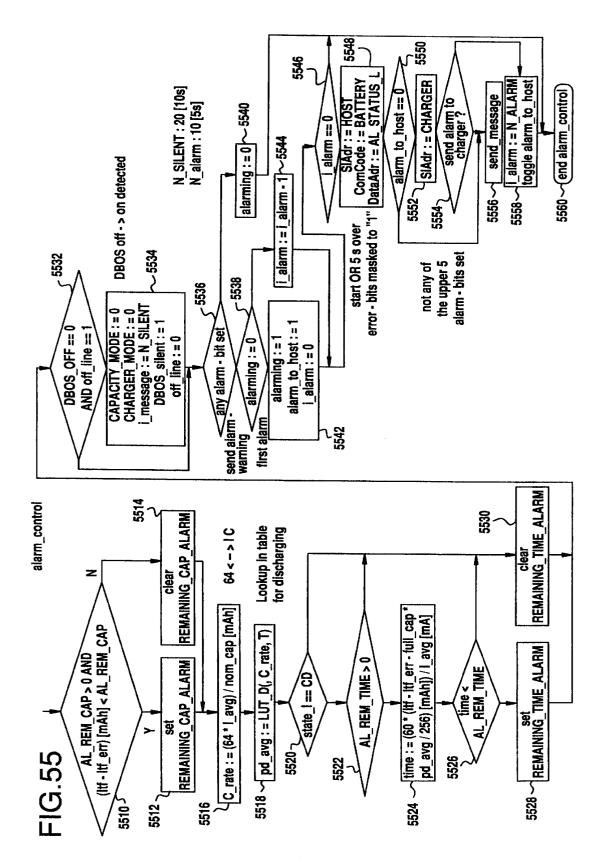

FIG. **55** shows a procedure for monitoring and generating alarms relating to various conditions of the battery pack.

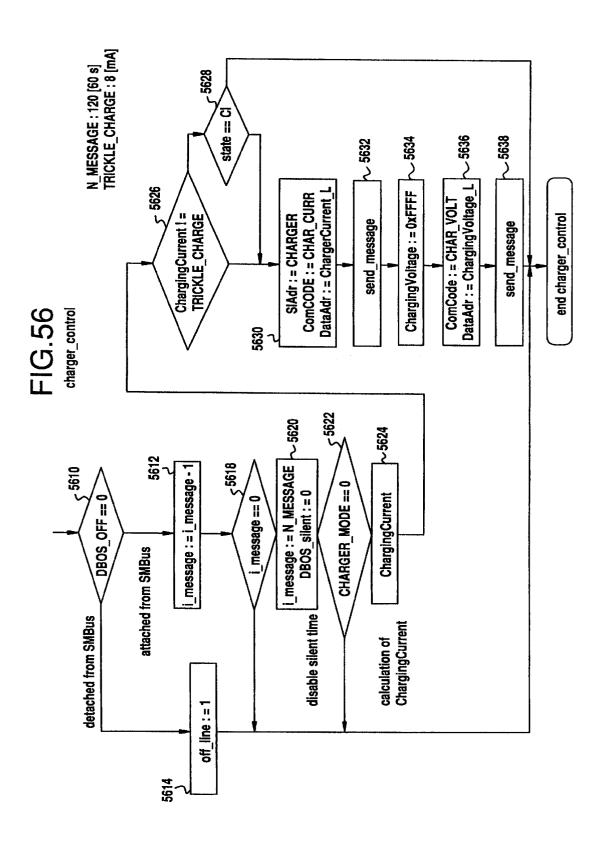

FIG. **56** illustrates a routine for sending instructions to a battery charger.

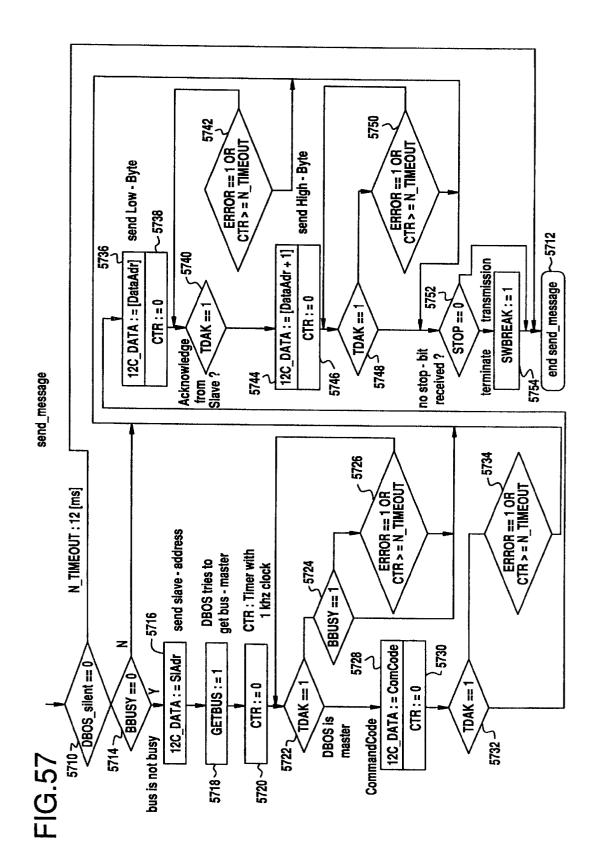

FIG. **57** shows a procedure used by the processor on the battery pack to prepare messages for transmission.

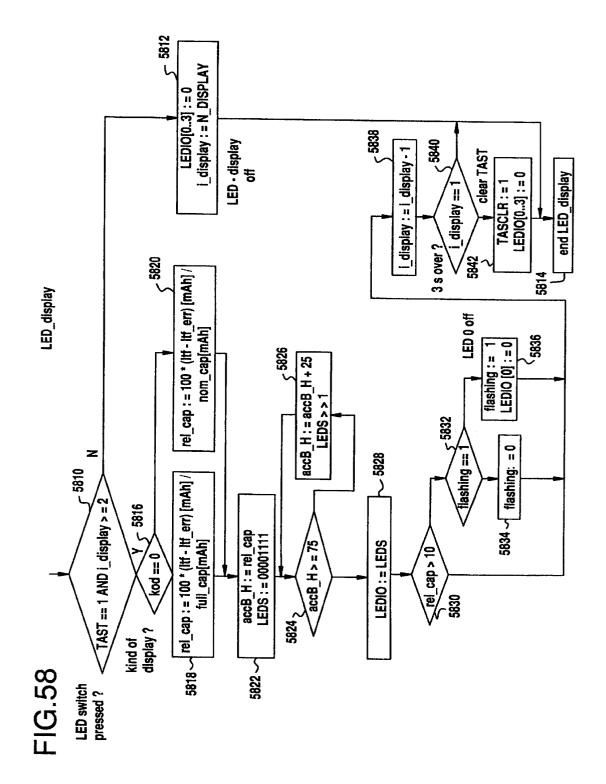

FIG. **58** is a flow chart of a routine used to control an LED display on the battery pack.

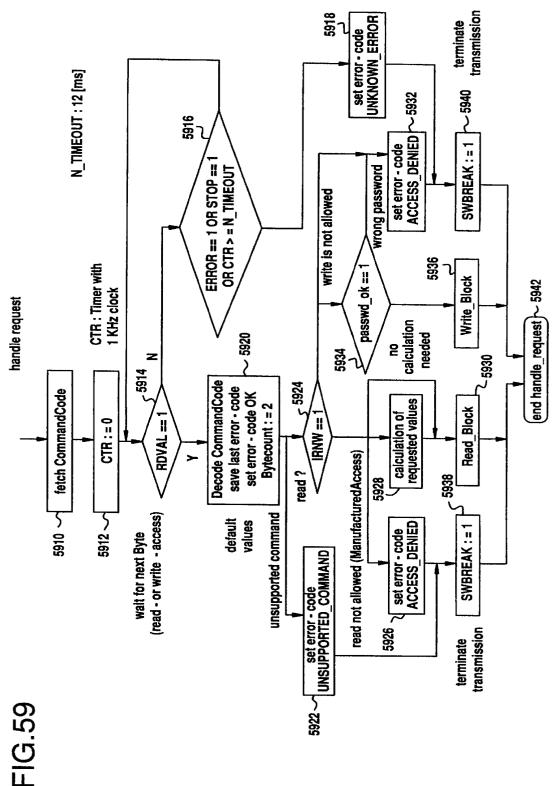

FIG. **59** illustrates a procedure for processing requests received by the processor on the battery pack.

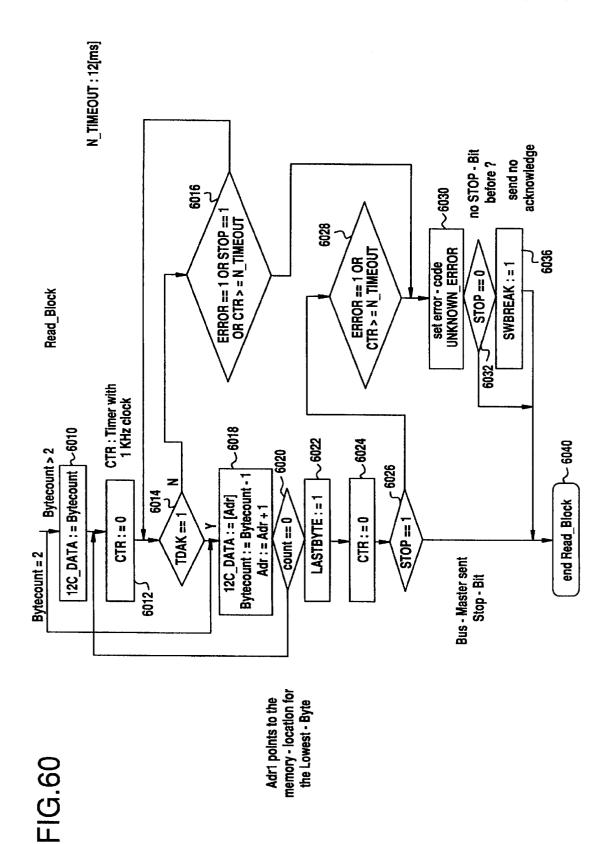

FIG. **60** shows a routine for reading data received by the processor on the battery pack.

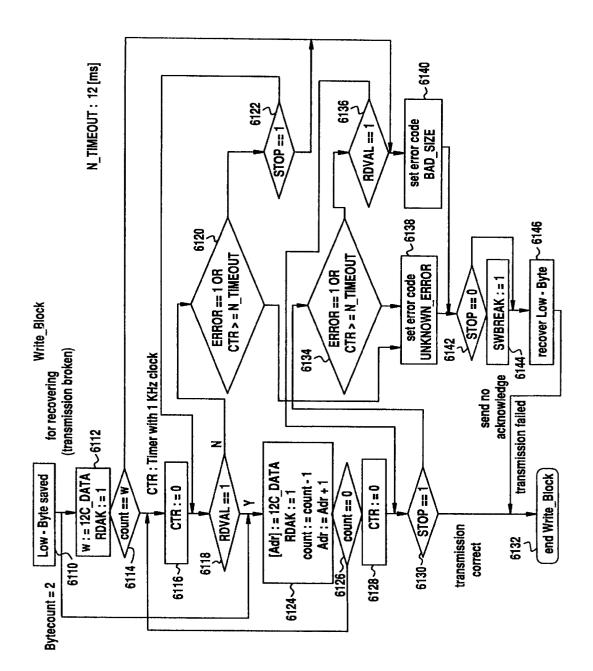

FIG. 61 shows a procedure used by the processor on the  $\,^{40}$  battery pack to write messages.

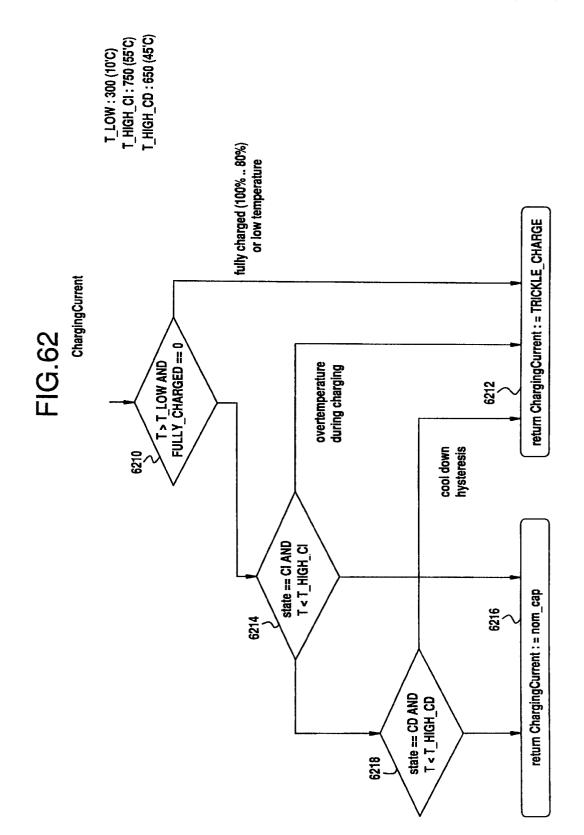

FIG. **62** is a flow chart illustrating a routine for identifying a charging current being applied to the battery pack.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

The smart battery device of the present invention, referred to as a Duracell Battery Operating System (DBOS), is initially described in the following overview which includes the following sequential topics, ASIC Hardware, Architecture, CPU, A/D Converter, Current Measurement, Temperature Measurement, Pack Voltage Measurement, Cell Voltage Measurements, ROM, RAM, RAM Data Backup Circuit, 12C/SMBus Interface, Clock generation circuit, Wake-up comparator circuit, LED Drivers, Interface circuits, Hardware Modes of Operation, Run Mode: Entry/ Exit, Sample Mode: Entry/Exit and Sleep Mode: Entry/Exit.

ASIC Hardware

Architecture

The ASIC (Application Specific Integrated Circuit) is composed of five basic blocks: processor core (CPU), analog to digital converter (A/D), program memory and look-up tables (ROM), data memory (RAM), and the I2C/SMBus communications interface. The primary goal of these com-55 ponents is to measure, calculate, and communicate the status of the Smart Battery.

Each of the above blocks includes additional hardware and software components required to perform the specific task. Some of these components are shared between components, such as the internal clock oscillator which is 5 used by the CPU and the A/D.

CPU

The Central Processing Unit, or processor core, of the ASCI is an 8-bit microcontroller processor. It is considered a Reduced-Instruction-Set-CPU (RISC) since it lacks complex instructions such as multiply and divide. It is a low-power design, optimized for both reasonable speed and very low power consumption.

The CPU requires a 4-phase clock which is derived from the internal RC oscillator. Each cycle of the clock is approximately 8.8 usec in duration.

The CPU executes the program software which includes everything from operation of the A/D to capacity calculations to I2C/SMBus communications. A more complete description of the software is included in Chapter 3—DBOS Algorithm. Portions are also discussed in Chapter 2—SBData and SMBus.

The CPU uses a Harvard architecture which separates the data and program memory accesses so the CPU can operate more efficiently. A traditional architecture uses a single data program memory space but this delays operation since a program instruction must wait for data read/writes and vice versa. The separate data and program memories require addition space but are faster in operation.

The CPU uses a 12-bit instruction word even though it is an 8-bit processor core. This allows a more efficient coding since the instructions can by combined with 8-bit data as well.

The CPU includes an Arithmetic Logic Unit (ALU), a standard stack and program counter, a bi-directional data bus, and a watch-dog timer. The ALU performs computions and executes program instructions. The data bus transfers program instructions and data values, and the watch-dog timer monitors the software execution.

The watch-dog timer is a common device within the CPUs. It helps prevent unwanted software execution or hang-ups. The watch-dog requires that a particular register must be written regularly. If it is not written, then the watch-dog has 'timed out' and will reset the CPU. This reset will clear the hang-up and re-start the CPU at a known state.

The CPU uses a paged-memory access procedure since its address mechanism cannot reach the whole 4K program ROM space. Instead, the memory is addressed and executed on in smaller pages of 128. This requires additional CPU overhead to track and correctly jump and switch the program instruction pages. This procedure was due to the continued growth in the size of the program code during the development of the DBOS. Due to time schedules it was easier to implement a paged-memory mechanism than to re-design the ASICs program memory addressing width.

A/D Converter

The A/D converter requires a 5-phase clock which is derived from the internal RC oscillator. The RC oscillator frequency is divided by 2 and then again by 5 to obtain the correct A/D clock. Each cycle of the A/D clock is approximately 22 usec in duration. The A/D is the longest (slowest) device withing the ASIC but this is due to the measurement method used in the A/D.

Analog-to-Digital conversion occurs by performing a series of comparisons to know values and then assigning a digital representation to the converted value. Speed and

35

resolution are sometimes inversely proportional. Given enough time, very accurate measurements can occur, however, time is usually critical to system operation.

The A/D converter performs a conversion for a duration relative to the desired level of resolution, in bits. The 5 conversion time is the period of the A/D -phase clock for  $2^{n+1}$  bits. The 10-bits resolution for temperature and pack voltage conversions require  $2^{11}$  clock cycles to complete while the 13-bits current conversion requires  $2^{14}$  clock cycles.

The A/D converter essentially performs only voltage conversions but these voltages can represent other measurements in the system, in this case, battery temperature and current as well. The pack voltage is measured through a resistive divider circuit. The pack temperature is measured as a voltage across another resistive divider where part of the divider circuit is a thermistor, a device who resistance changes with temperature in a known way. The pack current is measured as a very small voltage drop across a very small value sense or shunt resistor. The direction of the current is determined by a polarity of the voltage across the sense <sup>20</sup> resistor.

The A/D converter is an incremental delta-sigma converter, a particular type of an A/D implementation. This type of converter can perform bi-polar (both positive and negative measurements) using only a single voltage refer-<sup>25</sup> ence. The quantization error is also controlled very well by the delta-sigma design since the error is offset in both directions equally.

The A/D converter is not a sampling type implementation but instead integrates the analog input signal during the whole conversion cycle. This type of A/D/ is not sensitive to parameters such as the clocking frequency or waveform.

The A/D converter uses separate full-scale reference voltages for each type of measurement: current, voltage, and temperature. The current and temperature measurements use a 150 mV full-scale reference. The pack voltage measurements uses a 350 mV full-scale reference.

Current Measurement

The internal pack current is measured using a (shunt) 40 resistor connected in series with the power path of the pack. The voltage across this fixed value sense resistor is measured and converted to a representation of the current flowing in the pack. Direction of current flow is also determined. The resistance of the sense/shunt resistor must 45 not change due to temperature or other effects in order for the measurements to remain consistent and accurate.

The voltage value observed across the sense resistor is on the order of tens of microVolts (uV) or I/1,000,000 of a Volt. This is an extremely small value and is the most difficult measurement of the A/D. In order to provide accurate measurements, care is taken in the layout and routing of any part of this circuit, both internally and externally.

In order to accurate measure these very small voltages in the presence of internal and eternal noise, separate sense and 55 ground leads are used. Each end of the sense resistor has a sense lead (Vsh- and Vsh+) and the most negative end of the sense resistor also has an additional ground reference line, Vans. The Vans and Vsh- lines being separate help improve the noise immunity of the A/D current sense circuit. 60

Calibration of the current measurement requires two values: a correction factor or slope adjustment, and a correction offset. The Correction factor, Cf\_curr, is used to calibrate out the tolerance of the shunt sense resistor and the full-scale reference voltage. the correction offset, Co\_curr, 65 is used to re-zero the current measurement due to system offsets.

8

The current measurement equation is:

Ishunt=(Cf.curr/16384)\*(I\_A/D-Co\_curr)

I\_A/D is the raw digital conversion value of the current measurement. Ishunt is the actual current value reported in mA units.

Temperature Measurement

The internal pack temperature is measured using a temperature-varying resistance device (NTC) and a voltage divider string. The voltage across the NTC is converted into a temperature representation since the other resistance and reference voltage in the divider string are both known. The resistive voltage divider network is external to the ASIC.

To conserve power, the negative connection of the voltage divider string is connected only when a measurement is occurring. (If left connected, the resistive divider string would continually drain current, although very small amounts.)

The resistance value of the NTC decreases as the temperature increases but is nominal 10 kohms at 25° C. A look-up-table is used to convert the measured NTC voltage to actual temperature due to the slightly non-linear slope of the NTC curve. (Lower resistance=Higher temperature but not completely linearly.) Interpolation is used between lookup-table values.

Calibration of the temperature measurement requires two values: a correction factor or slope adjustment, and a correction offset. The correction factor Cf\_temp, is used to calibrate out the tolerances of the resistor divider network, the NTC, and the full-scale reference voltage. The correction offset, Co\_temp, is used to re-zero the temperature measurement due to system offsets. Not all versions of DBOS use both of these calibration correction values.

Due to the complications of measuring internal pack temperature during calibration, these correction values are not typically changed. The default values appear to work satisfactory, mostly since the temperature is only critical in a relative sense, not absolute. Accuracy for changes in temperature is critical, but not the absolute accuracy.

The temperature measurement equation is:

# $T\_LUT=(Cf\_temp/2048)*(T\_A/D-Co\_temp)$

T\_A/D is the raw digital conversion value of the temperature measurement. T\_LUT is the value used for a Look-Up Table conversion to an actual value reported in 0.1K units. (Note: Some versions of DBOS do not use the 50 Co\_temp value.)

Pack Voltage Measurement

The internal pack voltage is measured also using a voltage divider resistances and reference voltage in the divider string are known.

In some versions of the DBOS the resistive voltage divider network is external to the ASIC, in later versions (DBOS-II) it is internal to the ASIC. The external components are 1% values to maintain matched accuracy of the ratio. The internal components are less accurate for the exact values but the ratio is more closely matched and less likely to drift. However, this requires finer calibration with the internal version due to the initial wider variance in values.

To conserve power, the negative connection of the voltage divider string is connected only when a measurement is occurring.

Calibration of the pack voltage measurement requires two values: a correction factor or slope adjustment and a cor-

rection offset. The correction factor, Cf\_volt, is used to calibrate out the tolerances of the resistor divider network and the full-scale reference voltage. The correction offset, Co\_volt, is used to re-zero the pack voltage measurement due to system offsets. Not all versions of DBOS use both of 5 these calibration correction values.

The current measurement equation is:

### Vpack=(Cf\_volt/2048)\*(V\_A/D-Co\_volt)

V\_A/D is the raw digital conversion value of the pack voltage measurement. Vpack is the actual pack voltage value reported in mV units.

(Note: Some versions of DBOS do not use the Co\_volt value.)

Cell Voltage Measurements

In certain DBOS-II implementations used for LiION, individual cell voltages are measured in addition to the overall pack voltage. This is done for both safety and capacity calculation reasons. Each cell has its own voltage 20 from hours to days depending on the leakage of the monitoring connection and the cell stack voltage is measured by subtracting the individual voltages from the full pack voltage.

The measurement method is the same for the cell voltages since the ASIC uses an additional 2 pins for the added cell 25 monitoring points. Internal to the ASIC are resistive voltage divider networks to scale the cell voltage appropriately, just like the pack voltage measurement mechanism.

Due to additional components in the LiIon power path, some of the individual cell voltages, like the most negative 30 cell, have additional correction offsets added as series resistances. These allow compensation in the calculation for voltage drops which occur due to the addition power path components.

The individual Lilon cell voltages are used for all safety 35 and capacity calculations, while the pack voltage is only used for reporting the SBData value for Voltage when requested.

ROM

gram code software for the CPU instructions and the various look-up tables for self-discharge, charge efficiency, etc.

The ROM memory is 4096×12-bits in size due to the CPU's 12-bit program instruction width. This is equivalent to a 6k byte (8-bit) size memory. The ROM is encoded in the 45 conditions and responds to the Smart Battery address when ASIC's silicon as one of the last steps in the ASIC fabrication process. This allows it to be somewhat easily changed as changes in look-up value are required.

RAM

The Random-Access-Memory of the ASIC is a read/write 50 block of data memory which contains the many variables required to execute the DBOS algorithm. These variables and values include the learned functions such as FullChargeCapacity, and the pack-specific values such as DesignCapacity, DesignVoltage, SerialNumber, 55 ling the overall data flow. ManufactureDate, etc.

The RAM is organized as 128 bytes (8-bits per byte) some with write protection which requires password access in order to write to the RAM. A small portion of the RAM (used in the SBData ManufacturerData area) is used to 60 calculate a checksum. This checksum produces a known result if the contents of the RAM is correct. Otherwise, the value is incorrect and indicates that the RAM contents has been altered due to RAM data loss, an ESD event, or some other cause. When the checksum is incorrect, the RAM 65 contents are reset to power-on-reset defaults so that correct operation of the ASIC can continue.

RAM Data Back-up Circuit

Since the RAM contents are important to the operation of the ASIC, the data in the RAM is protected from accidental erasure and loss due to loss of power.

A RAM Data Back-Up circuit is used to maintain the contents of the RAM during loss of power to the ASIC, such as during a short-circuit condition, or during over-discharge.

The Data Back-Up circuit uses an external capacitor to maintain an acceptable voltage for the internal RAM. This capacitor is normally connected internally to the ASIC's 10 power supply, called Vasic or Vddd, through a PMOS transistor (FET). When the Vasic (Vddd) voltage drops below the POR threshold (approximately 2.0 V) then the capacitor is disconnected from the Vasic (Vddd) voltage and 15 the RAM is supplied from the capacitor alone.

The RAM typically requires only a few nano-Amps (1E-9 Amps) of operating current in its standby state (only maintaining itself, not being read or written). The external capacitor is thus able to maintain the RAM for anywhere capacitor, the internal FET switch, and the current consumption of the RAM itself.

When the Vasic (Vddd) voltage returns above the POR threshold (2.0 V to 2.4 V) then the FET switch re-connects the RAM to the main ASIC voltage to restore full operation. The contents of the RAM are then checked (in the POR procedure) using the checksum value and reset to defaults if the RAM data was not maintained.

Normally, RAM data is maintained since short-circuit conditions are usually only short duration events due to other pack protection devices such as PTCs and thermal fuses. 12C/SMBus Interface

The 12C/SMBus interface allows the ASIC to communicate with the outside world via a standard interface protocol using defined data sets. The 12C/SMBus interface can operate as either a slave, responding to requests for data, or as a master, generating alarm and charging broadcasts to another device.

The 12C/SMBus interface is a byte-wide hardware based The Read-Only-Memory of the ASIC contains the pro- 40 interface with a software link to the CPU. The first byte received is completely independent of the CPU but additional bytes are either received or the transfer aborted as controlled by the CPU.

The hardware 12C/SMBus interface monitors for Start recognized. If addressed correctly, an automatic ACKnowledge (ACK) is generated and the CPU is notified that a data request has been initiated.

The CPU then controls the transfer by informing the hardware interface to receive the next byte or terminate the transfer by generating a NOT ACKnowledge (NACK) at the end of the second byte.

Transfers continue in this manner with the hardware handling the individual input/output and the CPU control-

The hardware can respond to any 12C/SMBus clock speed but the CPU may require clock stretching between bytes during the ACK clock duration.

When a SBData request occurs, the CPU must calculate the appropriate value since there is not enough time or memory to pre-calculate all 34 SBData values. Due to long calculation times, the ACK clock is usually stretched (up to the 25 msec maximum allowed) while the CPU calculates the result requested.

The CPU can also initiate a 12C/SMBus communication when it determines that an alarm condition has been tripped (Alarm Warning) or when charging information should be sent to a Smart Charger (ChargingVoltage and ChargingCurrent).

When becoming a master device, the hardware interface notifies the CPU when the 12C/SMBus is clear and available, and then generates a Start condition and appro-5 priate clocking. The 12C/SMBus clock (CLK) frequency is a sub-multiple of the internal RC oscillator frequency.

Misc Components

Clock generating circuit

The clock generation circuitry controls two separate oscillator devices: an internal RC oscillator which is used for all CPU, A/D, and 12C/SMBus timing; and an external crystal which is used solely for the measurement and cycle timing of the software executing on the CPU. The internal RC oscillator is variable with voltage and temperature and nal crystal is highly stable and accurate over temperature and voltage so it is used for the critical time events, such as self-discharge estimations.

The RC oscillator normally runs at 450 to 460 kHz frequency but may vary to as low as 390 kHz or as high as 20 FullChargeCapacity) or Absolute (related to 510 kHz. This frequency is divided by 4 for the internal CPU clock and by 10 for the A/D measurement clock. It is also divided by either 10 or 8 for the 12C/SMBus alarm frequency clock when the ASIC must be an 12C/SMBus master device. 25

The ONLY way to measure the internal RC oscillator frequency is to set a SBData RemainingTime or RemainingCapacity Alarm and then wait for an AlarmWarning message to be generated. The clock frequency of the Alarm-Warning generated by the ASIC's 12C/SMBus circuit is the 30 RC oscillator's frequency divided by 10 or 8, depending on the DBOS version.

The internal RC oscillator is shut off when the ASIC enters Sleep Mode.

The external crystal operates at a very exact 32.768 kHz 35 and is used for all the exact timing within the ASIC. This frequency is divided down to a 1/2 Hz (500 msec) signal which is main cycle control interrupt used by the ASIC's software. The capacity algorithm is re-started based on this signal (depending on the mode of operation at the time, Run, 40 A/D logic interface, the CPU to RAM and ROM interface, Sample, or Sleep); the A/D measurements are started based on this signal; and the Wake-Up comparator is activated when in Sleep Mode based on this signal.

The external crystal is always running as long as the ASIC supply voltage is greater than the Power-on-Reset (POR) 45 level of 2.0 to 2.4 Vasic, regardless of the mode of operation.

Wake-Up Comparator Circuit

The Wake-Up Comparator circuit is used when the ASIC is in the Sleep Mode. Once in this mode, all internal operation of the ASIC stops (except for the control of the 50 external crystal). In order to detect an exit from the Sleep Mode into either the Run or Sample Modes, a Wake-Up Comparator must be used.

The Wake-Up Comparator is simply a voltage comparator which is turned on once every 500 msec cycle to roughly 55 measure the full pack voltage. This is not an A/D measurement, just a rough measurement of the pack voltage using a simple resistive divider circuit. The pack voltage is then compared to the internal band-gap reference (1.25 V nominal).

If the pack voltage is greater than the preset threshold, usually just below the nominal open-circuit pack voltages of 7.2 V, 10.8 V, 12 V, 14.4 V, etc. then the Wake-Up Comparator "awakens" the rest of the ASIC. (The actual comparator voltage value varies with the silicon process but is 65 approximately 1.17 V/cell for NiMH versions and 3.55 V/cell for LiION versions.)

To conserve power through the resistive divider circuit, this divider is only switched on for approximately 30 usec every 500 msec cycle.

LED Drivers

The LED driver circuit activates 5 LED outputs, of which only 4 are used for LEDs. The 5th LED driver output is either not used or used for other control functions (non-LED related) on some DBOS versions.

The LEDs are activated by a press of the LED switch or by invoking the LED test via a SBData command in the 10 BatteryMode register.

A press of the switch will activate all the LEDs corresponding to the current battery State-Of-Charge (SOC) for approximately 3 to 5 seconds. The LED test using the therefore not used for exact time measurements. The exter- 15 BatteryMode value of 1000h illuminates each LED in sequence for approximately 1/3 second.

> The illumination sequence (for SOC or test) starts with the LED closest to the switch, referred to as the 10% LED.

The SOC displayed is either Relative (related to DesignCapacity) and is determined by the value in the Kind-Of-Display (KOD) byte or bit in the ManufacturerData area. A KOD value of zero (0) indicates RelativeSOC will be displayed.

The LEDs are activated by internally connecting the cathode to the Vdss (ground) reference within the ASIC. This completes the circuit from the Vpack input, through the current limiting resistor, and the LED itself.

Instead of a continuous direct connect completing the circuit, the LEDs are switched into the complete circuit for 200 usec every 1 msec. This corresponds to a 1 kHz multiplex rate.

To achieve the effect of a continuous illumination, the LEDs are driven with a peak current of 25 to 50 mA.

Interface Circuits

There are numerous other interface circuits within the ASIC which perform additional input functions. Examples include the external crystal start-up and drive circuit which enables the operation of the external crystal. The CPU and the 12C/SMBus to CPU interface, etc.

Hardware Modes of Operation:

There are three (3) basic modes of operation of the ASIC: Run, Sample and Sleep. The separate modes are included to improve the power consumption of the ASIC to limit the drain on the battery cells during operation. Basic characteristics of each mode are listed below along with entry and exit conditions.

During each of the modes of operation there are slightly different CPU and A/D processes to compensate for the differing operation. During a normal process cycle, the CPU will go to 'sleep' if no further calculations are required and no 12C/SMBus communications are requested. This internal CPU mode, also termed 'sleep' is NOT the same as the whole ASIC going into the Sleep Mode.

Run Mode: Entry/Exit

The main operational mode of the ASIC is Run Mode: all components are active at all times. Entry into this mode is from both Sample or Sleep Mode depending on measured current and pack voltage values. Measurements and capacity calculations occur during every 500 msec operation cycle.

Run Mode is exited when the measured current drops into the Sample Mode limit or when the measured voltage drops below the Sleep Mode threshold.

Sample Mode: Entry/Exit

Sample Mode is the first level of lower power consumption used by the ASIC to prevent deep discharge of the

battery cells. It is primarily used for a battery at rest, being neither charged or discharged.

Sleep Mode is entered when the current measurement reports a pack current less than the Sample Mode threshold, typically +/-10 mA. This current value usually indicates a battery at rest or with only a maintenance charge or low-rate discharge.

During Sample Mode, the A/D is only started once per second (DBOS-I/IA) or once per 3 seconds (DBOS-II) to take voltage, temperature, and current measurements. All capacity calculations and 12C/SMBus communication requests still operate at their normal rate as in Run Mode. But the judicial use of the A/D, which uses more power in operation, reduces the ASIC's power consummation significantly.

frequency of current measurements so long periods of time in Sample Mode do NOT affect accuracy.

Sample Mode is exited when the current measurement returns a current greater than the threshold which returns the ASIC to Run Mode. Sample Mode is also exited when 20 entering Sleep Mode (see below).

Sleep Mode: Entry/Exit

Sleep Mode is the lowest power consuming state of the ASIC and is essentially the "off" state. The only devices in the ASIC still functioning are the external crystal drive 25 circuits, the Wake-Up Comparator Circuit, and the RAM data back-up circuit.

Sleep Mode is entered when the voltage measurement returns a voltage less than the Sleep Mode threshold, usually 0.9 V/cell for NiMH and 2.7 to 2.4 V/cell for LiION. These 30 voltages indicate a deeply discharge battery which should NOT be discharged further.

In DBOS-I/IA Sleep Mode is entered from either Run Mode or from Sample Mode whenever the 0.9 V/cell limit is reached. In DBOS-II Sleep Mode can only be entered 35 being drawn from the battery, current values averaged over from Sample Mode (unless a safety FET activation occurs). This way, the discharge must stop or slow prior to entering Sleep Mode.

During Sleep Mode, no capacity calculations or communications are preformed.

Sleep Mode is exited only via the Wake-Up Comparator Circuit which monitors the pack voltage. The smart battery device of the present invention is intended for use with an intelligent host device such as a portable computer, portable video camera or cellular telephone having a system man-45 agement bus and a smart charger, or an intelligent host device having a system power manager that can receive and send data over a system management bus.

A representative example of such a system is illustrated in FIG. 1, wherein the smart battery 10 is connected to a power 50 plane 12 to supply and receive electrical energy over the power plane, and a system management bus 14, which is a bi-directional modified I2C data bus (communication interface) that communicates with a host device 16 which may be a portable computer. The host device 16 may be 55 powered by the smart battery 10, or by the system power supply 18 and a conventional AC source 20. A system power supply or power management system also communicates with a smart charger 22 which may be used to determine the rate and duration of charge sent to the smart battery by the 60 power supply. Smart charger 22 also communicates with the system management bus 14, and may receive a temperature signal representative of battery cell temperature on a separate line feed 24. A detailed functional description of the system management bus 14 (bi-directional modified I2C data bus) can be found in the Intel\Duracell System Management Bus Specification, Rev 0.95, (April 1994).

The system power management system 18 may supply or draw power to/from the smart battery 10 over power plane 12, depending upon the state of charge in smart battery 10, and depending upon the presence or absence of power at AC source 20.

The smart charger 22 may periodically poll the smart battery 10 for charge characteristics, and adjust output to match a smart battery charge request. Optionally, and if selected by the user of the host device, the smart charger 22 can override the smart battery's charge rate request and charge the smart battery at a higher or quick charge rate. The user of the host device does not necessarily need to override the smart battery's request. As will be explained in greater detail below, the smart battery may periodically broadcast All capacity calculations compensate for the reduced 15 the desired charging current, or the smart charger 22 polls the smart battery for a charging current. The host or the charger need not comply with the smart battery's request and can provide a greater or lesser amount of power than requested.

> The host device 16 may communicate with the smart battery over the system management bus 14 and request information from the battery for use in the system power management scheme, thereby providing the user of the host device with information about the battery's present state and capabilities. The host device 16 will also receive notice of critical events, including alarm conditions, remaining capacity below a user set threshold value, a remaining run time below a user set threshold value, or an end of discharge signal. The alarm conditions include but are not limited to overcharging, overtemperature, a remaining charge capacity below a predetermined or user set capacity, or, a run time below a predetermined or user set run time remaining.

> As will be hereinafter explained in greater detail, the smart battery can report out an instantaneous current value predetermined time intervals, present temperature and present voltage.

The smart battery may also report out a number of battery status indicators, indicating whether or not the battery is 40 charging or discharging, that charging is complete, or, that the battery is fully discharged.

In addition, it can provide calculated values including run time remaining at a present current usage, a run time remaining at an average current use, a run time remaining at optimal current use, and a predicted run time remaining at a host device selected current level (discharge rate).

The smart battery device 10 is also provided with a read-only memory (ROM) that is manufactured to contain a set of predefined battery identification parameters which may include manufacturer data, cell chemistry, design capacity, design voltage, and a unique device identification number. The predefined battery identification parameters are available, for either the host device or the smart charger, to assist them in the selection of optimal usage and charge parameters for the smart battery.

The smart battery is also capable of recommending a desired charge current, reporting a time remaining to full charge, a battery capacity available at full charge, and the number of times the battery has been charged or discharged.

The smart battery of the present invention utilizes a hybrid integrated chip (IC) containing an embedded microprocessor and a novel analog to digital connector which receives analog signals from the battery and converts them to digital signals representative of battery voltage, current 65 and temperature. The smart battery microprocessor then calculates actual charge parameters over time from these digital signals according to a predetermined algorithm in

which CAP<sub>rem</sub> is the remaining capacity of the battery which is continuously assigned a new value to reflect adjustments for effective charge, discharge, and self discharge.

The charge delivered to the battery is measured, and for a NiMH battery is adjusted by an efficiency factor which is 5 a function of current, temperature, and relative state of charge. It should be mentioned that the remaining capacity, CAP<sub>rem</sub>, and the relative state of charge, SOC, represent the same thing (remaining battery capacity) and differ in that relative state of charge is indicated as a percentage of the last 10 full charge capacity. The charge efficiency for a NiMH battery is a value determined as a function of the above variables and may be derived from a look up table, hereinafter described with respect to FIG. 14, or calculated from a formula which provides a stepwise approximation of charge 15 efficiency behavior, depending upon current, temperature and state of charge. It is understood that the charge efficiency factor can be obtained from a response equation or interpolation between several different values stored in memory.

Likewise, the remaining battery capacity CAP<sub>rem</sub> is dec- 20 in FIG. 2. remented by the measured discharge rate over time. A predictive model of residual capacities determines expected CAP<sub>rem</sub> for a present current and temperature. This predictive model may also estimate when the battery voltage will drop to a predetermined cut-off voltage of the present rate of 25 discharge. This residual capacity model may be calculated from a formula or obtained from a look up table, which includes values of residual capacities as a function of discharge current and temperature.

Finally, CAP<sub>rem</sub> is also adjusted by subtracting self dis- 30 charge. For a NiMH battery self discharge is calculated as a function of temperature and state of charge, and is always subtracted from CAP<sub>rem</sub>, regardless of whether the battery is discharging or being charged. Self discharge may be derived from a look up table of empirical models of identical cell 35 chemistry that predict self discharge as a function of temperature and state of charge, or may be calculated by the microprocessor.

As will be hereinafter explained in greater detail,  $CAP_{FC}$ logic incorporated in the capacity algorithm.

The charge algorithm terminates its integration of the present discharge state when it reacts to an end of discharge (EOD) signal between 0.9 volts/cell and 1.1 volts/cell and preferably 1.02 volts per cell. At that point it resets CAP<sub>rem</sub> to a new learned value of residual capacity, as determined from the integration of the discharge current, as a function of discharge current and temperature.

As will be hereinafter explained in greater detail, the reset logic will reset  $\text{CAP}_{FC}$  as a function of which EOD signal 50 was acted on. Thus a new CAP<sub>FC</sub> value for the smart battery's actual capacity is learned after each full discharge cycle, as a function of the last fully integrated battery discharge cycle. The smart battery 10 of the present invention is thus able to self correct  $CAP_{FC}$  within one full cycle 55 to readjust its capacity at each EOD, and effectively relearn full battery capacity within a single cycle, even if all prior battery history has been extinguished by virtue of a catastrophic memory failure. The smart battery of the present invention is therefore able to accurately predict actual 60 capacity, and typically is able to correctly predict the remaining run time to empty within a few minutes for a 2400 maH battery.

Smart battery 10 of the present invention is more fully illustrated in FIG. 2 which is a simplified block diagram of 65 the smart battery, an advanced design multi-pin connector, and a battery module 28 which includes a pinout diagram of

the hybrid ASIC 32 used in the present invention. As illustrated in FIG. 2, the smart battery device 10 includes a plurality of rechargeable cells generally indicated at 26 which may be Nickel Metal Hydride (NiMH) or Nickel Cadmium (NiCad) cells.

For the purposes of an illustrative but not limiting example, in the following specification, 6 NiMH cells having a nominal 2400 maH capacity, will be assumed. Such an arrangement of cells is particularly appropriate for powering a portable computer.

A suitable advanced design multi-pin battery connector **30** is used to connect the smart battery to a host device 16 or power supply 18, as previously described with respect to FIG. 1. The multi-pin connector 30 includes a positive power supply terminal **31** which is connected to the positive terminal of the first cell, and a negative power supply terminal 33 which is connected to the negative terminal of the last cell. A plurality of rechargeable cells may be connected in series therebetween as illustrated schematically

The smart battery module 28 includes a hybrid IC 32 containing a microprocessor 50 (FIG. 3) and a plurality of sensor means for generating analog signals representative of battery voltage, current and temperature. The module also includes a series of four (4) LEDS 34 driven by an LED drive circuit 53 and a manually actuable switch 35 which may be manually actuated by an end user to determine the state of charge in the battery even when the battery has been removed from the host device 16. The LEDS 34 may be used to represent a relative state of charge (SOC) in a logic scheme as follows. If the state of charge is greater than 75% (or less than 100%) then all 4 LEDS are illuminated. If the SOC is from 50% to 75%, then 3 LEDS are illuminated; if SOC is from 25% to 50%, then 2 LEDS are illuminated; if SOC is from 10% to 25%, then 1 LED is illuminated, and if SOC is less than 10%, a single LED is flashing. As mentioned above, relative SOC is remaining capacity relative to last full capacity.

As shown in FIGS. 2 and 3, the hybrid ASIC 32 also is a learned value which is self correcting because of reset 40 includes an external crystal **36** operating at a fixed frequency which is used as a time base for integration of battery current over time, and to ensure stable start up after a prolong standby period when power is reapplied to the smart battery 10. The smart battery of the present invention utilizes two separate oscillators, a low power RC oscillator 48 formed within the hybrid IC 32 and used as an operating clock for the hybrid IC and the A/D converter 60 therein, and, the external crystal 36. As will be hereinafter described in greater detail, the external crystal 36 is used to restart the measurement period after each predetermined interval to provide for accurate measurements and integration of battery conditions, regardless of battery temperature, which can adversely affect the accuracy of the internal oscillator. The frequency value of external crystal 36 may range from 10kHz to 66 kHz and the frequency value of oscillator 48 may range from 450 kHz to 460 kHz.

> The hybrid IC 32 includes a MIKRON GmbH low cost, high performance, CMOS 8 bit microcontroller ( $\mu$ P) 50 with an advanced RISC architecture. A reduced set of 32 instructions that are all single cycle instructions (except for program branches which are two cycles), and a Harvard architecture scheme achieves a high level of performance with minimal power drain. The microprocessor operates at a clock input anywhere from DC to 10 MHZ with 12 bit wide instructions and 8 bit wide data path. A free programmable Counter/Timer circuitry is provided as well as a free programmable Watchdogtimer. Additionally, the microproces-

10

15

20

25

30

50

65

sor is addressable in direct, indirect, and relative addressing modes. The microprocessor is commercially available from Mikron Gmbh, located at Breslauer Straße 1-3, D-85386, Eching, Germany, and is available in the U.S.A. through MICROCHIP Technology, Inc., Chandler, Ariz., U.S.A.

The hybrid IC 32 also includes a plurality of analog circuits which are used, in combination with external analog sensors, to generate digital signals representative of battery voltage, current and temperature as will be hereinafter explained.

For example, as shown in FIG. 2 battery voltage is obtained from a voltage divider circuit which includes R1 and R2 which are internally switched by a NMOS transistor within the hybrid IC 32 to provide voltage measurement during a small portion of each measurement interval, thereby minimizing current drain on the battery cells 26.

The measurement of battery temperature is accomplished with an NTC-thermistor, illustrated as  $R_{NTC1}$  in FIG. 2, which varies resistance as its temperature varies. A resistor R3 is connected in series to form a voltage divider circuit between V<sub>ASS</sub>, (negative analog power supply voltage)  $V_{TEMP}$ , (the temperature voltage input) and  $V_{REFT}$ , which is a reference voltage applied to the thermistor/resistor string by the hybrid ASIC 32 at pin  $V_{REFT}$ . The temperature voltage input is measured at V<sub>TEMP</sub> according to the following formula:

$$\frac{V_{TEMP}}{V_{REFT}} = \frac{R3}{R3 + R_{NTCI}} \times V_{REFT}$$

wherein the NTC1 value may be 10 kohms at 25° C. and varies with temperature. If desired, a look-up table with a plurality of temperature values and a plurality of  $V_{TEMP}$ values may be defined to calculate the battery temperature, and between these values, the temperature is linearly inter- 35 polated by the microprocessor within IC 32.

The measurement of battery current is measured through a shunt resistor, illustrated in FIG. 2 as  $R_{shunt}$ , that is connected in series with the battery cells and negative terminal 33 of cell pack 26. The shunt resistor is of small 40 value, but may range anywhere from 1 mohm to 200 mohms depending on the number of cells and expected usage of the battery. The voltage drop across the shunt is sensed between  $V_{SHUNT+}$ , the shunt resistor positive input pin of ASIC 32, and  $V_{ASS}$ , the negative analog power supply voltage. 45

As shown in FIG. 3, whenever the analog signals representing battery voltage, current, and temperature are obtained, they are input into an ASIC multiplexor or switching network 55 which enables only one analog signal at a time to be input to the A/D converter 60 for digital conversion. The switching network acts in conjunction with digital logic circuitry for informing the A/D converter, via line 55', shown in FIG. 3, of the amount of integration cycles to perform depending upon the type of measurement to be converted. For instance, more integration cycles are needed 55 when making a current measurement conversion to ensure a higher bit resolution as compared to when a voltage or temperature measurement is being converted, as will be explained in further detail below with respect to FIG. 8.

A general schematic diagram of the A/D converter 60 is 60 shown in FIG. 4. In the preferred embodiment, the A/D converter 60 is a bipolar, high resolution, incremental sigmadelta converter and consists of three parts: a bandgap reference circuit 62 which provides a preset analog voltage which is used as an analog ground for the A/D; a voltage divider network 64 which divides the present voltage to the analog voltages which are used as the full-scale voltage for

the A/D; and, a sigma delta circuit 66 for converting the analog signal to a digital word output at line 69. FIG. 4 also show a schematic illustration of a switch 63 which is used during an auto offset current calibration procedure pursuant to the present invention. The switch 63 is provided at an input to the A/D converter, and is closed during normal operation thereof. Periodically (e.g. every 80 seconds), the switch 63 is opened to provide a 0 input to the A/D converter. The output of the A/D converter is then measured, and if different from 0, the measured value is used as a current offset during the subsequent set of A/D conversions to provide a zeroing compensation therefor.

A/D control circuit 68 having a clock input from the IC oscillator, provides the control for the sigma delta converter which has a different degree of resolution depending on the type of measurement. For instance, in one embodiment of the invention, the A/D converter was configured as having a resolution of 13 bits and a conversion time ranging from 300 to 400 msec for current measurements, and, was configured as having a resolution of 10 bits and a conversion time ranging from 30 to 60 msec for voltage and temperature measurements. The timing diagram for the voltage, current, and temperature measurements in each operating cycle is illustrated as 58a in the timing of operating cycles diagram of FIG. 8, as explained below.

In one embodiment of the invention, the voltage divider circuit 64 of the A/D converter divides the preset bandgap reference voltage into the following full scale voltages: a 150 mV signal used as the full scale voltage for the battery current measurement; 150 mV, 250 mV, or 350 mV signals used as the full-scale voltage for the battery pack voltage measurement and dependent upon the number of battery cells; and 150 mV used as the full-scale voltage for the battery temperature measurement. These values are illustrative and may vary as battery design varies.

The A/D converter of the smart battery device utilizes a sigma-delta converter circuit 66 as explained above in view of FIGS. 4 and 6. Details of the sigma-delta converter circuit 66 capable of bipolar conversion are explained hereinbelow in view of FIGS. 5(a),5(b) and FIGS. 6 and 7 which illustrates switching capacitor network for inputting positive and negative voltage values negative into a switching capacitor network for input into an integrator circuit 88 and comparator circuit 89 for output into control and logic circuit 68. In the reference, Jacques Robert et al., (1987) "A 16-bit Low-Voltage CMOS A/D Converter", IEEE Journal of Solid-State Circuits, Vol. sc-22, No. 2, 157-159, an incremental (integrating) sigma-delta converter implementing 4- $\mu$ m CMOS, switched capacitor technology similar to that implemented in the A/D converter of the smart battery device is disclosed. What is described in the reference is a simplified, unipolar A/D converter that is largely insensitive to variations in clock frequency and clock waveforms due to the fact that all signals are represented by charges, rather than currents, in a switched capacitor integrator that forms the core of the converter.

To measure positive and negative input voltages, a negative power supply is necessary in addition to the positive voltage supply. Thus, where it is desired to measure negative voltages (or currents) such as smart battery discharging current, external components (such as invertors) and circuitry that consume extra power are required, and the prospect of utilizing such circuitry for the low power application such as needed in the smart battery device of the instant invention, is diminished. Instead, to overcome this drawback, the A/D converter 60 of the instant invention does not utilize a negative voltage power supply, but makes use

of an available on-chip A/D bandgap reference voltage "AGND" to be used as a virtual ground. The concept of utilizing a "virtual ground" is based on the fact that a voltage stored on a capacitor can be transferred to another d.c. voltage reference point using analog switches with virtually 5 no loss of charge.

In FIG. 5(*a*) there is represented a first embodiment of the inventive circuit arrangement, consisting of three switches S1 through S3, and four connectors A1 through A4 and a capacitor C1 (with the capacitance C1). The connectors A1, 10 through respectively A4 are at the potentials  $\phi_1$  through respectively A4 are at the potentials  $\phi_1$  through respectively  $\phi_4$ , Thereby, the switches S1, respectively the parallel-connected/S2 and S3 are on one of one or respectively one other side of the capacitor C1.

In the following there is described the operation of the 15 inventive circuit arrangement. At the beginning, the switches S1 and S2 are closed and the switch S3 is open. The capacitor charges itself up due to the voltage differential  $\phi_1 - \phi_2$  and stores a charge C1×( $\phi_1 - \phi_2$ ).

In the next step of the inventive process, the switches S1 20 and S2 are opened and one pole of the capacitor is connected through switch S3 with a potential  $\phi_3$ . Present at the capacitor C1 is now a voltage  $\phi_3 + (\phi_1 - \phi_2)$  which can be tapped off through connection with the connectors A3 and A4 which lie on the potentials  $\phi_3$  and  $\phi_4$ . 25

In FIG. 5(*b*) there is now represented a further embodiment of the present invention whereby an additional switch S4 is provided which prevents in the opened condition thereof that at the connector A4 after closing of the switch S1, the presence of a potential  $\phi_1$  for the tapping off of the 30 voltage  $\phi_3+(\phi_1-\phi_2)$  at the connectors A3 and A4.

In FIG. 6 there is illustrated the schematic circuit diagram of the inventive circuit arrangement in a switched capacitor A/D converter. The A/D converter 66 possesses an operational amplifier 88 which is utilized as an integrator, and an 35 operational amplifier 89 which is utilized as a comparator. The non-inverted input of the comparator 89 by means of the line 50 stands in connection with the output of the integrator 15. The inverted input of the comparator 89 and the noninverted input of the integrator 88, are connected with a 40 reference potential AGND (analog ground=1.25 volt). The output of the comparator 89 is "high", in the event that the output voltage of the integrator 88 is higher than the reference voltage AGND and "low" in the event that the output voltage of the integrator 88 is lower than the reference 45 voltage AGND. By means of the lines L1, L2, L3 and L4, the integrator 88 or, in essence, the inverted input and the output of integrator 15 have connected in parallel, therewith a capacitor C2 with a capacitance C2. The capacitor C2 has a switch SR connected in parallel therewith through lines L1 50 and L5, which can effectuate a discharge of the capacitor C2. Through a line 56, the inverted input of the integrator 15 stands in connection, by means of a switch S5 and a line L7, with a capacitor C1 having the capacitance C1. A line L8connects the line L7 through a switch SI and the line L4 with 55 the output of the integrator 88. The line L9 connects the pole of the capacitor C1 facing towards the integrator 88 in FIG. 6 with a line L10, which stands in connection through the line L11, L12 and respectively L13, with the switches S4, S7 and, respectively S6. Connected to the other pole of the 60 capacitor C1 is a line L14, which is connected through the switch S3 with the reference voltage AGND=1.25 volt. A line L15 stands in connection with line 114 and connects through the lines L16, L17, and respectively L18, the pole of the capacitor C1, which faces away from the integrator 88 65 in FIG. 6, with the switches S2, S1, and respectively, S8. The internal mass of the chips  $V_{ss}=0$  volt stands through the line

20

L19 and, respectively, L20, in connection with the switches S8, respectively, S6. In this matter, through suitable opening and closing of the switches S8 and 86, the voltage  $V_{ss}$  can be applied to both poles of the capacitor C1. The input voltage  $V_{IN}$  which is to be digitalized stands in connection with the switches S1 and, respectively, S7 through lines L21 and, respectively, L22. In this manner, through suitable opening and closing of the switches S1 and S7 can the input voltage  $V_{IN}$  be applied to presently one pole of the capacitor C1. The reference voltage  $V_{REF}$  which determines the resolution of the A/D converter is connected through lines L23 and, respectively, L24 with the switch S2 and, respectively, S4. In this manner, the reference voltage  $V_{REF}$ , which, for example, consists of 150 milli- volt, can be applied to one of the two poles of the capacitor C1. The switches S1, ... S8, SR and SI are preferably CMOS switches, especially CMOS transmission gates. The connection of the input voltage  $V_{IN}$ , the reference voltage  $V_{\it REF}$  and the mass  $V_{\it ss}$  with the input capacitor C1 of the A/D converter is known in the technology. Inventively there is connected through the switch S3 a reference voltage AGND=1.25 volt ( $V_{ss}$ =0 volt) to the input capacitor C1. Similarly, through the inventive circuit there is facilitated that  $V_{IN}$ ,  $V_{REF}$  and AGND can be applied to both sides of the input capacitor C1, which presently causes a charging up at different polarity of the capacitor C1.

In FIG. 7, there is illustrated the operation of the A/D converter in a phase diagram. Thereby, S1 through S8, SR and SI designate the switches of the A/D converter 66 pursuant to FIG. 6, and CK is the pulse signal of the comparator 89 in FIG. 7. CK' represents a further tapped-off pulse signal.

In the diagram, the switch conditions fluctuate between 0 and 1, whereby 1 signifies that the switch is closed, whereas 0 stands for the opened switch. The operation of the A/D converter can be divided into four phases which are designated with I, II, III and IV whereby I designates a RESET or resetting phase; II an integration phase, III and inverting phase and IV an integration phase of the input voltage of reverse polarity or sign. The cycle is more finely subdivided into steps i, . . . xiv. In step i only the switch SR is closed, whereas all other switches are opened. This causes a discharge of the capacitor C2. In step ii, the switches S1 and S6 are closed, whereas all remaining switches remain further open. This causes a charging up of the capacitor to a charge  $\Delta Q = C1 \times (V_{IN} - V_{ss}) = CI \times V_{IN}$ . In step iii, the switches S3 and S5 are closed, whereas all other switches remain open. One pole of the capacitor is now set to the potential AGND, whereas the other pole of the capacitor C1, through closing of the switch S5, stands in connection with the capacitor C2. There now takes place a charge transfer from the capacitor C1 to the capacitor C2. Inasmuch as the integrator of 15 resultingly causes the two input potentials to be equalized, there is present at the output of the integrator 15 the output voltage  $V_{OUT}$  equal-(C1/C2)× $V_{IN}$ +AGND. In step iv all switches are opened and the comparator pulse CK is 1, meaning, the comparator 20 carries out a comparison between V<sub>OUT</sub> and AGND. Upon the result of this comparison there now depends the further cycle. The representation of the switch conditions in step v must be understood in the following manner. In step v the switches S2 through S8 are not closed, but the switches S2 and S6 are closed, and S1, S3, S4, S5, S7, SR and SI are open, in the event that the output of the comparator is 0, in effect "low", while the switches S4 and S8 are closed and S1, S2, S3, S5, S6, S7, SR and SI are open when the output of the comparator is 1, meaning, "high", and in other instances remain open. When the output of the comparator is 0, meaning the output voltage

10

15

20

$V_{out}$  is lower than AGND, then the switches S2 and S6 are closed. At the capacitor C1 there are now present  $V_{REF}$  and  $V_{ss}$ . In the instance in which the output of the comparator is 1, meaning,  $V_{OUT}$  is higher than AGND, then the switches S4 and S8 are closed, whereby similarly  $V_{ss}$  and  $V_{REF}$  are present at the two poles of the capacitor C1, but with the reverse sign or polarity than in the instance in which the output of the comparator is 0. In step v, the switches S1, SR and SI are opened, and in step vi, the switches S3 and S5 are closed (compare step iii) which causes that the capacitor C1 and C2 are interconnected. Similarly, voltage AGND is applied to one pole of the capacitor C1. There again, in turn takes place a charge transfer between the capacitors C1 and C2, as result of which a voltage-(C1/C2)× $\bar{V}_{REF}$ +AGND is added to or, respectively, subtracted from that of the output voltage of the integrator 88, in accordance with the result of the comparison by the comparator in step iv. Inventively, also during the phase II there is processed an input voltage which is phase shifted with respect to AGND, with a reference voltage which is shifted relative to AGND. Similarly, at the non-inverted input of the integrator **88** and the inverted input of the comparator 89 there lies AGND, which causes that the output voltage is referenced to AGND and causes a comparison by the comparator 89 not with V<sub>ss</sub>=0 voltage, but with AGND=1.25 volt.