## June 11-12, 1991

Santa Clara Marriott Hotel Santa Clara, CA IEEE Catalog No. 91TH0359-0

Library of Congress No. 89-644090

# 1991 PROCEEDINGS EIGHTH INTERNATIONAL IEEE VLSI MULTILEVEL INTERCONNECTION CONFERENCE

IN COOPERATION WITH IEEE Electron Devices Society

Find authenticated court documents without watermarks at docketalarm.com.

ţ,

5

# EIGHTH INTERNATIONAL VLSI MULTILEVEL INTERCONNECTION CONFERENCE PROCEEDINGS

Papers have been printed without editing as received from the authors.

All opinions expressed in the Proceedings are those of the authors and are not binding on The Institute of Electrical & Electronics Engineers, Inc.

#### **IEEE Catalog Number 91TH0359-0**

Library of Congress No. 89-644090

ISBN Number 0-87942-673-x Softbound N/A Casebound 0-87942-674-8 Microfiche

#### PERMISSION TO REPRINT OR COPY

Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limits of U.S. copyright law for private use of patrons those articles in this volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 21 Congress St., Salem, MA 01970. Instructors are permitted to photocopy isolated articles for noncommercial classroom use without fee. For other copying, reprint or republication permission, write to Director, Publishing Services, IEEE, 345 E. 47 St., New York, NY 10017. All rights reserved.

Copyright © 1991 by the Institute of Electrical and Electronics Engineers, Inc.

#### A FOUR-LEVEL-METAL FULLY PLANARIZED INTERCONNECT TECHNOLOGY

#### FOR DENSE HIGH PERFORMANCE LOGIC AND SRAM APPLICATIONS

#### Ronald R. Uttecht and Robert M. Geffken IBM General Technology Division Essex Junction, Vermont 05452

#### ABSTRACT

This paper describes a four-level-metal (4LM) interconnect technology used to wire high-density, high-performance logic and SRAM chip designs. Process features include oxide planarization under all metal levels, tungsten studs for contacts and interlevel vias, layered titanium and aluminum-0.5% copper metal lines patterned by reactive ion etch (RIE), and fusible metal links for redundancy applications. Functional 300K circuit ASIC logic test sites (4LM) and 256K SRAMs (3LM) have been fabricated in both 125-mm and 200-mm wafer sizes. Process details are described along with the results of standard electrical tests and reliability stresses.

#### INTRODUCTION

The continuing drive to achieve greater density and performance in CMOS logic and SRAM applications is placing ever-increasing demands on multilevel interconnection technology. Indeed, present ASIC offerings with high circuit counts and large chip sizes are usually wiring-limited; it is not unusual to have less than 60% of the available circuits wired on these chips. Current-generation designs require up to five levels of metal to satisfy all of the wiring needs. Maximum layout efficiency requires the ability to make vertical connections between any of these metal levels in a minimum space. The interconnect technology chosen to accomplish this task must also meet the performance and reliability targets of the designs and be manufacturable.

The interconnect process described in this paper was developed and piloted in a 125-mm logic manufacturing line and has been installed in a 200-mm manufacturing line which it shares with 4-Mbit DRAM production at IBM's Essex Junction, Vermont, facility. In fact, this logic interconnect process was developed using the DRAM process as a base [1], and then modified in several areas to meet the needs of logic. Various process modules from IBM's East Fishkill [2], Yorktown [3] and Essex Junction development areas are included in the final integrated process.

#### TECHNOLOGY FEATURES

This advanced interconnect technology provides logic and SRAM designers with the wireability features required to manufacture high-density, high-performance logic and SRAM products. The wiring features include a local interconnect level and up to four levels of reactive-ion-etched (RIE) layered titanium and aluminum-0.5% copper wiring; each metal level is fabricated on top of a planarized insulator.

DOCKE

The metal pitch and thickness for each of the interconnect levels are listed in Table 1.

Vertical tungsten stud vias are used to interconnect the wiring levels and stacked contacts and vias are allowed in the various product designs. As a further enhancement to wireability, metal borders around studs are not required for either the topside or underlying metal. Laser-blown metal fuses are also included in this technology and are primarily used for redundancy in stand-alone and imbedded SRAMs. Finally, in response to the I/O requirements of VLSI logic, an area array of up to 1600 lead/tin C4 terminals per chip is offered.

#### PROCESS DESCRIPTION

The basic process flow for each of the metal, insulator, and stud levels is repetitive and illustrated in Figure 1. The Al-Cu based film is sputter-deposited onto a planarized substrate, photo-patterned and then defined by RIE. A PECVD oxide is subsequently deposited over the underlying metal pattern. A deposition-etch-deposition sequence is used to provide adequate insulator-fill between minimum-spaced metal lines. The oxide is then planarized using a chemical-mechanical polish technique (CMP). Next, via-photo and RIE are employed to form nearly vertical vias down to the underlying metal level. A sputtered Ti/TiN liner and blanket CVD tungsten deposition processes are used to fill the vias (Figure 1d). A second CMP process then removes the tungsten and liner material from the surface, leaving it in the vias (Figure 1e).

| Metal Level | Thickness<br>(μm) | Wired Pitch<br>(µm) |

|-------------|-------------------|---------------------|

| M1          | 0.85              | 2.0                 |

| M2          | 1.05              | 2.4                 |

| M3          | 1.05              | 2.4                 |

| M4          | 2.0               | 4.8                 |

DOCKE

Table 1.Interconnect thickness andwiring pitch.

M1 a) Metal deposition, patterning and RIE. **PECVD** Oxide M1 b) Dep-etch-dep oxide deposition. PECVD Oxide M1 c) Oxide chem-mech polish, via patterning and RIE. Tungsten **PECVD** Oxide M1 d) Sputtered liner and CVD tungsten deposition. **PECVD** Oxide e) Tungsten chem-mech polish removal.

Figure 1. Process flow for metal, insulator and stud formation.

Find authenticated court documents without watermarks at docketalarm.com.

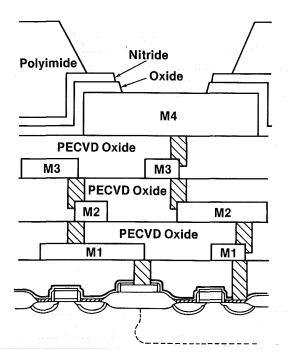

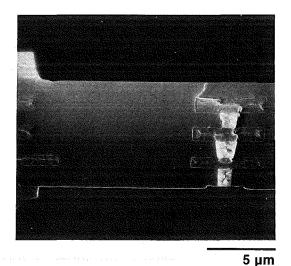

A cross section of the final integrated four-level-metal logic interconnect process is illustrated in Figure 2. As indicated, the tungsten studs are allowed to extend partially down the side of the metal wiring levels. This is a consequence of allowing designs without metal-bordering of vias. The final passivation is a layered structure of oxide, nitride and polyimide. An SEM cross section of a four-level-metal test structure fabricated with the processes described above is shown in Figure 3.

The use of a similar process sequence under the first level of metal, as shown in Figure 2, avoids reliance on reflow of highly doped BPSG glass layers for pre-M1 planarization. The result is a process that yields superior planarity, when compared to reflow, and avoids the degradation of device properties and sheet resistance of salicided materials that accompany high-temperature processes.

Figure 2. Cross section of four-levelmetal structure.

The use of redundant word and bit lines to repair defects in DRAMS and SRAMs is well known. Typically, the address of the redundant feature is incorporated into the operation of the chip by selectively blowing a series of fusible links. Fuses are integrated into this interconnect technology as part of the next to last level of metal as depicted in Figure 4. Any given fuse can be blown by focusing sufficient laser energy onto the appropriate metal line. As shown in the SEM cross section in Figure 5, a portion of the metal line and overlying insulator is removed during this operation. Unblown fuses remain passivated with oxide. This technique has been demonstrated by successfully fixing partially good 256K SRAM chips. In addition, blown metal fuses have been subjected to

Find authenticated court documents without watermarks at docketalarm.com.

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.