PTO/SB/05 (07-07)

Approved for use through 06/30/2010. OMB 0651-0032

U.S. Patent and Trademark Office. U.S. DEPARTMENT OF COMMERCE

Under the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it displays a valid OMB control number.

|                                                                                 | UTILITY                                                                                               |                                         | Attorney Docket No.                                                                                         | CI             | ROSS1120-33                                                           |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------|

| PA <sup>-</sup>                                                                 | PATENT APPLICATION                                                                                    |                                         | First Inventor                                                                                              | G              | eoffrey B. Hoese                                                      |

|                                                                                 | TRANSMITTAL                                                                                           |                                         | Title                                                                                                       | St             | torage Router and Method for                                          |

| (Only for new r                                                                 | nonprovisional applications under 37                                                                  | CFR 1.53(b))                            | Express Mail Label No.                                                                                      | N/             | /A                                                                    |

|                                                                                 | PPLICATION ELEMENTS er 600 concerning utility patent applic                                           |                                         | ADDRESS TO:                                                                                                 | Р              | Commissioner for Patents<br>P.O. Box 1450<br>Alexandria VA 22313-1450 |

|                                                                                 | mittal Form (e.g., PTO/SB/17)                                                                         |                                         | ACCOMPAN                                                                                                    | IYI            | NG APPLICATION PARTS                                                  |

|                                                                                 | original and a duplicate for fee proces<br>claims small entity status.<br>D 1 27                      | ssing)                                  | 9. Assignment F                                                                                             | Pape           | ers (cover sheet & document(s))                                       |

| 3. ✓ Specificati                                                                |                                                                                                       | 25 ]                                    | Name of Ass                                                                                                 | •              | ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` `                               |

| (For information                                                                | on on the preferred arrangement, see MPEI ) (35 U.S.C. 113) [Total Sheets                             | P 608.01(a))                            |                                                                                                             |                |                                                                       |

| 5. Oath or Declara                                                              | ation [Total Shee                                                                                     | ets <u>4</u> ]                          | 10. 37 CFR 3.73(k                                                                                           |                |                                                                       |

| b. ✓ A copy                                                                     | executed (original or copy)<br>from a prior application (37 CFR<br>tinuation/divisional with Box 18 o |                                         | (when there                                                                                                 |                | •                                                                     |

| i. DEL                                                                          | LETION OF INVENTOR(S)  ed statement attached deleting invent                                          | , , , , , , , , , , , , , , , , , , , , | <u> </u>                                                                                                    |                | on Document (if applicable)                                           |

| name                                                                            | e in the prior application, see 37 CFR (d)(2) and 1.33(b).                                            |                                         | 12. Information D                                                                                           | s of           | losure Statement (PTO/SB/08 or PTO-1449)<br>citations attached        |

| 6. Applicatio                                                                   | n Data Sheet. See 37 CFR 1.76                                                                         | 3                                       | 13. Preliminary Amendment                                                                                   |                |                                                                       |

|                                                                                 | or CD-R in duplicate, large table                                                                     | ог                                      | 14. Return Receipt Postcard (MPEP 503)                                                                      |                |                                                                       |

|                                                                                 | Program (Appendix) scape Table on CD                                                                  |                                         | (Should be specifically itemized)                                                                           |                |                                                                       |

|                                                                                 | d/or Amino Acid Sequence Sul<br>ems a. – c. are required)                                             | bmission                                | 15. Certified Copy of Priority Document(s) (if foreign priority is claimed)                                 |                |                                                                       |

| a. Com                                                                          | puter Readable Form (CRF) cification Sequence Listing on:                                             |                                         | 16. Nonpublication Request under 35 U.S.C. 122(b)(2)(B)(i).                                                 |                |                                                                       |

| i. 🔲                                                                            | CD-ROM or CD-R (2 copies); of                                                                         | or                                      | Applicant must attach form PTO/SB/35 or equivalent.  17. Other: Cert. of Transmission and Identification of |                |                                                                       |

| ii. []                                                                          | Paper                                                                                                 |                                         |                                                                                                             |                | •                                                                     |

|                                                                                 | ements verifying identity of abov                                                                     |                                         | Change in Power of Attorney  uply the requisite information below and in the first sentence of the          |                |                                                                       |

|                                                                                 | ng APPLICATION, check appro<br>ing the title, or in an Application I                                  |                                         |                                                                                                             | on pe          | elow and in the first sentence of the                                 |

| ✓ Continuation                                                                  | on Divisional                                                                                         | Continua                                | ntion-in-part (CIP) of p                                                                                    | rior a         | application No.:12/552,885                                            |

| Prior application inform                                                        | nation: Examiner U                                                                                    | nknown                                  | Art U                                                                                                       | Init: <u>1</u> | 2181                                                                  |

|                                                                                 | 1:                                                                                                    | 9. CORRESPON                            | DENCE ADDRESS                                                                                               |                |                                                                       |

| The address associated with Customer Number:  44654  OR  Correspondence address |                                                                                                       |                                         | Correspondence address below                                                                                |                |                                                                       |

| Name                                                                            |                                                                                                       |                                         |                                                                                                             |                |                                                                       |

| Address                                                                         |                                                                                                       |                                         |                                                                                                             |                |                                                                       |

| City                                                                            |                                                                                                       | State                                   |                                                                                                             |                | Zip Code                                                              |

| Country                                                                         |                                                                                                       | Telephone                               |                                                                                                             |                | Email                                                                 |

| Signature                                                                       | 1/1/                                                                                                  |                                         | Da                                                                                                          | ate            | January 20, 2010                                                      |

| Name                                                                            | John L. Adair                                                                                         |                                         |                                                                                                             |                | Registration No. 48 828                                               |

This collection of information is required by 37 CFR 1.53(b). The information is required to obtain or retain a benefit by the public which is to file (and by the USPTO to process) an application. Confidentiality is governed by 35 U.S.C. 122 and 37 CFR 1.11 and 1.14. This collection is estimated to take 12 minutes to complete, including gathering, preparing, and submitting the completed application form to the USPTO. Time will vary depending upon the individual case. Any comments on the amount of time you require to complete this form and/or suggestions for reducing this burden, should be sent to the Chief Information Officer, U.S. Patent and Trademark Office, U.S. Department of Commerce, P.O. Box 1450, Alexandria, VA 22313-1450. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. SEND TO: Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450.

If you need assistance in completing the form, call 1-800-PTO-9199 and select option 2.

(Print/Type)

(Attorney/Agent)

48,828

### STORAGE ROUTER AND METHOD FOR PROVIDING VIRTUAL LOCAL STORAGE

#### TECHNICAL FIELD OF THE INVENTION

[0001]

This application is a continuation of, and claims a benefit of priority under 35 U.S.C. 120 of the filing date of U.S. Patent Application Serial No. 12/552,885 entitled "Storage Router and Method for Providing Virtual Local Storage" filed 09/02/2009, which is a continuation of and claims the benefit of priority of U.S. Application Serial No. 11/851,724 entitled "Storage Router and Method for Providing Virtual Local Storage" filed 09/07/2007, which is a continuation of and claims the benefit of priority of U.S. Patent Application Serial No. 11/442,878 entitled "Storage Router and Method for Providing Virtual Local Storage" filed 09/07/2007, which is a continuation of and claims the benefit of priority of U.S. Patent Application Serial No. 11/353,826 entitled "Storage Router and Method for Providing Virtual Local Storage" filed on 02/14/2006, now U.S. Patent No. 7,340,549 issued 03/04/2008, which is a continuation of and claims the benefit of priority of U.S. Patent Application Serial No. 10/658,163 entitled "Storage Router and Method for Providing Virtual Local Storage" filed on 09/09/2003 now U.S. Patent No. 7,051,147 issued 05/23/2006, which is a continuation of and claims the benefit of benefit of priority of U.S. Patent Application Serial No. 10/081,110 by inventors Geoffrey B. Hoese and Jeffery T. Russell, entitled "Storage Router and Method for Providing Virtual Local Storage" filed on 02/22/2002, now U.S. Patent No. 6,789,152 issued on 09/07/2004, which in turn is a continuation of and claims benefit of priority of U.S. Application No. 09/354,682 by inventors Geoffrey B. Hoese and Jeffrey T. Russell, entitled "Storage Router and Method for Providing Virtual Local Storage" filed on 07/15/1999, now U.S. Patent No. 6,421,753 issued on 07/16/2002, which in turn is a continuation of and claims benefit of priority of U.S. Patent Application Serial No. 09/001,799, filed on 12/31/1997, now U.S. Patent No. 5,941,972 issued on 08/24/1999, and hereby incorporates these applications and patents by reference in their entireties as if they had been fully set forth herein.

[0002]

This invention relates in general to network storage devices, and more particularly to a storage router and method for providing virtual local storage on remote SCSI storage devices to Fibre Channel devices.

#### BACKGROUND OF THE INVENTION

[0003]

Typical storage transport mediums provide for a relatively small number of devices to be attached over relatively short distances. One such transport medium is a Small Computer System Interface (SCSI) protocol, the structure and operation of which is generally well known as is described, for example, in the SCSI-1, SCSI-2 and SCSI-3 specifications. High speed serial interconnects provide enhanced capability to attach a large number of high speed devices to a common storage transport medium over large distances. One such. serial interconnect is Fibre Channel, the structure and operation of which is described, for example, in Fibre Channel Physical and Signaling Interface (FC-PH), ANSI X3.230 Fibre Channel Arbitrated Loop (FC-AL), and ANSI X3.272 Fibre Channel Private Loop Direct Attach (FC-PLDA).

[0004]

Conventional computing devices, such as computer workstations, generally access storage locally or through network interconnects. Local storage typically consists of a disk drive, tape drive, CD-ROM drive or other storage device contained within, or locally connected to the workstation. The workstation provides a file system structure that includes security controls, with access to the local storage device through native low level block protocols. These protocols map directly to the mechanisms used by the storage device and consist of data requests without security controls. Network interconnects typically provide access for a large number of computing devices to data storage on a remote network server. The remote network server provides file system structure, access control, and other miscellaneous capabilities that include the network interface. Access to data through the network server is through network protocols that the server must translate into low level requests to the storage device. A workstation with access to the server storage must translate its file system protocols into network protocols that are used to communicate with the server. Consequently,

from the perspective of a workstation, or other computing device, seeking to access such server data, the access is much slower than access to data on a local storage device.

#### SUMMARY OF THE INVENTION

[0005]

In accordance with the present invention, a storage router and method for providing virtual local storage on remote SCSI storage devices to Fibre Channel devices are disclosed that provide advantages over conventional network storage devices and methods.

[0006]

According to one aspect of the present invention, a storage router and storage network provide virtual local storage on remote SCSI storage devices to Fibre Channel devices. A plurality of Fibre Channel devices, such as workstations, are connected to a Fibre Channel transport medium, and a plurality of SCSI storage devices are connected to a SCSI bus transport medium. The storage router interfaces between the Fibre Channel transport medium and the SCSI bus transport medium. The storage router maps between the workstations and the SCSI storage devices and implements access controls for storage space on the SCSI storage devices. The storage router then allows access from the workstations to the SCSI storage devices using native low level, block protocol in accordance with the mapping and the access controls.

[0007]

According to another aspect of the present invention, virtual local storage on remote SCSI storage devices is provided to Fibre Channel devices. A Fibre Channel transport medium and a SCSI bus transport medium are interfaced with. A configuration is maintained for SCSI storage devices connected to the SCSI bus transport medium. The configuration maps between Fibre Channel devices and the SCSI storage devices and implements access controls for storage space on the SCSI storage devices. Access is then allowed from Fibre Channel initiator devices to SCSI storage devices using native low level, block protocol in accordance with the configuration.

- [0008] A technical advantage of the present invention is the ability to centralize local storage for networked workstations without any cost of speed or overhead. Each workstation accesses its virtual local storage as if it were locally connected. Further, the centralized storage devices can be located in a significantly remote position even in excess of ten kilometers as defined by Fibre Channel standards.

- [0009] Another technical advantage of the present invention is the ability to centrally control and administer storage space for connected users without limiting the speed with which the users can access local data. In addition, global access to data, backups, virus scanning and redundancy can be more easily accomplished by centrally located storage devices.

- [0010] A further technical advantage of the present invention is providing support for SCSI storage devices as local storage for Fibre Channel hosts. In addition, the present invention helps to provide extended capabilities for Fibre Channel and for management of storage subsystems.

#### BRIEF DESCRIPTION OF THE DRAWINGS

router of FIGURE 4.

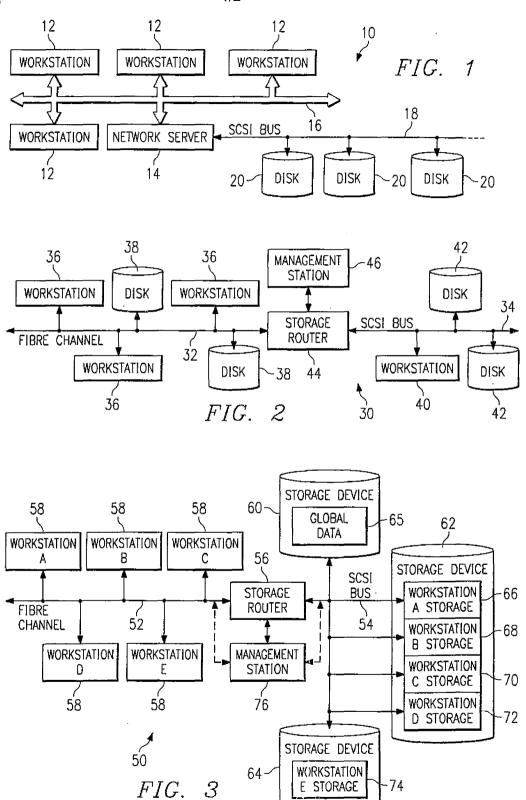

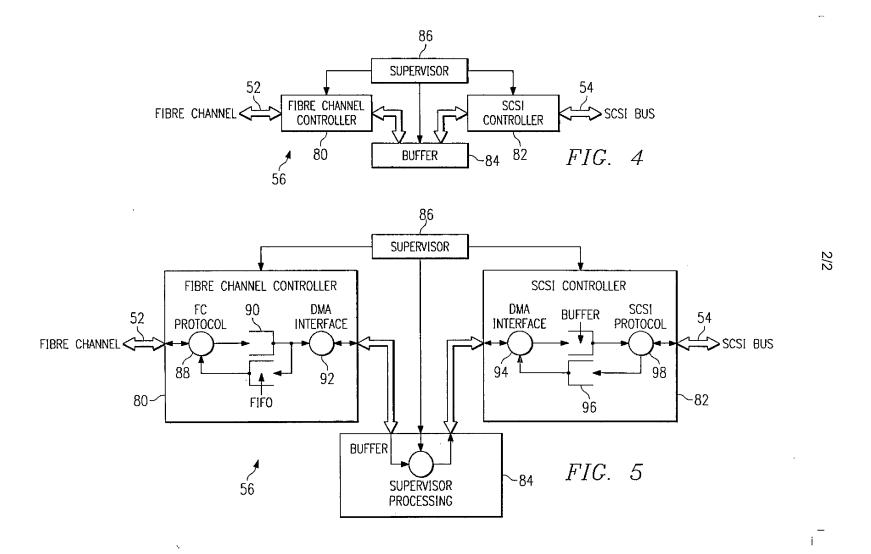

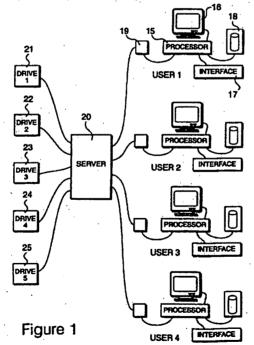

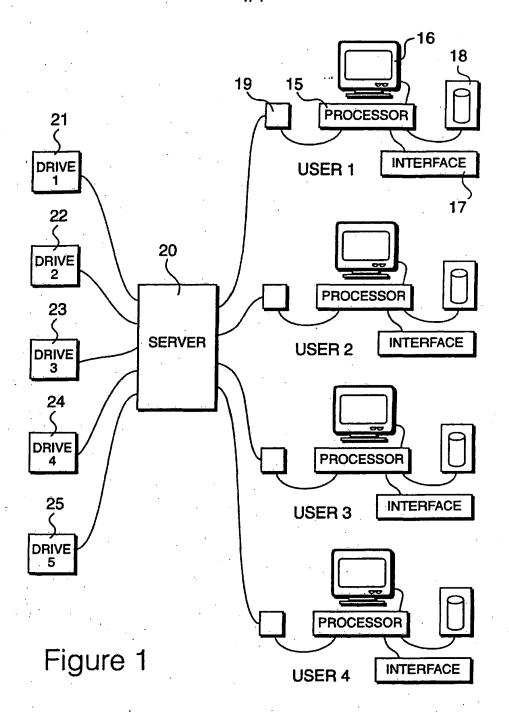

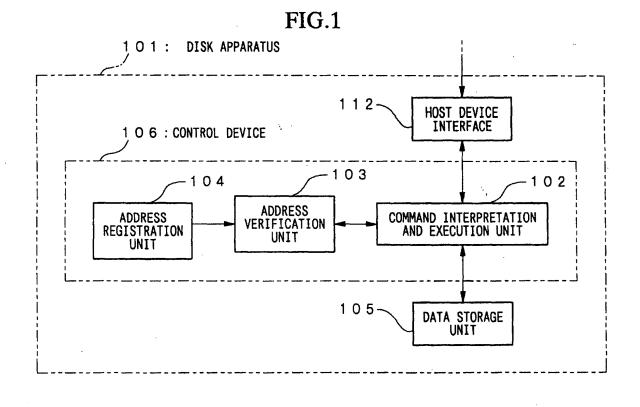

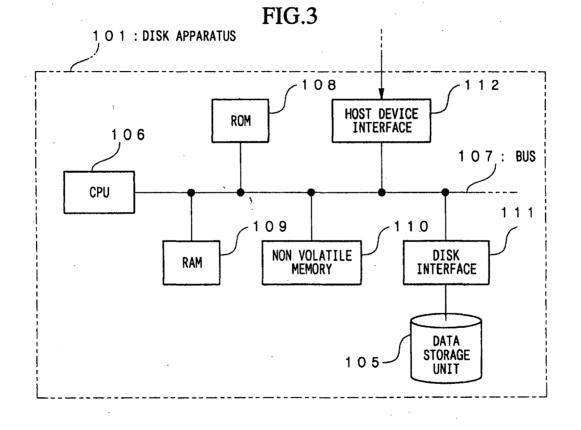

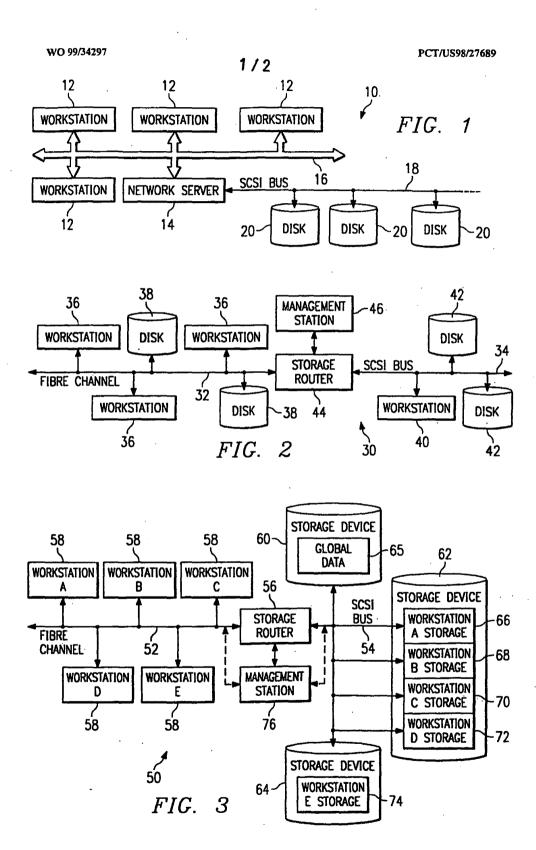

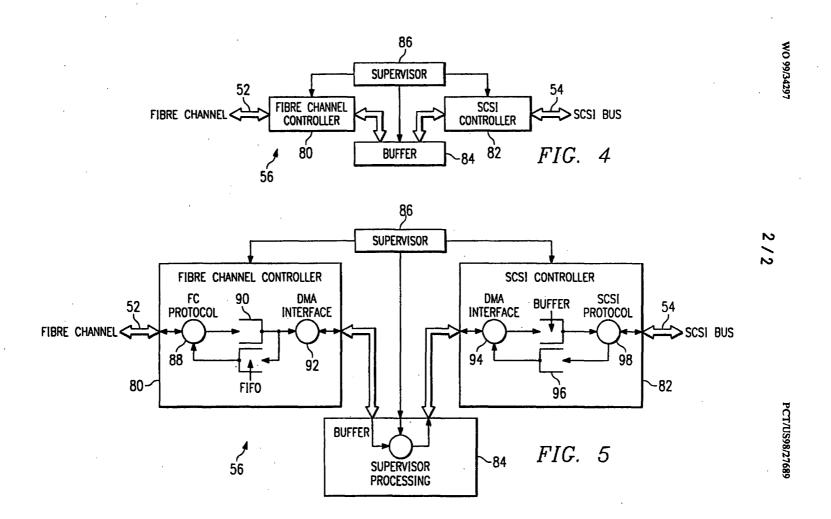

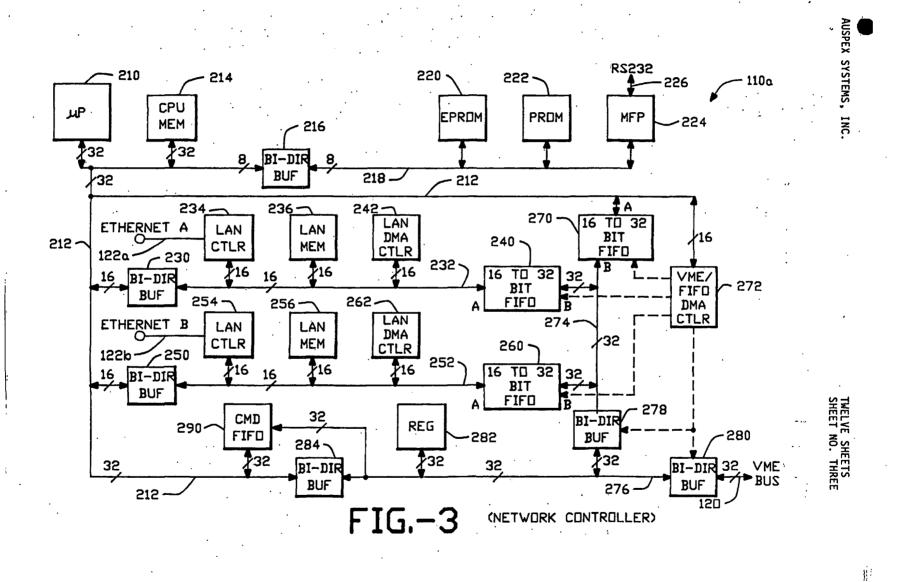

[0011] A more complete understanding of the present invention and the advantages thereof may be acquired by referring to the following description taken in conjunction with the accompanying drawings, in which like reference numbers indicate like features, and wherein: [0012] FIGURE 1 is a block diagram of a conventional network that provides storage through a network server; [0013] FIGURE 2 is a block diagram of one embodiment of a storage network with a storage router that provides global access and routing; [0014] FIGURE 3 is a block diagram of one embodiment of a storage network with a storage router that provides virtual local storage; [0015] FIGURE 4 is a block diagram of one embodiment of the storage router of FIGURE 3; and [0016] FIGURE 5 is a block diagram of one embodiment of data flow within the storage

#### DETAILED DESCRIPTION OF THE INVENTION

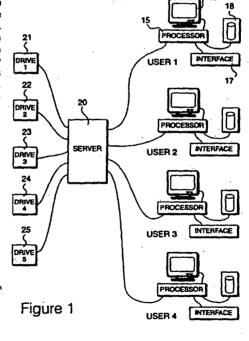

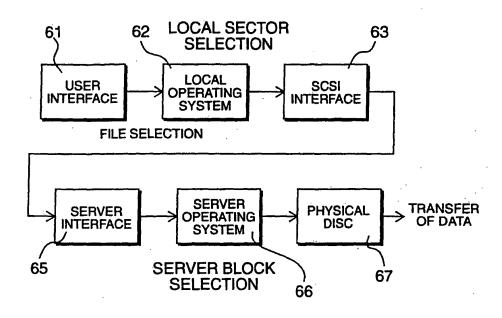

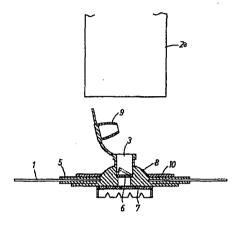

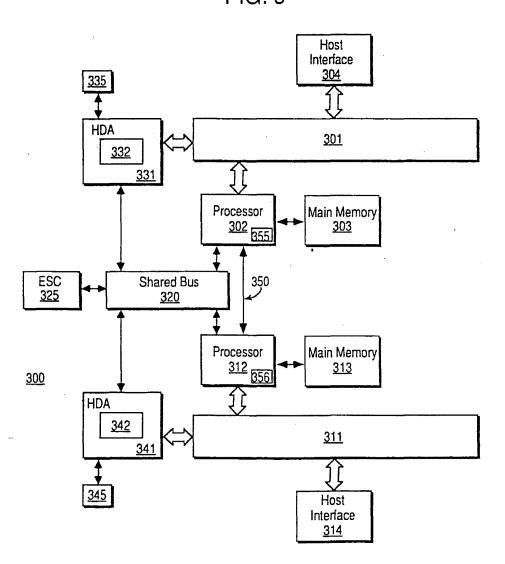

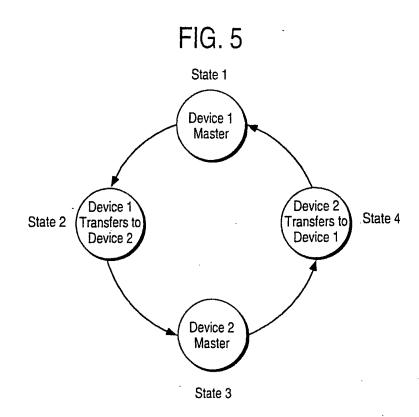

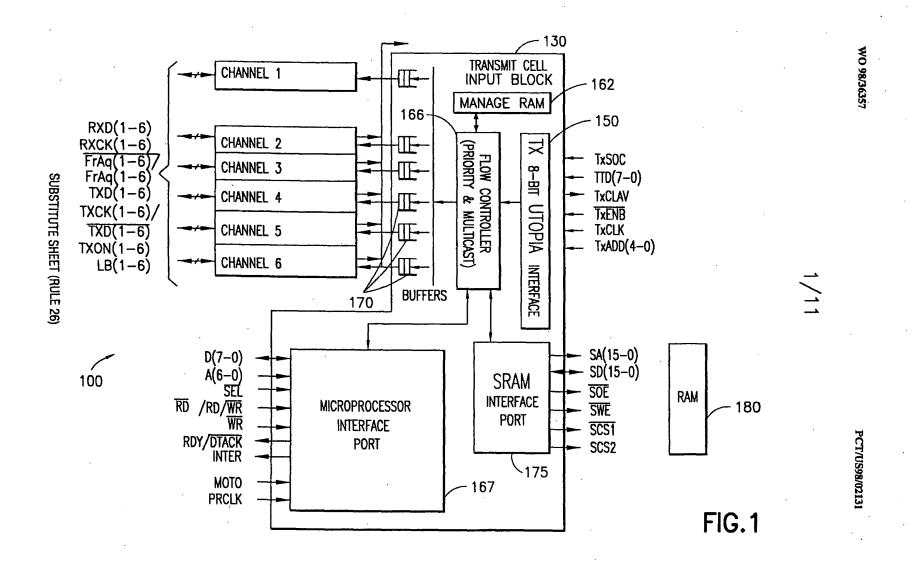

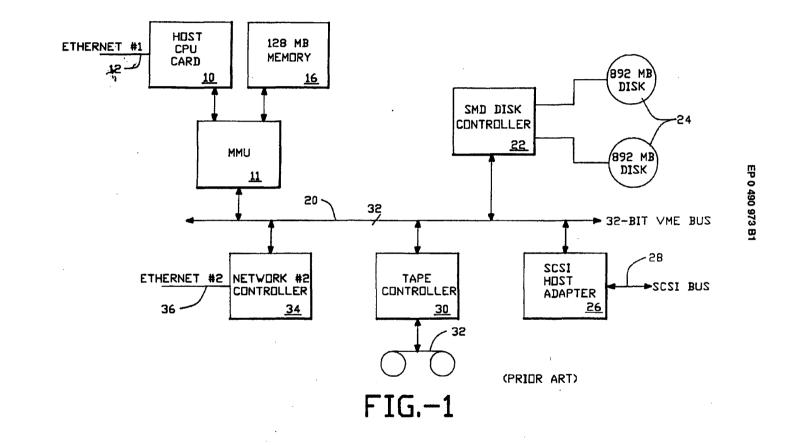

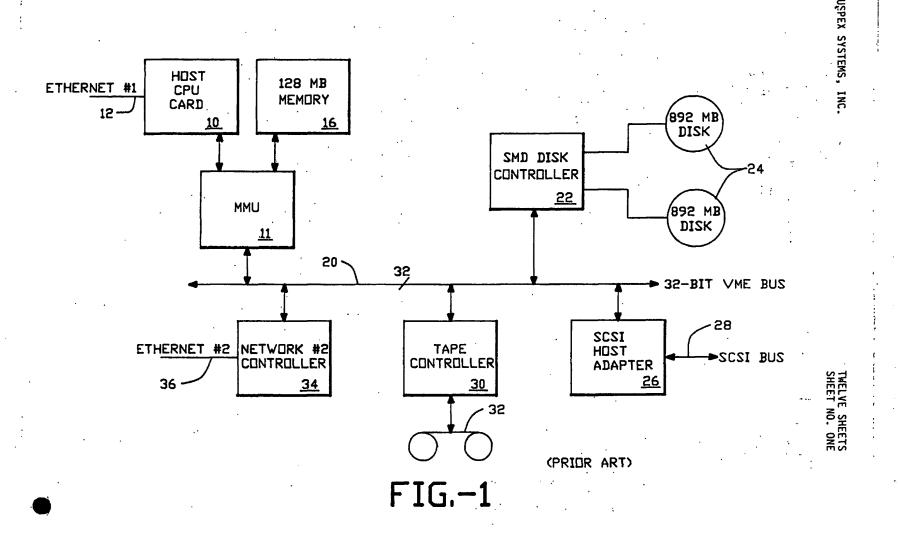

FIGURE 1 is a block diagram of a conventional network, indicated generally at 10, that provides access to storage through a network server. As shown, network 10 includes a plurality of workstations 12 interconnected with a network server 14 via a network transport medium 16. Each workstation 12 can generally comprise a processor, memory, input/output devices, storage devices and a network adapter as well as other common computer components. Network server 14 uses a SCSI bus 18 as a storage transport medium to interconnect with a plurality of storage devices 20 (tape drives, disk drives, etc.). In the embodiment of FIGURE 1, network transport medium 16 is a network connection and storage devices 20 comprise hard disk drives, although there are numerous alternate transport mediums and storage devices.

In network 10, each workstation 12 has access to its local storage device as well as network access to data on storage devices 20. The access to a local storage device is typically through native low level, block protocols. On the other hand, access by a workstation 12 to storage devices 20 requires the participation of network server 14 which implements a file system and transfers data to workstations 12 only through high level file system protocols. Only network server 14 communicates with storage devices 20 via native low level, block protocols. Consequently, the network access by workstations 12 through network server 14 is slow with respect to their access to local storage. In network 10, it can also be a logistical problem to centrally manage and administer local data distributed across an organization, including accomplishing tasks such as backups, virus scanning and redundancy.

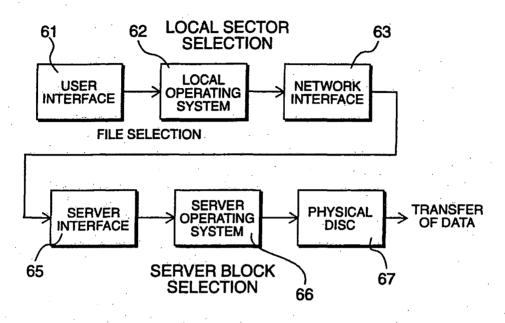

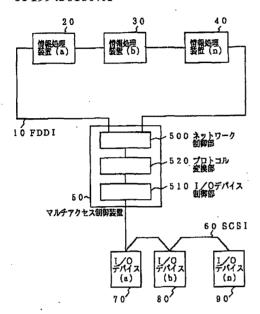

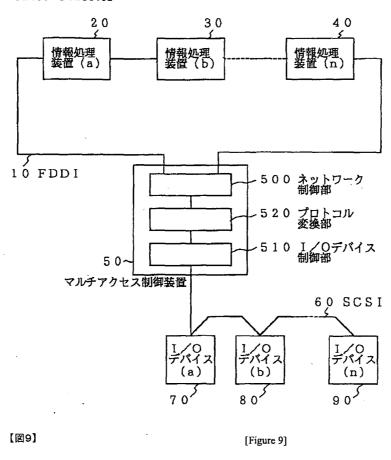

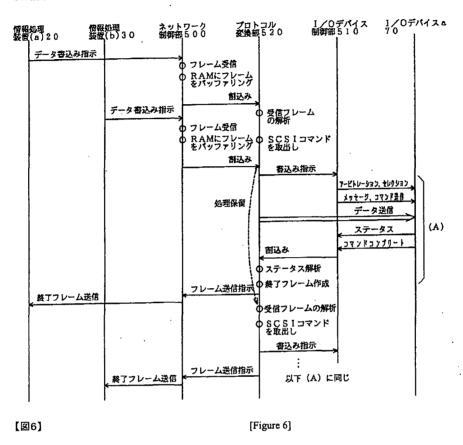

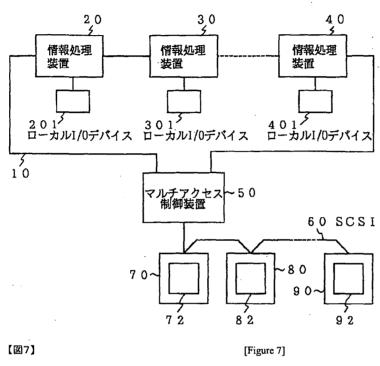

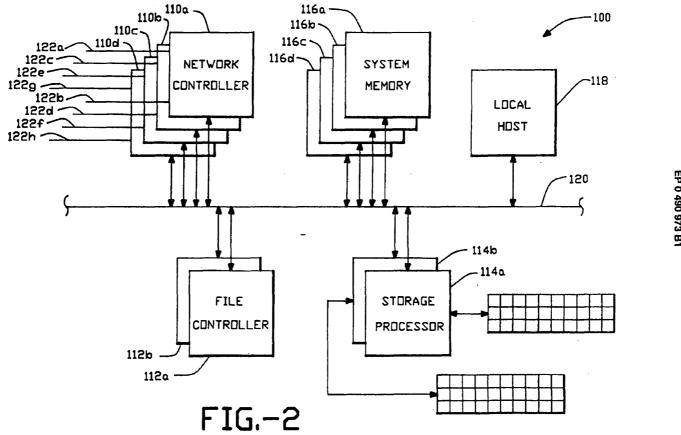

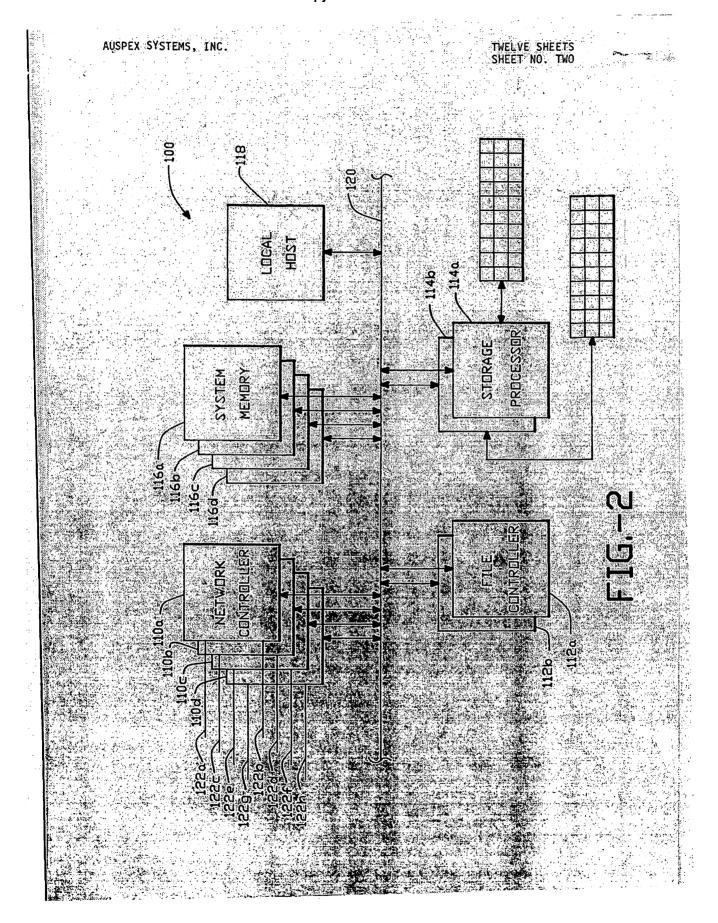

[0019] FIGURE 2 is a block diagram of one embodiment of a storage network, indicated generally at 30, with a storage router that provides global access and routing. This environment is significantly different from that of FIGURE 1 in that there is no network server involved. In FIGURE 2, a Fibre Channel high speed serial transport 32 interconnects a plurality of workstations 36 and storage devices 38. A SCSI bus storage transport medium interconnects workstations 40 and storage

devices 42. A storage router 44 then serves to interconnect these mediums and provide devices on either medium global, transparent access to devices on the other medium. Storage router 44 routes requests from initiator devices on one medium to target devices on the other medium and routes data between the target and the initiator. Storage router 44 can allow initiators and targets to be on either side. In this manner, storage router 44 enhances the functionality of Fibre Channel 32, by providing access, for example, to legacy SCSI storage devices on SCSI bus 34. In the embodiment of FIGURE 2, the operation of storage router 44 can be managed by a management station 46 connected to the storage router via a direct serial connection.

- In storage network 30, any workstation 36 or workstation 40 can access any storage device 38 or storage device 42 through native low level, block protocols, and vice versa. This functionality is enabled by storage router 44 which routes requests and data as a generic transport between Fibre Channel 32 and SCSI bus 34. Storage router 44 uses tables to map devices from one medium to the other and distributes requests and data across Fibre Channel 32 and SCSI bus 34 without any security access controls. Although this extension of the high speed serial interconnect provided by Fibre Channel is beneficial, it is desirable to provide security controls in addition to extended access to storage devices through a native low level, block protocol.

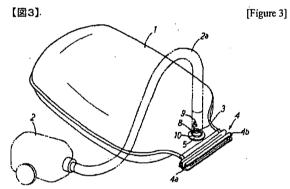

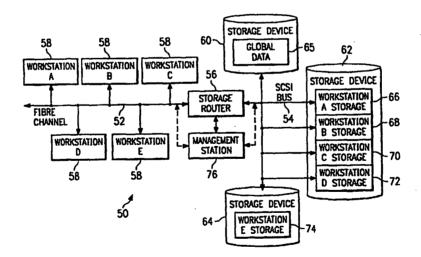

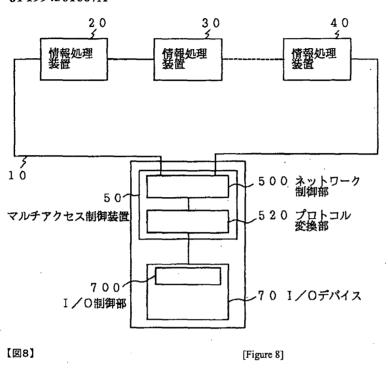

- [0021] FIGURE 3 is a block diagram of one embodiment of a storage network, indicated generally at 50, with a storage router that provides virtual local storage. Similar to that of FIGURE 2, storage network 50 includes a Fibre Channel high speed serial interconnect 52 and a SCSI bus 54 bridged by a storage router 56. Storage router 56 of FIGURE 3 provides for a large number of workstations 58 to be interconnected on a common storage transport and to access common storage devices 60, 62 and 64 through native low level, block protocols.

- [0022] According to the present invention, storage router 56 has enhanced functionality to implement security controls and routing such that each workstation 58 can

have access to a specific subset of the overall data stored in storage devices 60, 62 and 64. This specific subset of data has the appearance and characteristics of local storage and is referred to herein as virtual local storage. Storage router 56 allows the configuration and modification of the storage allocated to each attached workstation 58 through the use of mapping tables or other mapping techniques.

- [0023] As shown in FIGURE 3, for example, storage device 60 can be configured to provide global data 65 which can be accessed by all workstations 58. Storage device 62 can be configured to provide partitioned subsets 66, 68, 70 and 72, where each partition is allocated to one of the workstations 58 (workstations A, B, C and D). These subsets 66, 68, 70 and 72 can only be accessed by the associated workstation 58 and appear to the associated workstation 58 as local storage accessed using native low level, block protocols. Similarly, storage device 64 can be allocated as storage for the remaining workstation 58 (workstation E).

- [0024] Storage router 56 combines access control with routing such that each workstation 58 has controlled access to only the specified partition of storage device 62 which forms virtual local storage for the workstation 58. This access control allows security control for the specified data partitions. Storage router 56 allows this allocation of storage devices 60, 62 and 64 to be managed by a management station 76. Management station 76 can connect directly to storage router 56 via a direct connection or, alternately, can interface with storage router 56 through either Fibre Channel 52 or SCSI bus 54. In the latter case, management station 76 can be a workstation or other computing device with special rights such that storage router 56 allows access to mapping tables and shows storage devices 60, 62 and 64 as they exist physically rather than as they have been allocated.

- [0025] The environment of FIGURE 3 extends the concept of single workstation having locally connected storage devices to a storage network 50 in which workstations

58 are provided virtual local storage in a manner transparent to workstations 58. Storage router 56 provides centralized control of what each workstation 58 sees as its local drive, as well as what data it sees as global data accessible by other workstations 58. Consequently, the storage space considered by the workstation 58 to be its local storage is actually a partition (i.e., logical storage definition) of a physically remote storage device 60, 62 or 64 connected through storage router 56. This means that similar requests from workstations 58 for access to their local storage devices produce different accesses to the storage space on storage devices 60, 62 and 64. Further, no access from a workstation 58 is allowed to the virtual local storage of another workstation 58.

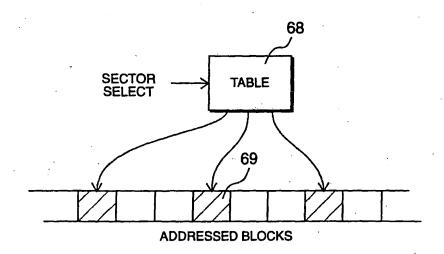

[0026] The collective storage provided by storage devices 60, 62 and 64 can have blocks allocated by programming means within storage router 56. To accomplish this function, storage router 56 can include routing tables and security controls that define storage allocation for each workstation 58. The advantages provided by implementing virtual local storage in centralized storage devices include the ability to do collective backups and other collective administrative functions more easily. This is accomplished without limiting the performance of workstations 58 because storage access involves native low level, block protocols and does not involve the overhead of high level protocols and file systems required by network servers.

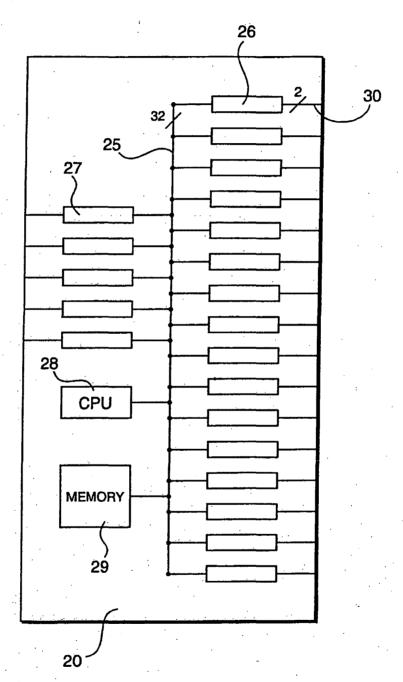

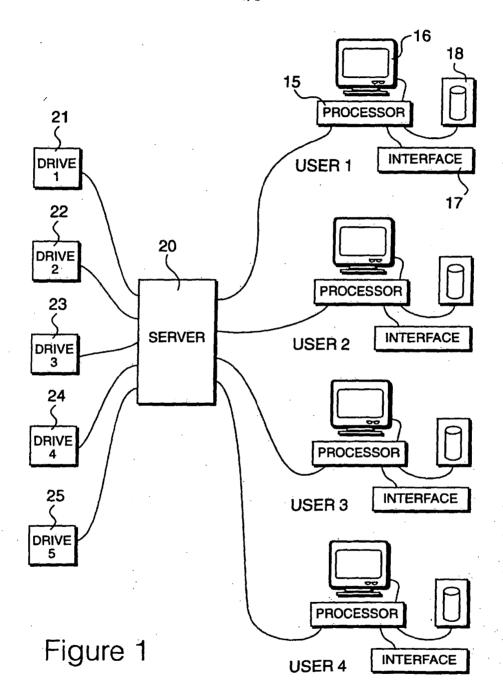

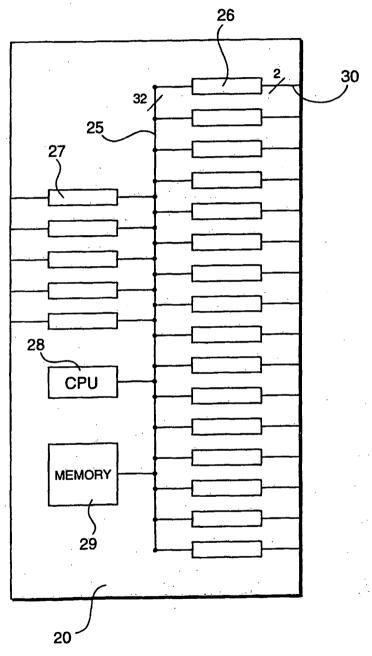

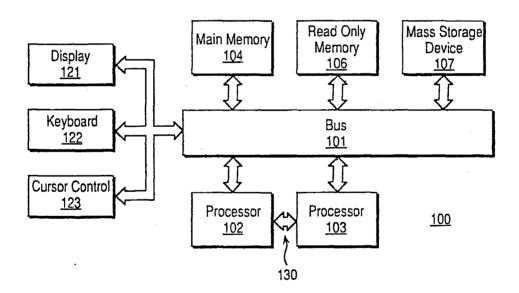

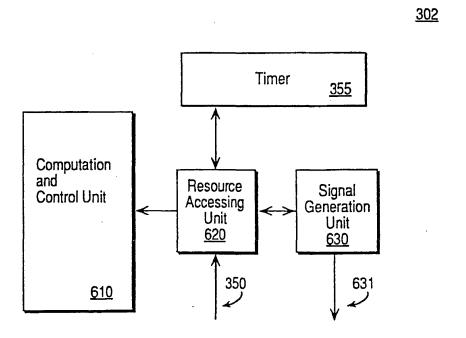

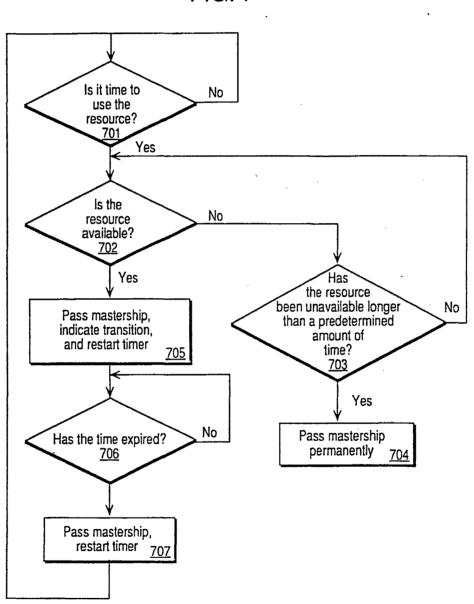

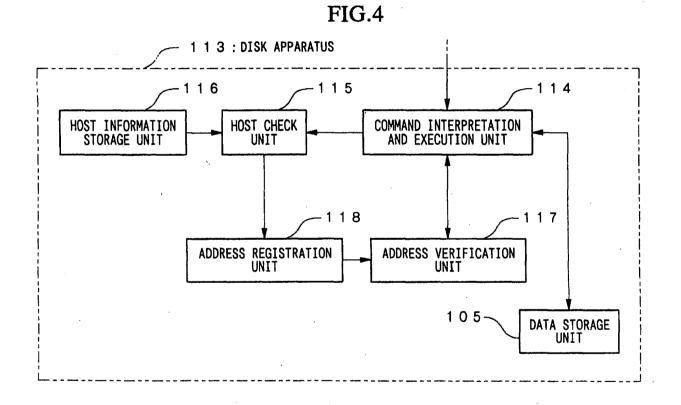

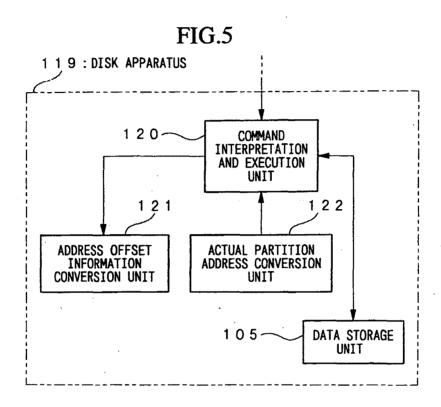

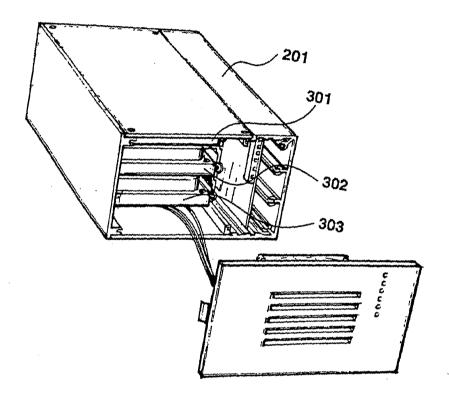

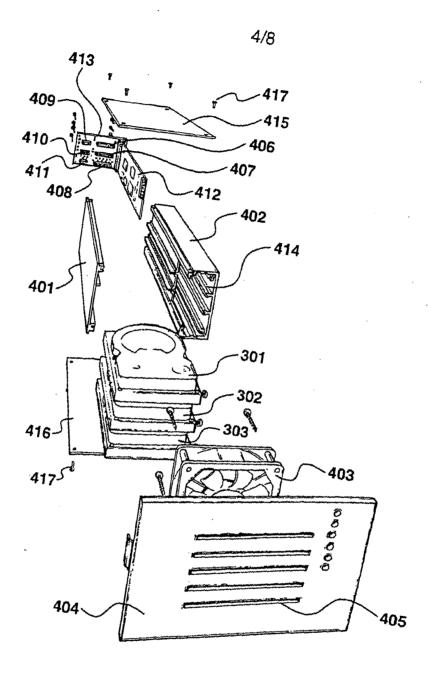

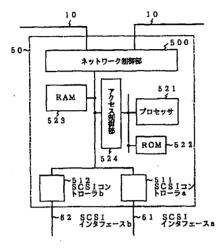

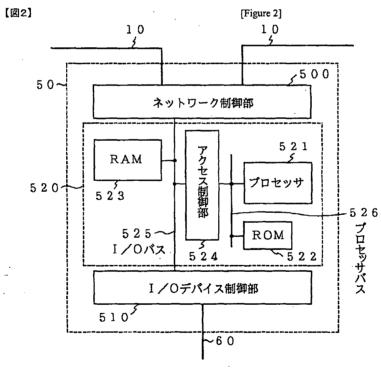

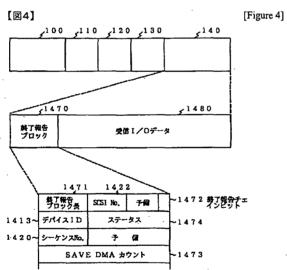

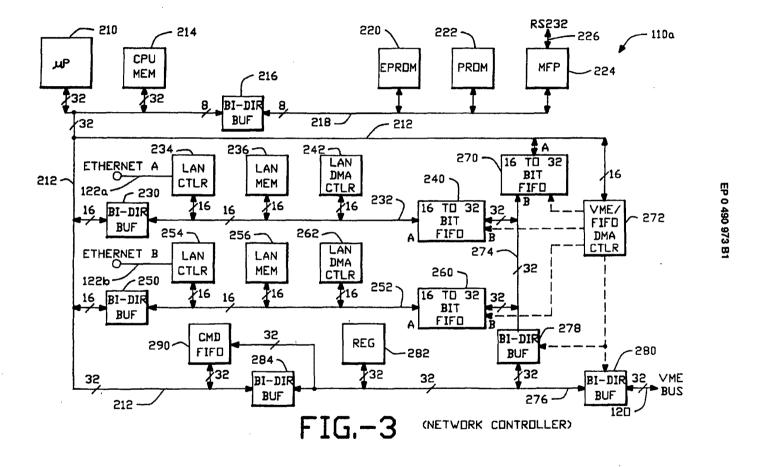

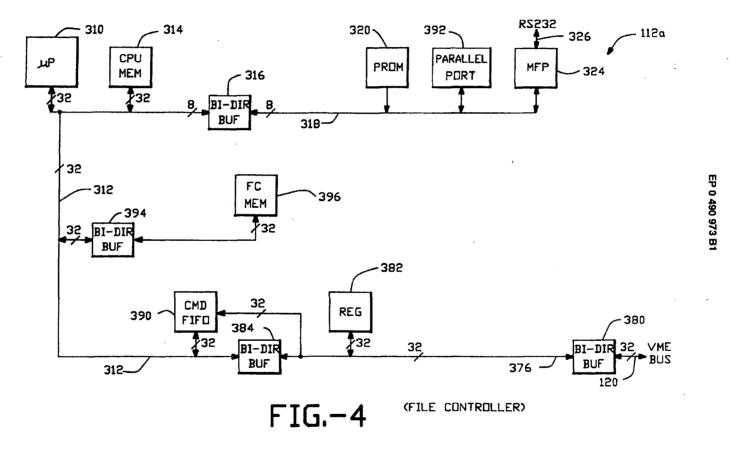

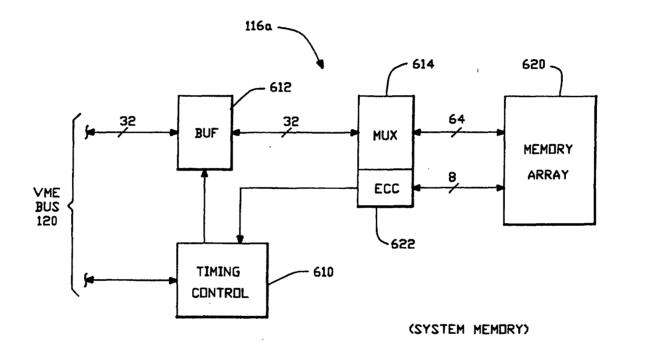

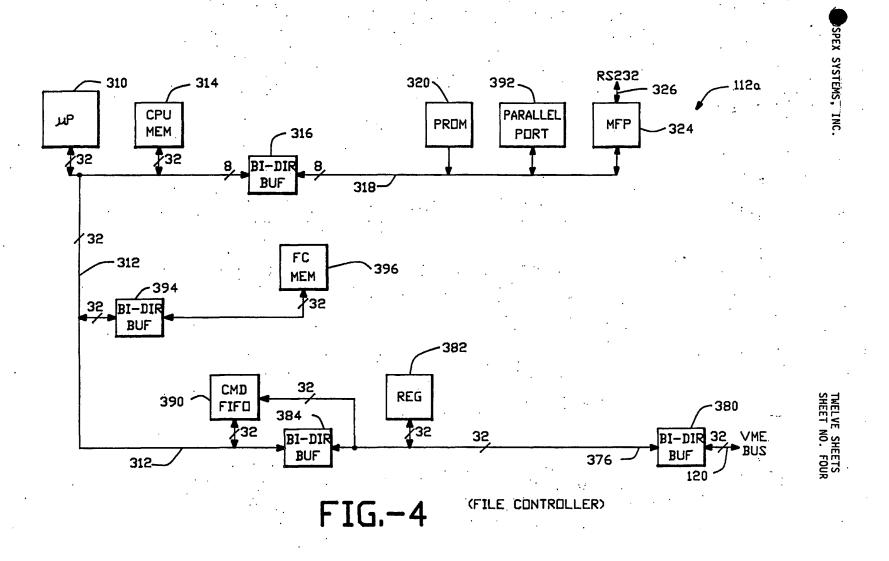

[0027] FIGURE 4 is a block diagram of one embodiment of storage router 56 of FIGURE 3. Storage router 56 can comprise a Fibre Channel controller 80 that interfaces with Fibre Channel 52 and a SCSI controller 82 that interfaces with SCSI bus 54. A buffer 84 provides memory work space and is connected to both Fibre Channel controller 80 and to SCSI controller 82. A supervisor unit 86 is connected to Fibre Channel controller 80, SCSI controller 82 and buffer 84. Supervisor unit 86 comprises a microprocessor for controlling operation of storage router 56 and to handle mapping and-security access for requests between Fibre Channel 52 and SCSI bus 54.

[0028]

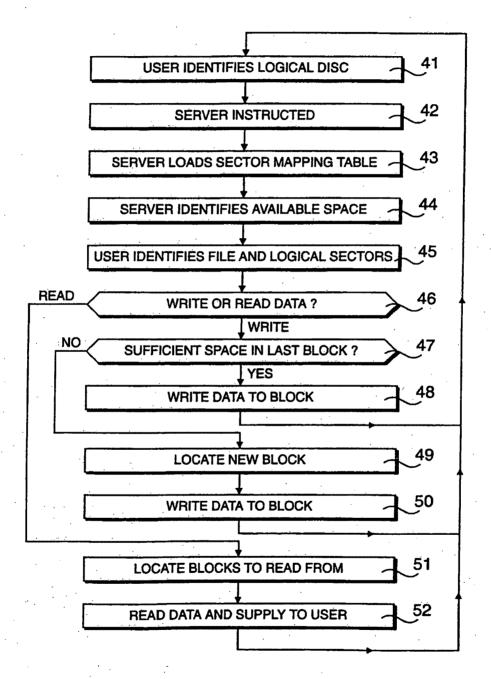

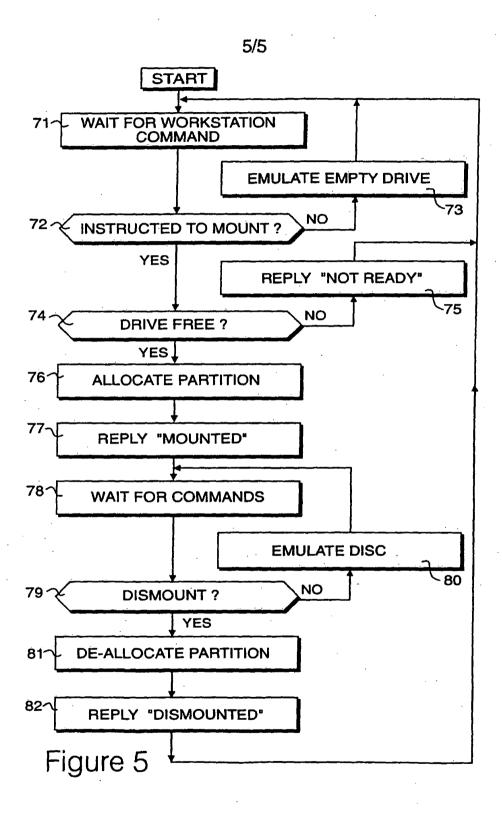

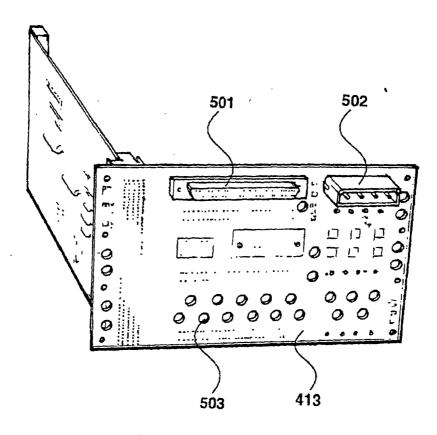

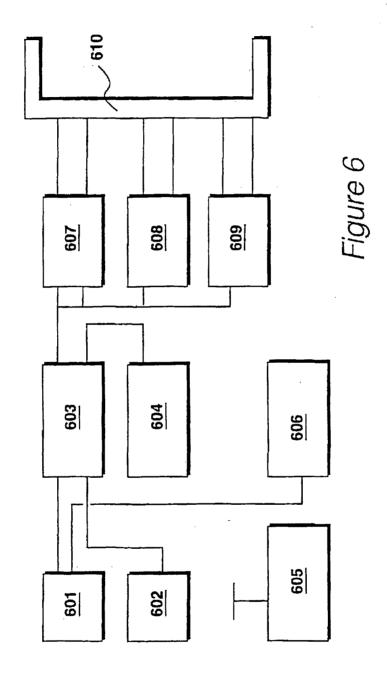

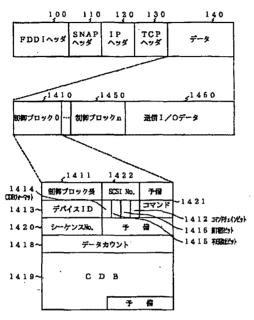

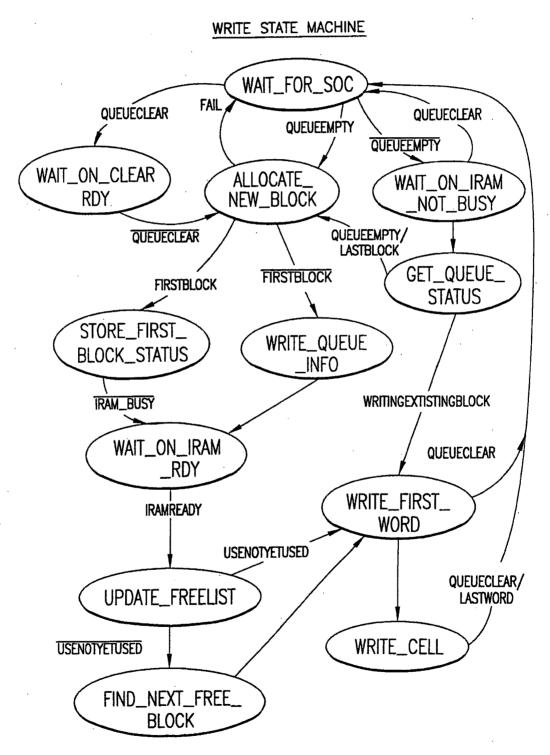

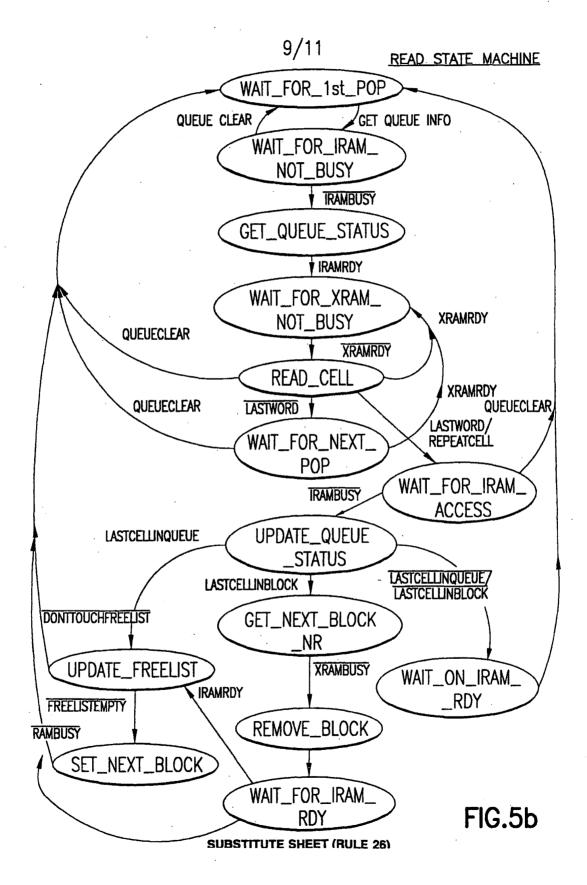

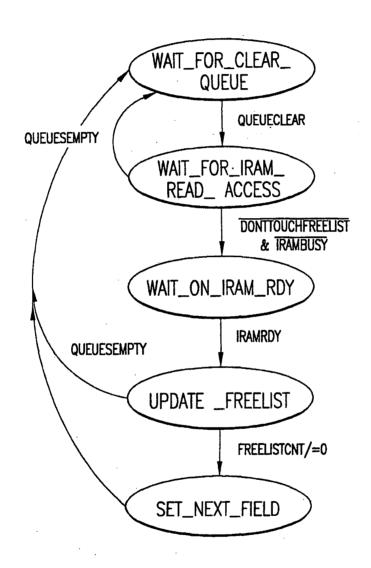

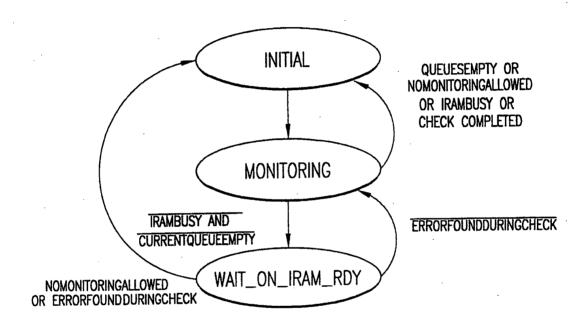

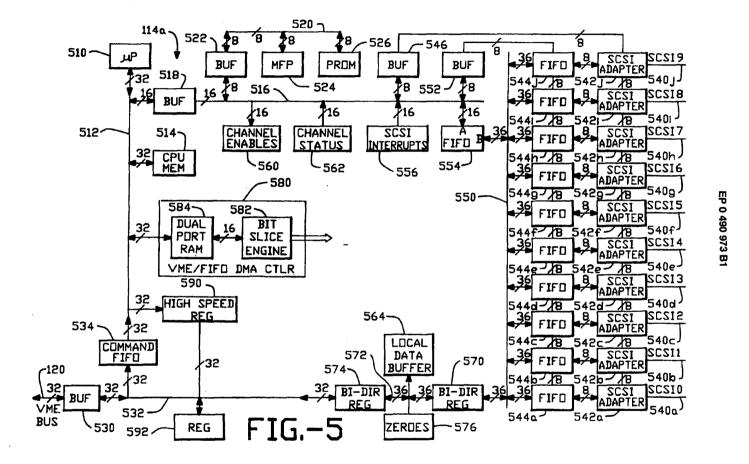

FIGURE 5 is a block diagram of one embodiment of data flow within storage router 56 of FIGURE 4. As shown, data from Fibre Channel 52 is processed by a Fibre Channel (FC) protocol unit 88 and placed in a FIFO queue 90. A direct memory access (DMA) interface 92 then takes data out of FIFO queue 90 and places it in buffer 84. Supervisor unit 86 processes the data in buffer 84 as represented by supervisor processing 93. This processing involves mapping between Fibre Channel 52 and SCSI bus 54 and applying access controls and routing functions. A DMA interface 94 then pulls data from buffer 84 and places it into a buffer 96. A SCSI protocol unit 98 pulls data from buffer 96 and communicates the data on SCSI bus 54. Data flow in the reverse direction, from SCSI bus 54 to Fibre Channel 52, is accomplished in a reverse manner.

[0029]

The storage router of the present invention is a bridge device that connects a Fibre Channel link directly to a SCSI bus and enables the exchange of SCSI command set information between application clients on SCSI bus devices and the Fibre Channel links. Further, the storage router applies access controls such that virtual local storage can be established in remote SCSI storage devices for workstations on the Fibre Channel link. In one embodiment, the storage router provides a connection for Fibre Channel links running the SCSI Fibre Channel Protocol (FCP) to legacy SCSI devices attached to a SCSI bus. The Fibre Channel topology is typically an Arbitrated Loop (FC\_AL).

[0030]

In part, the storage router enables a migration path Fibre Channel based, serial SCSI networks by providing connectivity for legacy SCSI bus devices. The storage router can be attached to a Fibre Channel Arbitrated Loop and a SCSI bus to support a number of SCSI devices. Using configuration settings, the storage router can make the SCSI bus devices available on the Fibre Channel network as FCP logical units. Once the configuration is defined, operation of the storage router is transparent to application clients. In this manner, the storage router can form an integral part of the migration to new Fibre Channel based networks while providing a means to continue using legacy SCSI devices.

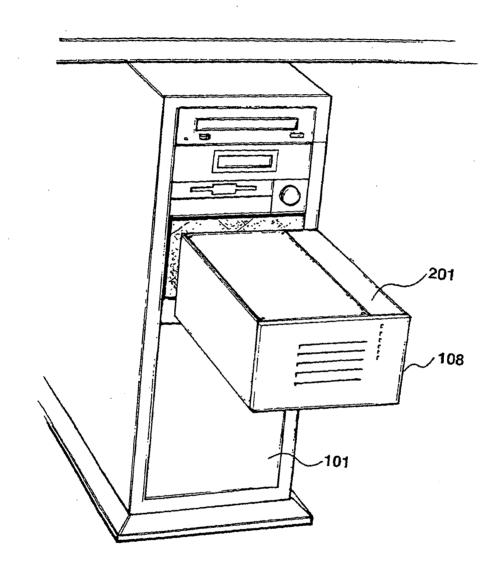

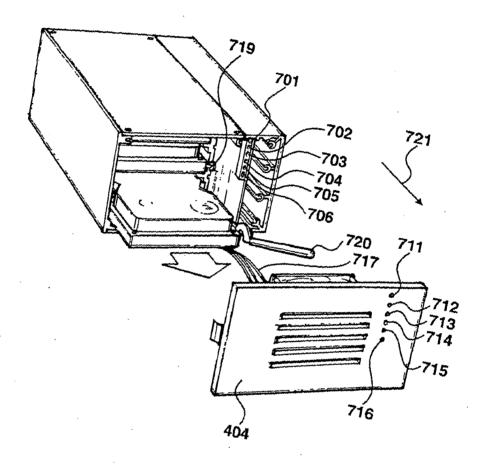

In one implementation (not shown), the storage router can be a rack mount or free standing device with an internal power supply. The storage router can have a Fibre Channel and SCSI port, and a standard, detachable power cord can be used, the FC connector can be a copper DB9 connector, and the SCSI connector can be a 68-pin type. Additional modular jacks can be provided for a serial port and an 802.3 10BaseT port, i.e. twisted pair Ethernet, for management access. The SCSI port of the storage router an support SCSI direct and sequential access target devices and can support SCSI initiators, as well. The Fibre

Channel port can interface to SCSI-3 FCP enabled devices and initiators.

- [0032] To accomplish its functionality, one implementation of the storage router uses: a Fibre Channel interface based on the HEWLETT-PACKARD TACHYON HPFC-5000 controller and a GLM media interface; an Intel 80960RP processor, incorporating independent data and program memory spaces, and associated logic required to implement a stand alone processing system; and a serial port for debug and system configuration. Further, this implementation includes a SCSI interface supporting Fast-20 based on the SYMBIOS 53C8xx series SCSI controllers, and an operating system based upon the WIND RIVERS SYSTEMS VXWORKS or IXWORKS kernel, as determined by design. In addition, the storage router includes software as required to control basic functions of the various elements, and to provide appropriate translations between the FC and SCSI protocols.

- [0033] The storage router has various modes of operation that are possible between FC and SCSI target and initiator combinations. These modes are: FC Initiator to SCSI Target; SCSI Initiator to FC Target; SCSI Initiator to SCSI Target; and FC Initiator to FC Target. The first two modes can be supported concurrently in a single storage router device and are discussed briefly below. The third mode can involve two storage router devices back to back and can serve primarily as a device to extend the physical distance beyond that possible via a direct SCSI connection. The last mode can be used to carry FC protocols encapsulated on

other transmission technologies (e.g. ATM, SONET), or to act as a bridge between two FC loops (e.g. as a two port fabric).

- The FC Initiator to SCSI Target mode provides for the basic configuration of a server using Fibre Channel to communicate with SCSI targets. This mode requires that a host system have an FC attached device and associated device drivers and software to generate SCSI-3 FCP requests. This system acts as an initiator using the storage router to communicate with SCSI target devices. The SCSI devices supported can include SCSI-2 compliant direct or sequential access (disk or tape) devices. The storage router serves to translate command and status information and transfer data between SCSI-3 FCP and SCSI-2, allowing the use of standard SCSI-2 devices in a Fibre Channel environment.

- [0035] The SCSI Initiator to FC Target mode provides for the configuration of a server using SCSI-2 to communicate with Fibre Channel targets. This mode requires that a host system has a SCSI-2 interface and driver software to control SCSI-2 target devices. The storage router will connect to the SCSI-2 bus and respond as a target to multiple target IDs. Configuration information is required to identify the target IDs to which the bridge will respond on the SCSI-2 bus. The storage router then translates the SCSI-2 requests to SCSI-3 FCP requests, allowing the use of FC devices with a SCSI host system. This will also allow features such as a tape device acting as an initiator on the SCSI bus to provide full support for this type of SCSI device.

- [0036] In general, user configuration of the storage router will be needed to support various functional modes of operation. Configuration can be modified, for example, through a serial port or through an Ethernet port via SNMP (simple network management protocol) or the Telnet session. Specifically, SNMP manageability can be provided via a B02.3 Ethernet interface. This can provide for configuration changes as well as providing statistics and error information. Configuration can also be performed via TELNET or RS-232 interfaces with menu driven command interfaces. Configuration information can be stored in a

segment of flash memory and can be retained across resets and power off cycles. Password protection can also be provided.

- In the first two modes of operation, addressing information is needed to map from FC addressing to SCSI addressing and vice versa. This can be 'hard' configuration data, due to the need for address information to be maintained across initialization and partial reconfigurations of the Fibre Channel address space. In an arbitrated loop configuration, user configured addresses will be needed for AL\_PAs in order to insure that known addresses are provided between loop reconfigurations.

- [0038] With respect to addressing, FCP and SCSI 2 systems employ different methods of addressing target devices. Additionally, the inclusion of a storage router means that a method of translating device IDs needs to be implemented. In addition, the storage router can respond to commands without passing the commands through to the opposite interface. This can be implemented to allow all generic FCP and SCSI commands to pass through the storage router to address attached devices, but allow for configuration and diagnostics to be performed directly on the storage router through the FC and SCSI interfaces.

- [0039] Management commands are those intended to be processed by the storage router controller directly. This may include diagnostic, mode, and log commands as well as other vendor-specific commands. These commands can be received and processed by both the FOP and SCSI interfaces, but are not typically bridged to the opposite interface. These commands may also have side effects on the operation of the storage router, and cause other storage router operations to change or terminate.

- [0040] A primary method of addressing management commands though the FCP and SCSI interfaces can be through peripheral device type addressing. For example, the storage router can respond to all operations addressed to logical unit (LUN) zero as a controller device. Commands that the storage router will support can

include INQUIRY as well as vendor-specific management commands. These are to be generally consistent with SCC standard commands.

- The SCSI bus is capable of establishing bus connections between targets. These targets may internally address logical units. Thus, the prioritized addressing scheme used by SCSI subsystems can be represented as follows:

BUS:TARGET:LOGICAL UNIT. The BUS identification is intrinsic in the configuration, as a SCSI initiator is attached to only one bus. Target addressing is handled by bus arbitration from information provided to the arbitrating device.

Target addresses are assigned to SCSI devices directly through some means of configuration, such as a hardware jumper, switch setting, or device specific software configuration. As such, the SCSI protocol provides only logical unit addressing within the Identify message. Bus and target information is implied by the established connection.

- [0042] Fibre Channel devices within a fabric are addressed by a unique port identifier. This identifier is assigned to a port during certain well-defined states of the FC protocol. Individual ports are allowed to arbitrate for a known, user defined address. If such an address is not provided, or if arbitration for a particular-user address fails, the port is assigned a unique address by the FC protocol. This address is generally not guaranteed to be unique between instances. Various scenarios exist where the AL-PA of a device will change, either after power cycle or loop reconfiguration.

- [0043] The FC protocol also provides a logical unit address field within command structures to provide addressing to devices internal to a port. The FCP\_CMD payload specifies an eight byte LUN field. Subsequent identification of the exchange between devices is provided by the FQXID (Fully Qualified Exchange ID).

- [0044] FC ports can be required to have specific addresses assigned. Although basic functionality is not dependent on this, changes in the loop configuration could

result in disk targets changing identifiers with the potential risk of data corruption or loss. This configuration can be straightforward, and can consist of providing the device a loop-unique ID (AL\_PA) in the range of " 01h" to "EFh." Storage routers could be shipped with a default value with the assumption that most configurations will be using single storage routers and no other devices requesting the present ID. This would provide a minimum amount of initial configuration to the system administrator. Alternately, storage routers could be defaulted to assume any address so that configurations requiring multiple storage routers on a loop would not require that the administrator assign a unique ID to the additional storage routers.

- [0045] Address translation is needed where commands are issued in the cases FC Initiator to SCSI Target and SCSI Initiator to FC Target. Target responses are qualified by the FQXID and will retain the translation acquired at the beginning of the exchange. This prevents configuration changes occurring during the course of execution of a command from causing data or state information to be inadvertently misdirected. Configuration can be required in cases of SCSI Initiator to FC Target, as discovery may not effectively allow for FCP targets to consistently be found. This is due to an FC arbitrated loop supporting addressing of a larger number of devices than a SCSI bus and the possibility of FC devices changing their AL-PA due to device insertion or other loop initialization.

- In the direct method, the translation to BUS:TARGET:LUN of the SCSI address information will be direct. That is, the values represented in the FCP LUN field will directly map to the values in effect on the SCSI bus. This provides a clean translation and does not require SCSI bus discovery. It also allows devices to be dynamically added to the SCSI bus without modifying the address map. It may not allow for complete discovery by FCP initiator devices, as gaps between device addresses may halt the discovery process. Legacy SCSI device drivers typically halt discovery on a target device at the first unoccupied LUN, and proceed to the next target. This would lead to some devices not being

discovered. However, this allows for hot plugged devices and other changes to the loop addressing.

- In the ordered method, ordered translation requires that the storage router perform discovery on reset, and collapses the addresses on the SCSI bus to sequential FSP LUN values. Thus, the FCP LUN values 0-N can represent N+1 SCSI devices, regardless of SCSI address values, in the order in which they are isolated during the SCSI discovery process. This would allow the FCP initiator discovery process to identify all mapped SCSI devices without further configuration. This has the limitation that hot-plugged devices will not be identified until the next reset cycle. In this case, the address may also be altered as well.

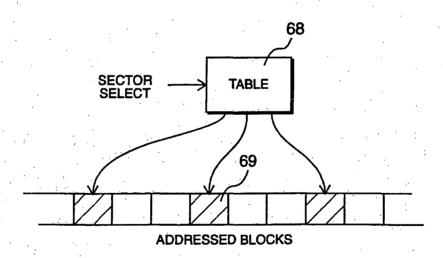

- In addition to addressing, according to the present invention, the storage router provides configuration and access controls that cause certain requests from FC Initiators to be directed to assigned virtual local storage partitioned on SCSI storage devices. For example, the same request for LUN 0 (local storage) by two different FC Initiators can be directed to two separate subsets of storage. The storage router can use tables to map, for each initiator, what storage access is available and what partition is being addressed by a particular request. In this manner, the storage space provided by SCSI storage devices can be allocated to FC initiators to provide virtual local storage as well as to create any other desired configuration for secured access.

- [0049] Although the present invention has been described in detail, it should be understood that various changes, substitutions, and alterations can be made hereto without departing from the spirit and scope of the invention as defined by the appended claims.

#### WHAT IS CLAIMED IS:

1. A storage router for providing virtual local storage on remote storage devices, comprising:

a first controller operable to interface with a first transport medium, wherein the first medium is a serial transport media; and

a processing device coupled to the first controller, wherein the processing device is configured to:

maintain a map to allocate storage space on the remote storage devices to devices connected to the first transport medium by associating representations of the devices connected to the first transport medium with representations of storage space on the remote storage devices, wherein each representation of a device connected to the first transport medium is associated with one or more representations of storage space on the remote storage devices;

control access from the devices connected to the first transport medium to the storage space on the remote storage devices in accordance with the map; and

allow access from devices connected to the first transport medium to the remote storage devices using native low level block protocol.

- 2. The storage router of Claim 1, wherein the map associates a representation of storage space on the remote storage devices with multiple devices connected to the first transport medium.

- 3. The storage router of Claim 1, wherein the storage space on the remote storage devices comprises storage space on multiple remote storage devices.

- 4. The storage router of Claim 1, wherein the map associates a representation of a device connected to the first transport medium with a representation of an entire storage space of at least one remote storage device.

- 5. The storage router of Claim 1, wherein the map resides at the storage router and is maintained at the storage router.

- 6. The storage router of Claim 1, wherein the native low level block protocol is received at the storage router via the first transport medium and the processing device uses the received native low level block protocol to allow the devices connected to the first transport medium access to storage space specifically allocated to them in the map.

- 7. The storage router of Claim 1, wherein the storage router is configured to receive commands according to a first low level block protocol from the device connected to the first transport medium and forward commands according to a second low level block protocol to the remote storage devices.

- 8. The storage router of Claim 7, wherein the first low level block protocol is an FCP protocol and the second low level block protocol is a protocol other than FCP.

- 9. The storage router of Claim 1, wherein the map comprises one or more tables.

- 10. The storage router of Claim 1, wherein the virtual local storage is provided to the devices connected to the first transport medium in a manner that is transparent to the devices and wherein the storage space allocated to the devices connected to the first transport medium appears to the devices as local storage.

- 11. The storage router of Claim 1, wherein the storage router provides centralized control of what the devices connected to the first transport medium see as local storage.

- 12. The storage router of Claim 1, wherein the representations of storage space comprise logical unit numbers that represent a subset of storage on the remote storage devices.

- 13. The storage router of Claim 12, wherein the storage router is operable to route requests to the same logical unit number from different devices connected to the first transport medium to different subsets of storage space on the remote storage devices.

- 14. The storage router of Claim 1, wherein the representations of devices connected to the first transport medium are unique identifiers.

- 15. The storage router of Claim 14, wherein the unique identifiers are world wide names.

- 16. The storage router of Claim 1, wherein the storage router is configured to allow modification of the map in a manner transparent to and without involvement of the devices connected to the first transport medium.

- 17. The storage router of Claim 1, wherein the processing device is a microprocessor.

- 18. The storage router of Claim 1, wherein the processing device is a microprocessor and associated logic to implement a stand-alone processing system.

- 19. The storage router of Claim 1, wherein the first transport medium is a fibre channel transport medium and further comprising a second transport medium connected to the remote storage devices that is a fibre channel transport medium.

- 20. A storage network comprising:

- a set of devices connected a first transport medium, wherein the first transport medium;

- a set of remote storage devices connected to a second transport medium;

- a storage router connected to the serial transport medium;

- a storage router connected to the first transport medium and second transport medium to provide virtual local storage on the remote storage devices, the storage router configured to:

- maintain a map to allocate storage space on the remote storage devices to devices connected to the first transport medium by associating representations of the devices connected to the first transport medium with representations of storage space on the remote storage devices, wherein each representation of a device connected to the first transport medium is associated with one or more representations of storage space on the remote storage devices;

control access from the devices connected to the first transport medium to the storage space on the remote storage devices in accordance with the map; and

allow access from devices connected to the first transport medium to the remote storage devices using native low level block protocol.

- 21. The storage network of Claim 20, wherein the map associates a representation of storage space on the remote storage devices with multiple devices connected to the first transport medium.

- 22. The storage network of Claim 20, wherein the storage space on the remote storage devices comprises storage space on multiple remote storage devices.

- 23. The storage network of Claim 20, wherein the map associates a representation of a device connected to the first transport medium with a representation of an entire storage space of at least one remote storage device.

- 24. The storage network of Claim 20, wherein the map resides at the storage router and is maintained at the storage router.

- 25. The storage network of Claim 20, wherein the native low level block protocol is received at the storage router via the first transport medium and the storage router uses the received native low level block protocol to allow the devices connected to the first transport medium access to storage space specifically allocated to them in the map.

- 26. The storage router of Claim 20, wherein the storage router is configured to receive commands according to a first low level block protocol from the device connected to the first transport medium and forward commands according to a second low level block protocol to the remote storage devices.

- 27. The storage network of Claim 20, wherein the first low level block protocol is an FCP protocol and the second low level block protocol is a protocol other than FCP.

- 28. The storage network of Claim 20, wherein the map comprises one or more tables.

- 29. The storage network of Claim 20, wherein the virtual local storage is provided to the devices connected to the first transport medium in a manner that is transparent to the devices and wherein the storage space allocated to the devices connected to the first transport medium appears to the devices as local storage.

- 30. The storage network of Claim 20, wherein the storage router provides centralized control of what the devices connected to the first transport medium see as local storage.

- 31. The storage network of Claim 20, wherein the representations of storage space comprise logical unit numbers that represent a subset of storage on the remote storage devices.

- 32. The storage network of Claim 31, wherein the storage router is operable to route requests to the same logical unit number from different devices connected to the first transport medium to different subsets of storage space on the remote storage devices.

- 33. The storage network of Claim 20, wherein the representations of devices connected to the first transport medium are unique identifiers.

- 34. The storage network of Claim 33, wherein the unique identifiers are world wide names.

- 35. The storage network of Claim 20, wherein the storage router is configured to allow modification of the map in a manner transparent to and without involvement of the devices connected to the first transport medium.

- 36. The storage network of Claim 20, wherein the first transport medium is a fibre channel transport medium and the second transport medium is a fibre channel transport medium.

- 37. A method for providing virtual local storage on remote storage devices comprising:

connecting a storage router between a set of devices connected to a first transport medium and a set of remote storage devices, wherein the first transport medium is a serial transport medium;

maintaining a map at the storage router to allocate storage space on the remote storage devices to devices connected to the first transport medium by associating representations of the devices connected to the first transport medium with representations of storage space on the remote storage devices, wherein each representation of a device connected to the first transport medium is associated with one or more representations of storage space on the remote storage devices;

controlling access from the devices connected to the first transport medium to the storage space on the remote storage devices in accordance with the map; and

allowing access from devices connected to the first transport medium to the remote storage devices using native low level block protocol.

- 38. The method of Claim 37, wherein the map associates a representation of storage space on the remote storage devices with multiple devices connected to the first transport medium.

- 39. The method of Claim 37, wherein the storage space on the remote storage devices comprises storage space on multiple remote storage devices.

- 40. The method of Claim 37, wherein the map associates a representation of a device connected to the first transport medium with a representation of an entire storage space of at least one remote storage device.

- 41. The method of Claim 37, wherein the map resides at the storage router and is maintained at the storage router.

- 42. The method of Claim 37, further comprising:

receiving the native low level block protocol at the storage router via the first transport medium;

using the received native low level block protocol at the storage router to allow the devices connected to the first transport medium access to storage space specifically allocated to them in the map.

- 43. The method of Claim 37, further comprising receiving commands at the storage router according to a first low level block protocol from the device connected to the first transport medium and forwarding commands according to a second low level block protocol to the remote storage devices.

- 44. The method of Claim 43, wherein the first low level block protocol is an FCP protocol and the second low level block protocol is a protocol other than FCP.

- 45. The method of Claim 37, wherein the map comprises one or more tables.

- 46. The method of Claim 37, wherein the virtual local storage is provided to the devices connected to the first transport medium in a manner that is transparent to the devices and wherein the storage space allocated to the devices connected to the first transport medium appears to the devices as local storage.

- 47. The method of Claim 37, wherein the storage router provides centralized control of what the devices connected to the first transport medium see as local storage.

- 48. The method of Claim 37, wherein the representations of storage space comprise logical unit numbers that represent a subset of storage on the remote storage devices.

- 49. The method of Claim 48, wherein the storage router is operable to route requests to the same logical unit number from different devices connected to the first transport medium to different subsets of storage space on the remote storage devices.

- 50. The method of Claim 37, wherein the representations of devices connected to the first transport medium are unique identifiers.

- 51. The method of Claim 50, wherein the unique identifiers are world wide names.

- 52. The method of Claim 51, wherein the storage router is configured to allow modification of the map in a manner transparent to and without involvement of the devices connected to the first transport medium.

- 53. The method of Claim 1 wherein connecting the storage router between a set of devices connected to a first transport medium and a set of remote storage devices further comprises connecting the storage router between a first fibre channel transport medium and a second fibre channel transport medium.

# STORAGE ROUTER AND METHOD FOR PROVIDING VIRTUAL LOCAL STORAGE

#### ABSTRACT OF THE DISCLOSURE

[0050]

A storage router and storage network provide virtual local storage on remote storage devices. A plurality of devices are connected to a first transport medium. In one embodiment, a storage router maintains a map to allocate storage space on the remote storage devices to devices connected to the first transport medium by associating representations of the devices connected to the first transport medium with representations of storage space on the remote storage devices. The storage router controls access from the devices connected to the first transport medium to the storage space on the remote storage devices in accordance with the map and allows access from devices connected to the first transport medium to the remote storage devices using native low level block protocol.

| Electronic Patent Application Fee Transmittal |                                                              |                      |          |        |                         |

|-----------------------------------------------|--------------------------------------------------------------|----------------------|----------|--------|-------------------------|

| Application Number:                           |                                                              |                      |          |        |                         |

| Filing Date:                                  |                                                              |                      |          |        |                         |

| Title of Invention:                           | STORAGE ROUTER AND METHOD FOR PROVIDING VIRTUAL LOCAL STORAG |                      |          |        |                         |

| First Named Inventor/Applicant Name:          | Ge                                                           | offrey B. Hoese      |          |        |                         |

| Filer:                                        | Joh                                                          | nn L. Adair/Delia Na | rvaiz    |        |                         |

| Attorney Docket Number:                       | CROSS1120-33                                                 |                      |          |        |                         |

| Filed as Large Entity                         |                                                              |                      |          |        |                         |

| Utility under 35 USC 111(a) Filing Fees       |                                                              |                      |          |        |                         |

| Description                                   |                                                              | Fee Code             | Quantity | Amount | Sub-Total in<br>USD(\$) |

| Basic Filing:                                 |                                                              |                      |          |        |                         |

| Utility application filing                    |                                                              | 1011                 | 1        | 330    | 330                     |

| Utility Search Fee                            |                                                              | 1111                 | 1        | 540    | 540                     |

| Utility Examination Fee                       |                                                              | 1311                 | 1        | 220    | 220                     |

| Pages:                                        |                                                              |                      |          |        |                         |

| Claims:                                       |                                                              |                      |          |        |                         |

| Claims in excess of 20                        |                                                              | 1202                 | 33       | 52     | 1716                    |

| Miscellaneous-Filing:                         |                                                              |                      |          |        |                         |

| Petition:                                     |                                                              |                      |          |        |                         |

| Description                       | Fee Code | Quantity  | Amount | Sub-Total in<br>USD(\$) |

|-----------------------------------|----------|-----------|--------|-------------------------|

| Patent-Appeals-and-Interference:  |          |           |        |                         |

| Post-Allowance-and-Post-Issuance: |          |           |        |                         |

| Extension-of-Time:                |          |           |        |                         |

| Miscellaneous:                    |          |           |        |                         |

|                                   | Tot      | al in USD | (\$)   | 2806                    |

| Electronic Acknowledgement Receipt   |                                                               |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------|--|--|--|--|

| EFS ID:                              | 6845953                                                       |  |  |  |  |

| Application Number:                  | 12690592                                                      |  |  |  |  |

| International Application Number:    |                                                               |  |  |  |  |

| Confirmation Number:                 | 8115                                                          |  |  |  |  |

| Title of Invention:                  | STORAGE ROUTER AND METHOD FOR PROVIDING VIRTUAL LOCAL STORAGE |  |  |  |  |

| First Named Inventor/Applicant Name: | Geoffrey B. Hoese                                             |  |  |  |  |

| Customer Number:                     | 44654                                                         |  |  |  |  |

| Filer:                               | John L. Adair/Delia Narvaiz                                   |  |  |  |  |

| Filer Authorized By:                 | John L. Adair                                                 |  |  |  |  |

| Attorney Docket Number:              | CROSS1120-33                                                  |  |  |  |  |

| Receipt Date:                        | 20-JAN-2010                                                   |  |  |  |  |

| Filing Date:                         |                                                               |  |  |  |  |

| Time Stamp:                          | 16:24:15                                                      |  |  |  |  |

| Application Type:                    | Utility under 35 USC 111(a)                                   |  |  |  |  |

## **Payment information:**

| Submitted with Payment                   | yes             |

|------------------------------------------|-----------------|

| Payment Type                             | Deposit Account |

| Payment was successfully received in RAM | \$2806          |

| RAM confirmation Number                  | 3127            |

| Deposit Account                          | 503183          |

| Authorized User                          |                 |

The Director of the USPTO is hereby authorized to charge indicated fees and credit any overpayment as follows:

Charge any Additional Fees required under 37 C.F.R. Section 1.16 (National application filing, search, and examination fees)

Charge any Additional Fees required under 37 C.F.R. Section 1.17 (Patent application and reexamination processing fees)

Charge any Additional Fees required under 37 C.F.R. Section 1.19 (Document supply fees)

Charge any Additional Fees required under 37 C.F.R. Section 1.20 (Post Issuance fees)

Charge any Additional Fees required under 37 C.F.R. Section 1.21 (Miscellaneous fees and charges)

## File Listing:

| Document<br>Number | Document Description               | File Name                              | File Size(Bytes)/<br>Message Digest                    | Multi<br>Part /.zip | Pages<br>(if appl.) |

|--------------------|------------------------------------|----------------------------------------|--------------------------------------------------------|---------------------|---------------------|

| 1                  | Miscellaneous Incoming Letter      | CROSS1120-33_Cert_Transmiss<br>ion.pdf |                                                        | no                  | 1                   |

| Warnings:          |                                    | 1500,                                  | 7d03f1dc62be0e2f8fd6d2793fc0af2a9d51a<br>966           |                     |                     |

| Information:       |                                    |                                        |                                                        |                     |                     |

| 2                  | Miscellaneous Incoming Letter      | CROSS1120-33_ld_chg_POA.<br>pdf        | 153882<br>c7162bfeeceb5044f313e4c768dc96c5d595<br>1a60 | no                  | 6                   |

| Warnings:          |                                    |                                        | 1200                                                   |                     |                     |

| Information:       |                                    |                                        |                                                        |                     |                     |

| 3                  | Oath or Declaration filed          | CROSS1120-33_Declaration_fr_           | 125807                                                 | no                  | 4                   |

|                    |                                    | parent.pdf                             | c84a7ce304d738dabf74ae001585566f64a8<br>a261           | 0                   |                     |

| Warnings:          |                                    |                                        |                                                        |                     |                     |

| Information:       |                                    | I                                      | <u> </u>                                               |                     |                     |

| 4                  | Drawings-only black and white line | CROSS1120-33_Drawings.pdf              | 36044                                                  | , no                | 2                   |

|                    | drawings                           |                                        | f06f4160ea41d04338498da87a96713f1652<br>c97b           | no                  |                     |

| Warnings:          |                                    |                                        |                                                        |                     |                     |

| Information:       |                                    | <del> </del>                           | 1                                                      |                     |                     |

| 5                  | Transmittal of New Application     | CROSS1120-33_Transmittal.pdf           | 75251                                                  | no                  | 1                   |

|                    |                                    |                                        | bcbbc251aa07bf22f000918791a0e6c8517f<br>dac9           |                     |                     |

| Warnings:          |                                    |                                        |                                                        |                     |                     |

| Information:       |                                    |                                        |                                                        |                     |                     |

| 6                  |                                    | CROSS1120-33_Application.pdf           | 89877                                                  | yes                 | 25                  |

| Ü                  |                                    | CNOSSTT20 35_Application.pdf           | 516836a9c3cb832e9c0eee0634652871cfb<br>45e3a           | yes                 | 23                  |

|                    | Multip                             | art Description/PDF files in .         | zip description                                        |                     |                     |

|                    | Document De                        | scription                              | Start                                                  | E                   | nd                  |

|                    | Specification                      |                                        | 1                                                      |                     | 16                  |

|                    | Claims                             |                                        | 17                                                     | 24                  |                     |

|                    | Abstract                           |                                        | 25                                                     | 25                  |                     |

| Warnings:          |                                    |                                        | 1                                                      |                     |                     |

| Information: |                           |                              |                                              |       |              |

|--------------|---------------------------|------------------------------|----------------------------------------------|-------|--------------|

| 7            | Fee Worksheet (PTO-875)   | fee-info.pdf                 | 36748                                        | no    | 2            |

| ,            | / Tee worksheet (110-073) |                              | 13f98da56b3ebe3eaa50c6aeefcc73a79b31<br>0d2f |       | <u>-</u><br> |

| Warnings:    |                           |                              |                                              |       |              |

| Information: |                           |                              |                                              |       |              |

|              |                           | Total Files Size (in bytes): | 5-                                           | 41181 |              |

This Acknowledgement Receipt evidences receipt on the noted date by the USPTO of the indicated documents, characterized by the applicant, and including page counts, where applicable. It serves as evidence of receipt similar to a Post Card, as described in MPEP 503.

#### New Applications Under 35 U.S.C. 111

If a new application is being filed and the application includes the necessary components for a filing date (see 37 CFR 1.53(b)-(d) and MPEP 506), a Filing Receipt (37 CFR 1.54) will be issued in due course and the date shown on this Acknowledgement Receipt will establish the filing date of the application.

#### National Stage of an International Application under 35 U.S.C. 371

If a timely submission to enter the national stage of an international application is compliant with the conditions of 35 U.S.C. 371 and other applicable requirements a Form PCT/DO/EO/903 indicating acceptance of the application as a national stage submission under 35 U.S.C. 371 will be issued in addition to the Filing Receipt, in due course.

#### New International Application Filed with the USPTO as a Receiving Office

If a new international application is being filed and the international application includes the necessary components for an international filing date (see PCT Article 11 and MPEP 1810), a Notification of the International Application Number and of the International Filing Date (Form PCT/RO/105) will be issued in due course, subject to prescriptions concerning national security, and the date shown on this Acknowledgement Receipt will establish the international filing date of the application.

| Electronic Acknowledgement Receipt   |                                                               |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------|--|--|--|--|

| EFS ID:                              | 6845953                                                       |  |  |  |  |

| Application Number:                  | 12690592                                                      |  |  |  |  |

| International Application Number:    |                                                               |  |  |  |  |

| Confirmation Number:                 | 8115                                                          |  |  |  |  |

| Title of Invention:                  | STORAGE ROUTER AND METHOD FOR PROVIDING VIRTUAL LOCAL STORAGE |  |  |  |  |

| First Named Inventor/Applicant Name: | Geoffrey B. Hoese                                             |  |  |  |  |

| Customer Number:                     | 44654                                                         |  |  |  |  |

| Filer:                               | John L. Adair/Delia Narvaiz                                   |  |  |  |  |

| Filer Authorized By:                 | John L. Adair                                                 |  |  |  |  |

| Attorney Docket Number:              | CROSS1120-33                                                  |  |  |  |  |

| Receipt Date:                        | 20-JAN-2010                                                   |  |  |  |  |