# **EXHIBIT** A

Samsung Ex. 1413A p. 1

# Universal Serial Bus Specification

Compaq Intel Microsoft NEC

Revision 1.1 September 23, 1998

Samsung Ex. 1413A p. 2

#### Scope of this Revision

The 1.1 revision of the specification is intended for product design. Every attempt has been made to ensure a consistent and implementable specification. Implementations should ensure compliance with this revision.

| Revision | Issue Date         | Comments                                                     |

|----------|--------------------|--------------------------------------------------------------|

| 0.7      | November 11, 1994  | Supersedes 0.6e.                                             |

| 0.8      | December 30, 1994  | Revisions to Chapters 3-8, 10, and 11. Added appendixes.     |

| 0.9      | April 13, 1995     | Revisions to all the chapters.                               |

| 0.99     | August 25, 1995    | Revisions to all the chapters.                               |

| 1.0 FDR  | November 13, 1995  | Revisions to Chapters 1, 2, 5-11.                            |

| 1.0      | January 15, 1996   | Edits to Chapters 5, 6, 7, 8, 9, 10, and 11 for consistency. |

| 1.1      | September 23, 1998 | Updates to all chapters to fix problems identified.          |

**Revision History**

Universal Serial Bus Specification Copyright © 1998, Compaq Computer Corporation, Intel Corporation, Microsoft Corporation, NEC Corporation. All rights reserved.

#### INTELLECTUAL PROPERTY DISCLAIMER

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE. A LICENSE IS HEREBY GRANTED TO REPRODUCE AND DISTRIBUTE THIS SPECIFICATION FOR INTERNAL USE ONLY. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY OTHER INTELLECTUAL PROPERTY RIGHTS IS GRANTED OR INTENDED HEREBY.

AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF PROPRIETARY RIGHTS, RELATING TO IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. AUTHORS OF THIS SPECIFICATION ALSO DO NOT WARRANT OR REPRESENT THAT SUCH IMPLEMENTATION(S) WILL NOT INFRINGE SUCH RIGHTS.

GeoPort and Apple Desktop Bus are trademarks of Apple Computer, Inc.

Windows and Windows NT are trademarks and Microsoft and Win32 are registered trademarks of Microsoft Corporation. IBM, PS/2, and Micro Channel are registered trademarks of International Business Machines Corporation.

AT&T is a registered trademark of American Telephone and Telegraph Company.

Compaq is a registered trademark of Compaq Computer Corporation.

UNIX is a registered trademark of UNIX System Laboratories.

I<sup>2</sup>C is a trademark of Phillips Semiconductors.

DEC is a trademark of Digital Equipment Corporation.

All other product names are trademarks, registered trademarks, or servicemarks of their respective owners.

#### Please send comments via electronic mail to techsup@usb.org

For industry information, refer to the USB Implementers Forum web page at http://www.usb.org

# Contents

| CHAF                            | PTER 1 INTRODUCTION                                                             |

|---------------------------------|---------------------------------------------------------------------------------|

| 1.1                             | Motivation1                                                                     |

| 1.2                             | Objective of the Specification1                                                 |

| 1.3                             | Scope of the Document2                                                          |

| 1.4                             | Document Organization                                                           |

| CHAF                            | PTER 2 TERMS AND ABBREVIATIONS                                                  |

| CHAF                            | PTER 3 BACKGROUND 11                                                            |

| 3.1                             | Goals for the Universal Serial Bus11                                            |

| 3.2                             | Taxonomy of Application Space12                                                 |

| 3.3                             | Feature List12                                                                  |

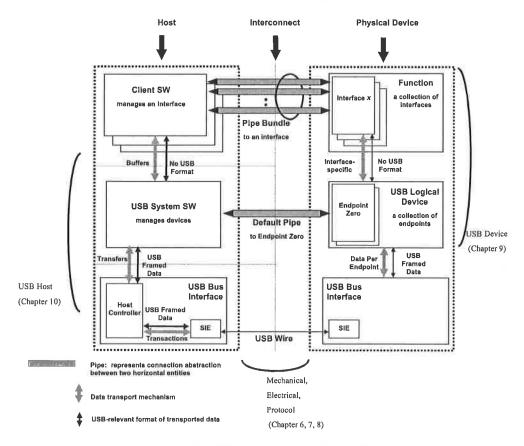

| CHAF                            | PTER 4 ARCHITECTURAL OVERVIEW15                                                 |

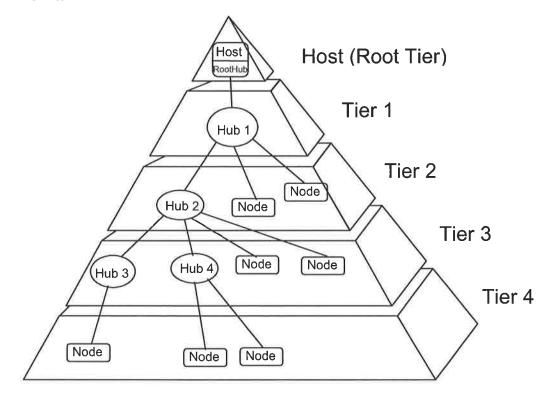

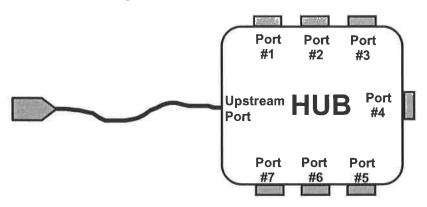

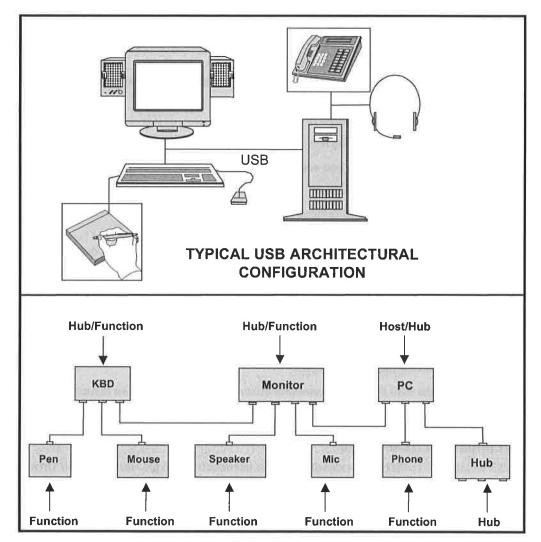

| <b>4.1</b><br>4.1               | USB System Description         15           1.1         Bus Topology         16 |

| <b>4.2</b><br>4.2<br>4.2        |                                                                                 |

| <b>4.3</b><br>4.3<br>4.3        |                                                                                 |

| 4.4                             | Bus Protocol                                                                    |

| <b>4.5</b><br>4.5<br>4.5        | Robustness                                                                      |

| <b>4.6</b><br>4.6<br>4.6<br>4.6 | 5.2 Removal of USB Devices                                                      |

|                                 | 5.3 Bus Enumeration                                                             |

| 4.7.3       Interrupt Transfers       21         4.7.4       Isochronous Transfers       21         4.7.5       Allocating USB Bandwidth       21         4.8.1       Device Descriptions       21         4.8.2       Device Descriptions       22         4.8.1       Device Descriptions       22         4.9       USB Host: Hardware and Software       24         4.10       Architectural Extensions       24         CHAPTER 5 USB DATA FLOW MODEL       25         5.1       Implementer Viewpoints       25         5.2       Bus Topology       27         5.2.1       USB Views       27         5.2.2       USB Dovices       28         5.2.3       Physical Bus Topology       27         5.2.4       Logical Bus Topology       29         5.2.4       Logical Bus Topology       29         5.2.4       Logical Bus Topology       30         5.3       USB Communication Flow       31         5.3       Lost Control Transfer Tofunction Relationship       30         5.3       Control Transfer Data Format       36         5.4       Transfer Types       33         5.5       Control Transfer Data Format<                                                                                                                                                                    | 4.7.2  | Bulk Transfers                                | Ì |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------|---|

| 4.7.4       Isochronus Transfers       21         4.7.5       Allocating USB Bandwidth       21         4.8       USB Devices       21         4.8.1       Device Characterizations       21         4.8.2       Device Descriptions       22         4.9       USB Host: Hardware and Software       24         4.10       Architectural Extensions       24         CHAPTER 5       USB DATA FLOW MODEL       25         5.1       Implementer Viewpoints       25         5.2       Bus Topology       27         5.2.1       USB Devices       28         5.2.2       USB Devices       28         5.2.3       Physical Bus Topology       27         5.2.4       USB Communication Flow       30         5.2.5       Client Software-to-function Relationship       30         5.3       Pipes       33         5.4       Transfer Types       35         5.5       Control Transfer Data Format       36         5.3.1       Device Endpoints       37         5.3.2       Pipes       33         5.4       Critransfer Data Format       36         5.5.       Control Transfer Data Constraints       37<                                                                                                                                                                                      | 4.7.3  |                                               |   |

| 4.8       USB Device       21         4.8.1       Device Characterizations       21         4.8.2       Device Descriptions       22         4.9       USB Host: Hardware and Software       24         4.10       Architectural Extensions       24         4.10       Architectural Extensions       24         CHAPTER 5 USB DATA FLOW MODEL       25         5.1       Implementer Viewpoints       25         5.2       Bus Topology       27         5.2.1       USB Dotices       28         5.2.3       Physical Bus Topology       29         5.4       Logical Bus Topology       29         5.2.4       USB Communication Flow       31         5.3.1       Device Endpoints       32         5.3       USB Communication Flow       31         5.3.1       Device Endpoints       32         5.3.2       Pipes       35         5.4       Transfer Tapser Data Format       36         5.5.1       Control Transfer Data Format       36         5.5.1       Control Transfer Data Format       31         5.6       Isochronous Transfer Data Format       36         5.7       Interrupt Transfer Data Sequences                                                                                                                                                                         | 4.7.4  | Isochronous Transfers                         |   |

| 4.8.1       Device Characterizations       21         4.8.2       Device Descriptions       22         4.9       USB Host: Hardware and Software       24         4.10       Architectural Extensions       24         CHAPTER 5 USB DATA FLOW MODEL       25         5.1       Implementer Viewpoints       25         5.2       Bus Topology       27         5.2.1       USB Host       27         5.2.2       USB Devices       28         5.2.3       Physical Bus Topology       29         5.2.4       USB Devices       28         5.2.3       Physical Bus Topology       29         5.2.4       Cleical Bus Topology       29         5.2.5       Cleint Software-to-function Relationship       30         5.3       USB Communication Flow       31         5.3.1       Device Endpoints       32         5.3       Control Transfer Data Format       36         5.5.1       Control Transfer Data Format       36         5.5.2       Control Transfer Bus Access Constraints       37         5.5.4       Control Transfer Bus Access Constraints       38         5.5.5       Control Transfer Direction       37         5.                                                                                                                                                           | 4.7.5  | Allocating USB Bandwidth                      |   |

| 4.8.1       Device Characterizations       21         4.8.2       Device Descriptions       22         4.9       USB Host: Hardware and Software       24         4.10       Architectural Extensions       24         CHAPTER 5 USB DATA FLOW MODEL       25         5.1       Implementer Viewpoints       25         5.2       Bus Topology       27         5.2.1       USB Host       27         5.2.2       USB Devices       28         5.2.3       Physical Bus Topology       29         5.2.4       USB Devices       28         5.2.3       Physical Bus Topology       29         5.2.4       Cleical Bus Topology       29         5.2.5       Cleint Software-to-function Relationship       30         5.3       USB Communication Flow       31         5.3.1       Device Endpoints       32         5.3       Control Transfer Data Format       36         5.5.1       Control Transfer Data Format       36         5.5.2       Control Transfer Bus Access Constraints       37         5.5.4       Control Transfer Bus Access Constraints       38         5.5.5       Control Transfer Direction       37         5.                                                                                                                                                           | 40 N   | SD D. 1                                       |   |

| 4.8.2       Device Descriptions       22         4.9       USB Host: Hardware and Software       24         4.10       Architectural Extensions       24         CHAPTER 5 USB DATA FLOW MODEL       25         5.1       Implementer Viewpoints       25         5.2       Bus Topology       27         5.2.1       USB Host       27         5.2.2       USB Devices       28         5.2.3       Physical Bus Topology       29         5.2.4       Logical Bus Topology       30         5.2.5       Client Software-to-function Relationship       30         5.3.1       Device Endpoints       32         5.3.2       Pipes       33         5.4       Transfer Types       35         5.5       Control Transfer Data Format       36         5.5.1       Control Transfer Data Format       36         5.5.2       Control Transfer Data Sequences       40         5.6       Isochronous Transfer Data Format       36         5.5.5       Control Transfer Data Format       36         5.6.1       Isochronous Transfer Data Format       37         5.6.1       Isochronous Transfer Data Format       37         5.6.1                                                                                                                                                                  |        |                                               |   |

| 4.9       USB Host: Hardware and Software       24         4.10       Architectural Extensions       24         CHAPTER 5 USB DATA FLOW MODEL       25         5.1       Implementer Viewpoints       25         5.2       Bus Topology       27         5.2.1       USB Devices       28         5.2.3       Dynamic Topology       29         5.4       Logical Bus Topology       29         5.2.4       Logical Bus Topology       29         5.2.5       Client Software-to-function Relationship       30         5.3       USB Communication Flow       31         5.3.1       Device Endpoints       32         5.3.2       Pipes       33         5.4       Transfer Types       35         5.5       Control Transfer Data Format       36         5.5.1       Control Transfer Data Format       36         5.5.2       Control Transfer Data Sequences       37         5.4       Isochronous Transfer Data Sequences       36         5.5       Control Transfer Data Sequences       36         5.6       Isochronous Transfer Data Sequences       37         5.5       Control Transfer Data Sequences       37                                                                                                                                                                        |        |                                               |   |

| 4.10       Architectural Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.8.2  | Device Descriptions                           |   |

| CHAPTER 5 USB DATA FLOW MODEL       25         5.1 Implementer Viewpoints       25         5.2 Bus Topology       27         5.2.1 USB Host       27         5.2.2 USB Devices       28         5.2.3 Physical Bus Topology       30         5.2.5 Client Software-to-function Relationship       30         5.3 USB Communication Flow       31         5.3.1 Device Endpoints       32         5.3.2 Pipes       33         5.4 Transfer Types       35         5.5 Control Transfers       36         5.5.1 Control Transfer Data Format       36         5.5.2 Control Transfer Direction       37         5.5.3 Control Transfer Data Format       36         5.5.4 Control Transfer Data Sequences       40         5.6 Isochronous Transfer Data Sequences       40         5.6 Isochronous Transfer Data Sequences       41         5.6.1 Isochronous Transfer Bus Access Constraints       34         5.6.2 Isochronous Transfer Data Sequences       41         5.6.3 Isochronous Transfer Data Sequences       41         5.6.4 Isochronous Transfer Data Sequences       43         5.7.1 Interrupt Transfer Data Sequences       43         5.7.2 Interrupt Transfer Data Format       43         5.7.3 In                                                                                | 4.9 U  | SB Host: Hardware and Software24              | ł |

| 5.1       Implementer Viewpoints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.10 A | rchitectural Extensions24                     | ł |

| 5.1       Implementer Viewpoints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | СНАРТ  | ER 5 USB DATA FLOW MODEL                      | 5 |

| 5.2       Bus Topology       27         5.2.1       USB Host       27         5.2.2       USB Devices       28         5.2.3       Physical Bus Topology       29         5.2.4       Logical Bus Topology       30         5.2.5       Client Software-to-function Relationship       30         5.3       USB Communication Flow       31         5.3.1       Device Endpoints       32         5.3.2       Pipes       33         5.4       Transfer Types       35         5.5       Control Transfer Data Format       36         5.5.2       Control Transfer Direction       37         5.5.3       Control Transfer Direction       37         5.5.4       Control Transfer Direction       37         5.5.5       Control Transfer Direction       38         5.5.5       Control Transfer Direction       38         5.5.5       Control Transfer Data Sequences       40         5.6       Isochronous Transfer Access Constraints       38         5.5.5       Control Transfer Data Format       41         5.6.1       Isochronous Transfer Date Format       41         5.6.1       Isochronous Transfer Dacket Size Constraints       42                                                                                                                                               |        |                                               |   |

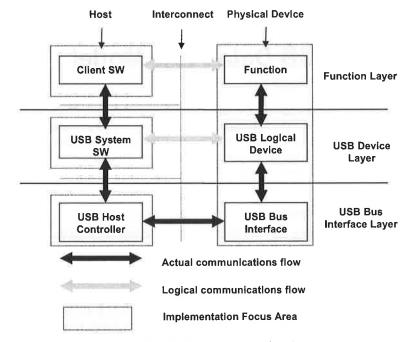

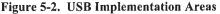

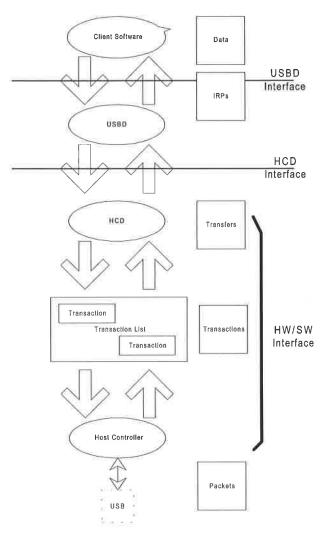

| 5.2.1       USB Host       27         5.2.2       USB Devices       28         5.2.3       Physical Bus Topology       29         5.2.4       Logical Bus Topology       30         5.2.5       Client Software-to-function Relationship       30         5.3       USB Communication Flow       31         5.3.1       Device Endpoints       32         5.3.2       Pipes       33         5.4       Transfer Types       35         5.5       Control Transfer Software       36         5.5.1       Control Transfer Data Format       36         5.5.2       Control Transfer Direction       37         5.5.4       Control Transfer Bus Access Constraints       38         5.5.5       Control Transfer Bus Access Constraints       38         5.5.5       Control Transfer Data Sequences       40         5.6       Isochronous Transfer Data Format       41         5.6.1       Isochronous Transfer Data Format       41         5.6.2       Schronous Transfer Data Format       41         5.6.4       Isochronous Transfer Data Format       41         5.6.5       Isochronous Transfer Data Format       41         5.6.6       Isochronous Transfe                                                                                                                                 | 5.1 I  | nplementer Viewpoints25                       | j |

| 5.2.1       USB Host       27         5.2.2       USB Devices       28         5.2.3       Physical Bus Topology       29         5.2.4       Logical Bus Topology       30         5.2.5       Client Software-to-function Relationship       30         5.3       USB Communication Flow       31         5.3.1       Device Endpoints       32         5.3.2       Pipes       33         5.4       Transfer Types       35         5.5       Control Transfer Software       36         5.5.1       Control Transfer Data Format       36         5.5.2       Control Transfer Direction       37         5.5.4       Control Transfer Bus Access Constraints       38         5.5.5       Control Transfer Bus Access Constraints       38         5.5.5       Control Transfer Data Sequences       40         5.6       Isochronous Transfer Data Format       41         5.6.1       Isochronous Transfer Data Format       41         5.6.2       Schronous Transfer Data Format       41         5.6.4       Isochronous Transfer Data Format       41         5.6.5       Isochronous Transfer Data Format       41         5.6.6       Isochronous Transfe                                                                                                                                 | 5.2 B  | us Topology                                   | 1 |

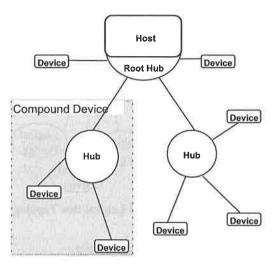

| 5.2.3       Physical Bus Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        | USB Host                                      | 7 |

| 5.2.3       Physical Bus Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.2.2  | USB Devices                                   | 3 |

| 5.2.4       Logical Bus Topology.       30         5.2.5       Client Software-to-function Relationship.       30         5.3       USB Communication Flow       31         5.3.1       Device Endpoints       32         5.3.2       Pipes       33         5.4       Transfer Types.       35         5.5       Control Transfer S       36         5.5.1       Control Transfer Data Format       36         5.5.2       Control Transfer Data Format       36         5.5.3       Control Transfer Data Format       36         5.5.4       Control Transfer Data Sequences       37         5.5.3       Control Transfer Bus Access Constraints       37         5.5.4       Control Transfer Data Sequences       40         5.6       Isochronous Transfer Data Sequences       41         5.6.1       Isochronous Transfer Data Format       41         5.6.2       Isochronous Transfer Data Format       41         5.6.3       Isochronous Transfer Data Sequences       41         5.6.4       Isochronous Transfer Data Sequences       43         5.7       Interrupt Transfer Data Sequences       43         5.7.1       Interrupt Transfer Data Format       43                                                                                                                       | 5.2.3  | Physical Bus Topology                         | ) |

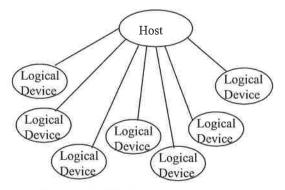

| 5.2.5       Client Software-to-function Relationship       30         5.3       USB Communication Flow       31         5.3.1       Device Endpoints       32         5.3.2       Pipes       33         5.4       Transfer Types       35         5.5       Control Transfer S       36         5.5.1       Control Transfer Direction       36         5.5.2       Control Transfer Direction       37         5.5.3       Control Transfer Packet Size Constraints       37         5.5.4       Control Transfer Packet Size Constraints       37         5.5.5       Control Transfer Data Sequences       40         5.6       Isochronous Transfer Data Sequences       40         5.6       Isochronous Transfer Direction       41         5.6.1       Isochronous Transfer Data Format       41         5.6.2       Isochronous Transfer Data Format       41         5.6.3       Isochronous Transfer Data Sequences       43         5.7.1       Interrupt Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Data Format       43         5.7.1       Interrupt Transfer Data Format       43         5.7.2       Interrupt Transfer Data Format       43                                                                                                   | 5.2.4  | Logical Bus Topology                          | ) |

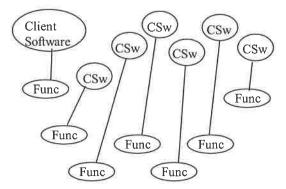

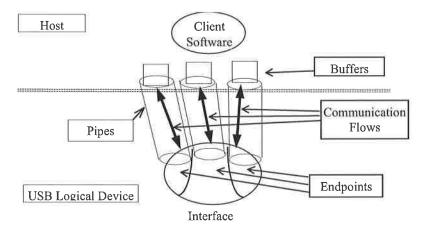

| 5.3.1       Device Endpoints       32         5.3.2       Pipes       33         5.4       Transfer Types       35         5.5       Control Transfer Data Format       36         5.5.1       Control Transfer Data Format       36         5.5.2       Control Transfer Data Format       36         5.5.3       Control Transfer Packet Size Constraints       37         5.5.4       Control Transfer Bus Access Constraints       38         5.5.5       Control Transfer Data Sequences       40         5.6       Isochronous Transfer Data Sequences       40         5.6       Isochronous Transfer Data Format       41         5.6.1       Isochronous Transfer Data Format       41         5.6.2       Isochronous Transfer Packet Size Constraints       41         5.6.3       Isochronous Transfer Bus Access Constraints       41         5.6.4       Isochronous Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Data Sequences       43         5.7       Interrupt Transfer Data Sequences       43         5.7.1       Interrupt Transfer Data Sequences       43         5.7.2       Interrupt Transfer Data Format       43         5.7.3       Interrupt                                                                                     | 5.2.5  | Client Software-to-function Relationship      | ) |

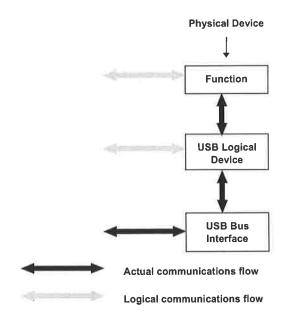

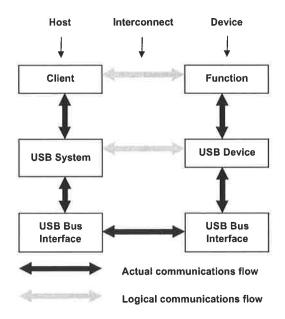

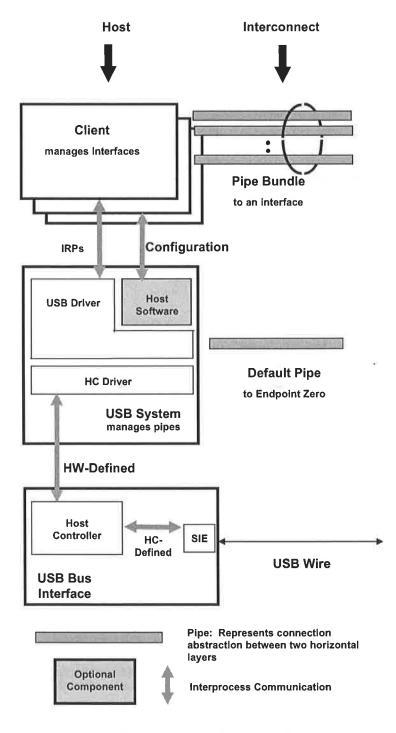

| 5.3.1       Device Endpoints       32         5.3.2       Pipes       33         5.4       Transfer Types       35         5.5       Control Transfer Data Format       36         5.5.1       Control Transfer Data Format       36         5.5.2       Control Transfer Data Format       36         5.5.3       Control Transfer Packet Size Constraints       37         5.5.4       Control Transfer Bus Access Constraints       38         5.5.5       Control Transfer Data Sequences       40         5.6       Isochronous Transfer Data Sequences       40         5.6       Isochronous Transfer Data Format       41         5.6.1       Isochronous Transfer Data Format       41         5.6.2       Isochronous Transfer Packet Size Constraints       41         5.6.3       Isochronous Transfer Bus Access Constraints       41         5.6.4       Isochronous Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Data Sequences       43         5.7       Interrupt Transfer Data Sequences       43         5.7.1       Interrupt Transfer Data Sequences       43         5.7.2       Interrupt Transfer Data Format       43         5.7.3       Interrupt                                                                                     | 5.3 T  | SB Communication Flow                         | l |

| 5.3.2       Pipes       33         5.4       Transfer Types       35         5.5       Control Transfer Data Format       36         5.5.1       Control Transfer Data Format       36         5.5.2       Control Transfer Direction       37         5.5.3       Control Transfer Packet Size Constraints       37         5.5.4       Control Transfer Bus Access Constraints       37         5.5.5       Control Transfer Bus Access Constraints       38         5.5.5       Control Transfer Data Sequences       40         5.6       Isochronous Transfer Data Format       41         5.6.1       Isochronous Transfer Data Format       41         5.6.2       Isochronous Transfer Data Format       41         5.6.3       Isochronous Transfer Bus Access Constraints       41         5.6.4       Isochronous Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Data Sequences       43         5.7       Interrupt Transfer Data Format       43         5.7.1       Interrupt Transfer Data Format       43         5.7.2       Interrupt Transfer Direction       43         5.7.3 <t< td=""><td></td><td>Device Endpoints</td><td>2</td></t<>                              |        | Device Endpoints                              | 2 |

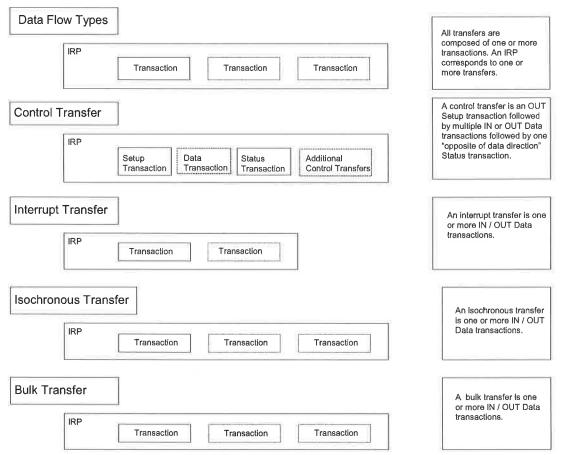

| 5.4       Transfer Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.3.2  | Pipes                                         | 5 |

| 5.5.1       Control Transfer Data Format       36         5.5.2       Control Transfer Direction       37         5.5.3       Control Transfer Packet Size Constraints       37         5.5.4       Control Transfer Bus Access Constraints       38         5.5.5       Control Transfer Data Sequences       40         5.6       Isochronous Transfer Data Sequences       40         5.6       Isochronous Transfer Data Format       41         5.6.1       Isochronous Transfer Direction       41         5.6.2       Isochronous Transfer Direction       41         5.6.3       Isochronous Transfer Direction       41         5.6.4       Isochronous Transfer Packet Size Constraints       41         5.6.5       Isochronous Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Data Sequences       43         5.7       Interrupt Transfer Bus Access Constraints       43         5.7.1       Interrupt Transfer Direction       43         5.7.2       Interrupt Transfer Packet Size Constraints       43         5.7.3       Interrupt Transfer Bus Access Constraints       43         5.7.4       Interrupt Transfer Bus Access Constraints       44         5.7.5       Interrupt Transfer Data Sequence                                         | 5.4 T  | ransfer Types                                 | 5 |

| 5.5.2       Control Transfer Direction       37         5.5.3       Control Transfer Packet Size Constraints       37         5.5.4       Control Transfer Bus Access Constraints       38         5.5.5       Control Transfer Data Sequences       40         5.6       Isochronous Transfers       41         5.6.1       Isochronous Transfer Data Format       41         5.6.2       Isochronous Transfer Data Format       41         5.6.3       Isochronous Transfer Data Format       41         5.6.4       Isochronous Transfer Data Format       41         5.6.3       Isochronous Transfer Bus Access Constraints       41         5.6.4       Isochronous Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Data Sequences       43         5.7       Interrupt Transfers       43         5.7.1       Interrupt Transfer Data Format       43         5.7.2       Interrupt Transfer Data Format       43         5.7.3       Interrupt Transfer Packet Size Constraints       43         5.7.4       Interrupt Transfer Bus Access Constraints       44         5.7.5       Interrupt Transfer Data Sequences       46 <td>5.5 0</td> <td>Control Transfers</td> <td>5</td> | 5.5 0  | Control Transfers                             | 5 |

| 5.5.3       Control Transfer Packet Size Constraints.       37         5.5.4       Control Transfer Bus Access Constraints.       38         5.5.5       Control Transfer Data Sequences.       40         5.6       Isochronous Transfers       41         5.6.1       Isochronous Transfer Data Format.       41         5.6.2       Isochronous Transfer Data Format.       41         5.6.3       Isochronous Transfer Data Format.       41         5.6.4       Isochronous Transfer Data Format.       41         5.6.5       Isochronous Transfer Packet Size Constraints       41         5.6.4       Isochronous Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Data Sequences.       43         5.7       Interrupt Transfers       43         5.7.1       Interrupt Transfer Data Format.       43         5.7.2       Interrupt Transfer Data Format.       43         5.7.3       Interrupt Transfer Packet Size Constraints.       43         5.7.4       Interrupt Transfer Bus Access Constraints.       44         5.7.5       Interrupt Transfer Data Sequences.       46         5.8       Bulk Transfer Data Format.                                                   | 5.5.1  |                                               |   |

| 5.5.4       Control Transfer Bus Access Constraints.       38         5.5.5       Control Transfer Data Sequences.       40         5.6       Isochronous Transfer Data Format.       41         5.6.1       Isochronous Transfer Direction.       41         5.6.2       Isochronous Transfer Direction.       41         5.6.3       Isochronous Transfer Packet Size Constraints.       41         5.6.4       Isochronous Transfer Bus Access Constraints.       41         5.6.5       Isochronous Transfer Bus Access Constraints.       42         5.6.5       Isochronous Transfer Data Sequences.       43         5.7       Interrupt Transfer Data Sequences.       43         5.7.1       Interrupt Transfer Data Format.       43         5.7.2       Interrupt Transfer Direction       43         5.7.3       Interrupt Transfer Packet Size Constraints.       43         5.7.4       Interrupt Transfer Bus Access Constraints.       44         5.7.5       Interrupt Transfer Data Sequences.       46         5.8       Bulk Transfer Data Sequences.       46         5.8.1       Bulk Transfer Data Format       47         5.8.2       Bulk Transfer Direction       47                                                                                                         | 5.5.2  |                                               |   |

| 5.5.5       Control Transfer Data Sequences       40         5.6       Isochronous Transfer Data Format       41         5.6.1       Isochronous Transfer Data Format       41         5.6.2       Isochronous Transfer Direction       41         5.6.3       Isochronous Transfer Direction       41         5.6.4       Isochronous Transfer Packet Size Constraints       41         5.6.5       Isochronous Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Data Sequences       43         5.7       Interrupt Transfers       43         5.7.1       Interrupt Transfer Data Format       43         5.7.2       Interrupt Transfer Direction       43         5.7.3       Interrupt Transfer Packet Size Constraints       43         5.7.4       Interrupt Transfer Bus Access Constraints       44         5.7.5       Interrupt Transfer Data Sequences       46         5.8       Bulk Transfer Data Sequences       46         5.8.1       Bulk Transfer Data Format       47         5.8.2       Bulk Transfer Direction       47                                                                                                                                                                                                                      | 5.5.3  |                                               |   |

| 5.6       Isochronous Transfers       41         5.6.1       Isochronous Transfer Data Format       41         5.6.2       Isochronous Transfer Direction       41         5.6.3       Isochronous Transfer Packet Size Constraints       41         5.6.4       Isochronous Transfer Bus Access Constraints       42         5.6.5       Isochronous Transfer Data Sequences       43         5.7       Interrupt Transfers       43         5.7.1       Interrupt Transfer Data Format       43         5.7.2       Interrupt Transfer Direction       43         5.7.3       Interrupt Transfer Packet Size Constraints       43         5.7.4       Interrupt Transfer Bus Access Constraints       44         5.7.5       Interrupt Transfer Data Sequences       46         5.8       Bulk Transfer Data Sequences       46         5.8.1       Bulk Transfer Data Format       47         5.8.2       Bulk Transfer Data Format       47                                                                                                                                                                                                                                                                                                                                                        | 5.5.4  |                                               |   |

| 5.6.1Isochronous Transfer Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.5.5  | Control Transfer Data Sequences40             | ) |

| 5.6.1Isochronous Transfer Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.6 I  | sochronous Transfers4                         | l |

| 5.6.2Isochronous Transfer Direction415.6.3Isochronous Transfer Packet Size Constraints415.6.4Isochronous Transfer Bus Access Constraints425.6.5Isochronous Transfer Data Sequences435.7Interrupt Transfers435.7.1Interrupt Transfer Data Format435.7.2Interrupt Transfer Direction435.7.3Interrupt Transfer Packet Size Constraints435.7.4Interrupt Transfer Bus Access Constraints445.7.5Interrupt Transfer Data Sequences465.8Bulk Transfer Data Format475.8.1Bulk Transfer Data Format475.8.2Bulk Transfer Direction47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                               |   |

| 5.6.4Isochronous Transfer Bus Access Constraints425.6.5Isochronous Transfer Data Sequences435.7Interrupt Transfers435.7.1Interrupt Transfer Data Format435.7.2Interrupt Transfer Direction435.7.3Interrupt Transfer Packet Size Constraints435.7.4Interrupt Transfer Bus Access Constraints435.7.5Interrupt Transfer Data Sequences445.7.6Interrupt Transfer Data Sequences465.8Bulk Transfer Data Format475.8.1Bulk Transfer Data Format475.8.2Bulk Transfer Direction47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.6.2  | Isochronous Transfer Direction4               | 1 |

| 5.6.5Isochronous Transfer Data Sequences.435.7Interrupt Transfers435.7.1Interrupt Transfer Data Format435.7.2Interrupt Transfer Direction435.7.3Interrupt Transfer Packet Size Constraints435.7.4Interrupt Transfer Bus Access Constraints445.7.5Interrupt Transfer Data Sequences465.8Bulk Transfer Data Format475.8.1Bulk Transfer Data Format47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.6.3  | Isochronous Transfer Packet Size Constraints  | 1 |

| 5.6.5Isochronous Transfer Data Sequences.435.7Interrupt Transfers435.7.1Interrupt Transfer Data Format435.7.2Interrupt Transfer Direction435.7.3Interrupt Transfer Packet Size Constraints435.7.4Interrupt Transfer Bus Access Constraints445.7.5Interrupt Transfer Data Sequences465.8Bulk Transfer Data Format475.8.1Bulk Transfer Data Format47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.6.4  | Isochronous Transfer Bus Access Constraints42 | 2 |

| 5.7.1       Interrupt Transfer Data Format       43         5.7.2       Interrupt Transfer Direction       43         5.7.3       Interrupt Transfer Packet Size Constraints       43         5.7.4       Interrupt Transfer Bus Access Constraints       44         5.7.5       Interrupt Transfer Data Sequences       46 <b>5.8</b> Bulk Transfer Data Format       47         5.8.1       Bulk Transfer Direction       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.6.5  |                                               |   |

| 5.7.1       Interrupt Transfer Data Format       43         5.7.2       Interrupt Transfer Direction       43         5.7.3       Interrupt Transfer Packet Size Constraints       43         5.7.4       Interrupt Transfer Bus Access Constraints       44         5.7.5       Interrupt Transfer Data Sequences       46         5.8       Bulk Transfer Data Format       47         5.8.1       Bulk Transfer Direction       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.7 I  | nterrunt Transfers                            | 3 |

| 5.7.2       Interrupt Transfer Direction       43         5.7.3       Interrupt Transfer Packet Size Constraints       43         5.7.4       Interrupt Transfer Bus Access Constraints       44         5.7.5       Interrupt Transfer Data Sequences       46         5.8       Bulk Transfer Data Format       47         5.8.1       Bulk Transfer Direction       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | Interrunt Transfer Data Format                | 3 |

| 5.7.3       Interrupt Transfer Packet Size Constraints       43         5.7.4       Interrupt Transfer Bus Access Constraints       44         5.7.5       Interrupt Transfer Data Sequences       46         5.8       Bulk Transfer Data Format       47         5.8.1       Bulk Transfer Direction       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | Interrupt Transfer Direction                  | 3 |

| 5.7.4       Interrupt Transfer Bus Access Constraints       44         5.7.5       Interrupt Transfer Data Sequences       46         5.8       Bulk Transfer Data Format       46         5.8.1       Bulk Transfer Data Format       47         5.8.2       Bulk Transfer Direction       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | Interrupt Transfer Packet Size Constraints    | 3 |

| 5.7.5       Interrupt Transfer Data Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | Interrupt Transfer Bus Access Constraints     | 4 |

| 5.8.1Bulk Transfer Data Format475.8.2Bulk Transfer Direction47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | Interrupt Transfer Data Sequences             | 5 |

| 5.8.1Bulk Transfer Data Format475.8.2Bulk Transfer Direction47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.8 1  | Rulk Transfers4                               | 6 |

| 5.8.2 Bulk Transfer Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                                               |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                               |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                               |   |

| 5.8.4   | Bulk Transfer Bus Access Constraints                        |

|---------|-------------------------------------------------------------|

| 5.8.5   | Bulk Transfer Data Sequences                                |

|         |                                                             |

|         | us Access for Transfers49                                   |

| 5.9.1   | Transfer Management                                         |

| 5.9.2   | Transaction Tracking                                        |

| 5.9.3   | Calculating Bus Transaction Times                           |

| 5.9.4   | Calculating Buffer Sizes in Functions and Software55        |

| 5.9.5   | Bus Bandwidth Reclamation                                   |

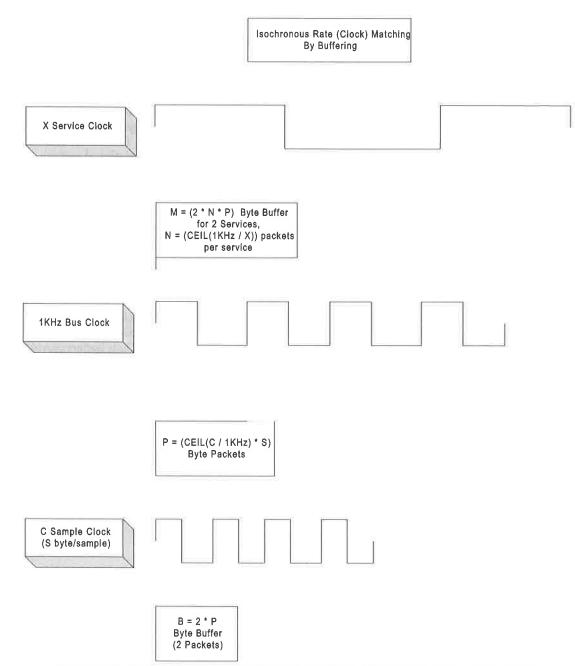

| 5.10 Sp | Decial Considerations for Isochronous Transfers             |

| 5.10.1  | Example Non-USB Isochronous Application                     |

| 5.10.2  | USB Clock Model                                             |

| 5.10.3  | Clock Synchronization61                                     |

| 5.10.4  |                                                             |

| 5.10.5  |                                                             |

| 5.10.6  |                                                             |

| 5.10.7  | Error Handling70                                            |

| 5.10.8  | Buffering for Rate Matching                                 |

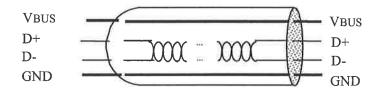

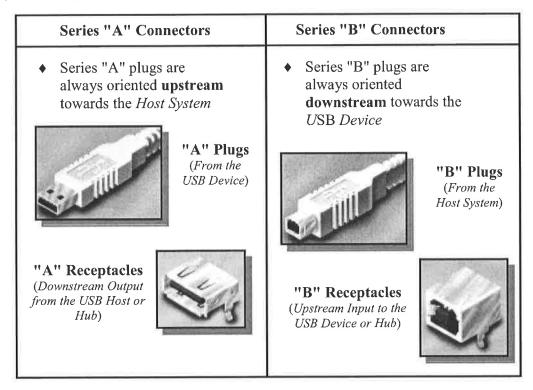

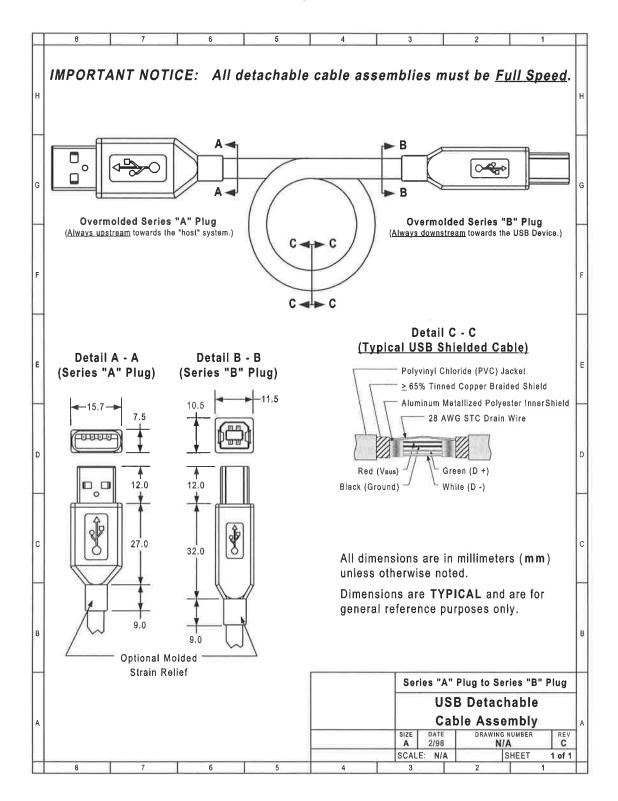

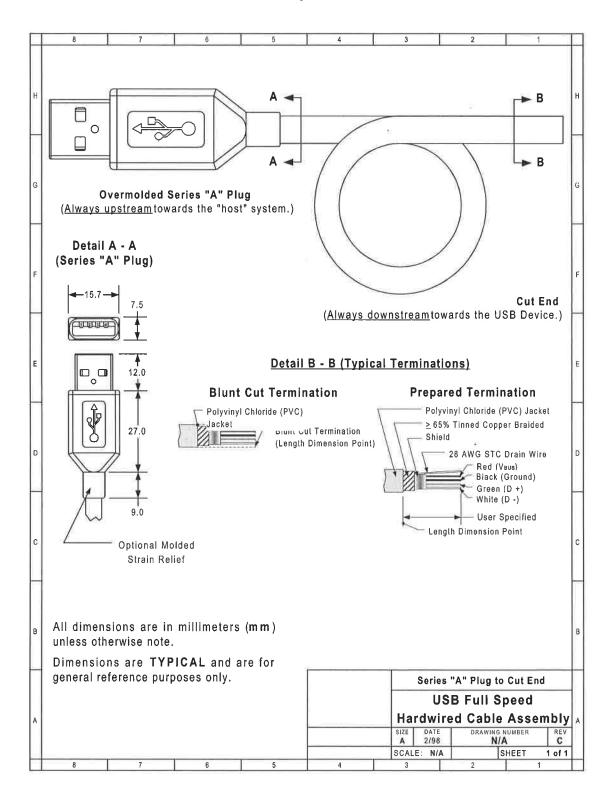

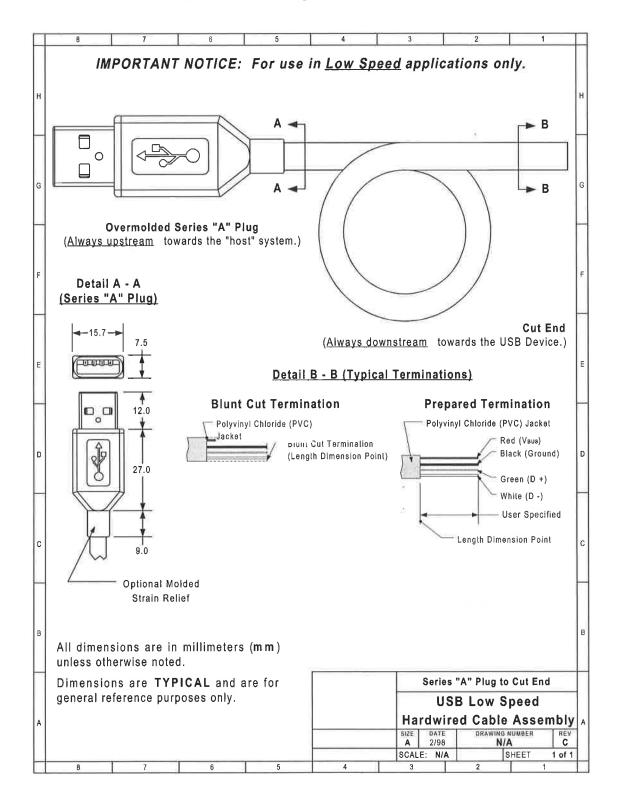

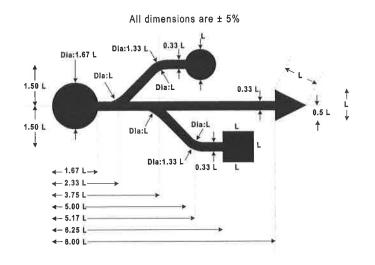

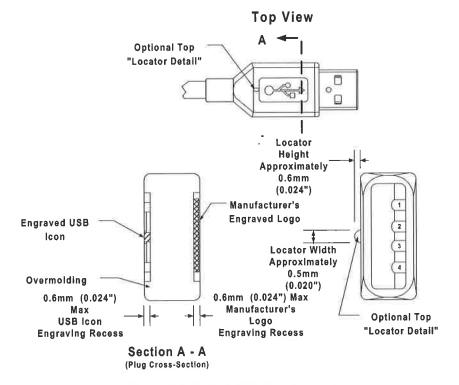

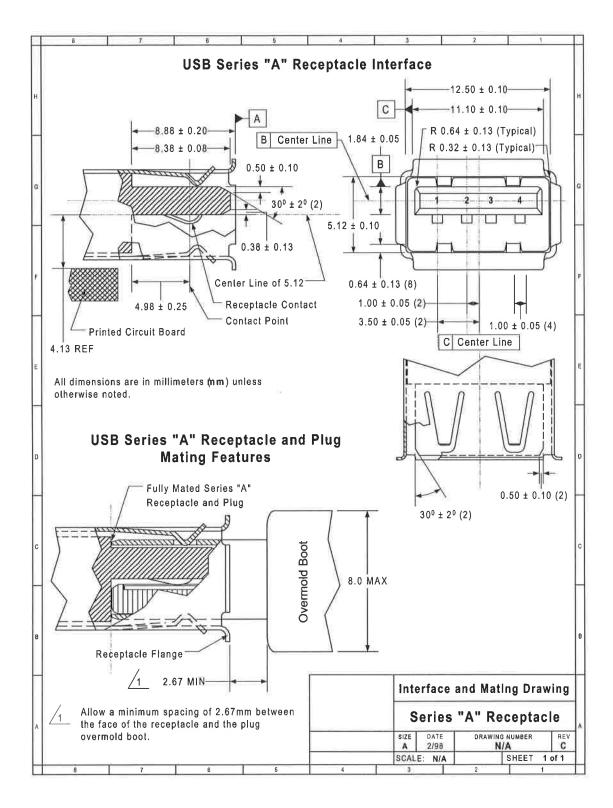

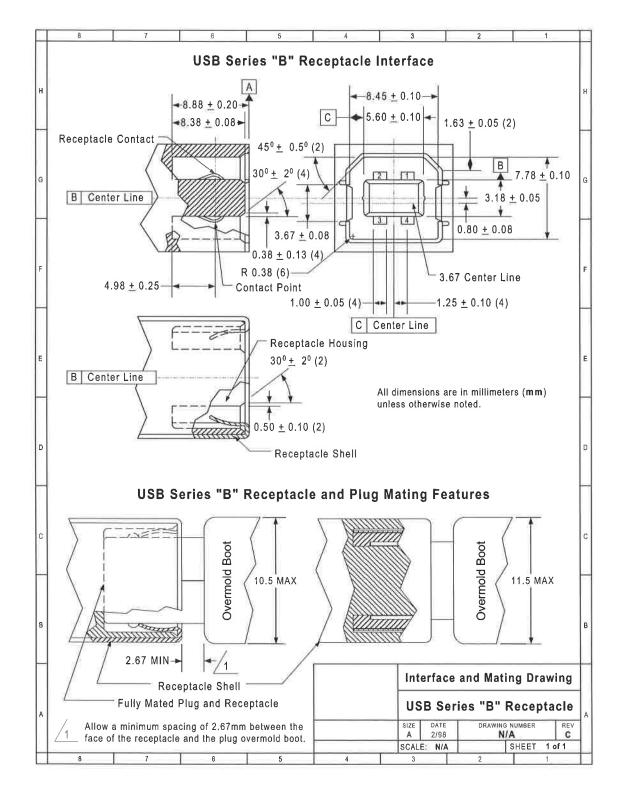

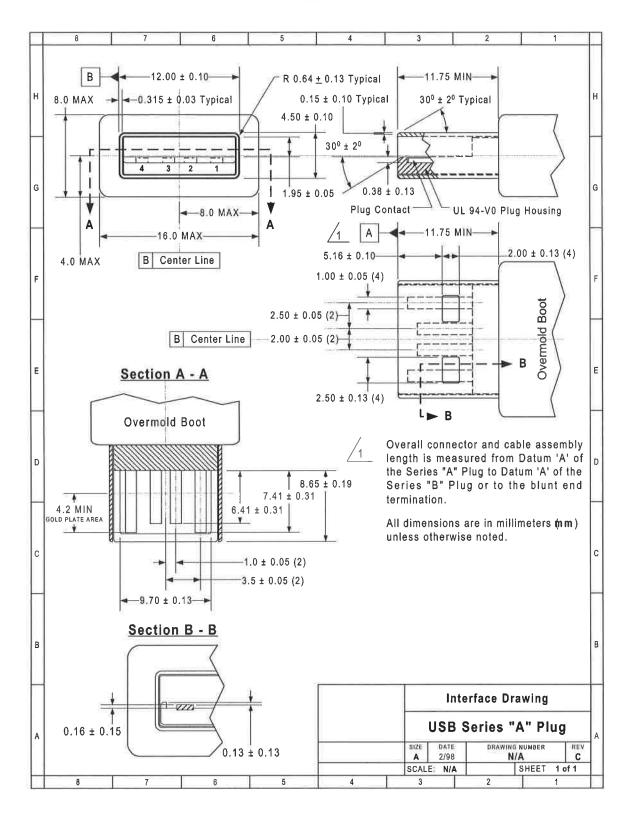

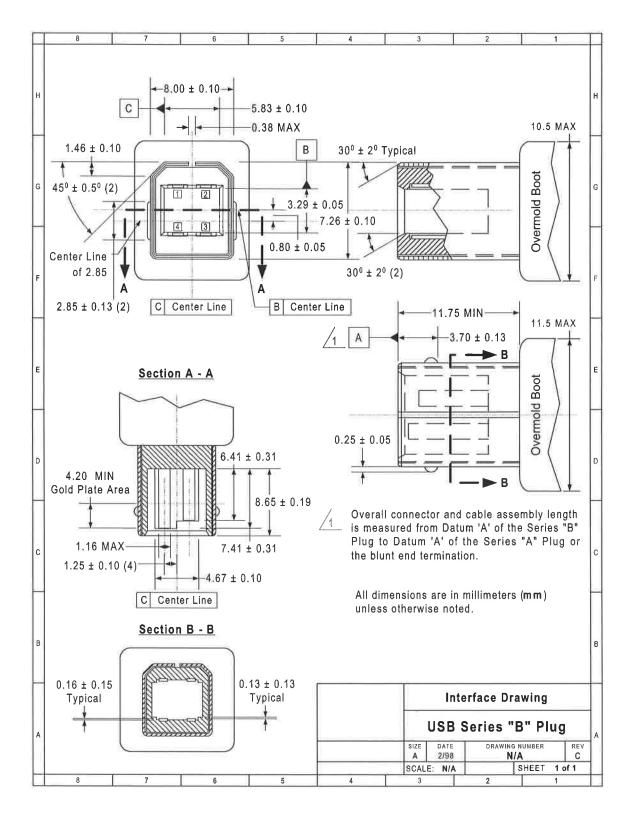

| CHAPTE  | ER 6 MECHANICAL73                                           |

| 6.1 A   | rchitectural Overview73                                     |

| 6.2 K   | eyed Connector Protocol                                     |

| 0.2 K   | eyeu Connector Protocol                                     |

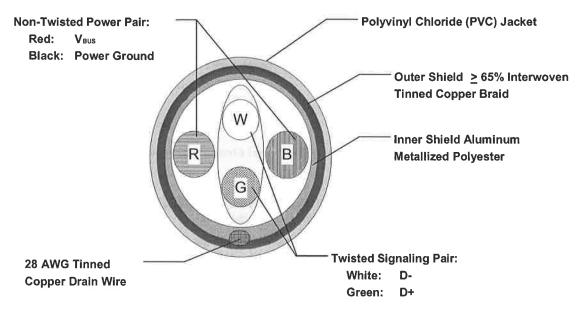

| 6.3 Ca  | able74                                                      |

| 6.4 Ca  | able Assembly74                                             |

| 6.4.1   | Detachable Cable Assemblies                                 |

| 6.4.2   | Full-speed Captive Cable Assemblies                         |

| 6.4.3   | Low-speed Captive Cable Assemblies                          |

| 6.4.4   | Prohibited Cable Assemblies                                 |

|         |                                                             |

| 6.5 Co  | onnector Mechanical Configuration and Material Requirements |

| 6.5.1   | USB Icon Location                                           |

| 6.5.2   | USB Connector Termination Data                              |

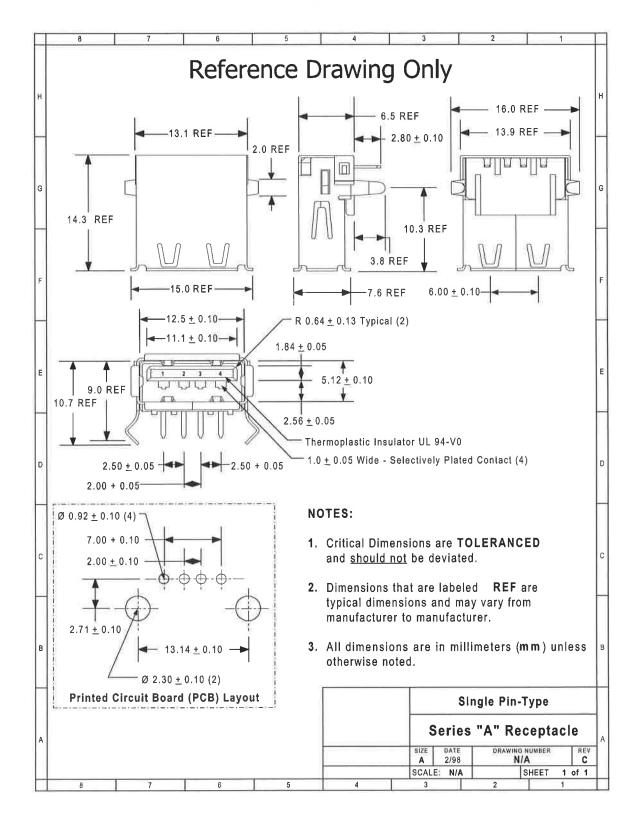

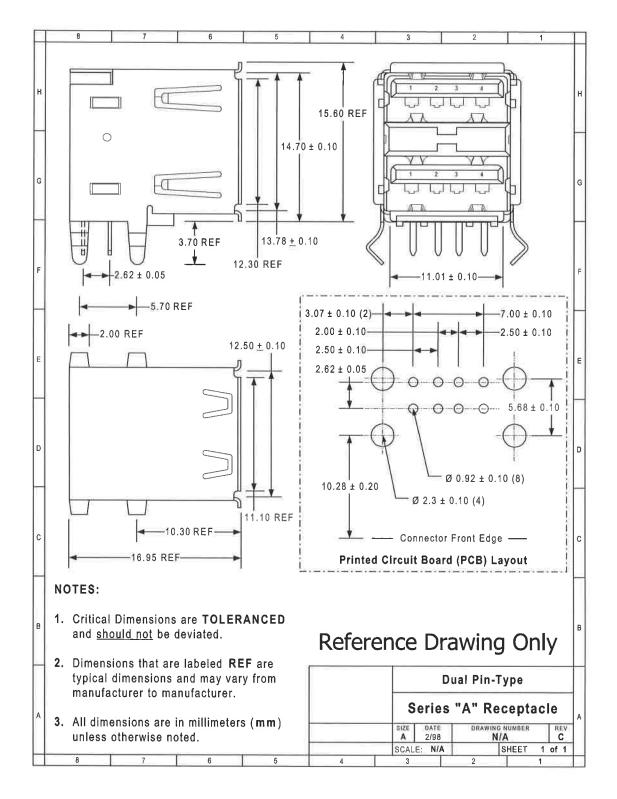

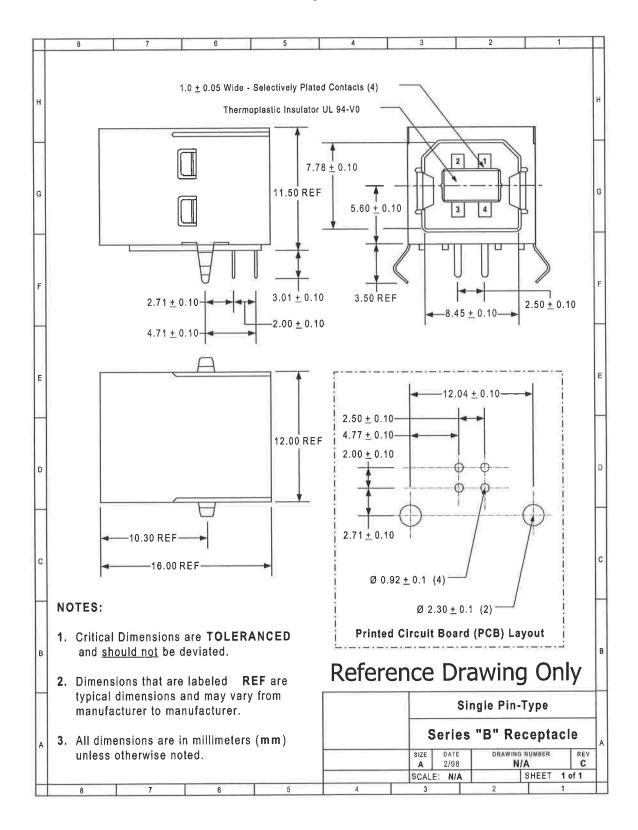

| 6.5.3   | Series "A" and Series "B" Receptacles                       |

| 6.5.4   | Series "A" and Series "B" Plugs                             |

| 6.6 Ca  | able Mechanical Configuration and Material Requirements     |

| 6.6.1   | Description                                                 |

| 6.6.2   | Construction                                                |

| 6.6.3   | Electrical Characteristics                                  |

| 6.6.4   | Cable Environmental Characteristics                         |

| 6.6.5   | Listing94                                                   |

| 6.7 El  | ectrical, Mechanical and Environmental Compliance Standards |

| 6.7.1   | Applicable Documents                                        |

| 6.8 US  | SB Grounding                                                |

|         | 8                                                           |

| 6.9 PC  | CB Reference Drawings102                                    |

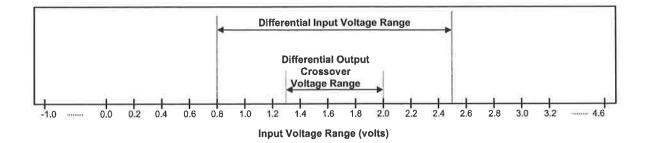

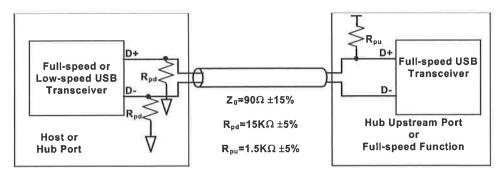

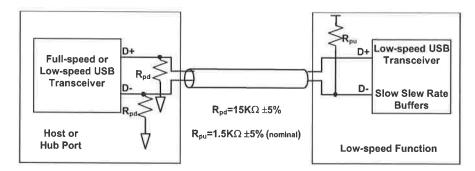

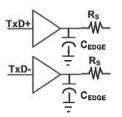

| CHAPTE  | R 7 ELECTRICAL                               | 107  |

|---------|----------------------------------------------|------|

| 7.1 Sig | naling                                       |      |

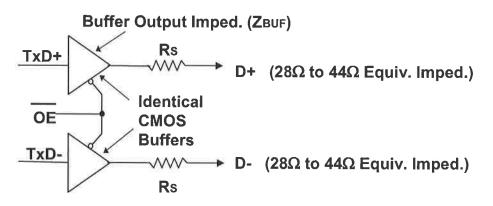

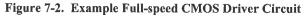

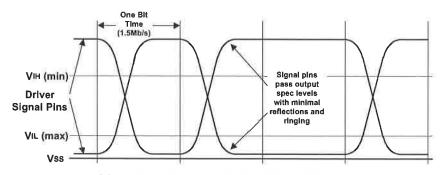

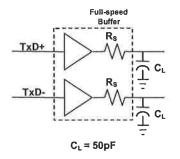

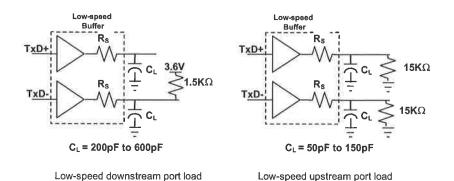

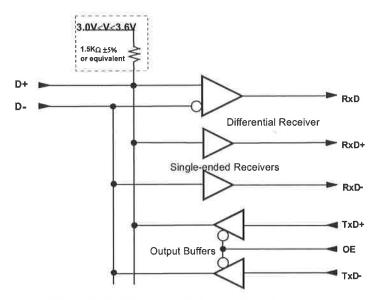

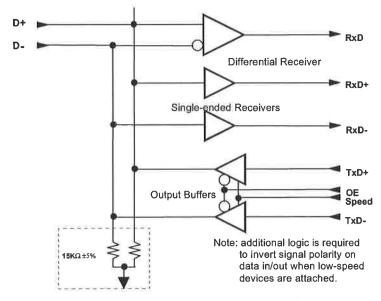

| 7.1.1   | USB Driver Characteristics                   |      |

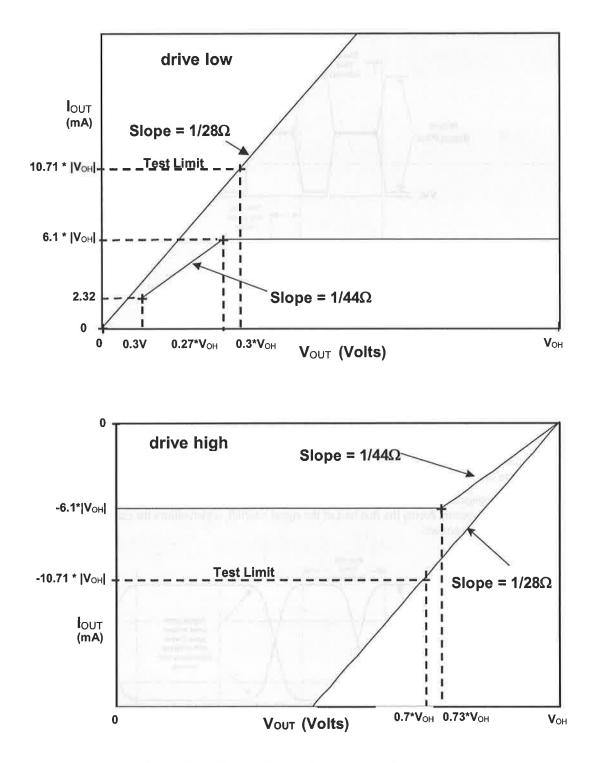

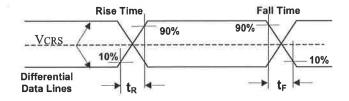

| 7.1.2   | Data Signal Rise and Fall                    |      |

| 7.1.3   | Cable Skew                                   |      |

| 7.1.4   | Receiver Characteristics                     |      |

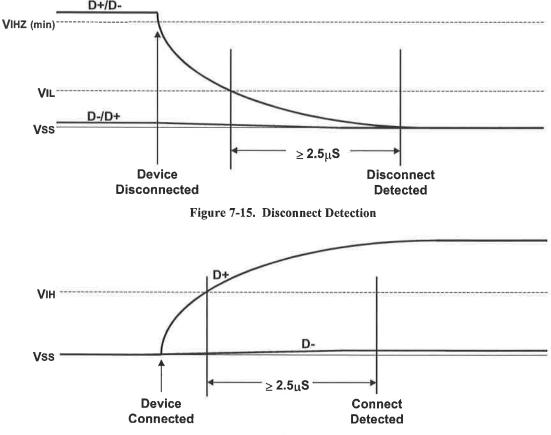

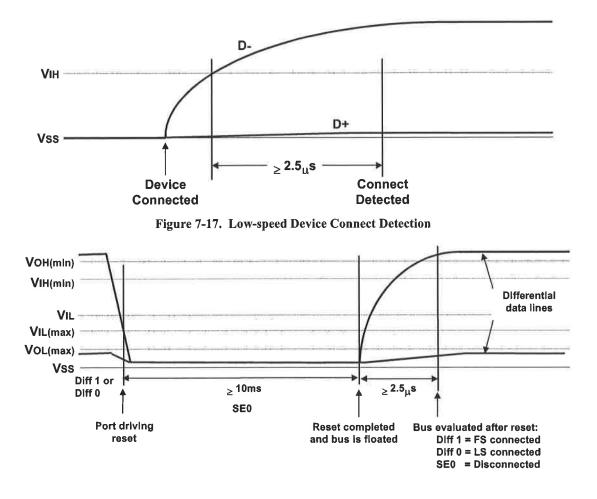

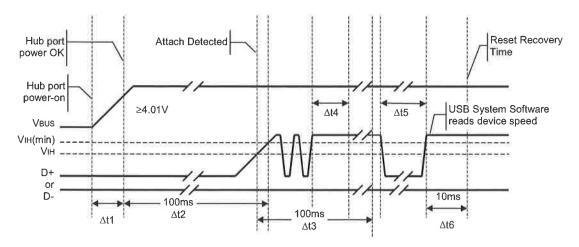

| 7.1.5   | Device Speed Identification                  |      |

| 7.1.6   | Input Characteristics                        |      |

| 7.1.7   | Signaling Levels                             |      |

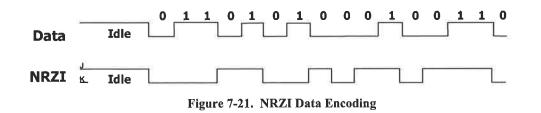

| 7.1.8   | Data Encoding/Decoding                       |      |

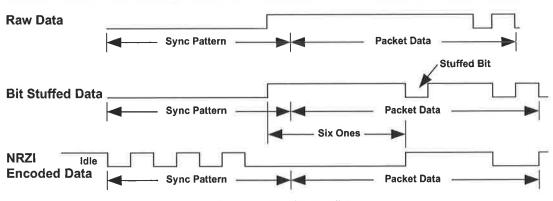

| 7.1.9   | Bit Stuffing                                 |      |

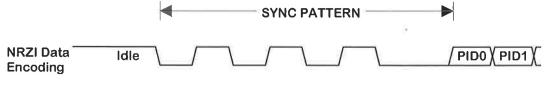

| 7.1.10  | Sync Pattern                                 |      |

| 7.1.11  | Data Signaling Rate                          |      |

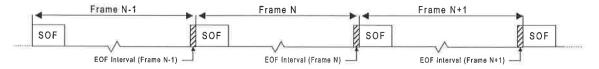

| 7.1.12  | Frame Interval and Frame Interval Adjustment |      |

| 7.1.13  | Data Source Signaling                        |      |

| 7.1.14  | Hub Signaling Timings                        |      |

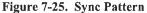

| 7.1.15  | Receiver Data Jitter                         |      |

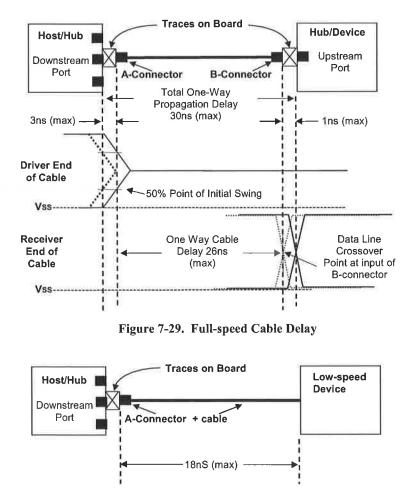

| 7.1.16  | Cable Delay                                  |      |

| 7.1.17  | Cable Attenuation                            |      |

| 7.1.18  | Bus Turn-around Time and Inter-packet Delay  |      |

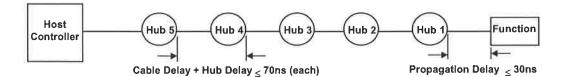

| 7.1.19  | Maximum End-to-end Signal Delay              |      |

|         |                                              |      |

|         | wer Distribution                             |      |

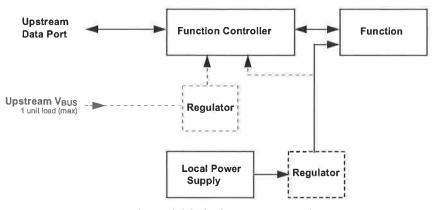

| 7.2.1   | Classes of Devices                           |      |

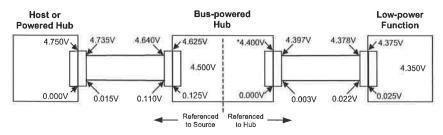

| 7.2.2   | Voltage Drop Budget                          |      |

| 7.2.3   | Power Control During Suspend/Resume          |      |

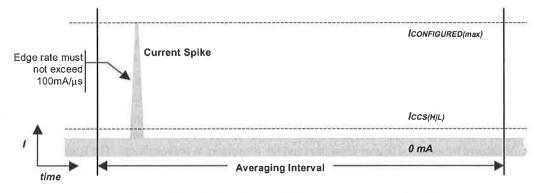

| 7.2.4   | Dynamic Attach and Detach                    |      |

| 7.3 Ph  | ysical Layer                                 |      |

| 7.3.1   | Regulatory Requirements                      | 142  |

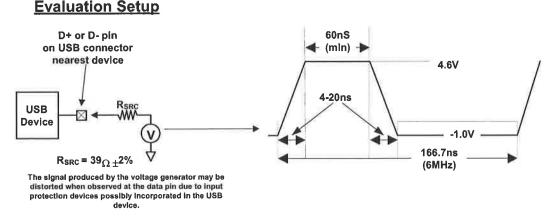

| 7.3.2   | Bus Timing/Electrical Characteristics        | 142  |

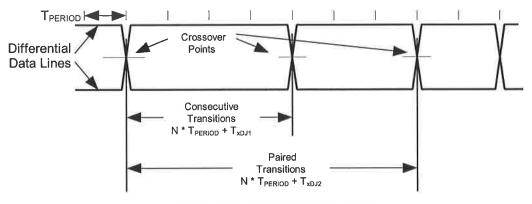

| 7.3.3   | Timing Waveforms                             |      |

|         |                                              |      |

| CHAPTE  | R 8 PROTOCOL LAYER                           | 155  |

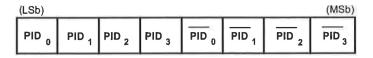

| 8.1 Bi  | t Ordering                                   | 155  |

| 8.2 SY  | NC Field                                     | 155  |

| 8.3 Pa  | cket Field Formats                           |      |

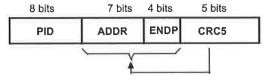

| 8.3.1   | Packet Identifier Field                      |      |

| 8.3.2   | Address Fields                               |      |

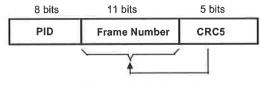

| 8.3.3   | Frame Number Field                           |      |

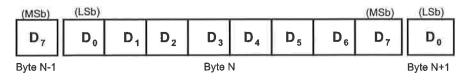

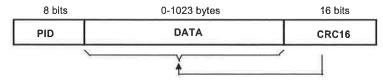

| 8.3.4   | Data Field                                   |      |

| 8.3.5   | Cyclic Redundancy Checks                     |      |

|         |                                              | 4.50 |

|         | cket Formats                                 |      |

| 8.4.1   | Token Packets                                |      |

| 8.4.2   | Start-of-Frame Packets                       |      |

| 8.4.3   | Data Packets                                 |      |

| 8.4.4   | Handshake Packets                            |      |

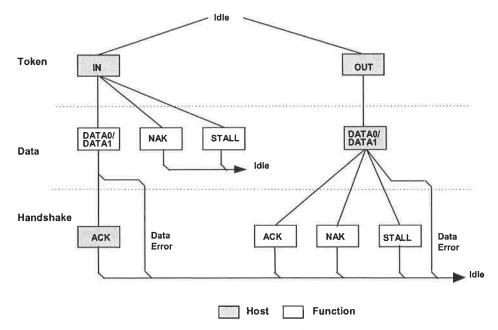

| 8.4.5   | Handshake Responses                          | 161  |

| 8.5 Tı         | ansaction Formats                    |                           |

|----------------|--------------------------------------|---------------------------|

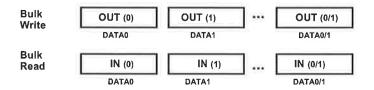

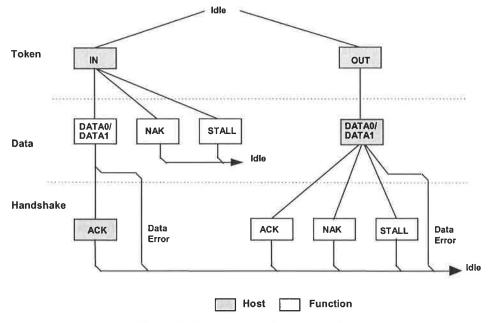

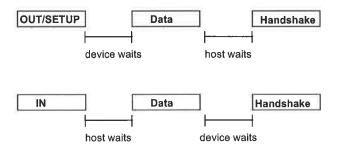

| 8.5.1          | Bulk Transactions                    |                           |

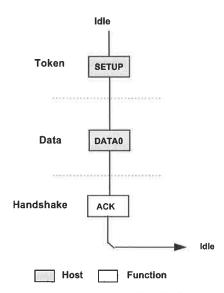

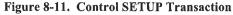

| 8.5.2          | Control Transfers                    |                           |

| 8.5.3          | Interrupt Transactions               |                           |

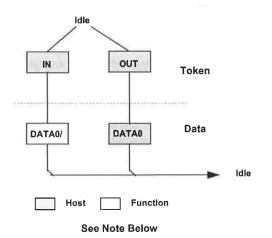

| 8.5.4          | Isochronous Transactions             | 168                       |

|                |                                      |                           |

|                | ta Toggle Synchronization and Retry  | 168                       |

| 8.6.1          | Initialization via SETUP Token       |                           |

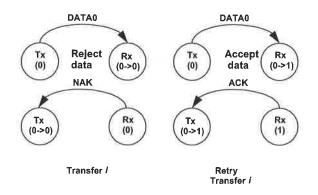

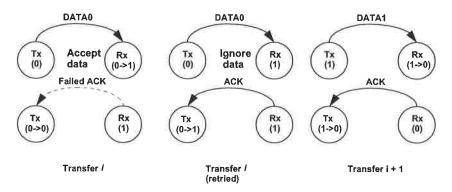

| 8.6.2          | Successful Data Transactions         |                           |

| 8.6.3          | Data Corrupted or Not Accepted       | 170                       |

| 8.6.4          | Corrupted ACK Handshake              | 170                       |

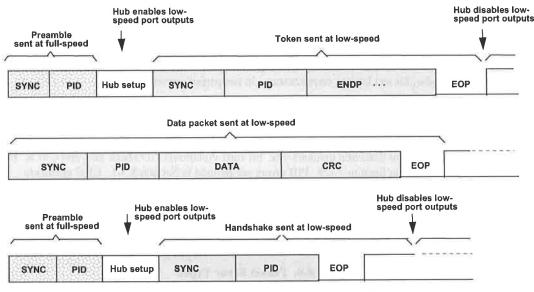

| 8.6.5          | Low-speed Transactions               |                           |

| 8.7 Er         | ror Detection and Recovery           | 173                       |

| 8.7.1          | Packet Error Categories              |                           |

| 8.7.2          | Bus Turn-around Timing               |                           |

| 8.7.3          | False EOPs                           | 172                       |

| 8.7.4          | Babble and Loss of Activity Recovery |                           |

| 0.7.4          | Dabble and Loss of Activity Recovery |                           |

|                |                                      | 475                       |

| CHAPTE         | R 9 USB DEVICE FRAMEWORK             |                           |

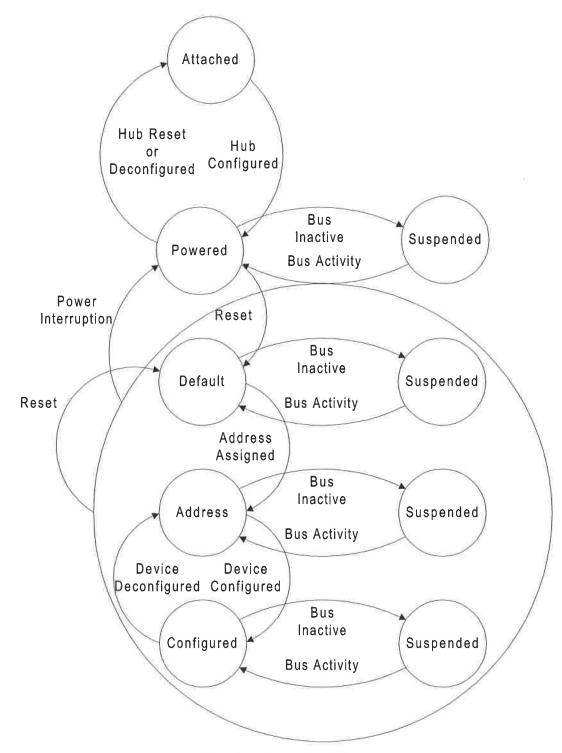

| 9.1 US         | BB Device States                     |                           |

| 9.1.1          | Visible Device States                |                           |

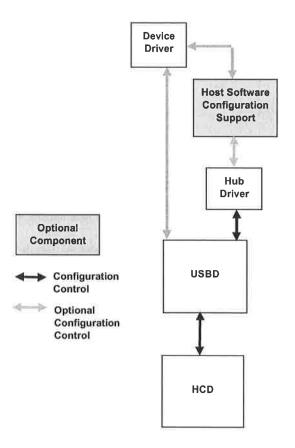

| 9.1.2          | Bus Enumeration                      |                           |

|                |                                      |                           |

| 9.2 Ge         | eneric USB Device Operations         |                           |

| 9.2.1          | Dynamic Attachment and Removal       |                           |

| 9.2.2          | Address Assignment                   |                           |

| 9.2.3          | Configuration                        |                           |

| 9.2.4          | Data Transfer                        |                           |

| 9.2.5          | Power Management                     |                           |

| 9.2.6          | Request Processing                   |                           |

| 9.2.7          | Request Error                        |                           |

| 9.3 US         | D Davies Desurate                    | 103                       |

| 9.3 08         | B Device Requests                    |                           |

| 9.3.1          | bmRequestType                        |                           |

| 9.3.2          | bRequest                             |                           |

| 9.3.3<br>9.3.4 | wValue                               |                           |

| 9.3.4          | wIndex                               |                           |

| 9.3.3          | wLength                              | 184                       |

| 9.4 St         | andard Device Requests               |                           |

| 9.4.1          | Clear Feature                        |                           |

| 9.4.2          | Get Configuration                    |                           |

| 9.4.3          | Get Descriptor                       |                           |

| 9.4.4          | Get Interface                        |                           |

| 9.4.5          | Get Status                           |                           |

| 9.4.6          | Set Address                          |                           |

| 9.4.7          | Set Configuration                    |                           |

| 9.4.8          | Set Descriptor                       |                           |

| 9.4.9          | Set Feature                          |                           |

| 9.4.10         | Set Interface                        |                           |

| 9.4.11         | Synch Frame                          |                           |

|                |                                      | www.wildeszecowwilden.ch/ |

| 9.5 De         | scriptors                            |                           |