# P GVCRR EXHIBIT 1002 PART 4

Ċ

#### -114-

uP Data 0-7, uP Data P, uPAdd 0-2, CS

These signals are used by a microprocessor to address the programmable registers within the chip. The odd parity signal uP Data P is only checked when data is written to the Fifo Data or Checksum Registers and microprocessor parity is enabled.

Clk

5

10

15

20

The clock input is used to generate some of the chip timing. It is expected to be in the 10-20 Mhz range.

Read En, Write En

••

During microprocessor accesses, while CS is true, these signals determine the direction of the microprocessor accesses. During data transfers in the WD mode these signals are data strobes used in conjunction with Port A Ack.

Port B 00-07, 10-17, 20-27, 30-37, 0P-3P

Port B is a 32 bit data port. There is one odd parity bit for each byte. Port B OP is the parity of bits 00-07, PortB 1P is the parity of bits 10-17, Port B 2P is the parity of bits 20-27, and Port B 3P is the parity of bits 30-37.

Attorney Docket No.: AUSP7209 . WP1/WSW/AUSP/7209.001

8/24/89-7

. . . . . .

(

B Select, B Req, B Ack, Parity Sync, B Output Enable

These signals are used in the data transfer mode to control the handshake of data on Port B. Port B Req and Port B Ack are both gated with Port B Select. The Port B Ack signal is used to strobe the data on the Port B data lines. The parity sync signal is used to indicate to a chip configured as the parity chip to indicate that the last words of data involved in the parity accumulation are on Port B. The Port B data lines will only be driven by the Fifo chip if all of the following conditions are met:

a. the data transfer is from Port A to Port B;

b. the Port B select signal is true;

c. the Port B output enable signal is true; and

i

d. the chip is not configured as the parity chip or it is in parity correct mode and the Parity Sync signal is true.

Reset

This signal resets all the registers within the chip and causes all bidirectional pins to be in a high impedance state.

#### DESCRIPTION OF OPERATION

Normal Operation. Normally the chip acts as a simple FIFO chip. A FIFO is simulated by using two RAM buffers in a simple ping-pong mode. It is intended, but not mandatory, that data is burst into or out of

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

. . . . . . . . . . . .

8/24/89-7

NetApp Ex. 1002, pg. 602

15

10

5

25

#### -116-

the FIFO on Port B. This is done by holding Port B Sel signal low and pulsing the Port B Ack signal. When transferring data from Port B to Port A, data is first written into RAM X and when this is full, the data paths will be switched such that Port B may start writing to RAM Y. Meanwhile the chip wills begin emptying RAM X to Port A. When RAM Y is full and RAM X empty the data paths will be switched again such that Port B may reload RAM X and Port A may empty RAM Y.

<u>Port A Slave Mode</u>. This is the default mode and the chip is reset to this condition. In this mode the chip waits for a master such as one of the SCSI adapter chips 542 to raise Port A Request for data transfer. If data is available the Fifo chip will respond with Port A Ack/Rdy.

Port A WD Mode. The chip may be configured to run in the WD or Western Digital mode. In this mode the chip must be configured as a slave on Port A. It differs from the default slave mode in that the chip responds with Read Enable or Write Enable as appropriate together with Port A Ack/Rdy. This mode is intended to allow the chip to be interfaced to the Western Digital 33C93A SCSI chip or the NCR 53C90 SCSI chip.

25

5

10

15

20

:

<u>Port A Master Mode</u>. When the chip is configured as a master, it will raise Port A Ack/Rdy when it is

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

-117-

(

ready for data transfer. This signal is expected to be tied to the Request input of a DMA controller which will respond with Port A Req when data is available. In order to allow the DMA controller to burst, the Port A Ack/Rdy signal will only be negated after every 8 or 16 bytes transferred.

Port B Parallel Write Mode. In parallel write mode, the chip is configured to be the parity chip for a parallel transfer from Port B to Port A. In this mode, when Port B Select and Port B Request are asserted, data is written into RAM X or RAM Y each time the Port B Ack signal is received. For the first block of 128 bytes data is simply copied into the selected RAM. The next 128 bytes driven on Port B will be exclusive-ORed with the first 128 bytes. This procedure will be repeated for all drives such that the parity is accumulated in this chip. The Parity Sync signal should be asserted to the parallel chip together with the last block of 128 bytes. This enables the chip to switch access to the other RAM and start accumulating a new 128 bytes of parity.

<u>Port B Parallel Read Mode - Check Data</u>. This mode is set if all drives are being read and parity is to be checked. In this case the Parity Correct bit in the Data Transfer Configuration Register is not set. The parity chip will first read 128 bytes on Port A as

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

NetApp Ex. 1002, pg. 604

10

5

15

20

-118-

(

• (•

in a normal read mode and then raise Port B Request. While it has this signal asserted the chip will monitor the Port B Ack signals and exclusive-or the data on Port B with the data in its selected RAM. The Parity Sync should again be asserted with the last block of 128 bytes. In this mode the chip will not drive the Port B data lines but will check the output of its exclusive-or logic for zero. If any bits are set at this time a parallel parity error will be flagged.

Port B Parallel Read Mode - Correct Data. This mode is set by setting the Parity Correct bit in the Data Transfer Configuration Register. In this case the chip will work exactly as in the check mode except that when Port B Output Enable, Port B Select and Parity Sync are true the data is driven onto the Port B data lines and a parallel parity check for zero is not performed.

Byte Swap. In the normal mode it is expected that Port B bits 00-07 are the first byte, bits 10-17 the second byte, bits 20-27 the third byte, and bits 30-37 the last byte of each word. The order of these bytes may be changed by writing to the byte swap bits in the configuration register such that the byte address bits are inverted. The way the bytes are written and read also depend on whether the CPU interface is configured as 16 or 8 bits. The following

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

10

15

20

5

ł

table shows the byte alignments for the different possibilities for data transfer using the Port A Request / Acknowledge handshake:

| 5  | CPU<br>I/F | Invert<br>Addr 1 | Invert<br>Addr O | Port B<br>00-07  | Port B<br>10-17  | Port B<br>20-27  | Port B<br>30-37  |

|----|------------|------------------|------------------|------------------|------------------|------------------|------------------|

|    | 8          | False            | False            | Port A<br>byte O | Port A<br>byte 1 | Port A<br>byte 2 | Port A<br>byte l |

| 10 | 8          | False            | True             | Port A<br>byte l | Port A<br>byte O | Port A<br>byte 3 | Port A<br>byte 2 |

|    | 8          | True             | False            | Port A<br>byte 2 | Port A<br>byte 3 | Port A<br>byte O | Port A<br>byte l |

|    | 8          | True             | True             | Port A<br>byte 3 | Port A<br>byte 2 | Port A<br>byte l | Port A<br>byte O |

| 15 | 16         | False            | False            | Port A<br>byte O | uProc<br>byte O  | Port A<br>byte l | uProc<br>byte l  |

| •  | 16         | False            | True             | uProc<br>byte O  | Port A<br>byte O | uProc<br>byte 1  | Port A<br>byte 1 |

| 20 | 16         | True             | False            | Port A<br>byte l | uProc<br>byte l  | Port A<br>byte O | uProc<br>byte O  |

|    | 16         | True             | True             | uProc<br>byte 1  | Port A<br>byte l | uProc<br>byte O  | Port A<br>byte O |

When the Fifo is accessed by reading or writing the Fifo Data Register through the microprocessor port in 8 bit mode, the bytes are in the same order as the table above but the uProc data port is used instead of Port A. In 16 bit mode the table above applies.

Odd Length Transfers. If the data transfer is not a multiple of 32 words, or 128 bytes, the microprocessor must manipulate the internal registers of the chip to ensure all data is transferred. Port A Ack and Port B Req are normally not asserted until all Attorney Docket No.:AUSP7209 WP1/WSW/AUSP/7209.001 8/24/89-7

-119-

Œ

.\*

25

-120-

(

(....

32 words of the selected RAM are available. These signals may be forced by writing to the appropriate RAM status bits of the Data Transfer Status Register.

When an odd length transfer has taken place the microprocessor must wait until both ports are quiescent before manipulating any registers. It should then reset both of the Enable Data Transfer bits for Port A and Port B in the Data Transfer Control Register. It must then determine by reading their Address Registers and the RAM Access Control Register whether RAM X or RAM Y holds the odd length data. It should then set the corresponding Address Register to a value of 20 hexadecimal, forcing the RAM full bit and setting the address to the first word. Finally the microprocessor should set the Enable Data Transfer bits to allow the chip to complete the transfer.

At this point the Fifo chip will think that there are now a full 128 bytes of data in the RAM and will transfer 128 bytes if allowed to do so. The fact that some of these 128 bytes are not valid must be recognized externally to the FIFO chip.

#### Attorney Docket No.:AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

10

5

15

20

(

#### Data Transfer Configuration Register (Read/Write)

Register Address 0. This register is cleared by the reset signal.

-121-

$\boldsymbol{\epsilon}$

|          |          | -          |                                                                                                                                                                                                                                                                                              |

|----------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5        | Bit O    | )          | <u>WD Mode</u> . Set if data transfers are to<br>use the Western Digital WD33C93A<br>protocol, otherwise the Adaptec 6250<br>protocol will be used.                                                                                                                                          |

| :-<br>10 | Bit 1    | L          | <u>Parity Chip</u> . Set if this chip is to accumulate Port B parities.                                                                                                                                                                                                                      |

| ·        | Bit 2    | 2 .        | <u>Parity Correct Mode</u> . Set if the<br>parity chip is to correct parallel<br>parity on Port B.                                                                                                                                                                                           |

| 15       | Bit 3    | <b>3</b> . | <u>CPU Interface 16 bits wide</u> . If set,<br>the microprocessor data bits are<br>combined with the Port A data bits to<br>effectively produce a 16 bit Port. All<br>accesses by the microprocessor as well<br>as all data transferred using the Port A                                     |

| 20       | ۲        |            | Request and Acknowledge handshake will transfer 16 bits.                                                                                                                                                                                                                                     |

|          | Bit 4    | 1          | <u>Invert Port A byte address O</u> . Set to<br>invert the least significant bit of<br>Port A byte address.                                                                                                                                                                                  |

| 25       | Bit 5    | 5          | <u>Invert Port A byte address 1</u> . Set to<br>invert the most significant bit of Port<br>A byte address.                                                                                                                                                                                   |

| 30       | Bit 6    | 5 ·        | <u>Checksum Carry Wrap</u> . Set to enable the<br>carry out of the 16 bit checksum adder<br>to carry back into the least significant<br>bit of the adder.                                                                                                                                    |

| 35       | Bit 7    | 7          | <u>Reset</u> . Writing a 1 to this bit will<br>reset the other registers. This bit<br>resets itself after a maximum of 2<br>clock cycles and will therefore normally<br>be read as a 0. No other register<br>should be written for a minimum of 4<br>clock cycles after writing to this bit. |

|          |          |            |                                                                                                                                                                                                                                                                                              |

| Atto     | orney Do | ocke       | t No.: AUSP7209                                                                                                                                                                                                                                                                              |

WP1/WSW/AUSP/7209.001

8/24/89-7

- ....----

#### Data Transfer Control Register (Read/Write)

Register Address 1. This register is cleared by the reset signal or by writing to the reset bit.

- Bit 0 <u>Enable Data Transfer on Port A</u>. Set to enable the Port A Reg/Ack handshake.

- Bit 1 <u>Enable Data Transfer on Port B</u>. Set to enable the Port B Req/Ack handshake.

- Bit 2 Port A to Port B. If set, data transfer is from Port A to Port B. If reset, data transfer is from Port B to Port A. In order to avoid any glitches on the request lines, the state of this bit should not be altered at the same time as the enable data transfer bits 0 or 1 above.

- Bit 3 <u>uProcessor Parity Enable</u>. Set if parity is to be checked on the microprocessor interface. It will only be checked when writing to the Fifo Data Register or reading from the Fifo Data or Checksum Registers, or during a Port A Request/Acknowledge transfer in 16 bit mode. The chip will, however, always re-generate parity ensuring that correct parity is written to the RAM or read on the microprocessor interface.

- Bit 4 <u>Port A Parity Enable</u>. Set if parity is to be checked on Port A. It is checked when accessing the Fifo Data Register in 16 bit mode, or during a Port A Request/Acknowledge transfer. The chip will, however, always re-generate parity ensuring that correct parity is written to the RAM or read on the Port A interface.

- Bit 5 <u>Port B Parity Enable</u>. Set if Port B data has valid byte parities. If it is not set, byte parity is generated internally to the chip when writing to the RAMS. Byte parity is not checked when writing from Port B, but always checked when reading to Port B.

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

#### NetApp Ex. 1002, pg. 609

40

5

10

15

20

25

30

Bit 6 <u>Checksum Enable</u>. Set to enable writing to the 16 bit checksum register. This register accumulates a 16 bit checksum for all RAM accesses, including accesses to the Fifo Data Register, as well as all writes to the checksum register. This bit must be reset before reading from the Checksum Register.

(.

Bit 7 <u>Port A Master</u>. Set if Port A is to operate in the master mode on Port A during the data transfer.

#### Data Transfer Status Register (Read Only)

(

5

10

Register Address 2. This register is cleared by

• the reset signal or by writing to the reset bit.

| 15 | Bit O    | Data in RAM X or RAM Y. Set if any bits<br>are true in the RAM X, RAM Y, or Port A<br>byte address registers.                                                                                                                    |

|----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20 | Bit 1    | <u>uProc Port Parity Error</u> . Set if the<br>uProc Parity Enable bit is set and a<br>parity error is detected on the<br>microprocessor interface during any RAM<br>access or write to the Checksum Register<br>in 16 bit mode. |

| 25 | Bit 2    | <u>Port A Parity Error</u> . Set if the Port A<br>Parity Enable bit is set and a parity<br>error is detected on the Port A<br>interface during any RAM access or write<br>to the Checksum Register.                              |

| 30 | Bit 3    | Port B Parallel Parity Error . Set if<br>the chip is configured as the parity<br>chip, is not in parity correct mode, and<br>a non zero result is detected when the<br>Parity Sync signal is true. It is also                    |

| 35 |          | set whenever data is read out onto Port<br>B and the data being read back through<br>the bidirectional buffer does not<br>compare.                                                                                               |

| 40 | Bits 4-7 | <u>Port B Bytes 0-3 Parity Error</u> . Set<br>whenever the data being read out of the<br>RAMs on the Port B side has bad parity.                                                                                                 |

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

.

8/24/89-7

<del>~</del> .

### -124-

#### Ram Access Control Register (Read/Write)

C

5

10

15

20

2,5

30

35

ł

Register Address 3. This register is cleared by the reset signal or by writing to the reset bit. The Enable Data Transfer bits in the Data Transfer Control Register must be reset before attempting to write to this register, else the write will be ignored.

- Bit 0 <u>Port A byte address 0</u>. This bit is the least significant byte address bit. It is read directly bypassing any inversion done by the invert bit in the Data Transfer Configuration Register.

- Bit 1 <u>Port A byte address 1</u>. This bit is the most significant byte address bit. It is read directly bypassing any inversion done by the invert bit in the Data Transfer Configuration Register.

- Bit 2 <u>Port A to RAM Y</u>. Set if Port A is accessing RAM Y, and reset if it is accessing RAM X.

- Bit 3 <u>Port B to RAM Y</u>. Set if Port B is accessing RAM Y, and reset if it is accessing RAM X.

- Bit 4 Long Burst. If the chip is configured to transfer data on Port A as a master, and this bit is reset, the chip will only negate Port A Ack/Rdy after every 8 bytes, or 4 words in 16 bit mode, have been transferred. If this bit is set, Port A Ack/Rdy will be negated every 16 bytes, or 8 words in 16 bit mode.

- Bits 5-7 Not Used.

#### RAM X Address Register (Read/Write)

Register Address 4. This register is cleared by the reset signal or by writing to the reset bit. The Enable Data Transfer bits in the Data Transfer Control Attorney Docket No.: AUSP7209

WP1/WSW/AUSP/7209.001

8/24/89-7

(:--

Register must be reset before attempting to write to this register, else the write will be ignored.

| Bits 0-4 | RAM X word address |

|----------|--------------------|

| Bit 5    | RAM X full         |

| Bits 6-7 | Not Used           |

#### RAM Y Address Register (Read/Write)

Ċ

Register Address 5. This register is cleared by the reset signal or by writing to the reset bit. The Enable Data Transfer bits in the Data Transfer Control Register must be reset before attempting to write to this register, else the write will be ignored.

| Bits | 0-4 | RAM | Y | word | address |

|------|-----|-----|---|------|---------|

| Bit  | 5   | RAM | Y | full |         |

| Bits |     | Not | U | sed  |         |

15

20

5

10

#### <u>Fifo Data Register (Read/Write)</u>

Register Address 6. The Enable Data Transfer bits in the Data Transfer Control Register must be reset before attempting to write to this register, else the write will be ignored. The Port A to Port B bit in the Data Transfer Control register must also be set before writing this register. If it is not, the RAM controls will be incremented but no data will be written to the RAM. For consistency, the Port A to PortB should be reset prior to reading this register.

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

#### -126-

(

Bits 0-7 are Fifo Data. The microprocessor may access the FIFO by reading or writing this register. The RAM control registers are updated as if the access was using Port A. If the chip is configured with a 16 bit CPU Interface the most significant byte will use the Port A 0-7 data lines, and each Port A access will increment the Port A byte address by 2.

#### Port A Checksum Register (Read/Write)

(

5

10

15

20

.

Register Address 7. This register is cleared by the reset signal or by writing to the reset bit.

Bits 0-7 are Checksum Data. The chip will accumulate a 16 bit checksum for all Port A accesses. If the chip is configured with a 16 bit CPU interface, the most significant byte is read on the Port A 0-7 data lines. If data is written directly to this register it is added to the current contents rather than overwriting them. It is important to note that the Checksum Enable bit in the Data Transfer Control Register must be set to write this register and reset to read it.

#### PROGRAMMING THE FIFO CHIP

In general the fifo chip is programmed by writing to the data transfer configuration and control registers to enable a data transfer, and by reading

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

(

(::

the data transfer status register at the end of the transfer to check the completion status. Usually the data transfer itself will take place with both the Port A and the Port B handshakes enabled, and in this case the data transfer itself should be done without any other microprocessor interaction. In some applications, however, the Port A handshake may not be enabled, and it will be necessary for the microprocessor to fill or empty the fifo by repeatedly writing or reading the Fifo Data Register.

Since the fifo chip has no knowledge of any byte counts, there is no way of telling when any data transfer is complete by reading any register within this chip itself. Determination of whether the data transfer has been completed must therefore be done by some other circuitry outside this chip.

The following C language routines illustrate how the parity FIFO chip may be programmed. The routines assume that both Port A and the microprocessor port are connected to the system microprocessor, and return a size code of 16 bits, but that the hardware addresses the Fifo chip as long 32 bit registers.

#### Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

10

5

15

-128-

(:

struct FIFO regs { unsigned char config, al, a2, a3; unsigned char control, b1, b2, b3; unsigned char status, c1, c2, c3; 5 unsigned char ram\_access\_control,d1,d2,d3; unsigned char ram\_X\_addr,el,e2,e3; unsigned char ram\_Y\_addr,f1,f2,f3; unsigned long data; unsigned int checksum, hl; 10 ); #define FIFO1 ((struct FIFO\_regs\*) FIFO\_BASE\_ADDRESS) #define FIFO\_RESET 0x80 #define FIFO\_16\_BITS 0x08 #define FIFO\_CARRY\_WRAP 0x40 15 #define FIFO\_PORT\_A\_ENABLE 0x01 #define FIFO\_PORT\_B\_ENABLE 0x02 #define FIFO\_PORT\_ENABLES 0x03 #define FIFO\_PORT\_A\_TO\_B 0x04 #define FIFO\_CHECKSUM\_ENABLE 0x40 20 #define FIFO\_DATA\_IN\_RAM 0x01 #define FIFO\_FORCE\_RAM\_FULL 0x20 #define PORT\_A\_TO\_PORT\_B(fifo) ((fifo-> control ) & 0x04) #define PORT\_A\_BYTE\_ADDRESS(fifo) ((fifo->ram\_access\_control) & 0x03) 25 #define PORT\_A\_TO\_RAM\_Y(fifo) ((fifo->ram\_access\_control ) & 0x04) #define PORT\_B\_TO\_RAM\_Y(fifo) ((fifo-> ram\_access\_control ) & (80x0 The following routine initiates a Fifo data transfer using 30 two values passed to it. config\_data This is the data to be written to the configuration register. control\_data This is the data to be written to the Data 35 Transfer Control Register. If the data transfer is to take place automatically using both the Port Aand Port B handshakes, both data transfer enables bits should be set in this parameter. 40 FIFO\_initiate\_data\_transfer(config\_data, control\_data) unsigned char config\_data, control\_data; £ FIFO1->config = config\_data { FIFO\_RESET; /\* Set Configuration value & Reset \*/ Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001 8/24/89-7

-129-FIFO1->control = control\_data & ("FIFO\_PORT\_ENABLES); /\* Set everything but enables \*/ FIFO1->control = control\_data ; /\* Set data transfer enables \*/ } /\*\*\*\* The following routine forces the transfer of any odd bytes that have been left in the Fifo at the end of a data transfer. It first disables both ports, then forces the Ram Full bits, and then re-enables the appropriate Port. \*\*\*\*\*\*\* FIFO\_force\_odd\_length\_transfer() ( FIFO1->control &= ~FIFO\_PORT\_ENABLES; /\* Disable Ports A & B \*/ if (PORT\_A\_TO\_PORT\_B(FIFO1)) { if (PORT A TO RAM Y(FIFO1)) { PIFO1->ram\_Y\_addr = FIFO\_FORCE\_RAM\_FULL; /\* Set RAM Y full \*/ 3 else FIFO1->ram\_X\_addr = FIFO\_FORCE\_RAM\_FULL ; /\* Set RAM X full \*/ FIFO1->control |= FIFO\_PORT\_B\_ENABLE ; /\* Re-Enable Port B \*/ } else { if (PORT\_B\_TO\_RAM\_Y(FIFO1)) { FIFO1->ram Y addr = FIFO FORCE RAM FULL ; /\* Set RAM Y full ≈/ } else FIFO1->ram\_X\_addr = FIFO\_FORCE\_RAM\_FULL ; /\* Set RAM X full \*/ FIFO1->control := FIFO\_PORT\_A\_ENABLE ; /☆ Re-Enable Port A \*/ } } The following routine returns how many odd bytes have been left in the Fifo at the end of a data transfer. \*\*\*\*\*\* int FIFO\_count\_odd\_bytes() ł int number odd byres; number\_odd\_bytes=0; if (FIFO1->status & FIFO\_DATA\_IN\_RAM) ł if (PORT\_A\_TO\_PORT\_B(FIFO1)) { number\_odd\_bytes = (PORT\_A\_BYTE\_ADDRESS(FIFO1)) ; if (PORT A TO RAM Y(FIFO1)) number\_odd\_bytes += (FIFOl->ram\_Y\_addr) = 4 ;

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

(.

8/24/89-7

N IN

•

5

10

15

20

25

30

35

40

-130else number\_odd\_bytes += (FIFO1->ram\_X\_addr) \* 4 ; } else { if (PORT\_B\_TO\_RAM\_Y(FIFO1)) number\_odd\_bytes = (FIFO1->ram\_Y\_addr) \* 4 ; else number\_odd\_bytes = (FIFO1->ram\_X\_addr) \* 4 ; } } return (number\_odd\_bytes); ) The following routine tests the microprocessor interface of the chip. It first writes and reads the first 6 registers. It then writes Is, Os, and an address pattern to the RAM, reading the data back and checking it. The test returns a bit significant error code where each bit represents the address of the registers that failed. Bit 0 = config register failed Bit 1 = control register failed Bit 2 = status register failed Bit 3 = ram access control register failed Bit 4 = ram X address register failed Bit 5 = ram Y address register failed Bit 6 = data register failed Bit 7 = checksum register failed #define RAM\_DEPTH 64 → /\* number of long words in Fifo Ram \*/ reg\_expected\_data[6] = { 0x7F, 0xFF, 0x00, 0x1F, 0x3F, 0x3F }; char FIFO\_uprocessor\_interface\_test() Ł unsigned long test\_data; char \*register\_addr; int i; char j, error; FIFO1->config = FIFO\_RESET; /\* reset the chip \*/ error=0; register\_addr =(char \*) FIF01; i=1: /\* first test registers 0 thru 5 \*/ for (i=0; i<6; i++) { \*register\_addr = 0xFF; /\* write test data \*/ if (\*register\_addr != reg\_expected\_data[i]) error != j; \*register\_addr = 0; /\* write 0s to register \*/ if (\*register\_addr) error {= j; Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001 8/24/89-7

· (

5

10

15

20

25

30

35

40

45

2

#### -131-

Ċ

٠. /\* write test data again \*/ \*register\_addr = 0xFF; if (\*register\_addr 1= reg\_expected\_data[i]) error |= j; FIF01->config = FIF0\_RESET; /\* reset the chip \*/ if (\*register addr) error |= j; /\* register should be 0 \*/ /\* go to next register \*/ 5 register\_addr++; j <<=1; . • } /\* now test Ram data & checksum registers 10 test 1s throughout Ram & then test 0s \*/ for (test\_data = -1; test\_data != 1; test\_data++) { /\* test for 1s & 0s \*/ FIF01->config = FIF0\_RESET { FIF0\_16\_BITS ; FIFO1->control = FIFO\_PORT\_A\_TO\_B; 15 /\* write data to RAM \*/ for (i=0;i<RAM DEPTH;i++)</pre> FIFO1->data = test\_data;  $FIFO1 \rightarrow control = 0;$ for (i=0;i<RAM DEPTH;i++)</pre> 20 if (FIFO1->data != test\_data) error {= j; /\* read & check data \*/ if (FIFO1->checksum) error {= 0x80; /\* checksum should =  $0 \neq /$ } 25 /\* now test Ram data with address pattern uses a different pattern for every byte \*/ test\_data=0x00010203; /\* address pattern start \*/ FIF01->config = FIF0\_RESET | FIF0\_16\_BITS | FIF0\_CARRY\_WRAP; 30 FIF01->control = FIF0\_PORT\_A\_TO\_B | FIF0\_CHECKSUM\_ENABLE; for (i=0;i<RAM\_DEPTH;i++) {</pre> FIFO1->data = test\_data; /\* write address pattern \*/ test\_data += 0x04040404;} 35 test\_data=0x00010203; /\* address pattern start \*/ FIFO1->control = FIFO\_CHECKSUM\_ENABLE; for (i=0;i<RAM\_DEPTH;i++) {</pre> if (FIFO1->status != FIFO\_DATA\_IN\_RAM) error |= 0x04; /\* should be data in ram \*/ 40 if (FIFO1->data != test\_data) error != j; /\* read & check address pattern \*/ test\_data += 0x04040404; } if (FIFO1->checksum != 0x0102) error := 0x80; /\* test 45 checksum of address pattern \*/ FIFO1->config = FIFO\_RESET | FIFO\_16\_BITS ; /\* inhibit carry wrap \*/ FIFO1->checksum = 0xFEFE; /\* writing adds to checksum \*/

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

#### 8/24/89-7

(

$\overline{\mathbf{C}}$

#### -132-

if (FIFO1->checksum) error {=0x80; /\* checksum should be 0 \*/ if (FIFO1->status) error {= 0x04; /\* status should be 0 \*/ return (error); } .

÷

## Attorney Docket No.:AUSP7209 WP1/WSW/AUSP/7209.001

•

Т

. . : .

#### 8/24/89-7

#### CLAIMS

(1)

1. Network server apparatus for use with a data network and a mass storage device, comprising:

an interface processor unit coupleable to said network and to said mass storage device;

a host processor unit capable of running remote procedures defined by a client node on said network;

means in said interface processor unit for satisfying requests from said network to store data from said network on said mass storage device;

means in said interface processor unit for satisfying requests from said network to retrieve data from said mass storage device to said network; and

means in said interface processor unit for transmitting predefined categories of messages from said network to said host processor unit for processing in said host processor unit, said transmitted messages including all requests by a network client to run client-defined procedures on said network server apparatus.

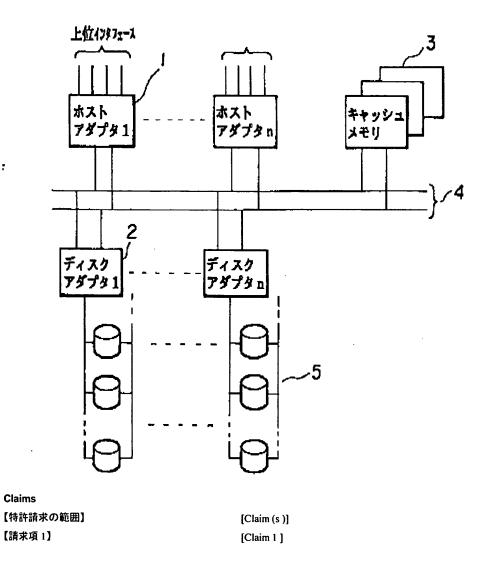

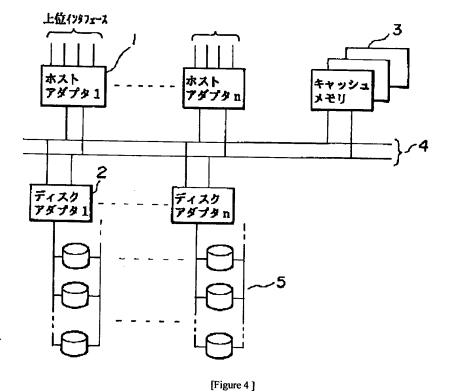

2. Apparatus according to claim 1, wherein said interface processor unit comprises:

a network control unit coupleable to said network;

a data control unit coupleable to said mass storage device;

a buffer memory;

- 133 -

Attorney Docket No.: AUSP7209HCF/GBR/WSW wsw/ausp/7209.claims

means in said network control unit for transmitting to said data control unit requests from said network to store specified storage data from said network on said mass storage device;

means in said network control unit for transmitting said specified storage data from said network to said buffer memory and from said buffer memory to said data control unit;

means in said network control unit for transmitting to said data control unit requests from said network to retrieve specified retrieval data from said mass storage device to said network;

means in said network control unit for transmitting said specified retrieval data from said data control unit to said buffer memory and from said buffer memory to said network; and

means in said network control unit for transmitting said predefined categories of messages from said network to said host processing unit for processing by said host processing unit.

3. Apparatus according to claim 2, wherein said data control unit comprises:

a storage processor unit coupleable to said mass storage device;

a file processor unit;

means on said file processor unit; for translating said file system level storage requests from said

- 134 -

Attorney Docket No.: AUSP7209MCF/GBR/WSW Wsw/ausp/7209.claims

network into requests to store data at specified physical storage locations in said mass storage device;

means on said file processor unit for instructing said storage processor unit to write data from said buffer memory into said specified physical storage locations in said mass storage device;

means on said file processor unit for translating file system level retrieval requests from said network into requests to retrieve data from specified physical retrieval locations in said mass storage device;

means on said file processor unit for instructing said storage processor unit to retrieve data from said specified physical retrieval locations in said mass storage device to said buffer memory if said data from said specified physical locations is not already in said buffer memory; and

means in said storage processor unit for transmitting data between said buffer memory and said mass storage device.

4. Network server apparatus for use with a data network and a mass storage device, comprising:

a network control unit coupleable to said network;

a data control unit coupleable to said mass storage device;

a buffer memory;

means for transmitting from said network control unit to said data control unit requests from said

- 135 -

. .... . . . . . . .

Attorney Docket No.: AUSP7209MCF/GBR/WSW WSW/ausp/7209.claims

network to store specified storage data from said network on said mass storage device;

. .: .!

means for transmitting said specified storage data by DMA from said network control unit to said buffer memory and by DMA from said buffer memory to said data control unit;

means for transmitting from said network control unit to said data control unit requests from said network to retrieve specified retrieval data from said mass storage device to said network; and

means for transmitting said specified retrieval data by DMA from said data control unit to said buffer memory and by DMA from said buffer memory to said network control unit.

5. Apparatus according to claim 1, for use further with a buffer memory, and wherein said requests from said network to store and retrieve data include file system level storage and retrieval requests respectively, and wherein said interface processor unit comprises:

a storage processor unit coupleable to said mass storage device;

a file processor unit;

means on said file processor unit for translating said file system level storage requests into requests to store data at specified physical storage locations in said mass storage device;

- 136 -

Attorney Docket No.: AUSP7209NCF/GBR/WSW wsw/ausp/7209.claims

means on said file processor unit for instructing said storage processor unit to write data from said buffer memory into said specified physical storage locations in said mass storage device;

means on said file processor unit for translating said file system level retrievable requests into requests to retrieve data from specified physical retrievable locations in said mass storage device;

۰.

means on said file processor unit for instructing said storage processor unit to retrieve data from said specified physical retrievablelocations in said mass storage device to said buffer memory if said data from said specified physical locations is not already in said buffer memory; and

means in said storage processor unit for transmitting data between said buffer memory and said mass storage device.

- 137-

Network server apparatus for use with a data network, comprising:

a network controller coupleable to said network to receive incoming information packets over said network, said incoming information packets including certain packets which contain part or all of a request to said server apparatus, said request being in either a first or a second class of requests to said server apparatus;

a first additional processor;

an interchange bus different from said network and coupled between said network controller and said first additional processor;

means in said network controller for detecting and satisfying requests in said first class of requests contained in said certain incoming information packets, said network controller lacking means in said network controller for satisfying requests in said second class of requests;

means in said network controller for detecting and assembling into assembled requests, requests in said second class of requests contained in said certain incoming information packets;

means for delivering said assembled requests from said network controller to said first additional processor over said interchange bus; and

means in said first additional processor for further processing said assembled requests in said second class of requests.

- 13'8 -

095447/2

7. Apparatus according to claim 6 wherein said packets each include a network node destination address, and wherein said means in said network controller for detecting and assembling into assembled requests, assembles said assembled requests in a format which omits said network node destination addresses.

095447/2

8. Apparatus according to claim 6 wherein said means in said network controller for detecting and satisfying requests in said first class of requests, assembles said requests in said first class of requests into assembled requests before satisfying said requests in said first class of requests.

9. Apparatus according to claim 6, wherein said packets each include a network node destination address, wherein said means in said network controller for detecting and assembling into assembled requests, assembles said assembled requests in a format which omits said network node destination addresses, and wherein said means in said network controller for detecting and satisfying requests in said first class of requests, assembles said requests in said first class of requests, in a format which omits said network node destination addresses, before satisfying said requests in said first class of requests.

- 139 -

095447/2 10. Apparatus according to claim 6, wherein said means in said network controller for detecting and satisfying requests in said first class includes means for preparing an outgoing message in response to one of said first class of requests, means for packaging said outgoing message in outgoing information packets suitable for transmission over said network, and means for transmitting said outgoing information packets over said network.

11. Apparatus according to claim 6, further comprising a buffer memory coupled to said interchange bus, and wherein said means for delivering said assembled requests comprises:

means for transferring the contents of said assembled requests over said interchange bus into said buffer memory; and

means for notifying said first additional processor of the presence of said contents in said buffer memory.

$\sim \sim$

12. Apparatus according to claim 6, wherein said means in said first additional processor for further processing said assembled requests includes means for preparing an outgoing message in response to one of said second class of requests, said apparatus further comprising means for delivering said outgoing message from said first additional processor to said network controller over said interchange bus, said network controller further comprising means in said network controller for packaging said outgoing message in outgoing information packets suitable for transmission over said network, and means in said network controller for transmitting said outgoing information packages over said network. - 14013. Apparatus according to claim  $_6$ , wherein said first class of requests comprises requests for an address of said server apparatus, and wherein said

095447/2

means in said network controller for detecting and satisfying requests in said first class comprises means for preparing a response packet to such an address request and means for transmitting said response packet over said network.

14. Apparatus according to claim 6 for use further with a second data network, said network controller being coupleable further to said second network, wherein said first class of requests comprises requests to route a message to a destination reachable over said second network, and wherein said means in said network controller for detecting and satisfying requests in said first class comprises means for detecting that one of said certain packets comprises a request to route a message contained in said one of said certain packets to a destination reachable over said second network, and means for transmitting said message over said second network.

15. Apparatus according to claim 14 for use further with a third data network, said network controller further comprising means in said network controller for detecting particular requests in said incoming information packets to route a message contained in said particular requests, to a destination reachable over said third network, said apparatus further comprising:

- 141 -

a second network controller coupled to said interchange bus and coupleable to said third data network;

means for delivering said message contained in said particular requests to said second network controller over said interchange bus; and

means in said second network controller for transmitting said message contained in said particular requests over said third network.

<sup>16</sup>. Apparatus according to claim 6, for use further with a third data network, said network controller further comprising means in said network controller for detecting particular requests in said incoming information packets to route a message contained in said particular requests, to a destination reachable over said third network, said apparatus further comprising:

a second network controller coupled to said interchange bus and coupleable to said third data network;

means for delivering said message contained in said particular requests to said second network controller over said interchange bus; and

means in said second network controller for transmitting said message contained in said particular requests over said third network.

- 142 -

Attorney Docket No.: AUSP7209KCF/GBR/WSW wsw/ausp/7209.claims

•....

1.1

17. Apparatus according to claim 6 for use further with a mass storage device, wherein said first additional processor comprises a data control unit coupleable to said mass storage device, wherein said second class of requests comprises remote calls to procedures for managing a file system in said mass storage device, and wherein said means in said first additional processor for further processing said assembled requests in said second class of requests comprises means for executing file system procedures on said mass storage device in response to said assembled requests.

18. Apparatus according to claim 17 wherein said file system procedures include a read procedure for reading data from said mass storage device,

said means in said first additional processor for further processing said assembled requests including means for reading data from a specified location in said mass storage device in response to a remote call to said read procedure,

said apparatus further including means for delivering said data to said network controller,

said network controller further comprising means on said network controller for packaging said data in outgoing information packets suitable for transmission over said network, and means for transmitting said outgoing information packets over said network.

- 143 -

Attorney Docket No.: AUSP7209MCF/GBR/WSW WBW/ausp/7209.claims

, . .

19. Apparatus according to claim 18, wherein said means for delivering comprises:

Alternative states and stat states and sta

a system buffer memory coupled to said interchange bus;

means in said data control unit for transferring said data over said interchange bus into said buffer memory; and

means in said network controller for transferring said data over said interchange bus from said system buffer memory to said network controller.

20. Apparatus according to claim 17, wherein said file system procedures include a read procedure for reading a specified number of bytes of data from said mass storage device beginning at an address specified in logical terms including a file system ID and a file ID, said means for executing file system procedures comprising:

means for converting the logical address specified in a remote call to said read procedure to a physical address; and

means for reading data from said physical address in said mass storage device.

21. Apparatus according to claim 20, wherein said mass storage device comprises a disk drive having a numbered tracks and sectors, wherein said logical address specifies said file system ID, said file ID,

- 144 -

Attorney Docket No.: AUSP7209MCF/GBR/WSW WSW/ausp/7209.claims

د....>

·:- ;:

and a byte offset, and wherein said physical address specifies a corresponding track and sector number.

22. Apparatus according to claim 17, wherein said file system procedures include a read procedure for reading a specified number of bytes of data from said mass storage device beginning at an address specified in logical terms including a file system ID and a file ID,

said data control unit comprising a file processor coupled to said interchange bus and a storage processor coupled to said interchange bus and coupleable to said mass storage device,

said file processor comprising means for converting the logical address specified in a remote call to said read procedure to a physical address,

said apparatus further comprising means for delivering said physical address to said storage processor,

said storage processor comprising means for reading data from said physical address in said mass storage device and for transferring said data over said interchange bus into said buffer memory; and

means in said network controller for transferring said data over said interchange bus from said system buffer memory to said network controller.

23. Apparatus according to claim 17, wherein said file system procedures include a write procedure for

- 145 -

Attorney Docket No.: AUSP7209NCF/GBR/WSW ··· wsw/susp/7209.claims

#### 095447/2

writing data contained in an assembled request, to said mass storage device,

said means in said first additional processor for further processing said assembled requests including means for writing said data to a specified location in said mass storage device in response to a remote call to said read procedure.

24. Apparatus according to claim 6, wherein said first additional processor comprises a host computer coupled to said interchange bus, wherein said second class of requests comprises remote calls to procedures other than procedures for managing a file system, and wherein said means in said first additional processor for further processing said assembled requests in said second class of requests comprises means for executing remote procedure calls in response to said assembled requests.

25. Apparatus according to claim 24, for use further with a mass storage device and a data control unit coupleable to said mass storage device and coupled to said interchange bus, wherein said network controller further comprises means in said network controller for detecting and assembling remote calls, received over said network, to procedures for managing a file system in said mass storage device, and wherein said data control unit comprises means for executing file system procedures on said mass storage device in

- 146 -

Attorney Docket No.: AUSP7209NCF/GBR/WSW WSW/AUSp/7209.claims

. . . . . . . .

response to said remote calls to procedures for managing a file system in said mass storage device.

26. Apparatus according to claim 24, further comprising means for delivering all of said incoming information packets not recognized by said network controller to said host computer over said interchange bus.

27. Apparatus according to claim 6, wherein said network controller comprises:

a microprocessor;

2.2

a local instruction memory containing local instruction code;

a local bus coupled between said microprocessor and said local instruction memory;

bus interface means for interfacing said microprocessor with said interchange bus at times determined by said microprocessor in response to said local instruction code; and

network interface means for interfacing said microprocessor with said data network,

said local instruction memory including all instruction code necessary for said microprocessor to perform said function of detecting and satisfying requests in said first class of requests, and all instruction code necessary for said microprocessor to perform said function of detecting and assembling into

\_ 147 \_

Attorney Docket No.: AUSP7209NCF/GBR/WSW wsw/ausp/7209.claims

095447/2 assembled requests, requests in said second class of requests.

28. Network server apparatus for use with a data network, comprising:

a network controller coupleable to said network to receive incoming information packets over said network, said incoming information packets including certain packets which contain part or all of a message to said server apparatus, said message being in either a first or a second class of messages to said server apparatus, said messages in said first class of messages including certain messages containing requests;

a host computer;

····

an interchange bus different from said network and coupled between said network controller and said host computer;

means in said network controller for detecting and satisfying said requests in said first class of messages ;

means for delivering messages in said second class of messages from said network controller to said host computer over said interchange bus; and

means in said host computer for further processing said messages in said second class of messages.

29. Apparatus according to claim 28, wherein said packets each include a network node destination address, and wherein said means for delivering messages

- 148 -

Attorney Docket No.: AUSP7209MCF/GBR/WSW wsw/ausp/7209.claims

095447/2

in said second class of messages comprises means in said network controller for detecting said messages in said second class of messages and assembling them into assembled messages in a format which omits said network node destination addresses.

30. Apparatus according to claim 28, wherein said means in said network controller for detecting and satisfying requests in said first class includes means for preparing an outgoing message in response to one of said requests in said first class of messages, means for packaging said outgoing message in outgoing information packets suitable for transmission over said network, and means for transmitting said outgoing information packets over said network.

31. Apparatus according to claim 28, for use further with a second data network, said network controller being coupleable further to said second network, wherein said first class of messages comprises messages to be routed to a destination reachable over said second network, and wherein said means in said network controller for detecting and satisfying requests in said first class comprises means for detecting that one of said certain packets includes a request to route a message contained in said one of said certain packets to a destination reachable over said second network, and means for transmitting said message over said second network.

- 1'49 -

Attorney Docket No.: AUSP7209MCF/GBR/WSW wsw/ausp/7209.claims

<sup>32</sup>. Apparatus according to claim 28, for use further with a third data network, said network controller further comprising means in said network controller for detecting particular messages in said incoming information packets to be routed to a destination reachable over said third network, said apparatus further comprising:

a second network controller coupled to said interchange bus and coupleable to said third data network;

means for delivering said particular messages to said second network controller over said interchange bus, substantially without involving said host computer; and

means in said second network controller for transmitting said message contained in said particular requests over said third network, substantially without involving said host computer.

33. Apparatus according to claim 28, for use further with a mass storage device, further comprising a data control unit coupleable to said mass storage device,

said network controller further comprising means in said network controller for detecting ones of said incoming information packets containing remote calls to procedures for managing a file system in said mass storage device, and means in said network controller

- 1:50 -

Attorney Docket No.: AUSP7209MCF/GBR/WSW WSW/BUSp/7209.claims

095447/2

for assembling said remote calls from said incoming packets into assembled calls, substantially without involving said host computer,

said apparatus further comprising means for delivering said assembled file system calls to said data control unit over said interchange bus substantially without involving said host computer, and said data control unit comprising means in said data control unit for executing file system procedures on said mass storage device in response to said assembled file system calls, substantially without involving said host computer.

34. Apparatus according to claim 28, further comprising means for delivering all of said incoming information packets not recognized by said network controller to said host computer over said interchange bus.

35. Apparatus according to claim 28, wherein said network controller comprises:

a microprocessor;

æ.,

a local instruction memory containing local instruction code;

a local bus coupled between said microprocessor and said local instruction memory;

bus interface means for interfacing said microprocessor with said interchange bus at times

- 151 -

Attorney Docket No.: AUSP7209MCF/GBR/WSW wsw/ausp/7209.claims

095447/2

$i_7$

÷.,

determined by said microprocessor in response to said local instruction code; and

network interface means for interfacing said microprocessor with said data network,

said local instruction memory including all instruction code necessary for said microprocessor to perform said function of detecting and satisfying requests in said first class of requests.

For the Applica Sanford T. Colb & Co. C:11071

- 152 -

i

ļ

i

AUSPEX SYSTEMS, INC.

TWELVE SHEETS SHEET NO. FIVE

\_\_\_\_\_

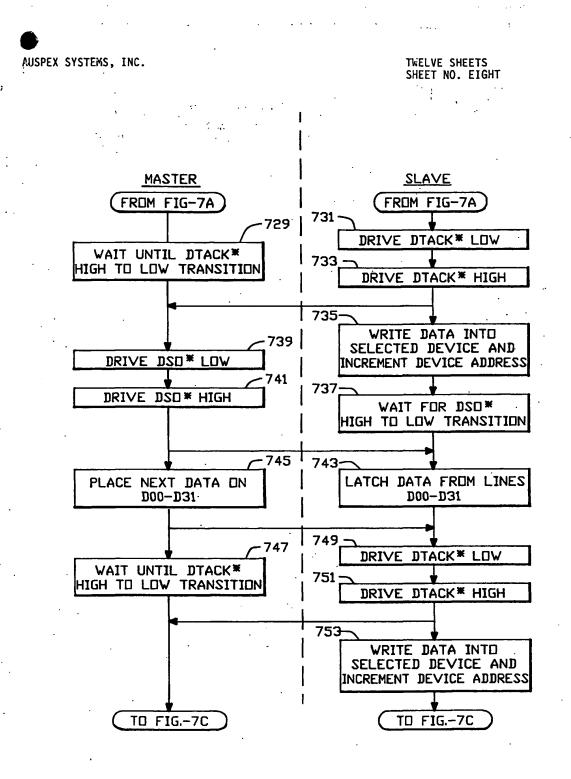

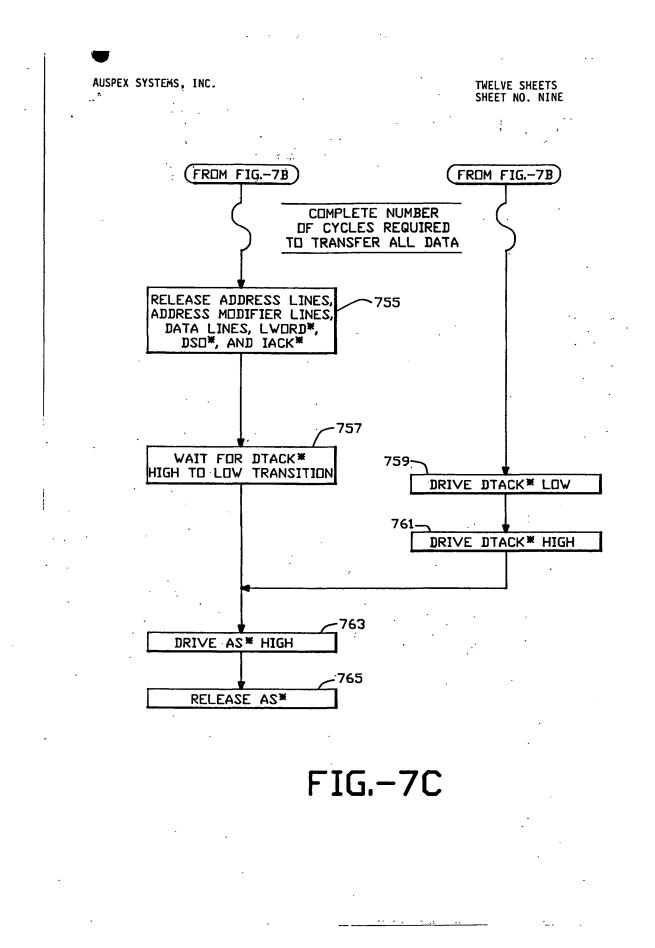

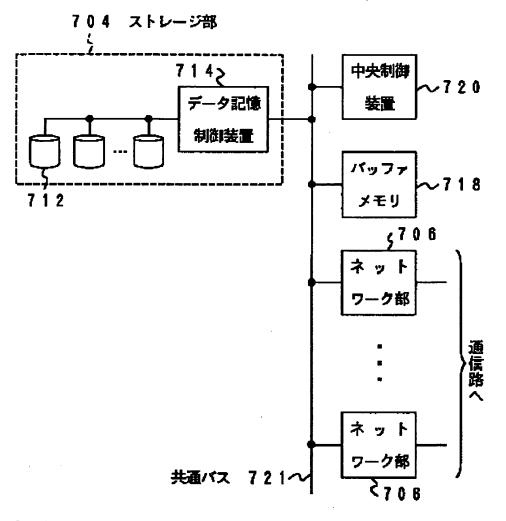

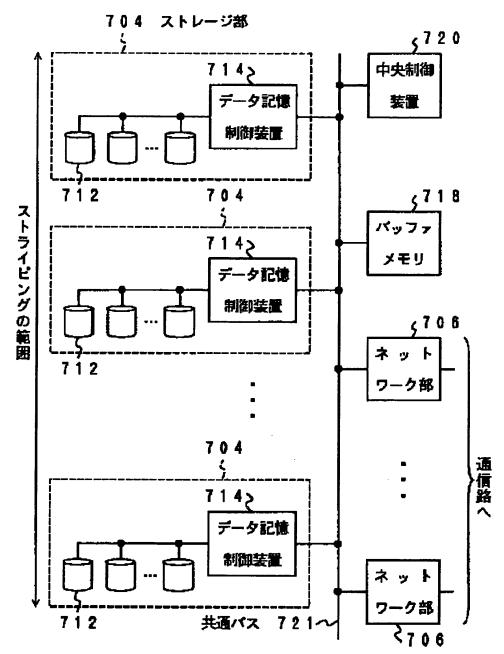

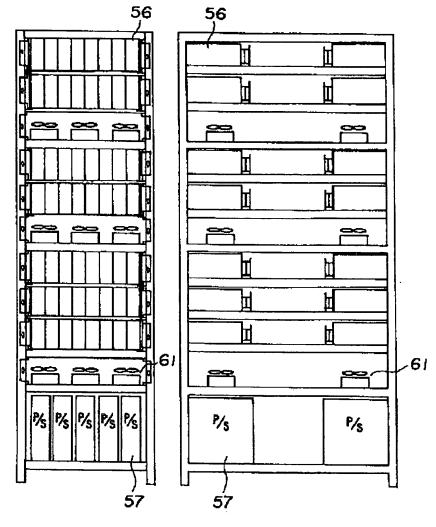

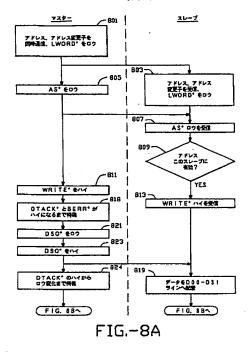

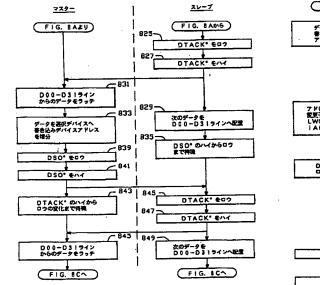

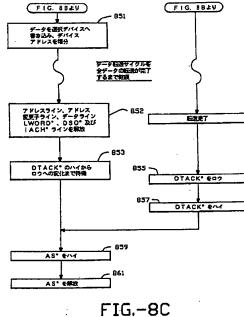

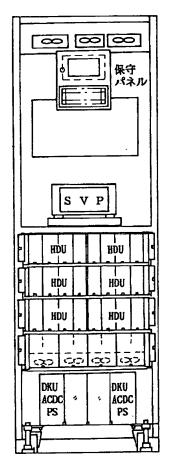

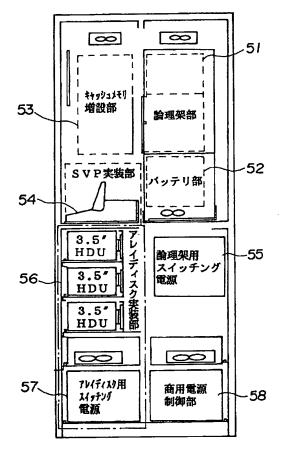

FIG.-7B

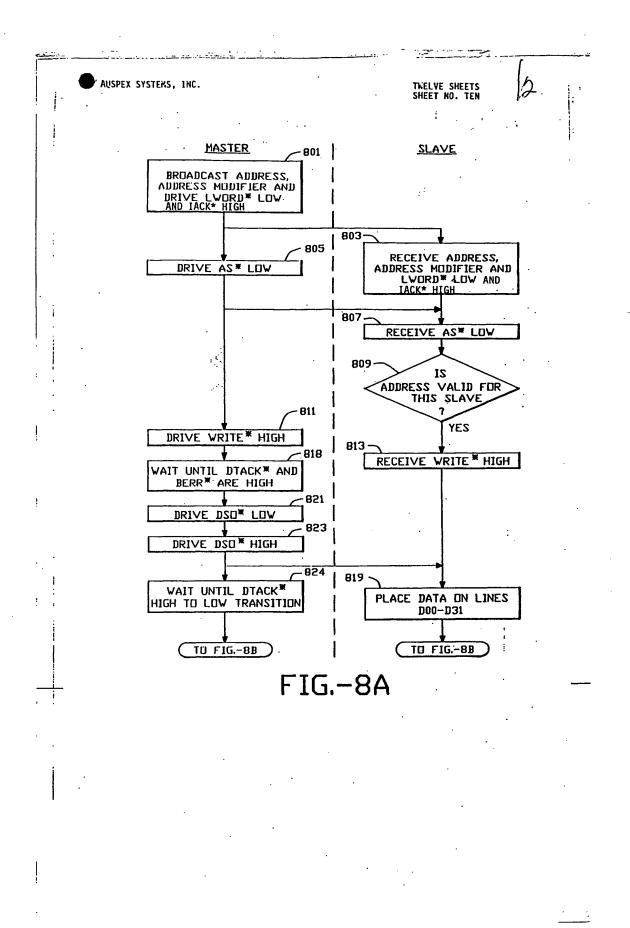

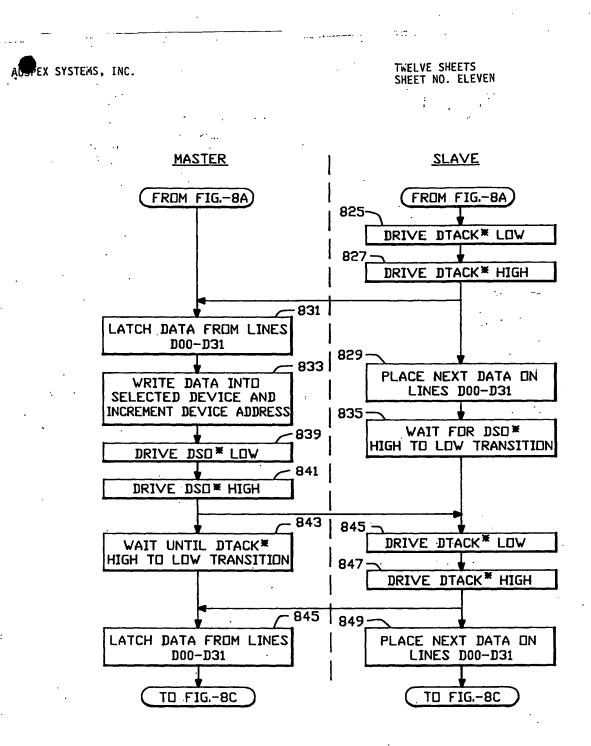

FIG.-8B

NetApp Ex. 1002, pg. 651

----

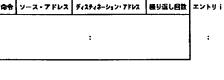

|                                                                                                       |                                                      |                                        |                                           |                                                                 | Se la        |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------|-------------------------------------------|-----------------------------------------------------------------|--------------|

| שימוש הלשכה<br>Fpr-Office Use                                                                         | · · · · · · · · · · · · · · · · · · ·                |                                        | 190                                       | חוק הפטנטים, תשכ"ו – 67<br>PATENT LAW, 5727 - 1967              | j <u>A</u> S |

| 107645                                                                                                | אריר:<br>Number                                      |                                        | b                                         | בקשה לפטנ<br>Application for Patent                             | Æ.           |

| ากา                                                                                                   | Dete<br>Interove                                     |                                        |                                           | C:17980                                                         | 13.12        |

| Anie/Po                                                                                               | osl-deled I (Name a                                  | nd address of applican                 | גרף מאונד – מקונ<br>, and in case of body | וני, (שם המבקש, מענו ולגבי<br>corporate-place of incorporation) | t .<br>)     |

| AUCDEY SY                                                                                             | STEMS, INC.,                                         |                                        |                                           |                                                                 |              |

| 2952 Bunk                                                                                             | èr Hill Lane, 👘 👘                                    |                                        |                                           | •                                                               |              |

| Santa Cla<br>Ca. 95054                                                                                |                                                      | •                                      |                                           |                                                                 |              |

| (Incorpor                                                                                             | ated in the State                                    | of California,                         | USA)                                      |                                                                 |              |

|                                                                                                       |                                                      |                                        |                                           | _                                                               |              |

| f an invention the title of a                                                                         | which is                                             | •••••••••••••••••••••••••••••••••••••• |                                           | בעל אמצאה מכח                                                   |              |

|                                                                                                       |                                                      |                                        | •                                         | Owner, by virtue of                                             |              |

|                                                                                                       | ירות תיקים                                           | קבילה למערכת ש                         | אריכטקטורה ם                              | (בעברית)<br>(Hebrew)                                            |              |

|                                                                                                       |                                                      |                                        |                                           | (באנגלית)                                                       |              |

| I                                                                                                     | PARALLEL I/O NETWOR                                  | K FILE SERVER                          | ARCHITECTURE                              | (English)                                                       |              |

|                                                                                                       |                                                      |                                        |                                           |                                                                 |              |

|                                                                                                       |                                                      |                                        | * .                                       |                                                                 |              |

| areby apply for a patent to                                                                           | be granted to me in respec                           | t thereof.                             |                                           | מבקש בואת כי ינתן לי עליה פט                                    |              |

| - בקשת וולוקה<br>Application of Division A                                                            | - Tono DID Patent Addition                           |                                        | שה רין קריפה<br>Priority Clai             | • 11.                                                           |              |

| DIDD NUPID<br>from Application                                                                        | לבקשה/למטנט •<br>to Patent/Appl.                     | 18°0/1803<br>Number/Mark               | תאריך<br>Date                             | מויינה האנוד<br>Convention Country                              |              |

| io. <u>095447</u> 00                                                                                  | No                                                   |                                        |                                           |                                                                 |              |

| L                                                                                                     | dated                                                | 07/404,959                             | 8.9.89                                    | U.S.A.                                                          |              |

| יאוי כח: כללי / מיוחד – רצוף בוה / עוד יונש<br>P.O.A.: general/individual-attached/to be filed later- |                                                      |                                        |                                           |                                                                 |              |

| filed in case                                                                                         |                                                      |                                        |                                           |                                                                 |              |

|                                                                                                       | המען למסירה מסמכים ביש<br>dress for Service in hreef |                                        |                                           |                                                                 |              |

|                                                                                                       | ס <u>נפורד ט. קולב .Co</u>                           |                                        |                                           |                                                                 |              |

| P.O.B. 2273                                                                                           | 2273т.л                                              |                                        |                                           |                                                                 |              |

| Rehovot 76 122                                                                                        | רחובות 76122                                         |                                        | 1                                         | Ļ                                                               | . •          |

| For the Applicant,                                                                                    | התימת המבקש<br>Signeture of Applicant                |                                        | 993 njv N<br>of the year                  | היום <u>16 בחודש V</u><br>of This                               |              |

|                                                                                                       |                                                      |                                        |                                           | לשיפוש חלשכה<br>For Office Use                                  |              |

| Sanford T. Colb & C: 1798                                                                             |                                                      |                                        |                                           |                                                                 |              |

| C. 1/98                                                                                               | U                                                    |                                        |                                           |                                                                 |              |

• 1

P

t<del>)</del>

· · · · ·

## אריכטקטורה מקבילה למערכת שירות תיקים

## PARALLEL I/O NETWORK FILE SERVER ARCHITECTURE

AUSPEX SYSTEMS, INC. C: 17980

# -1-PARALLEL I/O NETWORK FILE SERVER ARCHITECTURE

INVENTORS: EDWARD JOHN ROW, LAURENCE B. BOUCHER, WILLIAM M. PITTS, STEPHEN E. BLIGHTMAN

## CROSS-REFERENCE TO RELATED APPLICATIONS

The present application is related to the following U.S. Patent Applications, all filed concurrently herewith:

1. MULTIPLE FACILITY OPERATING SYSTEM ARCHITECTURE, invented by David Hitz, Allan Schwartz, James Lau and Guy Harris;

2. ENHANCED VMEBUS PROTOCOL UTILIZING PSEUDOSYNCHRONOUS HANDSHAKING AND BLOCK MODE DATA TRANSFER, invented by Daryl Starr; and

3. BUS LOCKING FIFO MULTI-PROCESSOR COMMUNICATIONS SYSTEM UTILIZING PSEUDOSYNCHRONOUS HANDSHAKING AND BLOCK MODE DATA TRANSFER invented by Daryl D. Starr, William Pitts and Stephen Blightman.

20

.

)

5

10

15

• •

The above applications are all assigned to the assignee of the present invention and are all expressly incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

#### Field of the Invention

25

The invention relates to computer data networks, and more particularly, to network file server architectures for computer networks.

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

#### 8/24/89-7

**.** ·

### Description of the Related Art

Over the past ten years, remarkable increases in hardware price/performance ratios have caused a startling shift in both technical and office computing environments. Distributed workstation-server networks are displacing the once pervasive dumb terminal attached to mainframe or minicomputer. To date, however, network I/O limitations have constrained the potential performance available to workstation users. This situation has developed in part because dramatic jumps in microprocessor performance have exceeded increases in network I/O performance.

-2-

C

In a computer network, individual user workstations are referred to as clients, and shared 15 resources for filing, printing, data storage and widearea communications are referred to as servers. Clients and servers are all considered nodes of a network. Client nodes use standard communications protocols to exchange service requests and responses 20 with server nodes.

Present-day network clients and servers usually run the DOS, MacIntosh OS, OS/2, or Unix operating systems. Local networks are usually Ethernet or Token Ring at the high end, Arcnet in the midrange, or LocalTalk or StarLAN at the low end. The client-server

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

5

10

$\bigcirc$

25

communication protocols are fairly strictly dictated by the operating system environment -- usually one of several proprietary schemes for PCs (NetWare, 3Plus, Vines, LANManager, LANServer); AppleTalk for MacIntoshes; and TCP/IP with NFS or RFS for Unix. These protocols are all well-known in the industry:

Unix client nodes typically feature a 16- or 32bit microprocessor with 1-8 MB of primary memory, a 640 x 1024 pixel display, and a built-in network interface. A 40-100 MB local disk is often optional. Low-end examples are 80286-based PCs or 68000-based MacIntosh I's; mid-range machines include 80386 PCs, MacIntosh II's, and 680X0-based Unix workstations; high-end machines include RISC-based DEC, HP, and Sun Unix workstations. Servers are typically nothing more than repackaged client nodes, configured in 19-inch racks rather than desk sideboxes. The extra space of a 19-inch rack is used for additional backplane slots, disk or tape drives, and power supplies.

Driven by RISC and CISC microprocessor developments, client workstation performance has increased by more than a factor of ten in the last few years. Concurrently, these extremely fast clients have also gained an appetite for data that remote servers are unable to satisfy. Because the I/O shortfall is most dramatic in the Unix environment, the

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

10

15

20

25

5

$\bigcirc$

•

.

-3-

description of the preferred embodiment of the present invention will focus on Unix file servers. The architectural principles that solve the Unix server I/O problem, however, extend easily to server performance bottlenecks in other operating system environments as well. Similarly, the description of the preferred embodiment will focus on Ethernet implementations, though the principles extend easily to other types of networks.

In most Unix environments, clients and servers exchange file data using the Network File System ("NFS"), a standard promulgated by Sun Microsystems and now widely adopted by the Unix community. NFS is defined in a document entitled, "NFS: Network File System Protocol Specification," Request For Comments (RFC) 1094, by Sun Microsystems, Inc. (March 1989). This document is incorporated herein by reference in its entirety.

While simple and reliable, NFS is not optimal. Clients using NFS place considerable demands upon both networks and NFS servers supplying clients with NFS data. This demand is particularly acute for so-called diskless clients that have no local disks and therefore depend on a file server for application binaries and virtual memory paging as well as data. For these Unix client-server configurations, the ten-

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

-4-

(

L

10

5

- 15

. . -

- - 25

to-one increase in client power has not been matched by: a ten-to-one increase in Ethernet capacity, in disk speed, or server disk-to-network I/O throughput.

-5-

The result is that the number of diskless clients that a single modern high-end server can adequately support has dropped to between 5-10, depending on client power and application workload. For clients containing small local disks for applications and paging, referred to as dataless clients, the clientto-server ratio is about twice this, or between 10-20.

Such low client/server ratios cause piecewise network configurations in which each local Ethernet contains isolated traffic for its own 5-10 (diskless) clients and dedicated server. For overall connectivity, these local networks are usually joined together with an Ethernet backbone or, in the future, with an FDDI backbone. These backbones are typically connected to the local networks either by IP routers or MAC-level bridges, coupling the local networks together 20 · directly, or by a second server functioning as a network interface, coupling servers for all the local networks together.

In addition to performance considerations, the low client-to-server ratio creates computing problems in several additional ways:

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

10

5

15

1. Sharing. Development groups of more than 5-10 people cannot share the same server, and thus cannot easily share files without file replication and manual, multi-server updates. Bridges or routers are a partial solution but inflict a performance penalty due to more network hops.

-6-

2. <u>Administration</u>. System administrators must maintain many limited-capacity servers rather than a few more substantial servers. This burden includes network administration, hardware maintenance, and user account administration.

3. <u>File System Backup</u>. System administrators or operators must conduct multiple file system backups, which can be onerously time consuming tasks. It is also expensive to duplicate backup peripherals on each server (or every few servers if slower network backup is used).

4. Price Per Seat. With only 5-10 clients per server, the cost of the server must be shared by only a small number of users. The real cost of an entry-level Unix workstation is therefore significantly greater, often as much as 140% greater, than the cost of the workstation alone.

The widening I/O gap, as well as administrative and economic considerations, demonstrates a need for higher-performance, larger-capacity Unix file servers.

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

## 8/24/89-7

NetApp Ex. 1002, pg. 659

10

15

20

25

5

$\bigcirc$

Conversion of a display-less workstation into a server may address disk capacity issues, but does nothing to address fundamental I/O limitations. As an NFS server, the one-time workstation must sustain 5-10 or more times the network, disk, backplane, and file system throughput than it was designed to support as a Adding larger disks, more network adaptors, client. extra primary memory, or even a faster processor do not basic architectural I/O constraints; I/O resolve throughput does not increase sufficiently.

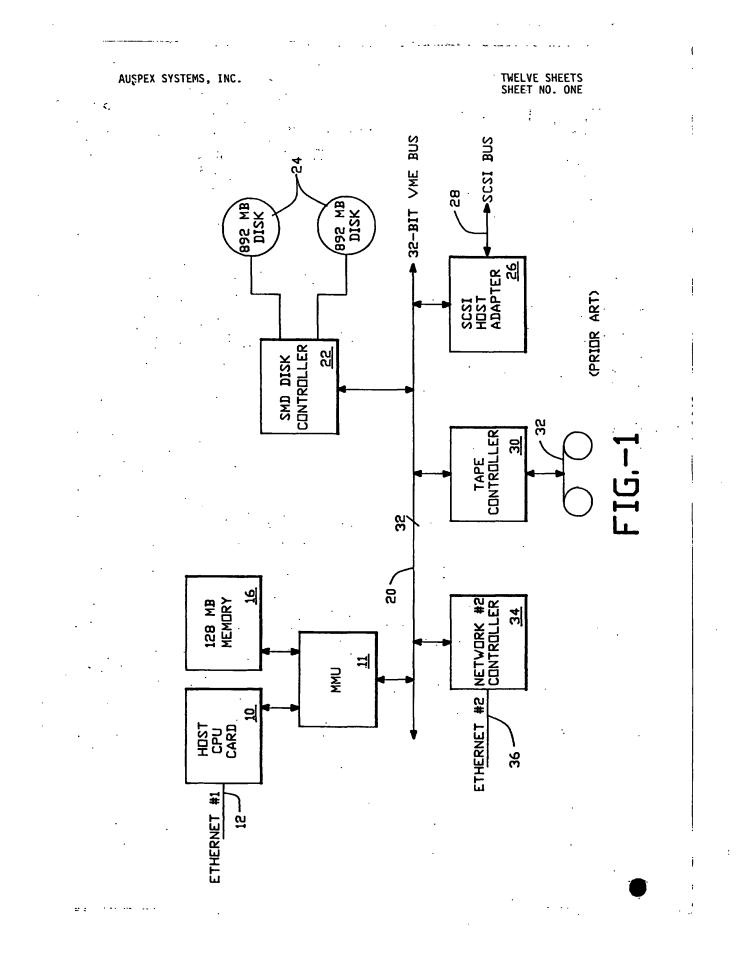

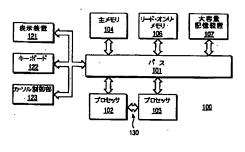

Other prior art computer architectures, while not specifically designed as file servers, may potentially be used as such. In one such well-known architecture, a CPU, a memory unit, and two I/O processors are 15 connected to a single bus. One of the I/O processors operates a set of disk drives, and if the architecture is to be used as a server, the other I/O processor would be connected to a network. This architecture is not optimal as a file server, however, at least because the two I/O processors cannot handle network file requests without involving the CPU. All network file requests that are received by the network I/O processor are first transmitted to the CPU, which makes appropriate requests to the disk-I/O processor for 25 satisfaction of the network request.

Attorney Docket No.: AUSP7209 WP1/WSW/AUSP/7209.001

8/24/89-7

NetApp Ex. 1002, pg. 660

-7-

$\mathbf{i}$

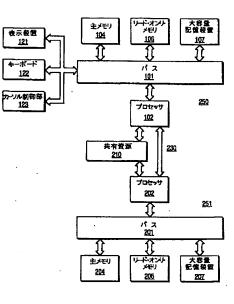

5

10

In another such computer architecture, a disk controller CPU manages access to disk drives, and several other CPUs, three for example, may be: clustered around the disk controller CPU. Each of the other CPUs can be connected to its own network. The network CPUs are each connected to the disk controller CPU as well as to each other for interprocessor communication. One of the disadvantages of this computer architecture is that each CPU in the system runs its own complete operating system. Thus, network file server requests must be handled by an operating system which is also heavily loaded with facilities and processes for performing a large number of other, non file-server tasks. Additionally, the interprocessor communication is not optimized for file server type requests.