### US006237127B1

## (12) United States Patent

Craven et al.

US 6,237,127 B1 (10) Patent No.:

(45) Date of Patent: May 22, 2001

### STATIC TIMING ANALYSIS OF DIGITAL ELECTRONIC CIRCUITS USING NON-**DEFAULT CONSTRAINTS KNOWN AS EXCEPTIONS**

Inventors: Ted L. Craven, Santa Clara; Denis M. Baylor, San Jose; Yael Rindenau,

Cupertino, all of CA (US)

Assignee: Synopsys, Inc., Mountain View, CA

Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 09/093,817

Jun. 8, 1998 (22)Filed:

(51)**Int. Cl.**<sup>7</sup> ...... **G06F** 17/50; G06F 1/04; G06F 1/06; G06F 1/08

**U.S. Cl.** ...... 716/6; 703/2; 703/15; 703/19; 716/1; 716/3; 716/5; 716/7; 716/2;

716/3, 5, 6, 7; 713/500

#### (56)References Cited

### U.S. PATENT DOCUMENTS

| 4,698,760 | * | 10/1987 | Lembach et al | 716/6 |

|-----------|---|---------|---------------|-------|

| 5,210,700 | * | 5/1993  | Tom           | 716/6 |

| 5,282,147 | * | 1/1994  | Goetz et al   | 716/2 |

| 5,339,253 | 計 | 8/1994  | Carrig et al  | 716/6 |

(List continued on next page.)

#### OTHER PUBLICATIONS

Krishna P. Belkhale et al., "Timing Analysis with Known False Sub Graphs", 1995 IEEE pp. 736-740.\*

(List continued on next page.)

Primary Examiner—Matthew Smith Assistant Examiner—Jibreel Speight (74) Attorney, Agent, or Firm—Brown Raysman Millstein Felder & Steiner LLP; Jonathan T. Kaplan

### **ABSTRACT**

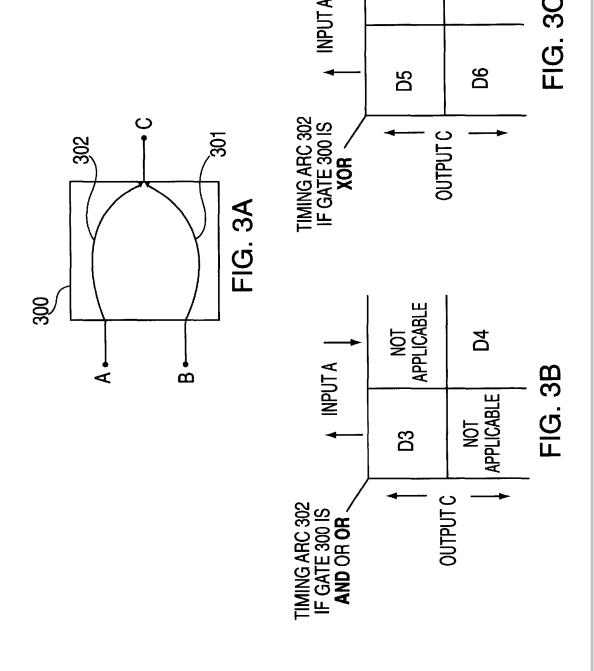

Exceptions allow a circuit designer, working with a circuit synthesis system, to specify certain paths through the circuit to be synthesized as being subject to non-default timing constraints. The additional information provided by the exceptions can allow the synthesis system to produce a more optimal circuit. A tag-based timing analysis tool is presented, which implements exceptions, and can be used in a synthesis system. A circuit is analyzed in "sections," which comprise a set of "launch" flip flops, non-cyclic combinational circuitry and a set of "capture" flip flops. The tagbased static timing analysis of the present invention is performed in four main steps: preprocessing, pin-labeling, RF timing table propagation and relative constraint analysis. Preprocessing converts the exceptions written by the circuit designer into a certain standard form in which paths through the circuit to be synthesized are expressed in terms of circuit "pins." Pin-labeling causes the particular circuit pins, which are the subject of exceptions, to be marked. During RF timing table propagation, "RF timing tables" with rise and fall times are propagated onto all pins of the circuit section. Rise and fall times in the RF timing tables are based on "timing arcs" describing the delay characteristics of each of the state (flip flop) and combinational (logic gate) devices. Each RF timing table has a tag which indicates: i) a launch flip flop clock, and ii) the exception pins through which the RF timing table has propagated. During relative constraint analysis, each RF timing table at the input to a capture flip flop is analyzed for meeting certain relative constraints. These relative constraints may be either defaults, or the defaults may be modified according to an exception satisfied by the contents of the RF timing table's tag.

### 13 Claims, 22 Drawing Sheets

### U.S. PATENT DOCUMENTS

| 5,508,937<br>5,535,145<br>5,602,754<br>5,615,127<br>5,636,372<br>5,648,913<br>5,696,694<br>5,740,067<br>5,864,487<br>5,910,897<br>5,956,256 | * | 7/1996<br>2/1997<br>3/1997<br>6/1997<br>7/1997<br>12/1997 | Beatty et al. 716/6   Beatty et al. 716/7   Hathaway et al. 713/500   Bennett et al. 716/6 |

|---------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 5,956,256<br>6,014,510                                                                                                                      | * | 9/1999<br>1/2000                                          | Č                                                                                          |

| 6,023,567 | * | 2/2000 | Osler et al. |  | 716/6 |

|-----------|---|--------|--------------|--|-------|

|-----------|---|--------|--------------|--|-------|

### OTHER PUBLICATIONS

IBM Corporation, "Using Special Path Exclusions and Adjusts", Web pages of edition of Eins Timer: User's Guide and Reference, 4th ed., Nov. 26, 1997, 10 pages.\* Krishna P. Belkhale et al., "Timing Analysis with Known False Sub Graphs", 1995 IEEE, pp. 736–740. IBM Corporation, "Using Special Path Exclusions and Adjusts", Web pages of edition of Eins Timer: User's Guide and Reference, Fourth Edition, Nov. 26, 1997, 10 pages.

\* cited by examiner

May 22, 2001

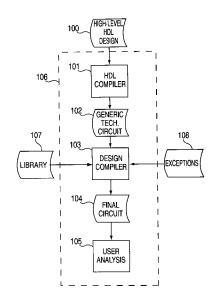

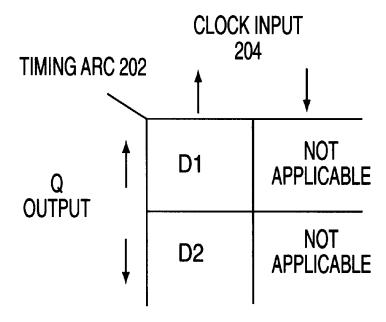

FIG. 1

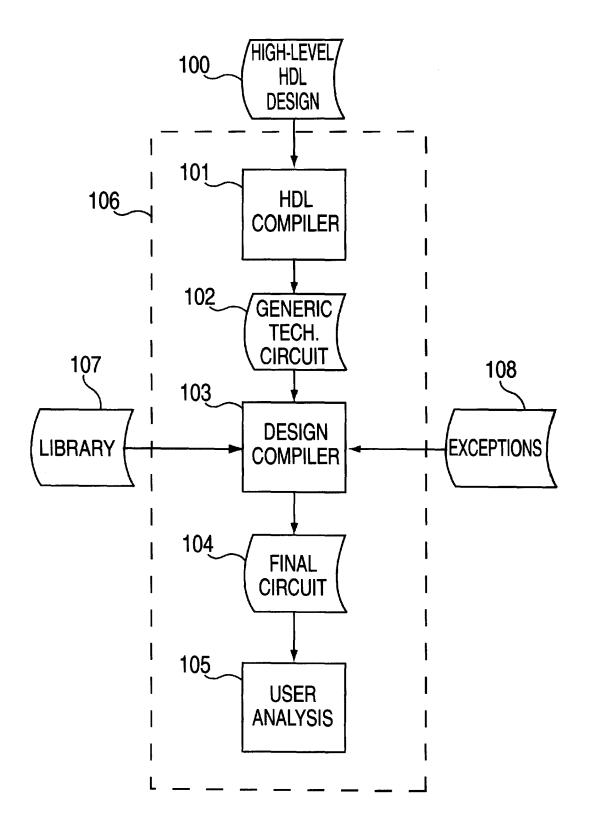

FIG. 2A

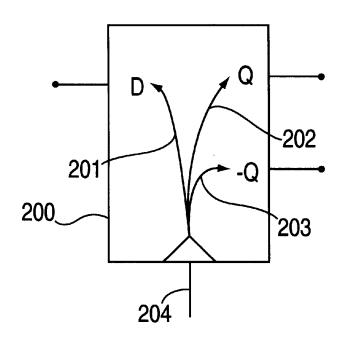

FIG. 2B

# DOCKET

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

### **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.