## EXHIBIT 1038

## U.S. PATENT NO. 5,043,820 TO WYLES

("the '820 Patent" or "WYLES")

TRW Automotive U.S. LLC: EXHIBIT 1038 PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NUMBER 8,599,001 IPR2015-00436

# United States Patent [19]

Wyles et al.

#### [54] FOCAL PLANE ARRAY READOUT EMPLOYING ONE CAPACITIVE FEEDBACK TRANSIMPEDANCE AMPLIFIER FOR EACH COLUMN

- [75] Inventors: Richard H. Wyles, Cardiff; James L. Gates, Vista; Steven D. Gaalema, Encinitas, all of Calif.

- [73] Assignee: Hughes Aircraft Company, Los Angeles, Calif.

- [21] Appl. No.: 329,229

- [22] Filed: Mar. 27, 1989

- [51] Int. Cl.<sup>5</sup> ..... H04N 5/30

- [58] Field of Search ...... 250/208.1; 358/213.12,

- 358/212, 213.28, 213.27

#### [56] References Cited

#### **U.S. PATENT DOCUMENTS**

| 3,852,714 | 12/1974 | Carson 250/208.1       |

|-----------|---------|------------------------|

| 3,949,162 | 4/1976  | Malueg 258/213.29      |

| 4,345,148 | 8/1982  | Pines et al 358/213.15 |

| 4,529,886 | 7/1985  | Yokayama et al 358/212 |

| 4,786,831 | 11/1988 | Morse et al 307/490    |

| 4,814,629 | 3/1989  | Arnold 358/105         |

#### OTHER PUBLICATIONS

Design Consideration and Performance of a new MOS Imaging Device, Haruhisa Ando, et al, IEEE Transactions on Electron Devices, vol. ED-32, No. 8, pp. 1484-1489.

A Solid State Color Video Camera with a Horizontal Readout MOS Imager, Noda et al, IEEE Transactions [11] Patent Number: 5,043,820

#### [45] Date of Patent: Aug. 27, 1991

on Consumer Electronics, vol. CE-32, No. 3, pp. 329-335.

Primary Examiner—Joseph A. Orsino Assistant Examiner—Jill Jackson Attorney, Agent, or Firm—W. C. Schubert; W. K. Denson-Low

#### ABSTRACT

[57]

A readout circuit for use with a focal plane array that employs a single transistor in each unit cell and a single capacitive feedback transimpedance amplifier to process the outputs of each column of detector elements of the array. The capacitive feedback transimpedance amplifiers extract the signals associated with the pixels along a particular row of the array. The present invention permits high performance readouts to be constructed with very little circuitry in the unit cells. Only a single minimum sized transistor switch is required in each unit cell to perform readout and reset functions for the array. In the disclosed embodiment, the readout circuit comprises an array of unit cells, each cell comprising a detector input circuit, a single transistor and a single charge storage capacitor. Row address circuits are coupled to the cells in each row of the array. A plurality of capacitive feedback transimpedance amplifiers are coupled to the cells in each column of the array. The amplifiers process charge derived from the detector elements and stored in the charge storage capacitor of each unit cell. Column multiplexing circuits multiplex the output signals provided by each of the amplifiers. Column address circuits are coupled to the column multiplexing circuits which couple output signals from each of the multiplexer circuits as the output from the readout circuit.

#### 15 Claims, 2 Drawing Sheets

# **R** M Find authenticated court documents without watermarks at docketalarm.com.

١

Α

**CKEI LARM** Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

#### FOCAL PLANE ARRAY READOUT EMPLOYING ONE CAPACITIVE FEEDBACK TRANSIMPEDANCE AMPLIFIER FOR EACH COLUMN

#### BACKGROUND

The present invention generally relates to focal plane arrays and more particularly to a focal plane array readout that employs a single capacitive feedback transimpedance amplifier for each column in the focal plane array.

Existing high performance direct readout devices for focal plane arrays generally require several transistors 15 in each unit cell, a unit cell being the circuit that stores charge from the detector elements of the focal plane array. Typically the number of transistors employed in the unit cell is four. Consequently, it is generally not possible to build monolithic focal plane arrays with 20 small unit cells and high fill factors, meaning the ratio of detector area to total unit cell area. For hybrid focal plane arrays, input circuit performance is generally compromised using such conventional circuits. Charge coupled device readouts also require large amounts of 25 space in the unit cell, and therefore have similar drawbacks.

Readout devices have been developed which require only two transistors in the unit cell. Such devices are described in a publication entitled "A Solid State Color <sup>30</sup> Video Camera with a Horizontal Readout MOS Imager," authored by Masaru Noda, et al, published in IEEE Transactions on consumer Electronics, Vol. CE-32, No. 3, August 1986. In addition to requiring more space in the unit cell this approach requires a very high <sup>35</sup> speed amplifier with low noise, a combination that is very difficult to achieve in practice.

Single transistor unit cells have been used in the past for reading out photodiode arrays. However, the reported devices have employed signal extraction circuitry, such as feedback enhanced direct injection circuits, whose noise performance is somewhat less than desirable. Typical of such single transistor unit cells are those referenced in "Design Consideration and Performance of a New MOS Imaging Device," authored by Haruhisa Ando, et al, in IEEE Transactions on Electron Devices, Vol ED-32, No. 8, August 1985.

#### SUMMARY OF THE INVENTION

In order to overcome some of the limitations of conventional focal plane readout devices, including relatively large unit cells and less than desirable circuit performance, the present invention provides for a readout device that employs a single transistor in each unit cell. In addition, a single capacitive feedback transimpedance amplifier is employed to process the outputs of each column of detector elements of the array. The capacitive feedback transimpedance amplifiers extract the signals associated with the pixels along a 60 particular row of the array.

The present invention permits high performance readouts to be constructed with very little circuitry in the unit cells. Only a single minimum sized transistor switch is required in each unit cell to perform the read- 65 out and reset functions for the array. The remaining space in the unit cell is available to achieve high detector fill factors in monolithic focal plane arrays, or im-

proved input circuit performance in hybrid focal plane arrays.

More specifically, in the disclosed embodiment, the present invention comprises a readout circuit for use 5 with a focal plane array of detector elements. The readout circuit comprises an array of unit cells, each cell comprising a detector input circuit, a single transistor and a single charge storage capacitor. A plurality of row address circuits are individually coupled to the 10 cells in a respective rows of the array. A plurality of capacitive feedback transimpedance amplifiers are individually coupled to the cells in a respective columns of the array. The amplifiers process charge derived from the detector elements and stored in the charge storage 15 capacitor of each unit cell.

A plurality of column multiplexing circuits are coupled to respective ones of the capacitive feedback transimpedance amplifiers which multiplex the output signals provided by each of the amplifiers. A plurality of column address circuits are respectively coupled to the column multiplexing circuits which couple output signals from each of the multiplexer circuits as the output from the readout circuit.

#### BRIEF DESCRIPTION OF THE DRAWING

The various features and advantages of the present invention may be more readily understood with reference to the following detailed description taken in conjunction with the accompanying drawings, wherein like reference numerals designate like structural elements, and in which:

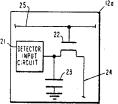

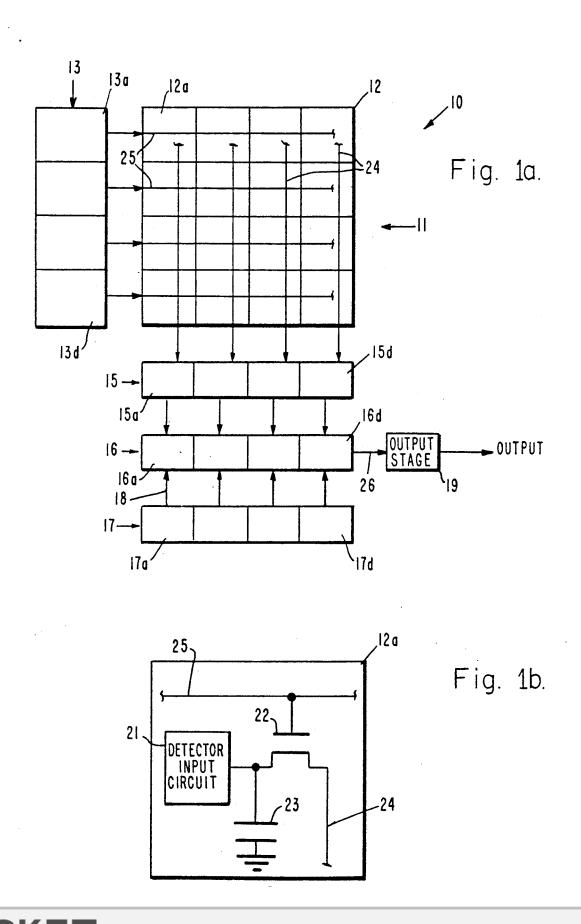

FIG. 1*a* shows a block diagram of a focal plane array readout circuit in accordance with the principles of the present invention;

FIG. 1b shows a diagram of a unit cell of the readout circuit of FIG. 1a; and

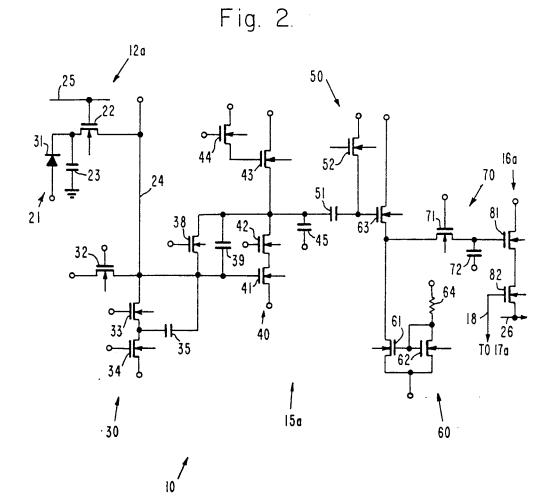

FIG. 2 shows a detailed diagram of a capacitive feedback transimpedance amplifier and unit cell employed in a focal plane array readout circuit in accordance with the principles of the present invention.

#### DETAILED DESCRIPTION

Referring to FIG. 1*a*, a block diagram of a focal plane array readout circuit 10 in accordance with the principles of the present invention is shown. The readout circuit 10 comprises an array 11 of unit cells 12, shown in FIG. 1*a* as a  $4 \times 4$  array of cells. Row address circuitry 13 comprising a plurality of row (Y) address circuits 13a-13d, are coupled to each of the cells 11 in a particular row of the array 11. The specific interconnection to the cells 12 will be described with reference to FIG. 1*b*.

With reference to FIG. 1b, a diagram of a unit cell of the readout device 10 of FIG. 1a is shown. The unit cell 12 comprises a detector input circuit 21, whose input is coupled to a detector element in the focal plane array, and whose output is coupled through a unit cell transistor 22 which operates as a switch. A charge storage capacitor 23 is coupled from a point between the detector input circuit 21 and the transistor 22 and ground. The gate of the transistor 22 is coupled to a selected row address circuit 13a-13d employed to address the row in which the particular cell 12 resides along a horizontal signal line 25. The drain of the transistor 22 is coupled to a vertical signal line 24 which couples charge out of the unit cell 12.

Referring again to FIG. 1*a*, the vertical signal lines of each column of the array are respectively coupled to

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

# API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

## LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

## FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

## E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.