#### UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_\_

#### BEFORE THE PATENT TRIAL AND APPEAL BOARD

\_\_\_\_\_\_

APPLE INC., HTC CORPORATION, HTC AMERICA, INC., SAMSUNG ELECTRONICS CO. LTD, SAMSUNG ELECTRONICS AMERICA, INC., AND AMAZON.COM, INC., Petitioners,

V.

MEMORY INTEGRITY, LLC, Patent Owner.

Case IPR2015-00163 Patent 7,296,121

\_\_\_\_\_

MOTION TO CORRECT EXHIBIT 1007 PURSUANT TO 37 C.F.R. § 42.104(c)

#### I. Introduction

37 C.F.R. § 42.104(c) provides for correction of "a clerical or typographical mistake in [a] petition" without changing the filing date of the petition. The Board routinely grants motions to correct exhibits where, as here, an inadvertent clerical mistake leads to the filing and service of an incomplete or improper exhibit. *See, e.g., Arthrex, Inc. v. Bonutti Skeletal Innovations, LLC*, IPR2013-00631, Paper 15, pp. 4-6 (P.T.A.B. Mar. 3, 2014); *ABB Inc. v. ROY-G-BIV Corp.*, Case IPR2013-00063, Paper No. 21; *Syntroleum Corp. v. Neste Oil OYJ*, IPR2013-00178, Paper 21, (P.T.A.B. Jul. 22, 2013).

As will be explained in greater detail below, an inadvertent error was made while preparing and photocopying Exhibit 1007 for filing and service. Courts have characterized "document preparation and copying documents" as "clerical" tasks. *See Spegon v. Catholic Bishop of Chicago*, 175 F. 3d 544, 553 (7th Cir. 1999). Thus, pursuant to 37 C.F.R. § 42.104(c), Petitioners seek permission to file and serve a corrected copy of Exhibit 1007 (a copy of which is attached as Exhibit D) that includes the previously missing pages cited in the Petition.

#### **II.** Statement of Facts

In seeking relief pursuant to 37 C.F.R. § 42.104(c), the Board requires the moving party to set forth a "full statement of the reasons for the relief requested," including a detailed explanation of the significance of the evidence including

material facts. 37 C.F.R. § 42.22(a)(2). This includes "what the alleged clerical error was or the circumstances of the error." *FedEx Corp v. IpVenture, Inc.*, IPR2014-00833, Paper 10, p. 3 (P.T.A.B. Oct. 24, 2014). Accordingly, the following statement of facts, supported by the Holt Declaration (Ex. A), Faeth Declaration (Ex. B), and Pantano Declaration (Ex. C), provide a full accounting of the circumstances of the clerical mistake.

On October 28, 2014, Petitioners filed four petitions for *inter partes* review of U.S. Patent No. 7,296,121, designated IPR2015-00159, -00161, -00163, and -00172. In each of IPR2015-00161, -00163, and -00172, the Petition sets forth a challenge to claims 9 and/or 10 based, in part, on Ex. 1007 (the Duato reference). In this case (i.e., IPR2015-00163), the Petition includes a description of the proposed ground of unpatentability of claims 9 and 10 based on Koster (Ex. 1009) in view of Duato (Ex. 1007), which included cites to numerous pages of Ex. 1007. *See* Petition, pp. 38-41. Similarly, the "Declaration of Dr. Robert Horst" (Ex. 1014) ("the Horst Declaration") includes a description of the combination of Koster and Duato, with cites to numerous pages of Ex. 1007. *See* Ex. 1014, ¶¶ D-20 to D-25. Both the Petition and Horst Declaration include direct quotes from and citations to pages 117 and 119 of Ex. 1007, among others.

Exhibit 1007 is a collection of excerpts from a textbook entitled "Interconnection Networks - An Engineering Approach" by Jose Duato *et al.*,

which includes over 500 pages. As filed and served, Exhibit 1007 includes approximately 140 pages of the Duato textbook, including the cover, title page, and copyright page. Exhibit 1007 was filed in two parts due to the size of the Portable Document Format (PDF) file.

Mr. David Holt (Reg. No. 65,161), an associate at Fish & Richardson, was responsible for supervising the preparation of the Petition and the accompanying exhibits for filing and service. Ex. A,  $\P \P 1$ , 2. As part of this effort, Mr. Holt was responsible for the clerical tasks of checking cites throughout the Petition and the Horst Declaration to the various exhibits, preparing an initial draft of the exhibits list, and gathering the various exhibits for preparation by Mr. Edward Faeth, a paralegal at Fish & Richardson. Ex. A,  $\P 2$ .

On October 27, 2014, in preparation for the filing and service of IPR2015-00163, Mr. Holt reviewed the Petitions for IPR2015-00161, -00163, and -00172 and the entire Horst Declaration to collect a list of all the pages of Ex. 1007 to which the Petitions and Horst Declaration cited. Ex. A, ¶ 3. Because Ex. 1007 is a large textbook and the Petitions were prepared based on the physical book, the relevant portions needed to be photocopied for filing and service. *Id.* Based on the cites included in the Petitions and Horst Declaration, Mr. Holt transcribed a list of the pages that needed to be photocopied on a sticky note, which he then attached to the front of the Duato textbook. *Id.*

Mr. Holt delivered the Duato textbook along with the sticky note to Mr. Faeth and requested that he scan the pages listed on the sticky note, electronically collate the scanned pages, and prepare the resulting electronic version of Ex. 1007 for filing and service. Ex. A,  $\P$  4; Ex. B,  $\P$  3. In preparing Ex. 1007 and all other documents related to IPR2015-00159, -00161, -00163, and -00172 for service and filing, Mr. Faeth requested the help of Ms. Sylvia Pantano, a legal secretary at Fish & Richardson, to scan the pages listed on the sticky note prepared by Mr. Holt. Ex. B,  $\P$  4; Ex. C,  $\P$  3.

Neither Mr. Holt, Mr. Faeth, nor Ms. Pantano retained a copy of the sticky note and none of them recollects whether the sticky note included pages 117 and 119 or a section encompassing these pages in the list of pages to be scanned. Ex. A, ¶ 5; Ex. B, ¶ 4; Ex. C, ¶ 5. Therefore, either Mr. Holt inadvertently did not include these pages in the list of pages to be photocopied or Ms. Pantano inadvertently did not photocopy them.

After Ms. Pantano scanned the pages included in the filed and served version of Ex. 1007, she uploaded a PDF file of the pages to a shared drive where the exhibits were being collected. Ex. C, ¶ 4 Mr. Faeth paginated and labeled the PDF file and prepared it to be electronically filed through use of the Patent Review Processing System (PRPS). Ex. B, ¶ 5. Once each of the Petitions and all exhibits were ready to be filed, Mr. Holt, Mr. Karl Renner (lead counsel) and Mr. Roberto

Devoto (backup counsel) briefly reviewed the submissions, each exceeding 1800 pages, to make sure that the Petitions reflected the latest drafts deemed ready for filing and to make sure that all corresponding exhibits were present and properly formatted. Ex. A, ¶ 6. After Mr. Holt, Mr. Renner and Mr. Devoto completed their review, Mr. Faeth attended to printing the Petitions and exhibits for service, and electronically filing the Petitions via PRPS. Ex. B, ¶ 5.

On February 13, 2015, Patent Owner filed its preliminary response. In the preliminary response, Patent Owner asserted that "Petitioners rely upon Duato's alleged disclosure of routing tables in chapter 4 and on pages 117 and 119 as allegedly disclosing the desirability of implementing routing algorithms using a routing table," and that "Ex. 1007 as filed and served by Petitioners does not contain the [se] pages." Preliminary Response, p. 39. This was the first time Patent Owner brought this clerical mistake to Petitioners' attention, and Petitioners were not aware of the clerical mistake prior to this point. *See* Ex. A, ¶ 7; Ex. B, ¶ 6; Ex. C, ¶ 6.

# III. The Inadvertent Photocopying Error is a "Clerical Mistake" for which Relief May Be Sought Pursuant to Rule 42.104(c)

Under 37 C.F.R. § 42.104(c), "[a] motion may be filed that seeks to correct a clerical or typographical mistake in the petition. The grant of such a motion does not change the filing date of the petition." "[T]his rule is remedial in nature and therefore is entitled to a liberal interpretation." *See ABB Inc. v. ROY-G-BIV Corp.*,

Case IPR2013-00063, Paper No. 21 (Decision – Motion to Correct Petition), at 7 (citing *Tcherepnin v. Knight*, 389 U.S. 332, 336 (1967)). Notably, Rule 42.104(c) "is not limited to correcting errors in previously-filed documents, but is broad enough to encompass clerical errors in uploading the documents." *Id.* at 8.

In this case, either an associate (Mr. Holt) or a legal secretary (Ms. Pantano) inadvertently made a mistake when preparing or photocopying portions of the Duato textbook for the creation of Exhibit 1007. *See* Ex. A, ¶ 5; Ex. B, ¶ 4; Ex. C, ¶ 4. In either case, the mistake made in the preparation and photocopying of Exhibit 1007 is a "clerical mistake" to which Rule 42.104(c) provides relief. Indeed, courts have characterized "document preparation and copying documents" as "clerical" tasks. *See Spegon v. Catholic Bishop of Chicago*, 175 F. 3d 544, 553 (7th Cir. 1999).

In a similar case, *Arthrex, Inc. v. Bonutti Skeletal Innovations, LLC*, IPR2013-00631, the Board correctly determined that a subordinate attorney's failure to include all pages of two exhibits was a "clerical mistake" and allowed the moving party to correct the inadvertent mistake by filing and serving copies of the two exhibits including the missing pages. *See Arthrex, Inc. v. Bonutti Skeletal Innovations, LLC*, IPR2013-00631, Paper 15, pp. 4-6 (P.T.A.B. Mar. 3, 2014). In particular, the moving party in *Arthrex* inadvertently filed English translations of

two exhibits without attaching the original foreign-language patents, as required by the Rules. *See id.* at p. 4.

As Patent Owner argues in this case, the opposing party in *Arthrex* argued that the grounds relying on the two incomplete exhibits should be dismissed for failing to meet the requirements of 35 U.S.C. § 312 and 37 C.F.R. §§ 42.6, 42.104, 42.105, and 42.106. *See id.*; *see also* Preliminary Response, pp. 39-40. In dismissing this argument, the Board determined that the opposing party's "argument that granting Arthrex's motion constitutes waiver of a statutory requirement is based on circular reasoning." *See Arthrex*, Paper 15 at p. 5. In concluding "that Arthrex's error is clerical in nature and subject to correction under 37 C.F.R. § 42.104(c)," the Board noted that it has previously:

deemed similar errors to be clerical in nature and have permitted their correction under 37 C.F.R. § 42.104(c). *See ABB, Inc. v. ROY-G-BIV Corp., IPR2013-00063*, Paper 21 at 7 (Jan. 16, 2013) (permitting petitioner to correct error of uploading the wrong exhibits with petition); *Syntoleum Corp. v. Neste Oil Oyj*, IPR2013-00178, Paper 21 at 5 (Jul. 22, 2013) (permitting petitioner to correct error of uploading incorrect exhibit with petition).

*Id.* at p. 6.

Moreover, the clerical mistake in this case is distinguishable from those cases where the Board has denied a moving party's motion to correct an exhibit

pursuant to Rule 42.104(c). For example, in *Zhongshan Broad Ocean Motor Co.*, *Ltd. v. Nidec Motor Corp.*, IPR2014-01121, the Board held that a lead counsel's failure to obtain "an attesting affidavit with the translation[]" of an exhibit was not a clerical error. *See Zhongshan Broad Ocean Motor Co., Ltd. v. Nidec Motor Corp.*, IPR2014-01121, Paper No. 20, pp. 9-12. In *Zhongshan*, the Board specifically contrasted a subordinate attorney's failure to collate available materials, which the Board had previously deemed to be a clerical mistake, with the "clear evidence that no attesting affidavit was even secured" by the lead counsel. *See id.* at p. 12. In the present case, Petitioners' inadvertent photocopying mistake is far closer in scope to a failure to properly collate already existing materials than to a lead counsel's failure to secure, much less file, all materials required by the Rules.

# IV. Any Substantive Effects on Patent Owner Due to this Clerical Mistake Have Been or Can Be Mitigated

The purpose of the filing requirements for a petition is to "give adequate notice to the Patent Owner of the basis for relief by laying out the petitioner's grounds and supporting evidence." *ABB*, IPR2013-00063, Paper No. 21 at 3 (citing Office Patent Trial Practice Guide, 77 Fed. Reg. 48756, 48763 (Aug. 14, 2012)). In this case, the Petition properly identified Exhibit 1007 as excerpts of the Duato textbook and identified by citation the pages of the Duato textbook upon which the proposed grounds of unpatentability were based. *See* Petition, pp. iii,

38-41. In fact, the Petition and the Horst Declaration each include direct quotations from the pages missing from the exhibit. *See* Petition, pp. 40-41; Ex. 1014, ¶¶ D-24, D-25. Moreover, a copy of the cover, title page, and copyright page were included in the portion of the exhibit filed and served. *See* Ex. 1007, pp. 1-3. Therefore, the Patent Owner was put on notice regarding the reference relied upon in the Petition and the specific sections and pages cited to support the proposed grounds of unpatentability.

Despite its discovery while preparing the preliminary response that certain cited pages were missing from the filed and served copy of Exhibit 1007, Patent Owner did not notify Petitioners of this clerical error until it filed the preliminary response. *See* Ex. A, ¶ 7. This decision by Patent Owner should mitigate any assertion of prejudice against Patent Owner. Patent Owner could have asked Petitioners for a copy of any portion of the Duato textbook it deemed necessary for preparation of the preliminary response, which it did not do. Alternatively, Patent Owner could have used the identifying information of the Duato textbook provided in the Petition to obtain a physical copy of the Duato textbook, a fact the Board found notable in *Arthrex* when finding a lack of prejudice to the opposing party. *See Arthrex*, IPR2013-00631, Paper 15 at p. 6, n. 2.

Moreover, to the extent that the Board still finds Petitioners' clerical mistake prejudiced Patent Owner, the prejudice can be obviated through additional

briefing. In particular, though Patent Owner has now filed its preliminary response, the Board has not yet issued its institution decision. Accordingly, once Petitioners have been permitted to correct Exhibit 1007, Petitioners would agree to a Board order permitting Patent Owner a reasonable amount of additional briefing (e.g., 3 to 5 pages) on the missing portions of Exhibit 1007. Since the institution decision is not due until May 13, 2015, there is nearly a month and a half for Patent Owner to prepare such briefing and for the Board to take it into consideration as part of its institution decision.

For at least these reasons, Petitioners respectfully submit that Petitioners' and Patent Owner's actions to this point in the proceeding should mitigate most, if not all, prejudice to Patent Owner arising from the clerical error in the preparation of Exhibit 1007, and that any remaining prejudice can be easily obviated by a limited additional brief on the missing pages.

#### V. Conclusion

The Board's precedent overwhelming supports a finding that Petitioners' inadvertent mistake when preparing or photocopying portions of the Duato textbook for the creation of Exhibit 1007 is a "clerical mistake" correctable through Rule 42.104(c). Because the prejudice to Patent Owner, if any, has been or can be mitigated, Petitioners respectfully request permission to file and serve the attached corrected version of Exhibit 1007 that includes the missing pages.

| IPR201   | 5-00163   |

|----------|-----------|

| Patent 7 | 7,296,121 |

Respectfully submitted,

Dated: 3-26-15 / Roberto J. Devoto /

Roberto Devoto, Reg. No. 55,108 W. Karl Renner, Reg. No. 41,265 Attorneys for Petitioner

#### **CERTIFICATE OF SERVICE**

Pursuant to 37 CFR §§ 42.6(e)(4)(i) *et seq.* and 42.105(b), the undersigned certifies that on March 26, 2015, a complete and entire copy of this "Motion to Correct Exhibit 1007 Pursuant to 37 C.F.R. § 42.104(c)" and all supporting exhibits were provided by electronic mail to the Patent Owner by serving the correspondence e-mail addresses of record as follows:

Jonathan D. Baker Reg. No. 45708 Farney Daniels PC 411 Borel Avenue, Suite 350 San Mateo, California 94402 Phone: 424-268-5210

jbaker@farneydaniels.com batkinson@farneydaniels.com fdlitsupport@farneydaniels.com

/Edward G. Faeth/

Edward Faeth Fish & Richardson P.C. 60 South Sixth Street, Suite 3200 Minneapolis, MN 55402 (202)-626-6420

#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re Patent of: Morton et al.

Case Nos: IPR2015-00161

U.S. Patent No.: 7,296,121

IPR2015-00163

Nov. 13, 2007 Issue Date:

IPR2015-00172

Filing Date:

Appl. Serial No.: 10/966,161 Oct. 15, 2004

Title: REDUCING PROBE TRAFFIC IN MULTIPROCESSOR SYSTEMS

#### DECLARATION OF MR. DAVID L. HOLT

- My name is David L. Holt. I am an associate at Fish & Richardson, 1. P.C., and a registered patent practitioner with the USPTO (Reg. No. 65,161).

- I assisted with the preparation and filing of the four petitions for inter 2. partes review of U.S. Patent No. 7,296,121 designated IPR2015-00159, -00161, -00163, and -00172. In particular, I was responsible for supervising the preparation of the Petitions and the accompanying exhibits for filing and service. As part of this effort, I was responsible for the clerical tasks of checking cites throughout the Petitions and the "Declaration of Dr. Robert Horst" (Ex. 1014) ("the Horst Declaration") to the various exhibits, preparing an initial draft of the exhibits list, and gathering the various exhibits for preparation by Mr. Edward Faeth, a paralegal at Fish & Richardson.

- On October 27, 2014, in preparation for the filing and service of the 3. various documents associated with IPR2015-00159, -00161, -00163, and -00172, I reviewed the Petitions for IPR2015-00159, -00161, -00163, and -00172 and the

entire Horst Declaration to collect a list of all the pages of Exhibit 1007 to which the Petitions and Horst Declaration cited. Exhibit 1007 is a collection of excerpts from a textbook entitled "Interconnection Networks - An Engineering Approach" by Jose Duato *et al.* ("the Duato textbook"), which includes over 500 pages. Because Exhibit 1007 is a large textbook and the Petitions were prepared based on a physical copy of the textbook, the relevant portions needed to be photocopied for filing and service. Based on the cites I located in the Petitions and Horst Declaration, I transcribed a list of the pages that needed to be photocopied on a sticky note, which I then attached to the front of the Duato textbook.

- 4. I delivered the Duato textbook along with the sticky note to Mr. Faeth and requested that he scan the pages listed on the sticky note, electronically collate the scanned pages, and prepare the resulting electronic version of Exhibit 1007 for filing and service. It is my understanding that Mr. Faeth worked with Ms. Sylvia Pantano, a secretary at Fish & Richardson, to scan the pages from the Duato textbook and prepare Exhibit 1007 for filing and service.

- 5. I did not retain a copy of the sticky note or any other record of the list of pages that I asked Mr. Faeth to photocopy in preparation of Exhibit 1007.

Moreover, I do not recollect whether the sticky note included pages 117 and 119 or a section encompassing these pages in the list of pages to be scanned. Therefore,

to the best of my understanding, either I inadvertently did not include these pages in the list or an error was made while scanning the excerpts of the Duato textbook.

- 6. Once Mr. Faeth informed our team that each of the Petitions and all exhibits were ready to be filed, Mr. Karl Renner (lead counsel), Mr. Roberto Devoto (backup counsel), and I briefly reviewed the submissions, each of which exceeded 1800 pages. The purpose of our review was to make sure that the Petitions reflected the latest drafts deemed ready for filing and to make sure that all corresponding exhibits were present and properly formatted. After Mr. Renner, Mr. Devoto, and I completed our review, we each notified the team of our belief that the various documents were ready for filing and service.

- 7. On February 13, 2015, Patent Owner filed and served its preliminary responses in each of IPR2015-00159, -00161, -00163, and -00172. In the preliminary responses for each of IPR2015-00161, -00163, and -00172, Patent Owner asserted that "Petitioners rely upon Duato's alleged disclosure of routing tables in chapter 4 and on pages 117 and 119 as allegedly disclosing the desirability of implementing routing algorithms using a routing table," and that "Ex. 1007 as filed and served by Petitioners does not contain the[se] pages." IPR2015-00161, Preliminary Response (Paper 13), p. 39; IPR2015-00163, Preliminary Response (Paper 13), p. 39; IPR2015-00172, Preliminary Response (Paper 11), p. 36. To the best of my knowledge, this was the first time anyone

involved with the preparation and filing of IPR2015-00159, -00161, -00163, and -00172 became aware of this clerical mistake.

8. I hereby declare that all statements made herein of my own knowledge are true and that all statements made on information and belief are believed to be true; and further that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of Title 18 of the United States Code.

Signature:

David L. Holt (Reg. No 65,161)

Date: 03/26/2015

#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re Patent of: Morton et al.

Case Nos: IPR2015-00161

U.S. Patent No.: 7,296,121 IPR2015-00163

Issue Date:

Nov. 13, 2007

IPR2015-00172

Appl. Serial No.: 10/966,161

Oct. 15, 2004 Filing Date:

Title: REDUCING PROBE TRAFFIC IN MULTIPROCESSOR SYSTEMS

#### DECLARATION OF MR. EDWARD G. FAETH

- My name is Edward G. Faeth. I am a paralegal at Fish & Richardson, 1. P.C.

- I assisted with the preparation and filing of the four petitions for inter 2. partes review of U.S. Patent No. 7,296,121 designated IPR2015-00159, -00161, -00163, and -00172. In particular, I was responsible for the preparation of the Petitions and the accompanying exhibits for filing and service. As part of this effort, I was responsible for ensuring the proper formatting of the petitions, ensuring all of the exhibits had been gathered, labeling and paginating the exhibits in accordance with the USPTO's rules, electronically filing the petitions and accompanying exhibits, and printing and mailing service copies of the petitions and exhibits.

- On October 27, 2014, during preparation for the filing and service of 3. the various documents associated with IPR2015-00159, -00161, -00163, and -00172, Mr. David Holt, an associate at Fish & Richardson, provided me with a

textbook entitled "Interconnection Networks - An Engineering Approach" by Jose Duato *et al.* ("the Duato textbook"). Attached to the Duato textbook was a sticky note that included a list of pages that Mr. Holt informed me need to be scanned and electronically collated into Exhibit 1007.

- 4. As I was responsible for preparing all documents related to IPR2015-00159, -00161, -00163, and -00172 for service and filing including Exhibit 1007, I requested the help of Ms. Sylvia Pantano, a legal secretary at Fish & Richardson, to scan the pages listed on the sticky note prepared by Mr. Holt. I did not retain a copy of the sticky note prepared by Mr. Holt or any other record of the list of pages that I was asked to photocopy in preparation of Exhibit 1007. Moreover, though I recall reviewing the scanned pages for accuracy, I do not specifically recollect whether the sticky note included pages 117 and 119 or a section encompassing these pages in the list of pages to be scanned. Therefore, to the best of my understanding, either Mr. Holt did not include these pages in the list or an inadvertent error was made while scanning and preparing the excerpts of the Duato textbook.

- 5. After Ms. Pantano scanned the pages included in the filed and served version of Ex. 1007, she informed me that she had uploaded a PDF file of the pages to a shared drive where the exhibits were being collected. I paginated and labeled the PDF file and prepared it to be electronically filed through use of the

Patent Review Processing System (PRPS). It is my understanding that Mr. Karl Renner (lead counsel), Mr. Roberto Devoto (backup counsel), and Mr. Holt briefly reviewed the submissions, each of which exceeded 1800 pages. After Mr. Renner, Mr. Devoto, and Mr. Holt completed their review, each notified the team of his belief that the various documents were ready for filing and service. Thereafter, Mr. Renner signed each of the Petitions. I uploaded each of the signed Petitions, the related exhibits, and a power of attorney from our client to PRPS, and took steps necessary to electronically file these documents. Furthermore, I printed copies of the signed Petitions, the related exhibits, and the power of attorney from our client and took steps necessary to serve these documents to Patent Owner via Federal Express.

6. On February 13, 2015, Patent Owner filed and served its preliminary responses in each of IPR2015-00159, -00161, -00163, and -00172. In the preliminary responses for each of IPR2015-00161, -00163, and -00172, Patent Owner asserted that "Petitioners rely upon Duato's alleged disclosure of routing tables in chapter 4 and on pages 117 and 119 as allegedly disclosing the desirability of implementing routing algorithms using a routing table," and that "Ex. 1007 as filed and served by Petitioners does not contain the[se] pages." IPR2015-00161, Preliminary Response (Paper 13), p. 39; IPR2015-00163, Preliminary Response (Paper 13), p. 39; IPR2015-00172, Preliminary Response

(Paper 11), p. 36. To the best of my knowledge, this was the first time anyone involved with the preparation and filing of IPR2015-00159, -00161, -00163, and -00172 became aware of this clerical mistake.

7. I hereby declare that all statements made herein of my own knowledge are true and that all statements made on information and belief are believed to be true; and further that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of Title 18 of the United States Code.

Signature:

Edward G. Faeth

Date: 3/26/15

#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re Patent of: Morton et al. Case Nos: IPR2015-00161

U.S. Patent No.: 7,296,121 IPR2015-00163

Issue Date: Nov. 13, 2007 IPR2015-00172 Appl. Serial No.: 10/966,161

Filing Date: Oct. 15, 2004

Title: REDUCING PROBE TRAFFIC IN MULTIPROCESSOR SYSTEMS

#### **DECLARATION OF MS. SYLVIA PANTANO**

- 1. My name is Sylvia Pantano. I am a legal secretary at Fish & Richardson, P.C.

- 2. I assisted with the preparation and filing of the four petitions for *inter* partes review of U.S. Patent No. 7,296,121 designated IPR2015-00159, -00161, -00163, and -00172. In particular, I assisted Mr. Edward Faeth, a paralegal at Fish & Richardson, with the preparation of exhibits for filing and service.

- 3. On October 27, 2014, during preparation for the filing and service of the various documents associated with IPR2015-00159, -00161, -00163, and -00172, Mr. Faeth, provided me with a textbook entitled "Interconnection Networks An Engineering Approach" by Jose Duato *et al.* ("the Duato textbook"). Attached to the Duato textbook was a sticky note that included a list of pages that Mr. Faeth informed me needed to be scanned and electronically collated into Exhibit 1007.

- 4. Per Mr. Faeth's instructions, I scanned the pages listed on the sticky note and created a Portable Document Format (PDF) file containing the pages I scanned. I uploaded the PDF file to a shared drive and informed Mr. Faeth where the PDF file was stored so that he could finalize its preparation for filing and service.

- 5. I did not retain a copy of the sticky note attached to the Duato textbook or any other record of the list of pages that I was asked to photocopy in preparation of Exhibit 1007. Moreover, though I recall reviewing the scanned pages for accuracy, I do not specifically recollect whether the sticky note included pages 117 and 119 or a section encompassing these pages in the list of pages to be scanned. Therefore, to the best of my understanding, either the sticky note did not include these pages in the list, or I made an inadvertent error while scanning the excerpts of the Duato textbook and creating the PDF file.

- 6. On February 13, 2015, Patent Owner filed and served its preliminary responses in each of IPR2015-00159, -00161, -00163, and -00172. In the preliminary responses for each of IPR2015-00161, -00163, and -00172, Patent Owner asserted that "Petitioners rely upon Duato's alleged disclosure of routing tables in chapter 4 and on pages 117 and 119 as allegedly disclosing the desirability of implementing routing algorithms using a routing table," and that "Ex. 1007 as filed and served by Petitioners does not contain the [se] pages."

IPR2015-00161, Preliminary Response (Paper 13), p. 39; IPR2015-00163, Preliminary Response (Paper 13), p. 39; IPR2015-00172, Preliminary Response (Paper 11), p. 36. To the best of my knowledge, this was the first time anyone involved with the preparation and filing of IPR2015-00159, -00161, -00163, and -00172 became aware of this clerical mistake.

7. I hereby declare that all statements made herein of my own knowledge are true and that all statements made on information and belief are believed to be true; and further that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 of Title 18 of the United States Code.

Signature:

Sylvia Pantano

Date:

APPLE 1007

## Interconnection Networks

## An Engineering Approach

José Duato Sudhakar Yalamanchili Lionel Ni

Los Alamitos, California

Washington

Brussels

Tokyo

#### Library of Congress Cataloging-in-Publication Data

Duato, José

Interconnection networks: an engineering approach / José Duato, Sudhakar Yalamanchili, Lionel Ni.

cm.

Includes bibliographical references.

ISBN 0-8186-7800-3

Computer networks.

Multiprocessors.

II. Ni, Lionel M. IEI HIMEANDFORD FLEWING.

I. Yalamanchili.

TK5105.5.D88 1997

COLLEGE BREALEY LIBRARY

97-20502

004.6-dc21

AUG 1 3 1998

CIP

Copyright © 1997 by The Institute of Electrical and Electronics Engineers, Inc. All rights reserved.

Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy isolated pages beyond the limits of US copyright law, for private use of their patrons. Other copying, reprint, or republication requests should be addressed to: IEEE Copyrights Manager, IEEE Service Center, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331.

#### IEEE Computer Society Press Order Number BP07800 Library of Congress Number 97-20502 ISBN 0-8186-7800-3

#### Additional copies may be ordered from:

IEEE Computer Society Press Customer Service Center 10662 Los Vaqueros Circle P.O. Box 3014

Los Alamitos, CA 90720-1314 Tel: +1-714-821-8380

Fax: +1-714-821-4641 Email: cs.books@computer.org IEEE Service Center 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 Tel: +1-908-981-1393 Fax: +1-908-981-9667

B-1200 Brussels BELGIUM Tel: +32-2-770-2198 Fax: +32-2-770-8505 mis.custserv@computer.org euro.ofc@computer.org

IEEE Computer Society

13, Avenue de l'Aquilon

**IEEE Computer Society** Ooshima Building 2-19-1 Minami-Aoyama Minato-ku, Tokyo 107 JAPAN Tel: +81-3-3408-3118 Fax: +81-3-3408-3553 tokyo.ofc@computer.org

Editor-in-Chief: Mohamed Fayad Publisher: Matt Loeb Acquisitions Editor: Bill Sanders Developmental Editor: Cheryl Baltes Advertising/Promotions: Tom Fink Production Editor: Lisa O'Conner Cover Artist: John Marshall

About the cover: Interconnection Networks by John Marshall, oil on canvass, 1997, is based on a concept by José Duato. The painting includes symbols representing important elements in the field. To find out more about the symbols in the painting, visit the book's website at http://computer.org/books.

Printed in the United States of America

## Chapter 1

### Introduction

Interconnection networks are currently being used for many different applications, ranging from internal buses in very large-scale integration (VLSI) circuits to wide area computer networks. Among others, these applications include backplane buses and system area networks, telephone switches, internal networks for asynchronous transfer mode (ATM) switches, processor/memory interconnects for vector supercomputers, interconnection networks for multicomputers and distributed shared-memory multiprocessors, clusters of workstations, local area networks, metropolitan area networks, wide area computer networks, and networks for industrial applications. Additionally, the number of applications requiring interconnection networks is continuously growing. For example, an integral control system for a car requires a network connecting several microprocessors and devices.

The characteristics and cost of these networks considerably depend on the application. There are no general solutions. For some applications, interconnection networks have been studied in depth for decades. This is the case for telephone networks, computer networks, and backplane buses. These networks are covered in many books. However, there are some other applications that have not been fully covered in the existing literature. This is the case for the interconnection networks used in multicomputers and distributed shared-memory multiprocessors.

The lack of standards and the need for very high performance and reliability pushed the development of interconnection networks for multicomputers. This technology was transferred to distributed shared-memory multiprocessors, improving the scalability of those machines. However, distributed shared-memory multiprocessors require an even higher network performance than multicomputers, pushing the development of interconnection networks even more. More recently, this network technology began to be transferred to local area networks (LANs). Also, it has been proposed as a replacement for backplane buses, creating the concept of system area network. Hence, the advances in interconnection networks for multicomputers are the basis for the development of interconnection networks for other architectures and environments. Therefore, there is a need for structuring the concepts and solutions for this kind of interconnection networks. Obviously, when this technology is transferred to another environment, new issues arise that have to be addressed.

Moreover, several of these networks are evolving very quickly, and the solutions proposed for different kinds of networks are overlapping. Thus, there is a need for formally stating the basic concepts, the alternative design choices, and the design trade-offs for most of those networks. In this book, we take that challenge and present in a structured way the basic underlying concepts of most interconnection networks, as well as the most interesting solutions currently implemented or proposed in the literature. As indicated above, the network technology developed for multicomputers has been transferred to other environments. Therefore, in this book we will mainly describe techniques

developed for multicomputer networks. Most of these techniques can also be applied to distributed shared-memory multiprocessors, and to local and system area networks. However, we will also describe techniques specifically developed for these environments.

#### 1.1 Parallel Computing and Networks

The demand for even more computing power has never stopped. Although the performance of processors has doubled in approximately every three-year span from 1980 to 1996, the complexity of the software as well as the scale and solution quality of applications have continuously driven the development of even faster processors. A number of important problems have been identified in the areas of defense, aerospace, automotive applications, and science, whose solution requires tremendous amount of computational power. In order to solve these grand challenge problems, the goal has been to obtain computer systems capable of computing at the teraflops (10<sup>12</sup> floating-point operations per second) level. Even the smallest of these problems requires gigaflops (10<sup>9</sup> floating-point operations per second) of performance for hours at a time. The largest problems require

teraflops performance for more than a thousand hours at a time.

Parallel computers with multiple processors are opening the door to teraflops computing performance to meet the increasing demand of computational power. The demand includes more computing power, higher network and input/output (I/O) bandwidths, and more memory and storage capacity. Even for applications requiring a lower computing power, parallel computers can be a cost-effective solution. Processors are becoming very complex. As a consequence, processor design cost is growing so fast that only a few companies all over the world can afford to design a new processor. Moreover, design cost should be amortized by selling a very high number of units. Currently, personal computers and workstations dominate the computing market. Therefore, designing custom processors that boost the performance one order of magnitude is not cost-effective. Similarly, designing and manufacturing high-speed memories and disks is not cost-effective. The alternative choice consists of designing parallel computers from commodity components (processors, memories, disks, interconnects, etc.). In these parallel computers, several processors cooperate to solve a large problem. Memory bandwidth can be scaled with processor computing power by physically distributing memory components among processors. Also, redundant arrays of inexpensive disks (RAID) allow the implementation of high-capacity reliable parallel file systems meeting the performance requirements of parallel computers.

However, a parallel computer requires some kind of communication subsystems to interconnect processors, memories, disks and other peripherals. The specific requirements of these communication subsystems depend on the architecture of the parallel computer. The simplest solution consists of connecting processors to memories and disks as if there were a single processor, using system buses and I/O buses. Then, processors can be interconnected using the interfaces to local area networks. Unfortunately, commodity communication subsystems have been designed to meet a different set of requirements, i.e., those arising in computer networks. Although networks of workstations have been proposed as an inexpensive approach to build parallel computers, the communication subsystem

becomes the bottleneck in most applications.

Therefore, designing high-performance interconnection networks becomes a critical issue to exploit the performance of parallel computers. Moreover, as the interconnection network is the only subsystem that cannot be efficiently implemented by using commodity components, its design becomes very critical. This issue motivated the writing of this book. Up to now, most manufacturers designed custom interconnection networks (nCUBE-2, nCUBE-3, Intel Paragon, Cray T3D, Cray T3E, Thinking Machines Corp. CM-5, NEC Cenju-3, IBM SP2). More recently, several high-

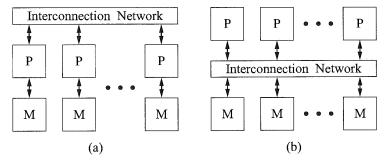

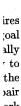

Figure 1.1. Schematic representation of parallel computers: (a) A multicomputer. (b) A UMA shared-memory multiprocessor. (M = memory; P = processor.)

performance switches have been developed (Autonet, Myrinet, ServerNet) and are being marketed. These switches are targeted to workstations and personal computers, offering the customer the possibility of building an inexpensive parallel computer by connecting cost-effective computers through high-performance switches. The main issues arising in the design of networks for both approaches are covered in this book.

#### 1.2 Parallel Computer Architectures

1

y

'S

In this section, we briefly introduce the most popular parallel computer architectures. This description will focus on the role of the interconnection network. A more detailed description is beyond the scope of this book.

The idea of using commodity components for the design of parallel computers led to the development of distributed-memory multiprocessors, or multicomputers in early 1980s. These parallel computers consist of a set of processors, each one connected to its own local memory. Processors communicate between them by passing messages through an interconnection network. Figure 1.1a shows a simple scheme for this architecture. The first commercial multicomputers utilized commodity components, including Ethernet controllers to implement communication between processors. Unfortunately, commodity communication subsystems were too slow, and the interconnection network became the bottleneck of those parallel computers. Several research efforts led to the development of interconnection networks that are several orders of magnitude faster than Ethernet networks. Most of the performance gain is due to architectural rather than technological improvements.

Programming multicomputers is not an easy task. The programmer has to take care of distributing code and data among the processors in an efficient way, invoking message-passing calls whenever some data are needed by other processors. On the other hand, shared-memory multiprocessors provide a single memory space to all the processors, simplifying the task of exchanging data among processors. Access to shared memory has been traditionally implemented by using an interconnection network between processors and memory (Figure 1.1b). This architecture is referred to as uniform memory access (UMA) architecture. It is not scalable because memory access time includes the latency of the interconnection network, and this latency increases with system size.

More recently, shared-memory multiprocessors followed some trends previously established for multicomputers. In particular, memory has been physically distributed among processors, therefore reducing the memory access time for local accesses and increasing scalability. These parallel computers are referred to as distributed shared-memory multiprocessors (DSM). Accesses to remote memory

are performed through an interconnection network, very much like in multicomputers. The main difference between DSMs and multicomputers is that messages are initiated by memory accesses rather than by calling a system function. In order to reduce memory latency, each processor has several levels of cache memory, thus matching the speed of processors and memories. This architecture provides nonuniform memory access (NUMA) time. Indeed, most of the nonuniformity is due to the different access time between caches and main memories, rather than the different access time between local and remote memories. The main problem arising in DSMs is cache coherence. Several hardware and software cache coherence protocols have been proposed. These protocols produce additional traffic through the interconnection network.

The use of custom interconnects makes multicomputers and DSMs quite expensive. So, networks of workstations (NOW) have been proposed as an inexpensive approach to build parallel computers. NOWs take advantage of recent developments in LANs. In particular, the use of ATM switches has been proposed to implement NOWs. However, ATM switches are still expensive, which has motivated the development of high-performance switches, specifically designed to provide a cost-effective interconnect for workstations and personal computers.

Although there are many similarities between interconnection networks for multicomputers and DSMs, it is important to keep in mind that performance requirements may be very different. Messages are usually very short when DSMs are used. Additionally, network latency is important because memory access time depends on that latency. However, messages are typically longer and less frequent when using multicomputers. Usually the programmer is able to adjust the granularity of message communication in a multicomputer. On the other hand, interconnection networks for multicomputers and NOWs are mainly used for message passing. However, the geographical distribution of workstations usually imposes constraints on the way processors are connected. Also, individual processors may be connected to or disconnected from the network at any time, thus imposing additional design constraints.

#### 1.3 Network Design Considerations

Interconnection networks play a major role in the performance of modern parallel computers. There are many factors that may affect the choice of an appropriate interconnection network for the underlying parallel computing platform. These factors include:

- 1. Performance requirements. Processes executing in different processors synchronize and communicate through the interconnection network. These operations are usually performed by explicit message passing or by accessing shared variables. Message latency is the time elapsed between the time a message is generated at its source node and the time the message is delivered at its destination node. Message latency directly affects processor idle time and memory access time to remote memory locations. Also, the network may saturate it may be unable to deliver the flow of messages injected by the nodes, limiting the effective computing power of a parallel computer. The maximum amount of information delivered by the network per time unit defines the throughput of that network.

- 2. Scalability. A scalable architecture implies that as more processors are added, their memory bandwidth, I/O bandwidth, and network bandwidth should increase proportionally. Otherwise the components whose bandwidth does not scale may become a bottleneck for the rest of the system, decreasing the overall efficiency accordingly.

- 3. Incremental expandability. Customers are unlikely to purchase a parallel computer with a full set of processors and memories. As the budget permits, more processors and memories may be

1

1

t

1

r

е

e

d

y

e

ıf

е

y

e

æ

11

added until a system's maximum configuration is reached. In some interconnection networks, the number of processors must be a power of 2, which makes them difficult to expand. In other cases, expandability is provided at the cost of wasting resources. For example, a network designed for a maximum size of 1,024 nodes may contain many unused communication links when the network is implemented with a smaller size. Interconnection networks should provide incremental expandability, allowing the addition of a small number of nodes while minimizing resource wasting.

- 4. Partitionability. Parallel computers are usually shared by several users at a time. In this case, it is desirable that the network traffic produced by each user does not affect the performance of other applications. This can be ensured if the network can be partitioned into smaller functional subsystems. Partitionability may also be required for security reasons.

- 5. Simplicity. Simple designs often lead to higher clock frequencies and may achieve higher performance. Additionally, customers appreciate networks that are easy to understand because it is easier to exploit their performance.

- 6. Distance span. This factor may lead to very different implementations. In multicomputers and DSMs, the network is assembled inside a few cabinets. The maximum distance between nodes is small. As a consequence, signals are usually transmitted using copper wires. These wires can be arranged regularly, reducing the computer size and wire length. In NOWs, links have very different lengths and some links may be very long, producing problems such as coupling, electromagnetic noise, and heavy link cables. The use of optical links solves these problems, equalizing the bandwidth of short and long links up to a much greater distance than when copper wire is used. Also, geographical constraints may impose the use of irregular connection patterns between nodes, making distributed control more difficult to implement.

- 7. Physical constraints. An interconnection network connects processors, memories, and/or I/O devices. It is desirable for a network to accommodate a large number of components while maintaining a low communication latency. As the number of components increases, the number of wires needed to interconnect them also increases. Packaging these components together usually requires meeting certain physical constraints, such as operating temperature control, wiring length limitation, and space limitation. Two major implementation problems in large networks are the arrangement of wires in a limited area, and the number of pins per chip (or board) dedicated to communication channels. In other words, the complexity of the connection is limited by the maximum wire density possible, and by the maximum pin count. The speed at which a machine can run is limited by the wire lengths, and the majority of the power consumed by the system is used to drive the wires. This is an important and challenging issue to be considered. Different engineering technologies for packaging, wiring, and maintenance should be considered.

- 8. Reliability and repairability. An interconnection network should be able to deliver information reliably. Interconnection networks can be designed for continuous operation in the presence of a limited number of faults. These networks are able to send messages through alternative paths when some faults are detected. In addition to reliability, interconnection networks should have a modular design, allowing hot upgrades and repairs. Nodes can also fail or be removed from the network. In particular, a node can be powered off in a network of workstations. Thus, NOWs usually require some reconfiguration algorithm for the automatic reconfiguration of the network when a node is powered on or off.

- 9. Expected workloads. Users of a general-purpose machine may have very different requirements. If the kind of applications that will be executed in the parallel computer are known in advance, it may be possible to extract some information on usual communication patterns, message sizes, network load, etc. That information can be used for the optimization of some design parameters. When it is not possible to get information on expected workloads, network design should be robust, i.e., design parameters should be selected in such a way that performance is good over a wide range of traffic conditions.

- 10. Cost constraints. Finally, it is obvious that the "best" network may be too expensive. Design decisions very often are trade-offs between cost and other design factors. Fortunately, cost is not always directly proportional to performance. Using commodity components whenever possible may considerably reduce the overall cost.

## 1.4 Classification of Interconnection Networks

Among other criteria, interconnection networks have been traditionally classified according to the operating mode (synchronous or asynchronous), and network control (centralized, decentralized, or distributed). Nowadays, multicomputers, multiprocessors, and NOWs dominate the parallel computing market. All of these architectures implement asynchronous networks with distributed control. Therefore, we will focus on other criteria that are currently more significant.

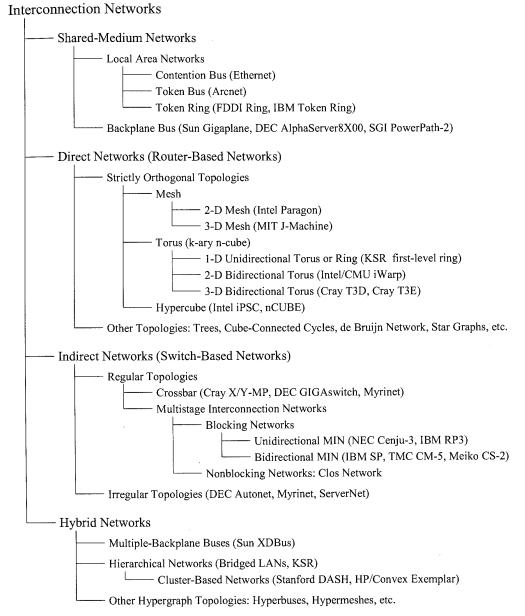

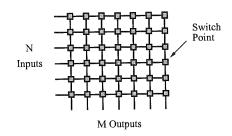

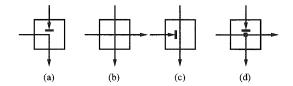

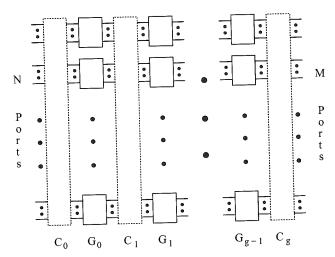

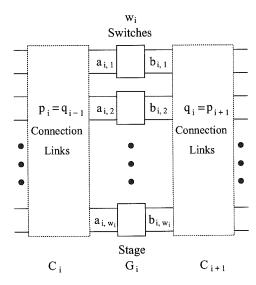

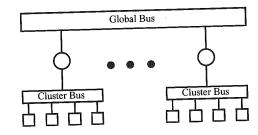

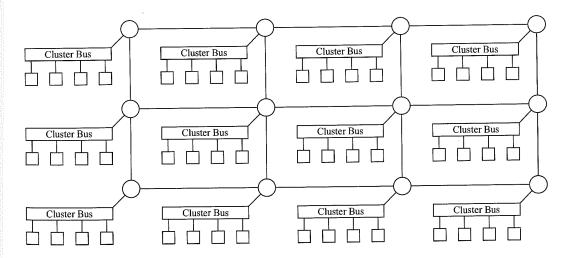

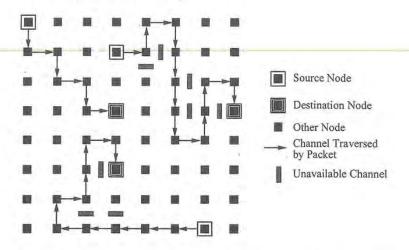

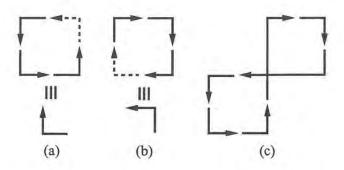

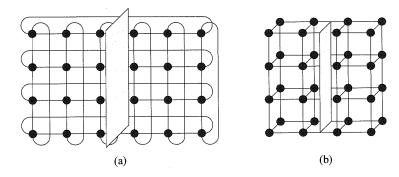

A classification scheme is shown in Figure 1.2 which categorizes the known interconnection networks into four major classes based primarily on network topology: shared-medium networks, direct networks, indirect networks, and hybrid networks. For each class, the figure shows a hierarchy of subclasses, also indicating some real implementations for most of them. This classification scheme is based on the classification proposed in [252], and it mainly focuses on networks that have been implemented. It is by no means complete as other new and innovative interconnection networks may emerge as technology further advances, such as mobile communication and optical interconnections.

In shared-medium networks, the transmission medium is shared by all communicating devices. An alternative to this approach consists of having point-to-point links directly connecting each communicating device to a (usually small) subset of other communicating devices in the network. In this case, any communication between nonneighboring devices requires transmitting the information through several intermediate devices. These networks are known as direct networks. Instead of directly connecting the communicating devices between them, indirect networks connect those devices by means of one or more switches. If several switches exist, they are connected between them using point-to-point links. In this case, any communication between communicating devices requires transmitting the information through one or more switches. Finally, hybrid approaches are possible. These network classes and the corresponding subclasses will be described in the following sections.

# 1.5 Shared-Medium Networks

The least complex interconnect structure is one in which the transmission medium is shared by all communicating devices. In such *shared-medium networks*, only one device is allowed to use the network at a time. Every device attached to the network has requester, driver, and receiver circuits to handle the passing of address and data. The network itself is usually passive, since the network itself does not generate messages.

Figure 1.2. Classification of interconnection networks. (1-D = one-dimensional; 2-D = two-dimensional; 3-D = three-dimensional; CMU = Carnegie Mellon University; DASH = Directory Architecture for Shared-Memory; DEC = Digital Equipment Corp.; FDDI = Fiber Distributed Data Interface; HP = Hewlett-Packard; KSR = Kendall Square Research; MIN = Multistage Interconnection Network; MIT = Massachusetts Institute of Technology; SGI = Silicon Graphics Inc.; TMC = Thinking Machines Corp.)

An important issue here is the arbitration strategy that determines the mastership of the shared-medium network to resolve network access conflicts. A unique characteristic of a shared medium is its ability to support atomic broadcast in which all devices on the medium can monitor network activities and receive the information transmitted on the shared medium. This property is important to efficiently support many applications requiring one-to-all or one-to-many communication services, such as barrier synchronization and snoopy cache coherence protocols. Due to limited network bandwidth, a single shared medium can only support limited number of devices before the medium becomes a bottleneck.

Shared-medium networks constitute a well established technology. Additionally, their limited bandwidth restricts their use in multiprocessors. So, these networks will not be covered in this book, but we will present a short introduction in the following sections. There are two major classes of shared-medium networks: local area networks, mainly used to construct computer networks that span physical distances no longer than a few kilometers, and backplane buses, mainly used for internal communication in uniprocessors and multiprocessors.

# 1.5.1 Shared-Medium Local Area Networks

High-speed LANs can be used as a networking backbone to interconnect computers to provide an integrated parallel and distributed computing environment. Physically, a shared-medium LAN uses copper wires or fiber optics in a bit-serial fashion as the transmission medium. The network topology is either a bus or a ring. Depending on the arbitration mechanism used, different LANs have been commercially available. For performance and implementation reasons, it is impractical to have a centralized control or to have some fixed access assignment to determine the bus master who can access the bus. Three major classes of LANs based on distributed control are described below.

#### Contention Bus

The most popular bus arbitration mechanism is to have all devices to compete for the exclusive access right of the bus. Due to the broadcast nature of the bus, all devices can monitor the state of the bus, such as idle, busy, and collision. Here the term "collision" means that two or more devices are using the bus at the same time and their data collided. When the collision is detected, the competing devices will quit transmission and try later. The most well-known contention-based LAN is Ethernet which adopts carrier-sense multiple access with collision detection (CSMA/CD) protocol. The bandwidth of Ethernet is 10 Mbps and the distance span is 250 meters (coaxial cable). As processors are getting faster, the number of devices that can be connected to Ethernet is limited to avoid the network bottleneck. In order to break the 10 Mbps bandwidth barrier, Fast Ethernet can provide 100 Mbps bandwidth.

#### Token Bus

One drawback of the contention bus is its nondeterministic nature as there is no guarantee of how much waiting time is required to gain the bus access right. Thus, the contention bus is not suitable to support real-time applications. To remove the nondeterministic behavior, an alternate approach involves passing a token among the network devices. The owner of the token has the right to access the bus. Upon completion of the transmission, the token is passed to the next device based on some scheduling discipline. By restricting the maximum token holding time, the upper bound that a device has to wait for the token can be guaranteed. Arcnet supports token bus with a bandwidth of 2.5 Mbps.

Figure 1.3. A single-bus network. (M = memory; P = processor.)

#### Token Ring

The idea of token ring is a natural extension of token bus as the passing of the token forms a ring structure. IBM token ring supports bandwidths of both 4 and 16 Mbps based on coaxial cable. Fiber Distributed Data Interface (FDDI) provides a bandwidth of 100 Mbps using fiber optics.

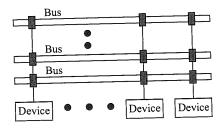

## 1.5.2 Shared-Medium Backplane Bus

A backplane bus is the simplest interconnection structure for bus-based parallel computers. It is commonly used to interconnect processor(s) and memory modules to provide UMA architecture. Figure 1.3 shows a single-bus network. A typical backplane bus usually has 50 – 300 wires and is physically realized by printed lines on a circuit board or by discrete (backplane) wiring. Additional costs are incurred by interface electronics, such as line drivers, receivers, and connectors.

There are three kinds of information in the backplane bus: data, address, and control signals. Control signals include bus request signal and request grant signal, among many others. In addition of the width of data lines, the maximum bus bandwidth that can be provided is dependent on the technology. The number of processors that can be put on a bus depends on many factors, such as processor speed, bus bandwidth, cache architecture, and program behavior.

#### Methods of Information Transfer

Both data and address information must be carried in the bus. In order to increase the bus bandwidth and provide a large address space, both data width and address bits have to be increased. Such an increase implies another increase in the bus complexity and cost. Some designs try to share address and data lines. For *multiplexed transfer*, address and data are sent alternatively. Hence, they can share the same physical lines and require less power and fewer chips. For *nonmultiplexed transfer*, address and data lines are separated. Thus, data transfer can be done faster.

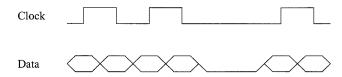

In synchronous bus design, all devices are synchronized with a common clock. It requires less complicated logic and has been used in most existing buses. However, a synchronous bus is not easily upgradable. New faster processors are difficult to fit into a slow bus.

In asynchronous buses, all devices connected to the bus may have different speeds and their own clocks. They use a handshaking protocol to synchronize with each other. This provides independence for different technologies and allows slower and faster devices with different clock rates to operate together. This also implies buffering is needed, since slower devices cannot handle messages as fast as faster devices.

#### Bus Arbitration

1

t

h

In a single-bus network, several processors may attempt to use the bus simultaneously. To deal with this, a policy must be implemented that allocates the bus to the processors making such requests. For performance reasons, bus allocation must be carried out by hardware arbiters. Thus, in order to perform a memory access request, the processor has to exclusively own the bus and become the bus

master. To become the bus master, each processor implements a bus requester, which is a collection of logic to request control of the data transfer bus. On gaining control, the requester notifies the requesting master.

Two alternative strategies are used to release the bus:

- Release-when-done: release the bus when data transfer is done

- Release-on-request: hold the bus until another processor requests it

Several different bus arbitration algorithms have been proposed, which can be classified into centralized or distributed. A centralized method has a central bus arbiter. When a processor wants to become the bus master, it sends out a bus request to the bus arbiter which then sends out a request grant signal to the requesting processor. A bus arbiter can be an encoder-decoder pair in hardware design. In distributed method, such as daisy chain method, there is no central bus arbiter. The bus request signals form a daisy chain. The mastership is released to the next device when data transfer is done.

#### Split Transaction Protocol

Most bus transactions involve request and response. This is the case for memory read operations. After a request is issued, it is desirable to have a fast response. If a fast response time is expected, the bus mastership is not released after sending the request, and data can be received soon. However, due to memory latency, the bus bandwidth is wasted while waiting for a response. In order to minimize the waste of bus bandwidth, the *split transaction protocol* has been used in many bus networks.

In this protocol, the bus mastership is released immediately after the request, and the memory has to gain mastership before it can send the data. Split transaction protocol has a better bus utilization but its control unit is much more complicated. *Buffering* is needed in order to save messages before the device can gain the bus mastership.

To support shared-variable communication, some atomic read/modify/write operations to memories are needed. With the split transaction protocol, the atomic read/modify/write can no longer be indivisible. One approach to solve this problem is to disallow bus release for those atomic operations.

#### **Bus Examples**

Several examples of buses and the main characteristics are listed below.

- Gigaplane used in Sun Ultra Enterprise X000 Server (ca. 1996): 2.6 Gbyte/s peak, 256 bits data, 42 bits address, split-transaction protocol, 83.8 MHz clock.

- DEC AlphaServer8X00, i.e., 8200 and 8400 (ca. 1995): 2.1 Gbyte/s, 256 bits data, 40 bits address, split-transaction protocol, 100 MHz clock (1 foot length).

- SGI PowerPath-2 (ca. 1993): 1.2 Gbyte/s, 256 bits data, 40 bits address, 6 bits control, split-transaction protocol, 47.5 MHz clock (1 foot length).

- HP9000 Multiprocessor Processor Memory Bus (ca. 1993): one Gbyte/s, 128 bits data, 64 bits address, 13 inches, pipelined-bus, 60 MHz clock.

е

ïS

S

1,

ts

#### 1.6 Direct Networks

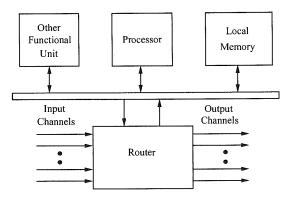

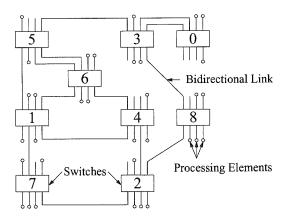

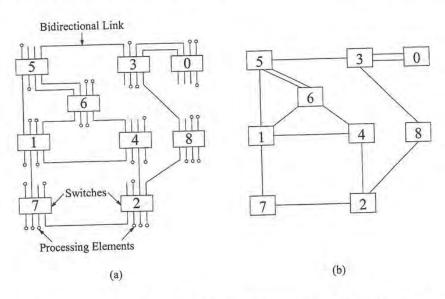

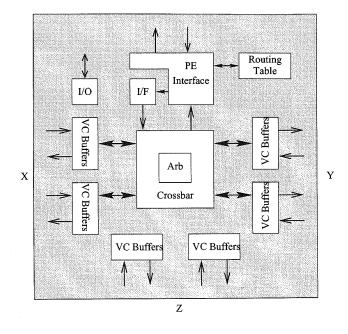

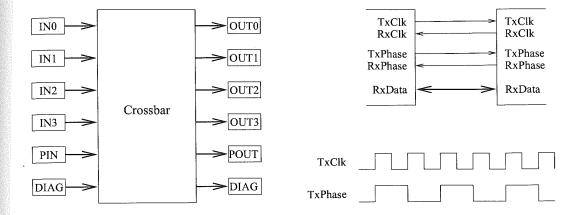

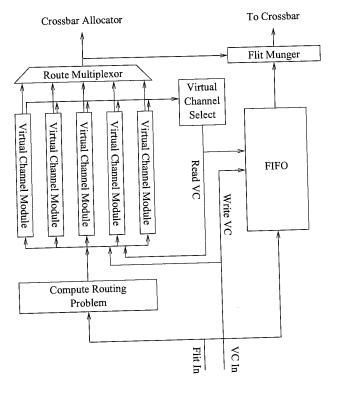

Scalability is an important issue in designing multiprocessor systems. Bus-based systems are not scalable as the bus becomes the bottleneck when more processors are added. The direct network or point-to-point network is a popular network architecture that scales well to a large number of processors. A direct network consists of a set of nodes, each one being directly connected to a (usually small) subset of other nodes in the network. Figures 1.5 through 1.7 show several direct networks. The corresponding interconnection patterns between nodes will be studied below. Each node is a programmable computer with its own processor, local memory, and other supporting devices. These nodes may have different functional capabilities. For example, the set of nodes may contain vector processors, graphics processors, and I/O processors. Figure 1.4 shows the architecture of a generic node. A common component of these nodes is a router, which handles message communication among nodes. For this reason, direct networks are also known as router-based networks. Each router has direct connections to the router of its neighbors. Usually, two neighboring nodes are connected by a pair of unidirectional channels in opposite directions. A bidirectional channel may also be used to connect two neighboring nodes. Although the function of a router can be performed by the local processor, dedicated routers have been used in high-performance multicomputers, allowing overlapped computation and communication within each node. As the number of nodes in the system increases, the total communication bandwidth, memory bandwidth, and processing capability of the system also increase. Thus, direct networks have been a popular interconnection architecture for constructing large-scale parallel computers.

Each router supports some number of input and output channels. Internal channels or ports connect the local processor/memory to the router. Although it is common to provide only one pair of internal channels, some systems use more internal channels in order to avoid a communication bottleneck between the local processor/memory and the router [39]. External channels are used for communication between routers. By connecting input channels of one node to the output channels of other nodes, the direct network is defined. Unless otherwise specified, the term "channel" will refer to an external channel. Two directly connected nodes are called neighboring or adjacent nodes. Usually, each node has a fixed number of input and output channels, and every input channel is paired with a corresponding output channel. Through the connections among these channels, there are many ways to interconnect these nodes. Obviously, every node in the network should be able to reach every other node.

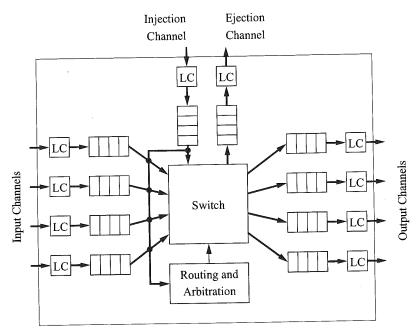

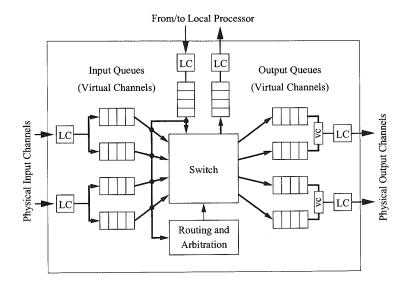

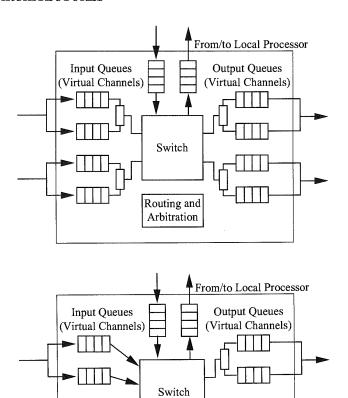

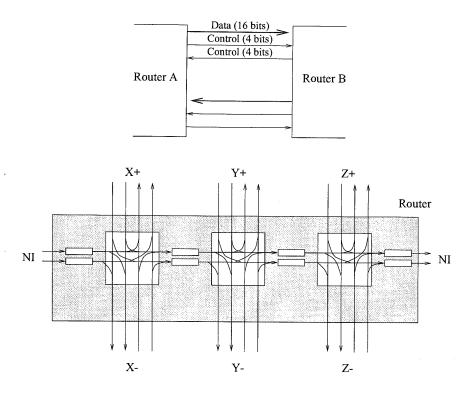

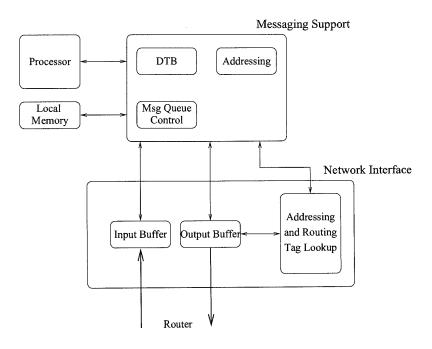

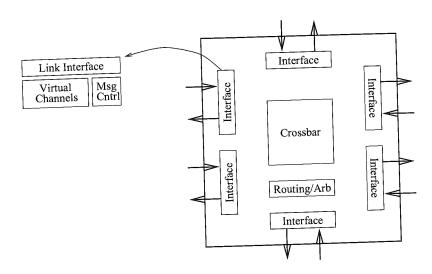

Figure 1.4. A generic node architecture.

# 1.6.1 Characterization of Direct Networks

Direct networks have been traditionally modeled by a graph G(N,C), where the vertices of the graph N represent the set of processing nodes, and the edges of the graph C represent the set of communication channels. This is a very simple model that does not consider implementation issues. However, it allows the study of many interesting network properties. Depending on the properties under study, a bidirectional channel may be modeled either as an edge or as two arcs in opposite directions (two unidirectional channels). The latter is the case for deadlock avoidance in Chapter 3. Let us assume that a bidirectional channel is modeled as an edge. Some basic network properties can be defined from the graph representation:

- Node degree: Number of channels connecting that node to its neighbors.

- Diameter: The maximum distance between two nodes in the network.

- Regularity: A network is regular when all the nodes have the same degree.

- Symmetry: A network is symmetric when it looks alike from every node.

A direct network is mainly characterized by three factors: topology, routing, and switching. The topology defines how the nodes are interconnected by channels, and is usually modeled by a graph as indicated above. For direct networks, the ideal topology would connect every node to every other node. No message would even have to pass through an intermediate node before reaching its destination. This fully connected topology requires a router with N links (including the internal one) at each node for a network with N nodes. Therefore, the cost is prohibitive for networks of moderate to large size. Additionally, the number of physical connections of a node is limited by hardware constraints such as the number of available pins and the available wiring area. These engineering and scaling difficulties preclude the use of such fully connected networks even for small network sizes. As a consequence, many topologies have been proposed, trying to balance performance and some cost parameters. In these topologies, messages may have to traverse some intermediate nodes before reaching the destination node.

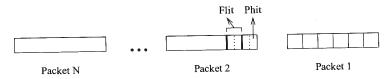

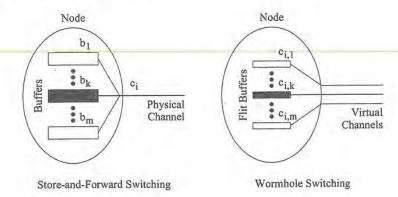

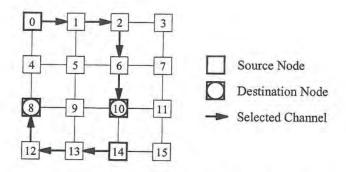

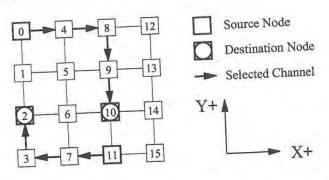

From the programmer's perspective, the unit of information exchange is the message. The size of messages may vary depending on the application. For efficient and fair use of network resources, a message is often divided into packets prior to transmission. A packet is the smallest unit of communication that contains the destination address and sequencing information, which are carried in the packet header. For topologies in which packets may have to traverse some intermediate nodes, the routing algorithm determines the path selected by a packet to reach its destination. At each intermediate node, the routing algorithm indicates the next channel to be used. That channel may be selected among a set of possible choices. If all the candidate channels are busy, the packet is blocked and cannot advance. Obviously, efficient routing is critical to the performance of interconnection networks.

When a message or packet header reaches an intermediate node, a *switching* mechanism determines how and when the router switch is set, i.e., the input channel is connected to the output channel selected by the routing algorithm. In other words, the switching mechanism determines how network resources are allocated for message transmission. For example, in circuit switching, all the channels required by a message are reserved before starting message transmission. In packet switching, however, a packet is transmitted through a channel as soon as that channel is reserved but the next channel is not reserved (assuming that it is available) until the packet releases the channel it is currently using. Obviously, some buffer space is required to store the packet until the next channel is reserved. That buffer should be allocated before starting packet transmission. So,

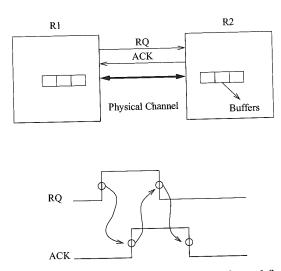

buffer allocation is closely related to the switching mechanism. Flow control is also closely related to the switching and buffer allocation mechanisms. The flow control mechanism establishes a dialog between sender and receiver nodes, allowing and stopping the advance of information. If a packet is blocked, it requires some buffer space to be stored. When there is no more available buffer space, the flow control mechanism stops information transmission. When the packet advances and buffer space is available, transmission is started again. If there is no flow control and no more buffer space is available, the packet may be dropped, or derouted through another channel.

The above factors affect the network performance. They are not independent of each other but are closely related. For example, if a switching mechanism reserves resources in an aggressive way (as soon as a packet header is received), packet latency can be reduced. However, each packet may be holding several channels at the same time. So, such a switching mechanism may cause severe network congestion and, consequently, make the design of efficient routing and flow control policies difficult. The network topology also affects performance, as well as how the network traffic can be distributed over available channels. In most cases, the choice of a suitable network topology is restricted by wiring and packaging constraints.

#### 1.6.2 Popular Network Topologies

Many network topologies have been proposed in terms of their graph theoretic properties. However, very few of them have ever been implemented. Most of the implemented networks have an orthogonal topology. A network topology is orthogonal if and only if nodes can be arranged in an orthogonal n-dimensional space, and every link can be arranged in such a way that it produces a displacement in a single dimension. Orthogonal topologies can be further classified as strictly orthogonal and weakly orthogonal. In a strictly orthogonal topology, every node has at least one link crossing each dimension. In a weakly orthogonal topology, some nodes may not have any link in some dimensions. Hence, it is not possible to cross every dimension from every node. Crossing a given dimension from a given node may require moving in another dimension first.

#### Strictly Orthogonal Topologies

f

1

e

e

ıf

d

3,

h

e

d

$\mathbf{n}$

r-

1t

ЭS

g,

et

æ

ıе

зe

о,

The most interesting property of strictly orthogonal topologies is that routing is very simple. Thus, the routing algorithm can be efficiently implemented in hardware. Effectively, in a strictly orthogonal topology nodes can be numbered by using their coordinates in the *n*-dimensional space. As each link traverses a single dimension and every node has at least one link crossing each dimension, the distance between two nodes can be computed as the sum of dimension offsets. Also, the displacement along a given link only modifies the offset in the corresponding dimension. Taking into account that it is possible to cross any dimension from any node in the network, routing can be easily implemented by selecting a link that decrements the absolute value of the offset in some dimension. The set of dimension offsets can be stored in the packet header, and updated (by adding or subtracting one unit) every time the packet is successfully routed at some intermediate node. If the topology is not strictly orthogonal, however, routing may become much more complex.

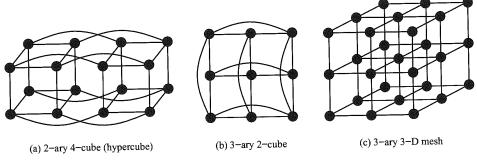

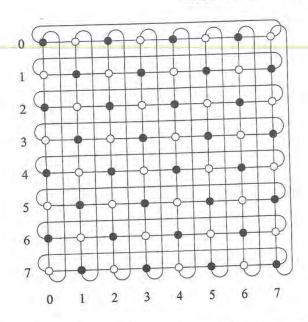

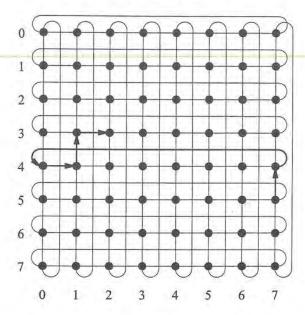

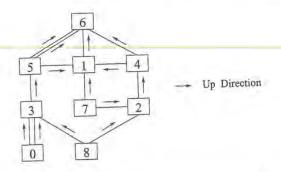

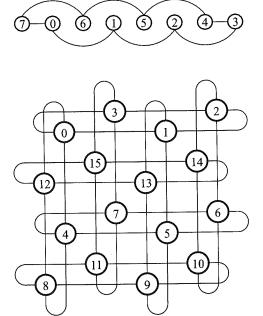

The most popular direct networks are the n-dimensional mesh, the k-ary n-cube or torus, and the hypercube. All of them are strictly orthogonal. Formally, an n-dimensional mesh has  $k_0 \times k_1 \times \cdots \times k_{n-2} \times k_{n-1}$  nodes,  $k_i$  nodes along each dimension i, where  $k_i \geq 2$  and  $0 \leq i \leq n-1$ . Each node X is identified by n coordinates,  $(x_{n-1}, x_{n-2}, \ldots, x_1, x_0)$ , where  $0 \leq x_i \leq k_i - 1$  for  $0 \leq i \leq n-1$ . Two nodes X and Y are neighbors if and only if  $y_i = x_i$  for all i,  $0 \leq i \leq n-1$ , except one, j, where  $y_j = x_j \pm 1$ . Thus, nodes have from n to 2n neighbors, depending on their location in the mesh. Therefore, this topology is not regular.

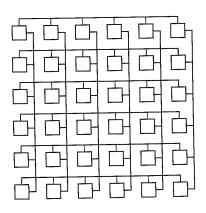

Figure 1.5. Strictly orthogonal direct network topologies.

In a bidirectional k-ary n-cube [71], all nodes have the same number of neighbors. The definition of a k-ary n-cube differs from that of an n-dimensional mesh in that all of the  $k_i$  are equal to k and two nodes X and Y are neighbors if and only if  $y_i = x_i$  for all  $i, 0 \le i \le n-1$ , except one, j, where  $y_j = (x_j \pm 1) \mod k$ . The change to modular arithmetic in the definition adds wraparound channels to the k-ary n-cube, giving it regularity and symmetry. Every node has n neighbors if k = 2 and 2n neighbors if k > 2. When n = 1, the k-ary n-cube collapses to a bidirectional ring with k nodes.

Another topology with regularity and symmetry is the hypercube, which is a special case of both n-dimensional meshes and k-ary n-cubes. A hypercube is an n-dimensional mesh in which  $k_i = 2$  for  $0 \le i \le n-1$ , or a 2-ary n-cube, also referred to as a binary n-cube.

Figure 1.5a depicts a binary 4-cube or 16-node hypercube. Figure 1.5b illustrates a 3-ary 2-cube or two-dimensional (2-D) torus. Figure 1.5c shows a 3-ary three-dimensional (3-D) mesh, resulting by removing the wraparound channels from a 3-ary 3-cube.

Two conflicting requirements of a direct network are that it must accommodate a large number of nodes while maintaining a low network latency. This issue will be addressed in Chapter 7.

#### Other Direct Network Topologies

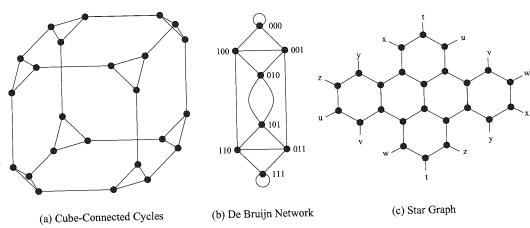

In addition to the topologies defined above, many other topologies have been proposed in the literature. Most of them were proposed with the goal of minimizing the network diameter for a given number of nodes and node degree. As will be seen in Chapter 2, for pipelined switching techniques network latency is almost insensitive to network diameter, especially when messages are long. So it is unlikely that those topologies are implemented. In the following paragraphs, we present an informal description of some relevant direct network topologies.

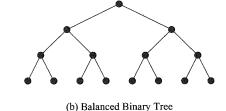

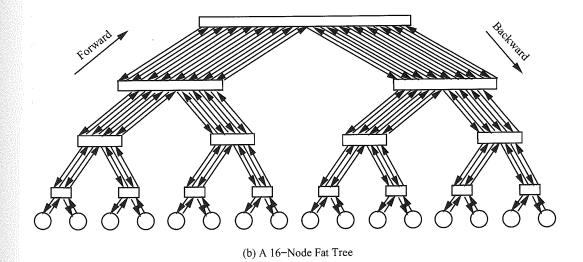

A popular topology is the *tree*. This topology has a *root* node connected to a certain number of descendant nodes. Each of these nodes is in turn connected to a disjoint set (possibly empty) of descendants. A node with no descendants is a *leaf* node. A characteristic property of trees is that every node but the root has a single parent node. Therefore, trees contain no cycles. A tree in which every node but the leaves has a fixed number k of descendants is a k-ary tree. When the distance from every leaf node to the root is the same, i.e., all the branches of the tree have the same length, the tree is *balanced*. Figures 1.6a and 1.6b show an unbalanced and a balanced binary tree, respectively.

The most important drawback of trees as general-purpose interconnection networks is that the root node and the nodes close to it become a bottleneck. Additionally, there are no alternative paths between any pair of nodes. The bottleneck can be removed by allocating a higher channel

Figure 1.6. Some tree topologies.

bandwidth to channels located close to the root node. The shorter the distance to the root node, the higher the channel bandwidth. However, using channels with different bandwidth is not practical, specially when message transmission is pipelined. A practical way to implement trees with higher channel bandwidth in the vicinity of the root node (fat trees) will be described in Section 1.7.5.