decode transactions, may handle conflicts, may interface with the snoop filter 204, and may process transactions. In one embodiment, the protocol logic 202 may comprise distributed protocol logic (DPL) 210 and centralized protocol logic (CPL) 212. In one embodiment, each port 200 has an associated DPL 210 to locally implement portions of the protocol logic 202 for the respective port 200. In particular, the DPL 210 may comprise decode logic to decode incoming transactions and may comprise one or more buffers or queues to store data and/or other information associated with incoming and outgoing transactions while being processed by the protocol logic 202 and/or awaiting responses from cache nodes 102, 104.")

. [4:61-5:13] ("The CPL 212 may provide global functions for processing transactions regardless of which port 200 the transaction originated. For example, the CPL 212 for each port 200 may check for-transaction conflicts, may prevent transaction starvation, and may maintain data coherency in accordance with a snoop-based protocol. In particular, the CPL 212 in response to processing a read, snoop, or invalidate request may check the state of the line of the request in the caches 114 and may issue requests to one or more cache nodes 102, 104 based upon the state of the line. In one embodiment, the CPL 212 may use the coherency data of the snoop filter 204 to reduce the number of requests sent to the cache nodes 102, 104 and may update coherency data in the snoop filter 204 based upon the transaction type and snoop responses received from the cache nodes 102, 104. The CPL 212 may further comprise logic to bypass the snoop filter 204 and to maintain data coherency without using the coherency data of the snoop filter 204. Moreover, the CPL 212 may be divided into four interleaves 214, and a separate CPL interleave 214 may be associated with each of the four SF interleaves 208.").

In addition, the claimed interconnection controller comprises protocol engines for

processing transactions in accordance with a cache coherence protocol. *See*, *e.g.*, '206 patent claim 1.4. A cache coherence protocol facilitates cache coherency, thus the claimed interconnection controller is necessarily operable to facilitate cache coherency in the computer system.

Furthermore, to the extent not disclosed, a person of ordinary skill in the art at the time of the alleged invention of the Asserted Claims would have been motivated to modify the prior art references identified in Section III and Exhibits A-1 - A-9; B-1 - B-19; C-1 - C-8; D-1 - D-14; and Exhibits E-1 - E-14 to include an interconnection controller operable to facilitate cache coherency across the computer system, at least under Memory Integrity's apparent infringement

theories. See, e.g., Exhibits D-1 - D-14, claim 15.1. For example, it would have been obvious for an interconnection controller that processes coherence transactions to process those transactions so as to facilitate cache coherency across the computer system as described above with respect to the "cache coherence controller."

# 8. "Cache Coherence Controller" "Constructed to Act As An Aggregate Remote Cache"

Some of the Asserted Claims are directed to a "cache coherence controller" "constructed to act as an aggregate remote cache." For example, claim 18.1 of the '409 patent recites "the cache coherence controller is constructed to act as an aggregate remote cache." *See also*, *e.g.*, '409 patent claim 47.1; and '636 patent claim 29.1. At least under Memory Integrity's apparent infringement theories, cache coherence controllers "constructed to act as an aggregate remote cache" were well-known in the art before the priority dates of the Asserted Patents. *See*, *e.g.*, Exhibits A-1 – A-9, claims 18.1 and 47.1; and Exhibits B-1 – B-19, claim 29.1. The following discussion further shows that, at least under Memory Integrity's apparent infringement theory, it was well known and conventional to implement cache coherence controllers "constructed to act as an aggregate remote to act as an aggregate remote cache" in multiprocessor systems.

At least under Memory Integrity's apparent infringement theories, there are many examples of prior art references that disclose implementing cache coherence controllers "constructed to act as an aggregate remote cache." Examples of prior art references that disclose and further demonstrate that such was well known include:

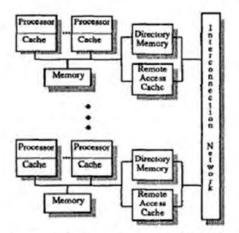

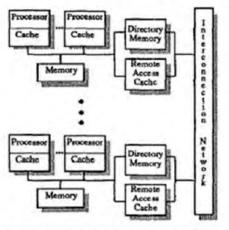

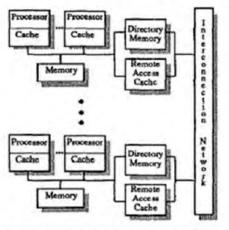

"The Directory-Based Cache Coherence Protocol for the DASH Multiprocessor." Lenoski (1990): See, e.g., p. 1, para. 2 ("We are currently building a prototype of a scalable shared memory multiprocessor. The system provides high processor performance and scalability though the use of coherent caches and a directory-based coherence protocol. The high-level organization of the prototype, called DASH (Directory Architecture for SHared memory) [17]. is shown in Figure 1. The architecture consists of a number of processing nodes connected through a high-bandwidth low-latency interconnection network. The physical memory in the

> machine is distributed among the nodes of the multiprocessor, with all memory accessible to each node. Each processing node, or cluster, consists of a small number of high-performance processors with their individual caches, a portion of the shared-memory, a common cache for pending remote accesses, and a directory controller interfacing the cluster to the network. A bus-based snoopy scheme is used to keep caches coherent within a cluster, while inter-node cache consistency is maintained using a distributed directory-based coherence protocol.")

Figure 1: General architecture of DASH.

Lenoski (1990), Figure 1

- Lenoski (1990): See, e.g., p. 1, para. 4 ("In DASH, each processing node has a directory memory corresponding to its portion of the shared physical memory. For each memory block, the directory memory stores the identities of all remote nodes caching that block. Using the directory memory, a node writing a location can send point-to-point invalidation or update messages to those processors that are actually caching that block.")

- Lenoski (1990): See, e.g., p. 3, para. 5 ("The directory controller (DC) contains the . directory memory corresponding to the portion of main memory present within the cluster. It also initiates out-bound network requests and replies. The pseudo-CPU (PCPU) is responsible for buffering incoming requests and issuing such requests on the cluster bus. It mimics a CPU on this bus on behalf of remote processors except that responses from the bus are sent out by the directory controller. The reply controller (RC) tracks outstanding requests made by the local processors and receives and buffers the corresponding replies from remote clusters. It acts as memory when the local processors are allowed to retry their remote requests. The network interface and the local portion of the network itself reside on the directory card. The interconnection network consists of a pair of meshes. One mesh is dedicated to the request messages while the other handles replies. These meshes utilize wormhole routing [9] to minimize latency. Finally, the board contains hardware monitoring logic and miscellaneous control and status registers. The monitoring logic samples a variety of directory board and bus events from which usage and performance statistics can be derived.")

- Lenoski (1990): See, e.g., p. 4.5, para. 4 ("In the protocol, invalidation acknowledges are sent to the local cluster that initiated the memory request. An alternative would be for the home cluster to gather the acknowledges, and, when all have been received, send a message to the requesting cluster indicating that the request has been completed. We chose the former because it reduces the waiting time for completion of a subsequent fence operation by the requesting cluster and reduces the potential of a hot spot developing at the memory.")

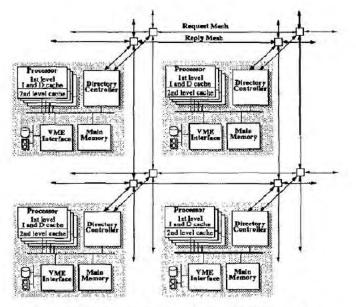

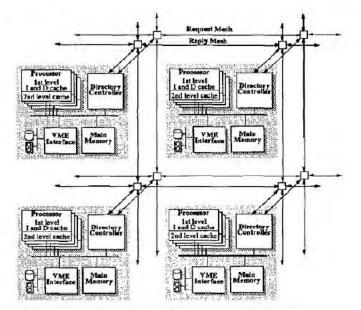

- "The Directory-Based Cache Coherence Protocol for the DASH Multiprocessor." Lenoski (1992): See, e.g., p. 150 ("A DASH system consists of a number of modified 4D/240 systems that have been supplemented with a directory controller board. This directory controller board is responsible for maintaining the cache coherence across the nodes and serving as the interface to the interconnection network.")

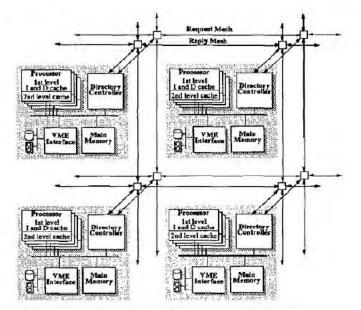

Figure 2: Block diagram of sample 2 x 2 DASH system.

Lenoski (1992), Figure 2

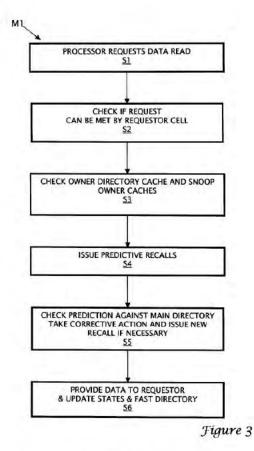

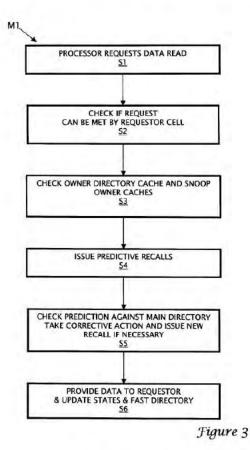

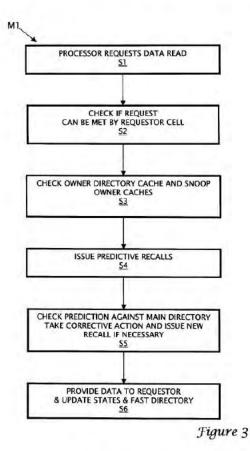

U.S. Patent No. 6,055,610 to Smith: See, e.g., 11:44-55 ("A flow chart of the basic method M1 of handling a data request is flow charted in FIG. 3. At step S1, processor P11 issues a read request of data stored in main memory MM0. At step S2, caches C10-C13 of requester cell MC1 are examined to determine if the request can be met locally. First, associated cache C11 is checked. A hit allows the request to be met locally. A miss refers the request to the requestor's coherency controller CC1. Coherency controller CC1 initiates a local snoop while referring the request to owner cell MC0. If the snoop results in a hit, the request can be met locally. If the data is held privately by another local processor, e.g., processor P12, coherency controller requests that the data be made public so that the request can be met. Only if the local snoop misses is involvement of the owner cell MC0 required.")

- Smith: See, e.g., 11:56-63 ("At step S3, coherency controller CC0 of owner cell MC0 initiates a local snoop of its caches, accesses fast directory FD0, and initiates access of main memory MM0. Coherency controller CC0 determines whether or not the fast-directory data calls for a recall and whether the directory cache data is consistent with the local snoop results. If the directory data is consistent with the snoop results and if a recall is indicated, it is initiated at step S4.")

- Smith: *See*, *e.g.*, 12:3-8 ("Once the recall process is complete, the requested data is transferred to the requester cell MC1, coherency controller CC1, cache C11, and processor P11, at step S6. State information in cache C11, fast directory FD0, and the coherency directory of main memory MM0 is updated as necessary. This completes method M1.")

• U.S. Patent No, 6,085,295 to Ekanadham: See, e.g., 2:25-33 ("In a node where a remote line is brought into the cache of a processor, but not into the node's memory, the adapter acts as a proxy memory representing the remote memory that the line is mapped onto. More specifically, when a memory command is issued from a local processor to a remote memory, the memory command is directed to the adapter which is responsible for insuring that the command is executed at that remote memory.")

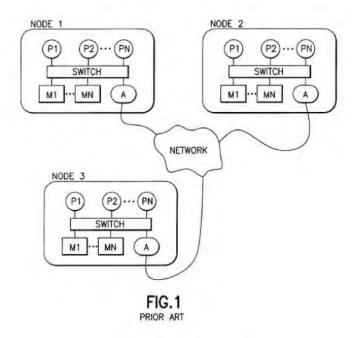

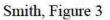

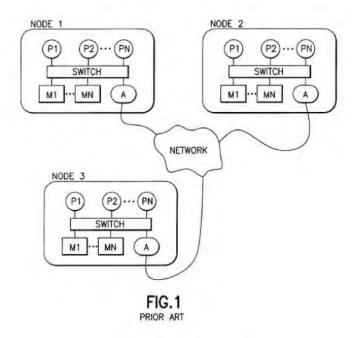

- Ekanadham: See, e.g., 3:37-45 ("The preferred embodiment of our system that is based on a network of switch-based SMP nodes with an adapter attached to each node. FIG. 1 illustrates a high-level diagram of such a multiprocessing system. Each node has a plurality of processors P1, P2, ..., PN interconnected to each other by a switch (SW). The switch also interconnects the memory modules M1, M2, ..., MN and adapters A. The nodes in turn, are connected to each other through a network as shown.")

- Ekanadham: See, e.g., 3:49-56 ("The adapter connects to the switch and plays the role of either a memory or a processor. The behavior of the adapter is different for different memory lines. When a line is homed at the local memory of the node, the adapter behaves as a proxy processor for that line. When a line is homed at the memory of a remote node, the adapter behaves as a proxy memory for that line. These roles are illustrated in FIGS. 3A-3C and are elaborated further below.")

- Ekanadham: See, e.g., 4:7-24 ("In a node in which a line is homed in the local memory, the adapter plays the role of a proxy processor representing the accesses to the line made by the processors in other nodes of the system. In this role, the adapter maintains a state for the line and the list of all nodes sharing that line. The state can be I (indicating that no other node has this line), E (indicating that some other node has exclusive copy of this line) or S (indicating that this line is shared by this and other nodes). As a proxy processor, the adapter receives requests from other adapters and performs the reads and writes in this node on their behalf. Whenever a local processor requires exclusive access to the line while it is in shared state, it communicates with other adapters and invalidates the line in all other nodes. When another node requests for exclusive copy of the line. The adapter only invalidates the copies in all other nodes, but also requests the local memory to grant the exclusive access. The memory controller treats the adapter as another processor.")

- Ekanadham: See, e.g., 4:26-41 ("In a node in which a line is homed at a remote memory, the adapter acts as a proxy memory. It captures all the transactions for the corresponding address and runs the memory protocol. In this role, the adapter maintains a state for the line and the list of local caches sharing the line. The state can be I (indicating that no local cache this line), E (indicating that some local cache has exclusive copy of this line) or S (indicating that this line is shared by this and other nodes). As a proxy memory, the adapter responds to all requests to the line and obtains the contents of the line from the remote node (where that line is backed by memory) and supplies the contents to the local caches. It performs the usual coherence control operations in the node and coordinates with other adapters. In order to maintain global coherence, it may have to issue some bus transactions as a master, as illustrated later.")

Ekanadham, Figure 1

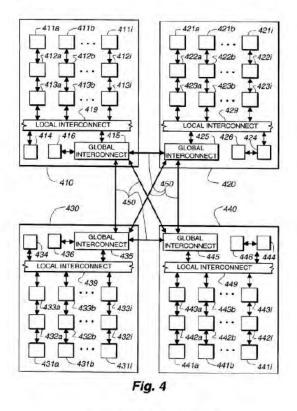

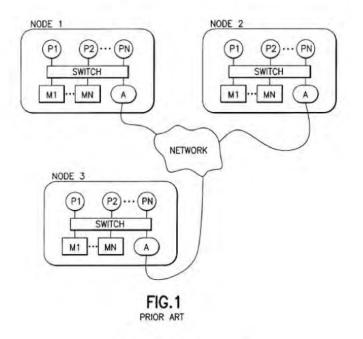

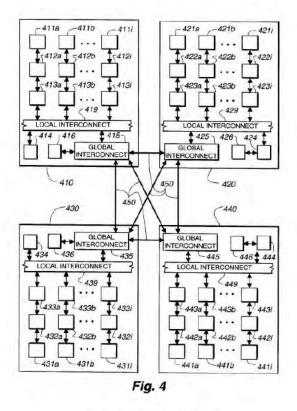

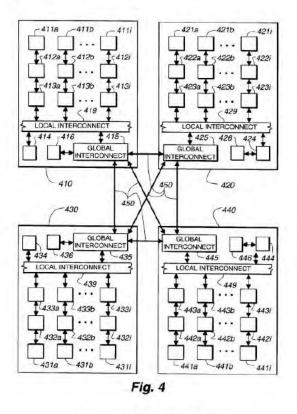

- U.S. Patent No, 6,141,692 to Loewenstein: See, e.g., 6:29-33 ("Requests for data and responses to those requests are exchanged between nodes by the respective HA, SA, and RA of each global interface (i.e., 415, 425, 435, and 445) in the form of data/control packets, thereby enabling each node to keep track of the status of all data cached therein.")

- Loewenstein: See, e.g., 11:1-9 ("When the system is operating in NUMA mode, a typical read request (e.g., a Read-- To-- Share request) by processor 411a of node 410 occurs in the following manner. To initiate the request, processor 411a presents a virtual address (VA) to MMU 412a, which converts the VA into a GA and presents the GA to cache 413a. If there is a valid copy of the data line of interest in cache 413a (e.g., a shared or owned copy), then cache 413a provides the data to processor 411a via MMU 412a, thereby completing the read request.")

- Loewenstein: *See*, *e.g.*, 11:10-15 ("However, if cache 413a does not have a valid copy, then cache 413a presents the GA to the local interconnect 419 of its associated node. If the GA is not part of the node 410's local address space (i.e., node 410 is not the home node for the requested address), then the request is forwarded to the appropriate home node (i.e., node 420).")

- Loewenstein: *See*, *e.g.*, 11:40-50 ("If the home node is determined to have a valid copy of the requested data line, then the home node provides the data to the requesting node. In the case where the requesting node is also the home node, only an internal data transfer is required. Alternatively, where the home node is not the requesting node, then the global interface of the home node (global interface 425 in the above example) responds by retrieving the requested data line from the main memory 424 or from a

cache line which is owned by a processor within node 420, and sends the data line to the global interface 415 of the requesting node 410 via global interconnect 450.")

Loewenstein: See, e.g., 11:60-64 ("Upon receiving the data line, global interface 415 forwards the data line to cache 413a, which provides the data to the requesting processor 411a.")

Loewenstein, Figure 4

U.S. Patent No, 6,751,721 to Webb: See, e.g., Abstract ("A directory-based multiprocessor cache control scheme for distributing invalidate messages to change the state of shared data in a computer system. The plurality of processors are grouped into a plurality of clusters. A directory controller tracks copies of shared data sent to processors in the clusters. Upon receiving an exclusive request from a processor requesting permission to modify a shared copy of the data, the directory controller generates invalidate messages requesting that other processors sharing the same data invalidate that data. These invalidate messages are sent via a point-to-point transmission only to master processors in clusters actually containing a shared copy of the data. Upon receiving the invalidate message, the master processors broadcast the invalidate message in an ordered fan-in/fan-out process to each processor in the cluster. All processors within the cluster invalidate a local copy of the shared data if it exists and once the master processor receives acknowledgements from all processors in the cluster, the master processor sends an invalidate acknowledgment message to the processor that originally requested the exclusive rights to the shared data. The cache coherency is scalable and may be implemented using the hybrid

point-to-point/broadcast scheme or a conventional point-to-point only directory-based invalidate scheme.")

As illustrated by the prior art references above, it was well known before the priority dates of the Asserted Patents to implement a "cache coherence controller" "constructed to act as an aggregate remote cache" in multiprocessor systems, at least under Memory Integrity's apparent infringement theories. Indeed, a person of ordinary skill would have been motivated to implement a "cache coherence controller" "constructed to act as an aggregate remote cache" in a multiprocessor system as described below:

- Ekanadham: *See*, *e.g.*, 1:23-35 ("Technology considerations limit the size of an SMP node to a small number of processors. A method for building a shared-memory multiprocessor with a larger number of processors is to connect a number of SMP nodes with a network, and provide an adapter to extend the SMP's memory across the SMP nodes (see FIG. 1). Existing adapter designs plug into the memory bus of bus-based SMP nodes and collectively provide shared memory across the system, so that any processor in any node can access any location in any memory module in the system. Resources within a node are termed local and resources on other nodes are termed remote.")

- Ekanadham: *See*, *e.g.*, 2:37-41 ("By appearing as either a local processor or a local memory, the adapter uses the local SMP coherence protocol within a node to accomplish the above tasks, without any changes to the memory controllers.")

- Loewenstein: See, e.g., 5:1-8 ("Since global interface 115 is also responsible for maintaining global cache coherency, global interface 115 includes a hardware and/or software implemented cache-coherency mechanism for maintaining coherency between the respective caches and main memories of nodes 110, 120, ... 180. Cache coherency is essential in order for the system 100 to properly execute shared-memory programs correctly.")

Accordingly, it would have been obvious to implement a "cache coherence controller"

"constructed to act as an aggregate remote cache" in a multiprocessor system having multiple clusters of processors while maintaining coherency with a reasonable expectation of success. Furthermore, it would have been obvious to implement a "cache coherence controller" "constructed to act as an aggregate remote cache" because such a modification would simply be the use of a known technique (*e.g.*, a cache coherence controller "constructed to act as an aggregate

remote cache") to improve similar devices (*e.g.*, multiprocessor systems) in the same way (*e.g.*, improve performance and scalability while maintaining coherency).

#### 9. "Cache Coherence Controller" "Constructed to Act As A Probing Agent Pair"

Some of the Asserted Claims are directed to a "cache coherence controller" "constructed to act as a probing agent pair." For example, claim 19.1 of the '409 patent recites "the cache coherence controller is constructed to act as a probing agent pair." *See also*, *e.g.*, '409 patent claim 48.1; and '636 patent claim 30.1. At least under Memory Integrity's apparent infringement theories, cache coherence controllers "constructed to act as a probing agent pair." were well-known in the art before the priority dates of the Asserted Patents. *See*, *e.g.*, Exhibits A-1 – A-9, claims 19.1 and 48.1; and Exhibits B-1 – B-19, claim 30.1. The following discussion further shows that, at least under Memory Integrity's apparent infringement theory, it was well known and conventional to implement cache coherence controllers "constructed to act as a probing agent pair" in multiprocessor systems.

At least under Memory Integrity's apparent infringement theories, there are many examples of prior art references that disclose implementing cache coherence controllers "constructed to act as a probing agent pair." Examples of prior art references that disclose and further demonstrate that such was well known include:

"The Directory-Based Cache Coherence Protocol for the DASH Multiprocessor." Lenoski (1990): See, e.g., p. 1, para. 2 ("We are currently building a prototype of a scalable shared memory multiprocessor. The system provides high processor performance and scalability though the use of coherent caches and a directory-based coherence protocol. The high-level organization of the prototype, called DASH (Directory Architecture for SHared memory) [17]. is shown in Figure 1. The architecture consists of a number of processing nodes connected through a high-bandwidth low-latency interconnection network. The physical memory in the machine is distributed among the nodes of the multiprocessor, with all memory accessible to each node. Each processing node, or cluster, consists of a small number of high-performance processors with their individual caches, a portion of the shared-memory, a common cache for pending remote accesses, and a directory

controller interfacing the cluster to the network. A bus-based snoopy scheme is used to keep caches coherent within a cluster, while inter-node cache consistency is maintained using a distributed directory-based coherence protocol.")

Figure 1: General architecture of DASH.

Lenoski (1990), Figure 1

- Lenoski (1990): See, e.g., p. 1, para. 4 ("In DASH, each processing node has a directory memory corresponding to its portion of the shared physical memory. For each memory block, the directory memory stores the identities of all remote nodes caching that block. Using the directory memory, a node writing a location can send point-to-point invalidation or update messages to those processors that are actually caching that block.")

- Lenoski (1990): See, e.g., p. 3, para. 5 ("The directory controller (DC) contains the directory memory corresponding to the portion of main memory present within the cluster. It also initiates out-bound network requests and replies. The pseudo-CPU (PCPU) is responsible for buffering incoming requests and issuing such requests on the cluster bus. It mimics a CPU on this bus on behalf of remote processors except that responses from the bus are sent out by the directory controller. The reply controller (RC) tracks outstanding requests made by the local processors and receives and buffers the corresponding replies from remote clusters. It acts as memory when the local processors are allowed to retry their remote requests. The network interface and the local portion of the network itself reside on the directory card. The interconnection network consists of a pair of meshes. One mesh is dedicated to the request messages while the other handles replies. These meshes utilize wormhole routing [9] to minimize latency. Finally, the board contains hardware monitoring logic and miscellaneous control and status registers. The monitoring logic samples a variety of directory board and bus events from which usage and performance statistics can be derived.")

- Lenoski (1990): See, e.g., p. 4.5, para. 4 ("In the protocol, invalidation acknowledges are sent to the local cluster that initiated the memory request. An alternative would be for the home cluster to gather the acknowledges, and, when all have been received,

send a message to the requesting cluster indicating that the request has been completed. We chose the former because it reduces the waiting time for completion of a subsequent fence operation by the requesting cluster and reduces the potential of a hot spot developing at the memory.")

"The Directory-Based Cache Coherence Protocol for the DASH Multiprocessor." Lenoski (1992): See, e.g., p. 150 ("A DASH system consists of a number of modified 4D/240 systems that have been supplemented with a directory controller board. This directory controller board is responsible for maintaining the cache coherence across the nodes and serving as the interface to the interconnection network.")

Figure 2: Block diagram of sample 2 x 2 DASH system.

Lenoski (1992), Figure 2

- U.S. Patent No. 6,055,610 to Smith: See, e.g., 11:44-55 ("A flow chart of the basic method M1 of handling a data request is flow charted in FIG. 3. At step S1, processor P11 issues a read request of data stored in main memory MM0. At step S2, caches C10-C13 of requester cell MC1 are examined to determine if the request can be met locally. First, associated cache C11 is checked. A hit allows the request to be met locally. A miss refers the request to the requestor's coherency controller CC1. Coherency controller CC1 initiates a local snoop while referring the request to owner cell MC0. If the snoop results in a hit, the request can be met locally. If the data is held privately by another local processor, e.g., processor P12, coherency controller requests that the data be made public so that the request can be met. Only if the local snoop misses is involvement of the owner cell MC0 required.")

- Smith: *See*, *e.g.*, 11:56-63 ("At step S3, coherency controller CC0 of owner cell MC0 initiates a local snoop of its caches, accesses fast directory FD0, and initiates access of main memory MM0. Coherency controller CC0 determines whether or not the

fast-directory data calls for a recall and whether the directory cache data is consistent with the local snoop results. If the directory data is consistent with the snoop results and if a recall is indicated, it is initiated at step S4.")

• Smith: *See*, *e.g.*, 12:3-8 ("Once the recall process is complete, the requested data is transferred to the requester cell MC1, coherency controller CC1, cache C11, and processor P11, at step S6. State information in cache C11, fast directory FD0, and the coherency directory of main memory MM0 is updated as necessary. This completes method M1.")

- U.S. Patent No, 6,085,295 to Ekanadham: *See*, *e.g.*, 2:25-33 ("In a node where a remote line is brought into the cache of a processor, but not into the node's memory, the adapter acts as a proxy memory representing the remote memory that the line is mapped onto. More specifically, when a memory command is issued from a local processor to a remote memory, the memory command is directed to the adapter which is responsible for insuring that the command is executed at that remote memory.")

- Ekanadham: *See*, *e.g.*, 3:37-45 ("The preferred embodiment of our system that is based on a network of switch-based SMP nodes with an adapter attached to each node. FIG. 1 illustrates a high-level diagram of such a multiprocessing system. Each node has a plurality of processors P1, P2, ..., PN interconnected to each other by a switch (SW).

The switch also interconnects the memory modules M1, M2, ..., MN and adapters A. The nodes in turn, are connected to each other through a network as shown.")

- Ekanadham: *See*, *e.g.*, 3:49-56 ("The adapter connects to the switch and plays the role of either a memory or a processor. The behavior of the adapter is different for different memory lines. When a line is homed at the local memory of the node, the adapter behaves as a proxy processor for that line. When a line is homed at the memory of a remote node, the adapter behaves as a proxy memory for that line. These roles are illustrated in FIGS. 3A-3C and are elaborated further below." )

- Ekanadham: See, e.g., 4:7-24 ("In a node in which a line is homed in the local memory, the adapter plays the role of a proxy processor representing the accesses to the line made by the processors in other nodes of the system. In this role, the adapter maintains a state for the line and the list of all nodes sharing that line. The state can be I (indicating that no other node has this line), E (indicating that some other node has exclusive copy of this line) or S (indicating that this line is shared by this and other nodes). As a proxy processor, the adapter receives requests from other adapters and performs the reads and writes in this node on their behalf. Whenever a local processor requires exclusive access to the line while it is in shared state, it communicates with other adapters and invalidates the line in all other nodes. When another node requests for exclusive copy of the line. The adapter only invalidates the copies in all other nodes, but also requests the local memory to grant the exclusive access. The memory controller treats the adapter as another processor.")

- Ekanadham: See, e.g., 4:26-41 ("In a node in which a line is homed at a remote memory, the adapter acts as a proxy memory. It captures all the transactions for the corresponding address and runs the memory protocol. In this role, the adapter maintains a state for the line and the list of local caches sharing the line. The state can be I (indicating that no local cache this line), E (indicating that some local cache has exclusive copy of this line) or S (indicating that this line is shared by this and other nodes). As a proxy memory, the adapter responds to all requests to the line and obtains the contents of the line from the remote node (where that line is backed by memory) and supplies the contents to the local caches. It performs the usual coherence control operations in the node and coordinates with other adapters. In order to maintain global coherence, it may have to issue some bus transactions as a master, as illustrated later.")

Ekanadham, Figure 1

- U.S. Patent No, 6,141,692 to Loewenstein: See, e.g., 6:29-33 ("Requests for data and responses to those requests are exchanged between nodes by the respective HA, SA, and RA of each global interface (i.e., 415, 425, 435, and 445) in the form of data/control packets, thereby enabling each node to keep track of the status of all data cached therein.")

- Loewenstein: See, e.g., 11:1-9 ("When the system is operating in NUMA mode, a typical read request (e.g., a Read-- To-- Share request) by processor 411a of node 410 occurs in the following manner. To initiate the request, processor 411a presents a virtual address (VA) to MMU 412a, which converts the VA into a GA and presents the GA to cache 413a. If there is a valid copy of the data line of interest in cache 413a (e.g., a shared or owned copy), then cache 413a provides the data to processor 411a via MMU 412a, thereby completing the read request.")

- Loewenstein: *See*, *e.g.*, 11:10-15 ("However, if cache 413a does not have a valid copy, then cache 413a presents the GA to the local interconnect 419 of its associated node. If the GA is not part of the node 410's local address space (i.e., node 410 is not the home node for the requested address), then the request is forwarded to the appropriate home node (i.e., node 420).")

- Loewenstein: *See*, *e.g.*, 11:40-50 ("If the home node is determined to have a valid copy of the requested data line, then the home node provides the data to the requesting node. In the case where the requesting node is also the home node, only an internal data transfer is required. Alternatively, where the home node is not the requesting node, then the global interface of the home node (global interface 425 in the above example) responds by retrieving the requested data line from the main memory 424 or from a

cache line which is owned by a processor within node 420, and sends the data line to the global interface 415 of the requesting node 410 via global interconnect 450.")

Loewenstein: See, e.g., 11:60-64 ("Upon receiving the data line, global interface 415 forwards the data line to cache 413a, which provides the data to the requesting processor 411a.")

Loewenstein, Figure 4

U.S. Patent No, 6,751,721 to Webb: See, e.g., Abstract ("A directory-based multiprocessor cache control scheme for distributing invalidate messages to change the state of shared data in a computer system. The plurality of processors are grouped into a plurality of clusters. A directory controller tracks copies of shared data sent to processors in the clusters. Upon receiving an exclusive request from a processor requesting permission to modify a shared copy of the data, the directory controller generates invalidate messages requesting that other processors sharing the same data invalidate that data. These invalidate messages are sent via a point-to-point transmission only to master processors in clusters actually containing a shared copy of the data. Upon receiving the invalidate message, the master processors broadcast the invalidate message in an ordered fan-in/fan-out process to each processor in the cluster. All processors within the cluster invalidate a local copy of the shared data if it exists and once the master processor receives acknowledgements from all processors in the cluster, the master processor sends an invalidate acknowledgment message to the processor that originally requested the exclusive rights to the shared data. The cache coherency is scalable and may be implemented using the hybrid

point-to-point/broadcast scheme or a conventional point-to-point only directory-based invalidate scheme.")

As illustrated by the prior art references above, it was well known before the priority dates of the Asserted Patents to implement a "cache coherence controller" "constructed to act as a probing agent pair" in multiprocessor systems. Indeed, a person of ordinary skill would have been motivated to implement a "cache coherence controller" "constructed to act as a probing agent pair" in a multiprocessor system as described below:

- Ekanadham: See, e.g., 1:23-35 ("Technology considerations limit the size of an SMP node to a small number of processors. A method for building a shared-memory multiprocessor with a larger number of processors is to connect a number of SMP nodes with a network, and provide an adapter to extend the SMP's memory across the SMP nodes (see FIG. 1). Existing adapter designs plug into the memory bus of bus-based SMP nodes and collectively provide shared memory across the system, so that any processor in any node can access any location in any memory module in the system. Resources within a node are termed local and resources on other nodes are termed remote.")

- Ekanadham: *See*, *e.g.*, 2:37-41 ("By appearing as either a local processor or a local memory, the adapter uses the local SMP coherence protocol within a node to accomplish the above tasks, without any changes to the memory controllers.")

- Loewenstein: See, e.g., 5:1-8 ("Since global interface 115 is also responsible for maintaining global cache coherency, global interface 115 includes a hardware and/or software implemented cache-coherency mechanism for maintaining coherency between the respective caches and main memories of nodes 110, 120, ... 180. Cache coherency is essential in order for the system 100 to properly execute shared-memory programs correctly.")

Accordingly, it would have been obvious to implement a "cache coherence controller"

"constructed to act as a probing agent pair" in a multiprocessor system having multiple clusters of processors while maintaining coherency with a reasonable expectation of success. Furthermore, it would have been obvious to implement a "cache coherence controller" "constructed to act as a probing agent pair" because such a modification would simply be the use of a known technique (*e.g.*, a cache coherence controller "constructed to act as a probing agent pair") to improve similar

devices (*e.g.*, multiprocessor systems) in the same way (*e.g.*, improve performance and scalability while maintaining coherency).

# 10. "Cache Coherence Controller" "Constructed to Act As A Remote Memory"

Some of the Asserted Claims are directed to a "cache coherence controller" "constructed to act as a remote memory." For example, claim 20.1 of the '409 patent recites "the cache coherence controller is constructed to act as a remote memory." *See also*, *e.g.*, '409 patent claim 49.1; and '636 patent claim 31.1. At least under Memory Integrity's apparent infringement theories, "cache coherence controllers" "constructed to act as a remote memory" were well-known in the art before the priority dates of the Asserted Patents. *See*, *e.g.*, Exhibits A-1 – A-9, claims 20.1 and 49.1; and Exhibits B-1 – B-19, claim 31.1. The following discussion further shows that, at least under Memory Integrity's apparent infringement theories in the original to implement "cache coherence controllers" "constructed to act as a remote well known and conventional to implement "cache coherence controllers" "constructed to act as a remote to act as a remote memory" in multiprocessor systems.

At least under Memory Integrity's apparent infringement theories, there are many examples of prior art references that disclose implementing "cache coherence controllers" "constructed to act as a remote memory." Examples of prior art references that disclose and further demonstrate that such was well known include:

"The Directory-Based Cache Coherence Protocol for the DASH Multiprocessor." Lenoski (1990): See, e.g., p. 1, para. 2 ("We are currently building a prototype of a scalable shared memory multiprocessor. The system provides high processor performance and scalability though the use of coherent caches and a directory-based coherence protocol. The high-level organization of the prototype, called DASH (Directory Architecture for Shared memory) [17]. is shown in Figure 1. The architecture consists of a number of processing nodes connected through a high-bandwidth low-latency interconnection network. The physical memory in the machine is distributed among the nodes of the multiprocessor, with all memory accessible to each node. Each processing node, or cluster, consists of a small number of high-performance processors with their individual caches, a portion of the shared-memory, a common cache for pending remote accesses, and a directory

controller interfacing the cluster to the network. A bus-based snoopy scheme is used to keep caches coherent within a cluster, while inter-node cache consistency is maintained using a distributed directory-based coherence protocol.")

Figure 1: General architecture of DASH.

Lenoski (1990), Figure 1

- Lenoski (1990): See, e.g., p. 1, para. 4 ("In DASH, each processing node has a directory memory corresponding to its portion of the shared physical memory. For each memory block, the directory memory stores the identities of all remote nodes caching that block. Using the directory memory, a node writing a location can send point-to-point invalidation or update messages to those processors that are actually caching that block.")

- Lenoski (1990): See, e.g., p. 3, para. 5 ("The directory controller (DC) contains the directory memory corresponding to the portion of main memory present within the cluster. It also initiates out-bound network requests and replies. The pseudo-CPU (PCPU) is responsible for buffering incoming requests and issuing such requests on the cluster bus. It mimics a CPU on this bus on behalf of remote processors except that responses from the bus are sent out by the directory controller. The reply controller (RC) tracks outstanding requests made by the local processors and receives and buffers the corresponding replies from remote clusters. It acts as memory when the local processors are allowed to retry their remote requests. The network interface and the local portion of the network itself reside on the directory card. The interconnection network consists of a pair of meshes. One mesh is dedicated to the request messages while the other handles replies. These meshes utilize wormhole routing [9] to minimize latency. Finally, the board contains hardware monitoring logic and miscellaneous control and status registers. The monitoring logic samples a variety of directory board and bus events from which usage and performance statistics can be derived.")

- Lenoski (1990): See, e.g., p. 4.5, para. 4 ("In the protocol, invalidation acknowledges are sent to the local cluster that initiated the memory request. An alternative would be for the home cluster to gather the acknowledges, and, when all have been received,

send a message to the requesting cluster indicating that the request has been completed. We chose the former because it reduces the waiting time for completion of a subsequent fence operation by the requesting cluster and reduces the potential of a hot spot developing at the memory.")

"The Directory-Based Cache Coherence Protocol for the DASH Multiprocessor." Lenoski (1992): See, e.g., p. 150 ("A DASH system consists of a number of modified 4D/240 systems that have been supplemented with a directory controller board. This directory controller board is responsible for maintaining the cache coherence across the nodes and serving as the interface to the interconnection network.")

Figure 2: Block diagram of sample 2 x 2 DASH system.

Lenoski (1992), Figure 2

- U.S. Patent No. 6,055,610 to Smith: See, e.g., 11:44-55 ("A flow chart of the basic method M1 of handling a data request is flow charted in FIG. 3. At step S1, processor P11 issues a read request of data stored in main memory MM0. At step S2, caches C10-C13 of requester cell MC1 are examined to determine if the request can be met locally. First, associated cache C11 is checked. A hit allows the request to be met locally. A miss refers the request to the requestor's coherency controller CC1. Coherency controller CC1 initiates a local snoop while referring the request to owner cell MC0. If the snoop results in a hit, the request can be met locally. If the data is held privately by another local processor, e.g., processor P12, coherency controller requests that the data be made public so that the request can be met. Only if the local snoop misses is involvement of the owner cell MC0 required.")

- Smith: *See*, *e.g.*, 11:56-63 ("At step S3, coherency controller CC0 of owner cell MC0 initiates a local snoop of its caches, accesses fast directory FD0, and initiates access of main memory MM0. Coherency controller CC0 determines whether or not the

fast-directory data calls for a recall and whether the directory cache data is consistent with the local snoop results. If the directory data is consistent with the snoop results and if a recall is indicated, it is initiated at step S4.")

Smith: See, e.g., 12:3-8 ("Once the recall process is complete, the requested data is transferred to the requester cell MC1, coherency controller CC1, cache C11, and processor P11, at step S6. State information in cache C11, fast directory FD0, and the coherency directory of main memory MM0 is updated as necessary. This completes method M1.")

- U.S. Patent No, 6,085,295 to Ekanadham: *See*, *e.g.*, 2:25-33 ("In a node where a remote line is brought into the cache of a processor, but not into the node's memory, the adapter acts as a proxy memory representing the remote memory that the line is mapped onto. More specifically, when a memory command is issued from a local processor to a remote memory, the memory command is directed to the adapter which is responsible for insuring that the command is executed at that remote memory.")

- Ekanadham: *See*, *e.g.*, 3:37-45 ("The preferred embodiment of our system that is based on a network of switch-based SMP nodes with an adapter attached to each node. FIG. 1 illustrates a high-level diagram of such a multiprocessing system. Each node has a plurality of processors P1, P2, ..., PN interconnected to each other by a switch (SW).

The switch also interconnects the memory modules M1, M2, ..., MN and adapters A. The nodes in turn, are connected to each other through a network as shown.")

- Ekanadham: *See*, *e.g.*, 3:49-56 ("The adapter connects to the switch and plays the role of either a memory or a processor. The behavior of the adapter is different for different memory lines. When a line is homed at the local memory of the node, the adapter behaves as a proxy processor for that line. When a line is homed at the memory of a remote node, the adapter behaves as a proxy memory for that line. These roles are illustrated in FIGS. 3A-3C and are elaborated further below." )

- Ekanadham: See, e.g., 4:7-24 ("In a node in which a line is homed in the local memory, the adapter plays the role of a proxy processor representing the accesses to the line made by the processors in other nodes of the system. In this role, the adapter maintains a state for the line and the list of all nodes sharing that line. The state can be I (indicating that no other node has this line), E (indicating that some other node has exclusive copy of this line) or S (indicating that this line is shared by this and other nodes). As a proxy processor, the adapter receives requests from other adapters and performs the reads and writes in this node on their behalf. Whenever a local processor requires exclusive access to the line while it is in shared state, it communicates with other adapters and invalidates the line in all other nodes. When another node requests for exclusive copy of the line. The adapter only invalidates the copies in all other nodes, but also requests the local memory to grant the exclusive access. The memory controller treats the adapter as another processor.")

- Ekanadham: See, e.g., 4:26-41 ("In a node in which a line is homed at a remote memory, the adapter acts as a proxy memory. It captures all the transactions for the corresponding address and runs the memory protocol. In this role, the adapter maintains a state for the line and the list of local caches sharing the line. The state can be I (indicating that no local cache this line), E (indicating that some local cache has exclusive copy of this line) or S (indicating that this line is shared by this and other nodes). As a proxy memory, the adapter responds to all requests to the line and obtains the contents of the line from the remote node (where that line is backed by memory) and supplies the contents to the local caches. It performs the usual coherence control operations in the node and coordinates with other adapters. In order to maintain global coherence, it may have to issue some bus transactions as a master, as illustrated later.")

Ekanadham, Figure 1

- U.S. Patent No, 6,141,692 to Loewenstein: See, e.g., 6:29-33 ("Requests for data and responses to those requests are exchanged between nodes by the respective HA, SA, and RA of each global interface (i.e., 415, 425, 435, and 445) in the form of data/control packets, thereby enabling each node to keep track of the status of all data cached therein.")

- Loewenstein: See, e.g., 11:1-9 ("When the system is operating in NUMA mode, a typical read request (e.g., a Read-- To-- Share request) by processor 411a of node 410 occurs in the following manner. To initiate the request, processor 411a presents a virtual address (VA) to MMU 412a, which converts the VA into a GA and presents the GA to cache 413a. If there is a valid copy of the data line of interest in cache 413a (e.g., a shared or owned copy), then cache 413a provides the data to processor 411a via MMU 412a, thereby completing the read request.")

- Loewenstein: *See*, *e.g.*, 11:10-15 ("However, if cache 413a does not have a valid copy, then cache 413a presents the GA to the local interconnect 419 of its associated node. If the GA is not part of the node 410's local address space (i.e., node 410 is not the home node for the requested address), then the request is forwarded to the appropriate home node (i.e., node 420).")

- Loewenstein: *See*, *e.g.*, 11:40-50 ("If the home node is determined to have a valid copy of the requested data line, then the home node provides the data to the requesting node. In the case where the requesting node is also the home node, only an internal data transfer is required. Alternatively, where the home node is not the requesting node, then the global interface of the home node (global interface 425 in the above example) responds by retrieving the requested data line from the main memory 424 or from a

cache line which is owned by a processor within node 420, and sends the data line to the global interface 415 of the requesting node 410 via global interconnect 450.")

• Loewenstein: See, e.g., 11:60-64 ("Upon receiving the data line, global interface 415 forwards the data line to cache 413a, which provides the data to the requesting processor 411a.")

Loewenstein, Figure 4

U.S. Patent No, 6,751,721 to Webb: See, e.g., Abstract ("A directory-based ٠ multiprocessor cache control scheme for distributing invalidate messages to change the state of shared data in a computer system. The plurality of processors are grouped into a plurality of clusters. A directory controller tracks copies of shared data sent to processors in the clusters. Upon receiving an exclusive request from a processor requesting permission to modify a shared copy of the data, the directory controller generates invalidate messages requesting that other processors sharing the same data invalidate that data. These invalidate messages are sent via a point-to-point transmission only to master processors in clusters actually containing a shared copy of the data. Upon receiving the invalidate message, the master processors broadcast the invalidate message in an ordered fan-in/fan-out process to each processor in the cluster. All processors within the cluster invalidate a local copy of the shared data if it exists and once the master processor receives acknowledgements from all processors in the cluster, the master processor sends an invalidate acknowledgment message to the processor that originally requested the exclusive rights to the shared data. The cache

coherency is scalable and may be implemented using the hybrid point-to-point/broadcast scheme or a conventional point-to-point only directory-based invalidate scheme.")

As illustrated by the prior art references above, it was well known before the priority dates

of the Asserted Patents to implement a "cache coherence controller" "constructed to act as a

remote memory" in a multiprocessor system, at least under Memory Integrity's apparent

infringement theories. A person of ordinary skill would have been motivated to implement a

"cache coherence controller" "constructed to act as a remote memory" in a multiprocessor system

as described below:

- Ekanadham: See, e.g., 1:23-35 ("Technology considerations limit the size of an SMP node to a small number of processors. A method for building a shared-memory multiprocessor with a larger number of processors is to connect a number of SMP nodes with a network, and provide an adapter to extend the SMP's memory across the SMP nodes (see FIG. 1). Existing adapter designs plug into the memory bus of bus-based SMP nodes and collectively provide shared memory across the system, so that any processor in any node can access any location in any memory module in the system. Resources within a node are termed local and resources on other nodes are termed remote.")

- Ekanadham: *See*, *e.g.*, 2:37-41 ("By appearing as either a local processor or a local memory, the adapter uses the local SMP coherence protocol within a node to accomplish the above tasks, without any changes to the memory controllers.")

- Loewenstein: See, e.g., 5:1-8 ("Since global interface 115 is also responsible for maintaining global cache coherency, global interface 115 includes a hardware and/or software implemented cache-coherency mechanism for maintaining coherency between the respective caches and main memories of nodes 110, 120, ... 180. Cache coherency is essential in order for the system 100 to properly execute shared-memory programs correctly.")

Accordingly, it would have been obvious to implement a "cache coherence controller"

"constructed to act as a remote memory" in a multiprocessor system having multiple clusters of processors while maintaining coherency with a reasonable expectation of success. Furthermore, it would have been obvious to implement a "cache coherence controller" "constructed to act as a remote memory" because such a modification would simply be the use of a known technique (*e.g.*,

a cache coherence controller "constructed to act as a remote memory") to improve similar devices (*e.g.*, multiprocessor systems) in the same way (*e.g.*, improve performance and scalability while maintaining coherency).

#### 11. "Shared Memory Address Space"

Some of the Asserted Claims are directed to a shared memory address space. For example, claim 9.1 of the '409 patent recites "the plurality of local processors in the local cluster share a memory address space with a plurality of non-local processors in the non-local cluster." *See also, e.g.*, '409 patent claims 25.6, 27.1, 34.6, and 36.1; '636 patent claims 13.1 and 24.1; and '254 patent claims 1.5-1.11 and 8.1. Claim 42.4 of '409 patent also recites "the first and second processors sharing a common virtual address space." At least under Memory Integrity's apparent infringement theories, sharing an address space and/or sharing a common virtual address space between processors in a multiprocessor system was well-known in the art before the priority dates of the Asserted Patents. *See, e.g.*, Exhibits A-1 – A-9, claims 9.1, 25.6, 27.1, 34.6, 36.1, and 42.4; Exhibits B-1 – B-19, claims 13.1 and 24.1; and Exhibits E-1 – E-14, claims 1.5-1.11 and 8.1. The following discussion further shows that, at least under Memory Integrity's apparent infringement theory, it was well known and conventional to share an address space and/or share a common virtual address space between processors in multiprocessors in multiprocessor systems.

As an initial matter, the Asserted Patents acknowledge that a shared memory address space was well known. *See*, *e.g.*, '409 patent at 2:18-3:40 ("Background of the Invention ... Although, cache coherency mechanisms such as bus arbitration are effective, using a shared bus limits the number of processors that can be implemented in a single system with a single memory space. ... Performance limitations have led to the development of a point-to-point architecture for connecting processors in a system with a single memory space. ... However, using a point-to-point architecture to connect multiple processors in a multiple cluster system sharing a single memory

- 175 -

space presents its own problems."); '636 patent at 1:33-2:59; '121 patent at 1:20-2:38; '206 patent

at 1:13-38; and '254 patent at 1:16-41.

Indeed, under Memory Integrity's apparent infringement theories, there are many

examples of prior art references that disclose sharing an address space and/or a common virtual

address space between processors in a multiprocessor system and further demonstrate that such

features were well known include:

- "Computer Organization & Design," Patterson et al. (1998): See, e.g., p. 713 ("Single address space multiprocessors come in two styles. The first takes the same time to access main memory no matter which processor requests it and no matter which word is asked. Such machines are called *uniform memory access (UMA)* multiprocessors or *symmetric multiprocessors (SMP)*. In the second style, some memory accesses are faster than others depending on which processor asks for which word. Such machines are called *nonuniform memory access (NUMA)* multiprocessors. As you might expect, there are more programming challenges to get highest performance from a NUMA multiprocessor than a UMAmultiprocessor, but NUMAmachines can scale to larger sizes and hence are potentially higher performance.")

- Patterson: See, e.g., p. 713 ("The alternative model to shared memory for communicating uses message passing for communicating among processors. Message passing is required for machines with private memories, in contrast to shared memory. As an extreme example, processors in different desktop computers communicate by passing messages over a local area network. Provided the system has routines to send and receive messages, coordination is built in with message passing since one processor knows when a message is sent and the receiving processor knows when a message arrives. The receiving processor can then send a message back to the sender saying the message has arrived, if the sender needs that confirmation.")

| Name                          | Maximum<br>number of<br>processors | Processor<br>name | Processor<br>clock<br>rate | Maximum<br>memory size/<br>system | Communi-<br>cations<br>BW/link | Node      | Topology                    |

|-------------------------------|------------------------------------|-------------------|----------------------------|-----------------------------------|--------------------------------|-----------|-----------------------------|

| Cray Research T3E             | 2048                               | Alpha 21164       | 450 MHz                    | 524,288 MB                        | 1200 MB/sec                    | 4-way SMP | 3-D torus                   |

| HP/Convex<br>Exemplar X-class | 64                                 | PA-8000           | 180 MHz                    | 65,536 MB                         | 980 MB/sec                     | 2-way SMP | 8-way<br>crossbar<br>+ ring |

| Sequent NUMA-Q                | 32                                 | Pentium Pro       | 200 MHz                    | 131,072 MB                        | 1024 MB/sec                    | 4-way SMP | Ring                        |

| SGI Origin2000                | 128                                | MIPS R10000       | 195 MHz                    | 131,072 MB                        | 800 MB/sec                     | 2-way SMP | 6-cube                      |

| Sun Enterprise<br>10000       | 64                                 | UltraSPARC 1      | 250 MHz                    | 65,536 MB                         | 1600 MB/sec                    | 4-way SMP | 16-way<br>crossbar          |

FIGURE 9.9 Characteristics of multiprocessor computers connected by a network that are for sale in 1997. All these machines have a shared address space with nonuniform memory access time except for the Sun Enterprise 10000, which offers a shared address with uniform memory access time. And all these machines except the Cray Research T3E are cache coherent, with the HP, Sequent, and SQI using directories. The Sun machine uses buses for addresses and a switch for data, so it supports coherency with conventional snooping on the address buses. Communication bandwidth is peak per link, counting all bytes sent including network headers. The bisection bandwidth typically scales with the number of processors. (See *www.mkp.com/cod2e.htm* for pointers to these and more recent network-connected multiprocessors.)

#### Patterson, Figure 9.9

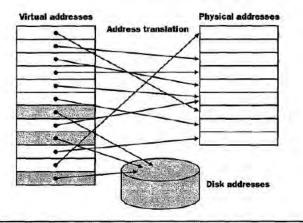

• Patterson: See, e.g., p. 579 ("7.4 Virtual Memory In the previous section, we saw how caches served as a method for providing fast access to recently used portions of a program's code and data. Similarly, the main memory can act as a 'cache' for the secondary storage, usually implemented with magnetic disks. This technique is called virtual memory. There are two major motivations for virtual memory: to allow efficient and safe sharing of memory among multiple programs and to remove the programming burdens of a small, limited amount of main memory.")

FIGURE 7.20 In virtual memory, blocks of memory (called pages) are mapped from one set of addresses (called virtual addresses) to another set (called physical addresses). The processor generates virtual addresses while the memory is accessed using physical addresses. Both the virtual memory and the physical memory are broken into pages, so that a virtual page is really mapped to a physical page. Of course, it is also possible for a virtual page to be absent from main memory and not be mapped to a physical address, residing instead on disk. Physical pages can be shared by having two virtual addresses point to the same physical address. This capability is used to allow two different programs to share data or code.

Patterson, Figure 7.20

- "Computer Organization," Hamacher (2001): See, e.g., p. 637 ("In Chapter 5 we saw that the organization of the memory in a uniprocessor system has a large impact on performance. The same is true in multiprocessor systems. To exploit the locality of reference phenomenon, each processor usually includes a primary cache and a secondary cache. If the organization in Figure 12.2 is used, then each processor module can be connected to the communication network as shown in Figure 12.12. Only the secondary cache is shown in the figure since the primary cache is assumed to be a part of the processor chip. The memory modules are accessed using a single global address space, where a range of physical addresses is assigned to each memory module. In such a shared memory system, the processors access all memory modules in the same way. From the software standpoint, this is the simplest use of the address space.")

- Hamacher: See, e.g., p. 637-638 ("In NUMA-organized multiprocessors, shown in Figure 12.3, each node contains a processor and a portion of the memory. A natural way of implementing the node is illustrated in Figure 12.13. In this case, it is also convenient to use a single global address space. Again, the processor accesses all memory modules in the same way, but the accesses to the local memory component of the global address space take less time to complete than accesses to remote memory modules.")

- Hamacher: *See*, *e.g.*, p. 638 ("In the organization of Figure 12.4, each processor accesses directly only its own local memory. Thus, each memory module constitutes the private address space of one processor; there is no global address space. Any interaction among programs or processes running on different processors is implemented by sending messages from one processor to another. In this form of communication, each processor views the interconnection network as an I/O device. In effect, each node in such a system behaves as a computer in the same manner as discussed in previous chapters for uniprocessor machines. For this reason, systems of this type are referred to also as multicomputers. This organization, provides the easiest way to connect a number of computers into a large system. Communication between tasks running on different computers is relatively slow because the exchange of messages requires software intervention. We consider this type of system in Section 12.7.")

- "Parallel Computer Architecture," Culler et al. (1998): See, e.g., p. 28 ("One of the most important classes of parallel machines is shared memory multiprocessors. The key property of this class is that communication occurs implicitly as a result of conventional memory access instructions (i.e., loads and stores). This class has a long history, dating at least to precursors of mainframes in the early 1960s,<sup>3</sup> and today it has a role in almost every segment of the computer industry. Shared memory multiprocessors serve to provide better throughput on multiprogramming workloads, as well as to support parallel programs. Thus, they are naturally found across a wide range of scale, from a few processors to perhaps hundreds. This section examines the communicator architecture of shared memory machines and the key organizational issues for small-scale designs and large configurations.")

- U.S. Patent No. 5,796,605 to Hagersten: See, e.g., Abstract ("A technique for system memory space address mapping in a multiprocessor computer system is provided. The disclosed mapping architecture may be applied to a multiprocessor computer system having multiple processing nodes (SMP nodes), where each processing node may include multiple processors. The system memory address space is split into different regions such that each of the n SMP nodes is assigned 1/n of the total address space. Cache coherency state information is stored for the memory in each SMP node.")

- U.S. Patent No. 6,336,177 to Stevens: *See*, *e.g.*, 6:59-65 ("The light shaded sections, 402, 406, 410, and 414 indicate that these areas of the virtual address space are shared by at least two threads. Note that in this example, the virtual address space 304 is represented in a wrap-around fashion so that the shared section 402 appears both the top and at the bottom of the virtual address space 304."); *See*, *e.g.*, 7:49-57 ("FIG. 5 depicts an example of memory placement that could occur, if the known memory access patterns, as described above with reference to FIG. 4, are not taken into account for the purpose of maximizing memory placement locality. Accordingly, in this example, the threads 302 a and 302 b are randomly mapped to the node 502, in one comer of the system 316, while the threads 302 c and 302 d are randomly mapped to the node 504, in the opposite comer of the system 316.")

- U.S. Patent No. 6,490,671 to Frank: See, e.g., 1:46-56 ("In a multi-processor machine, a process may be divided into threads of execution, some threads executing on different CPUs. All of a process's threads share a common virtual address space. Each of the CPUs, however, maintains its own copy of the TLB. When any of the CPUs in the machine invalidates an entry in the TLB, each CPU is notified, traditionally by means of a hardware interrupt, that there has been a change to the TLB and refreshes its copy. Invalidating TLB entries, however, is very expensive, because all of the CPUs on the machine stop their processing to perform the refresh.")

- U.S. Patent No. 6,631,448 to Weber: See, e.g., 1:34-51 ("A distributed, shared-memory system is known as a distributed shared-memory (DSM) or a non-uniform memory access (NUMA) architecture." "DSM architecture provides a single shared address space to the programmer where all memory locations may be accessed by every processor. As there is no need to distribute data or explicitly communicate data between the processors in software, the burden of programming a parallel machine is simpler in a DSM model. In addition, by dynamically partitioning the work, DSM architecture makes it easier to balance the computational load between processors. Finally, as shared memory is the model provided on small-scale multiprocessors, DSM architecture facilitates the portability of programs parallelized for a small system to a larger shared-memory system. In contrast, in a message-passing system, the programmer is responsible for partitioning all shared data and managing communication of any updates.")

- U.S. Patent Application No. 2003/0009640 to Arimilli: *See, e.g.*, para. [0043] ("To illustrate the present invention, an embodiment will be described in which instruction sequencing unit 52 and LSU 68 of each CPU 20 in NUMA data processing system 10 reference instructions and data utilizing 32-bit effective addresses, meaning that CPUs

20 have a 4 Gbyte (2<sup>32</sup>) effective address space. This effective address space is a subset of a much larger virtual address space referenced by 52-bit virtual addresses. This virtual address space, which is shared by all CPUs 20 in NUMA data processing system 10, is partitioned into a number of (e.g., 4 Kbyte) memory pages, which each have an Page Table Entry (PTE) address descriptor that associates the base virtual address of the memory page with the corresponding physical address of the memory page in one of system memories 26.")

• U.S. Patent No. 6,684,305 to Deneau: *See, e.g.*, 7:21-36 ("The main processor operating system 206 creates and maintains both the main processor page tables 200 and the co-processor page tables 202, and embodies virtual-to-physical address translation mechanisms of both the main processor 102 and the co-processor, 104. The main processor page tables 200 are used by the main processor 102 to translate virtual addresses generated within the main processor 102 to physical addresses within the shared memory 106. The co-processor page tables 202 are used by the co-processor 104 to translate virtual addresses generated within the co-processor 104 to physical addresses within the shared memory 106. The main processor 102 and the co-processor 104 to physical addresses generated within the shared memory 106. The main processor 102 and the co-processor 104 to physical addresses generated within the shared memory 106. The main processor 102 and the co-processor 104 share a common physical address space within the shared memory 106. For simplicity of operation, the main processor 102 and the co-processor 104 may also share a common virtual address space.")

As illustrated by the prior art references above, it was well known before the priority dates

of the Asserted Patents to share an address space and/or a common virtual address space between

processors in a multiprocessor system, at least under Memory Integrity's apparent infringement

theories. Indeed, a person of ordinary skill would have been motivated to implement a shared an

address space and/or a common virtual address space as described below:

- Hamacher: *See*, *e.g.*, p. 637 ("The memory modules are accessed using a single global address space, where a range of physical addresses is assigned to each memory module. In such a shared memory system, the processors access all memory modules in the same way. From the software standpoint, this is the simplest use of the address space.")

- Weber: *See*, *e.g.*, 1:38-51 ("DSM architecture provides a single shared address space to the programmer where all memory locations may be accessed by every processor. As there is no need to distribute data or explicitly communicate data between the processors in software, the burden of programming a parallel machine is simpler in a DSM model. In addition, by dynamically partitioning the work, DSM architecture makes it easier to balance the computational load between processors. Finally, as shared memory is the model provided on small-scale multiprocessors, DSM architecture facilitates the portability of programs parallelized for a small system to a larger shared-memory system. In contrast, in a message-passing system, the programmer is responsible for partitioning all shared data and managing communication of any updates.")

• Patterson: See, e.g., p. 579 ("7.4 Virtual Memory ... This technique is called virtual memory. There are two major motivations for virtual memory: to allow efficient and safe sharing of memory among multiple programs and to remove the programming burdens of a small, limited amount of main memory.")

Accordingly, it would have been obvious to implement a shared address and/or a common virtual address space between processors in a multiprocessor system because doing so would simply be an obvious engineering design choice by selecting one of a finite number of known options (*e.g.*, shared address space or message passing and physical mapping or virtual address mapping) according to the desired multiprocessor system implementation with a reasonable expectation of success. Furthermore, it would have been obvious to implement a shared address space and/or a common virtual address space between processors in a multiprocessor system because such a modification would simply be the use of a known technique (*e.g.*, shared address space and/or a common virtual address space) to improve similar devices (*e.g.*, multiprocessor systems) in the same way (*e.g.*, simplified programming, improved computational load balancing, efficient and safe sharing of memory among multiple programs, etc.).

#### 12. "Protocol Engines"

Some of the Asserted Claims are directed to one or more protocol engines. For example, some of the Asserted claims are directed to a cache coherence controller comprising a protocol engine coupled to interface circuitry. *See*, *e.g.*, '409 patent claims 7.4, 8.1, 10.1, 12.1, and 22.1; '636 patent claims 22.3. 22.4, 23.1, 27.1, and 33.1. Some of the Asserted Claims are directed to an interconnection controller including one or more protocol engines for processing transactions, for example, in accordance with a cache coherence protocol, or for processing interrupts. *See*, *e.g.*, '206 patent claims 1.4, 1.5, 1.6, 14.2, 19.2, 19.3, 21.4, 21.5, 21.6, 30.3, 30.4, 30.5, 35.1, 38.2, 39.4, 39.5, 39.7, 39.8, 41.1, and 44.2; '254 patent claims 1.4, 1.5, 1.6, 1.8, 1.10, 1.11, 6.2, and 7.1. At least under Memory Integrity's apparent infringement theories, an interconnection or cache

coherence controller including one or more protocol engines coupled to interface circuitry, for processing transactions in accordance with a cache coherence protocol, etc. was well-known in the art at the time of the alleged invention of the Asserted Claims. *See, e.g.*, Exhibits A-1 – A-9 claims 7.4, 8.1, 10.1, 12.1, and 22.1; Exhibits B-1 – B-19 claims 22.3. 22.4, 23.1, 27.1, and 33.1; Exhibits D-1 – D-14, claims 1.4, 1.5, 1.6, 14.2, 19.2, 19.3, 21.4, 21.5, 21.6, 30.3, 30.4, 30.5, 35.1, 38.2, 39.4, 39.5, 39.7, 39.8, 41.1, and 44.2; and Exhibits E-1 – E-14 claims 1.4, 1.5, 1.6, 1.8, 1.10, 1.11, 6.2, and 7.1. At least under Memory Integrity's apparent infringement theories, there are many additional exemplary prior art references that disclose an interconnection or cache coherence controller including a plurality of protocol engines coupled to interface circuitry, for processing transactions in accordance with a cache coherence protocol, etc. Some examples include:

- See, e.g., Tendler et al., "POWER4 system microarchitecture," at

- *Page* 6 ("The two processors share a unified second-level cache, also on the same chip, through a core interface unit (CIU), as shown in Figure 1. The CIU is a crossbar switch between the L2, implemented as three separate, autonomous cache controllers, and the two processors. Each L2 cache controller can operate concurrently and feed 32 bytes of data per cycle. The CIU connects each of the three L2 controllers to either the data cache or the instruction cache in either of the two processors. Additionally, the CIU accepts stores from the processors across 8-byte-wide buses and sequences them to the L2 controllers."),

- Figure 1,

- Page 7 ("Four POWER4 chips can be packaged on a single module to form an eight-way SMP. Four such modules can be interconnected to form a 32-way SMP. To accomplish this, each chip contains five primary interfaces. To communicate with other POWER4 chips on the same module, there are logically four 16-byte buses. Physically, these four logical buses are implemented with six buses, three on and three off, as shown in Figure 1. To communicate with POWER4 chips on other modules, there are two 8-byte buses, one on and one off. Each chip has its own interface to the off-chip L3 across two 16-bytewide buses, one on and one off, operating at one-third processor frequency."),

- Page 15 ("The unified second-level cache is shared across the two processors on the POWER4 chip. Figure 5 shows a logical view of the L2 cache. The L2 is implemented as three identical slices, each with its own controller. Cache lines are hashed across the three controllers."),

- Figure 5,

- Page 16 ("The majority of control for L2 cache management is handled by four coherency processors in each controller. A separate coherency processor is assigned to handle each request to the L2. Requests can come from either of the two processors (for either an L1 data-cache reload or an instruction fetch) or from one of the store queues."),

- Page 16 ("Included in each L2 controller are four snoop processors responsible for managing coherency operations snooped from the fabric."),

- Page 16 ("The L2 cache implements an enhanced version of the MESI coherency protocol . . .").

- See, e.g., Behling et al., "The POWER4 Processor Introduction and Tuning Guide," at

- Page 15 ("Stores can be sent to the L2 cache at a maximum rate of one store per cycle. Store data is directed to the proper L2 controller (through a hashing function) by way of the storage slice queue (SSQ) and the L2 store queue (STQ)."),

- Page 17 ("Each POWER4 chip has an L2 cache that is supervised by three L2 controllers, each of which manages 480 KB, for a total L2 size of 1440 KB. Cache lines are hashed across the three controllers. Cache line replacement is implemented as a binary-tree pseudo-LRU algorithm. The L2 cache is a unified cache: it caches instructions, data, and page table entries. The L2 cache is also shared by the processors on the chip."),

- Page 18 ("Memory coherency in the system is enforced primarily at the L2 cache level by L2 cache controllers. Each L2 has associated command queues, known as coherency processors. Snoop processors within each controller observe all transactions in the system and respond accordingly, providing responses or delivering cache lines if the situation merits."),

- Page 30 ("The size of the L2 cache is 1440 KB per POWER4 chip, and this is shared between the two processors in the chip. As with the L1 data cache, the cache line size is 128 bytes. The replacement policy is pseudo-LRU (least recently used) so frequently accessed cache lines should be readily maintained in the cache. The L2 cache is a combined data and instruction cache. Instruction caching aspects of the L2 cache are not considered here. The L2 cache is divided into three equal parts, each under control of a separate L2 cache controller. The particular portion a line is stored is in is determined from the real memory address using a hashing algorithm. Sixteen consecutive double-precision Fortran array elements (138 bytes) are held in the same cache line, and therefore under control of the same cache controller. The 17th element will be in a different cache line and the hashing algorithm guarantees it will be stored under control of a different cache controller.").

- See, e.g., IBM POWER4 processor (as disclosed at least in the above references)

• See, e.g., Intel 870 Chipset

- See, e.g., U.S. Patent No. 7,093,079 to Quach at