# Application-Specific Integrated Circuits Michael John Sebastian Smith

Sony-1019

## Application-Specific Integrated Circuits

Michael John Sebastian Smith

**V** ADDISON–WESLEY

Boston • San Francisco • New York • Toronto • Montreal London • Munich • Paris • Madrid Capetown • Sidney • Tokyo • Singapore • Mexico City This book is in the Addison-Wesley VLSI Systems Series Lynn Conway and Charles Seitz, *Consulting Editors*

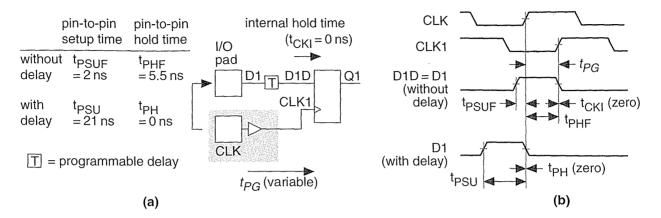

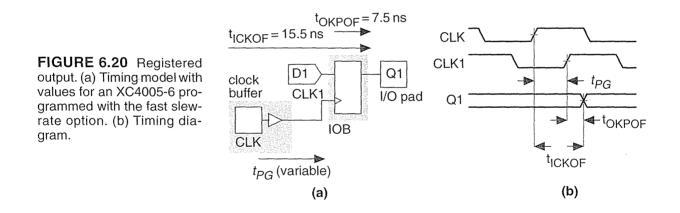

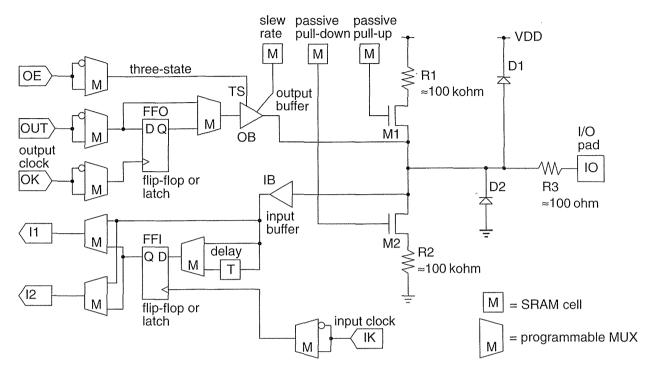

Sponsoring Editor Associate Editor Senior Production Supervisor Copyeditor/Proofreader Cover Design Supervisor Marketing Manager Manufacturing Manager Peter Gordon Helen Goldstein Juliet Silveri Cynthia Benn Simone Payment Tracy Russ Roy Logan

Material in Chapters 10-12, Chapter 14, Appendix A, and Appendix B in this book is reprinted from IEEE Std 1149.1-1990, "IEEE Standard Test Access Port and Boundary-Scan Architecture," Copyright © 1990; IEEE Std 1076/INT-1991 "IEEE Standards Interpretations: IEEE Std 1076-1987, IEEE Standard VHDL Language Reference Manual," Copyright © 1991; IEEE Std 1076-1993 "IEEE Standard VHDL Language Reference Manual," Copyright © 1993; IEEE Std 1164-1993 "IEEE Standard Multivalue Logic System for VHDL Model Interoperability (Std\_logic\_1164)," Copyright © 1993; IEEE Std 1149.1b-1994 "Supplement to IEEE Std 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan Architecture," Copyright © 1994; IEEE Std 1076.4-1995 "IEEE Standard for VITAL Application-Specific Integerated Circuit (ASIC) Modeling Specification," Copyright © 1995; IEEE 1364-1995 "IEEE Standard Description Language Based on the Verilog® Hardware Description Language," Copyright © 1995; and IEEE Std 1076.3-1997 "IEEE Standard for VHDL Synthesis Packages," Copyright © 1997; by the Institute of Electrical and Electronics Engineers, Inc. The IEEE disclaims any responsibility or liability resulting from the placement and use in the described manner. Information is reprinted with the permission of the IEEE. Figures produced by the Compass Design Automation software in Chapters 9-17 are reprinted with permission of Compass Design Automation. Figures describing Xilinx FPGAs in Chapters 4-8 are courtesy of Xilinx, Inc. ©Xilinx, Inc. 1996, 1997. All rights reserved. Figures describing Altera CPLDs in Chapters 4-8 are courtesy of Altera Corporation. Altera is a trademark and service mark of Altera Corporation in the United States and other countries. Altera products are the intellectual property of Altera Corporation and are protected by copyright laws and one or more U.S. and foreign patents and patent applications. Figures describing Actel FPGAs in Chapters 4-8 are courtesy of Actel Corporation.

#### Library of Congress Cataloging-in-Publication Data

Smith, Michael J. S. (Michael John Sebastian)

Application-specific integrated circuits / Michael J.S. Smith.

p. cm.

Includes bibliographical references and index.

ISBN 0-201-50022-1

1. Application-specific integrated circuits. I. Title.

TK7874.6.S63 1997

621.39'5--dc20

93-32538

CIP

Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and we were aware of a trademark claim, the designations have been printed in initial capital letters or in all capitals.

The author and publisher have taken care in the preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein.

Visit AW on the Web: www.awl.com/cseng/

Copyright © 1997 by Addison-Wesley

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior consent of the publisher. Printed in the United States of America. Published simultaneously in Canada.

ISBN 0-201-50022-1 Text printed on recycled paper 8 9 10 11 12 13 14—CRW—0403020100 8th printing, May 2000

## PREFACE

In 1988 I began to teach full-custom VLSI design. In 1990 I started teaching ASIC design instead, because my students found it easier to get jobs in this field. I wrote a proposal to The National Science Foundation (NSF) to use electronic distribution of teaching material. Dick Lyon helped me with preparing the first few CD-ROMs at Apple, but Chuck Seitz, Lynn Conway, and others explained to me that I was facing a problem that Carver Mead and Lynn had experienced in trying to get the concept of multichip wafers adopted. It was not until the publication of the Mead-Conway text that people accepted this new idea. It was suggested that I must generate interest using a conventional format before people would use my material in a new one (CD-ROM or the Internet). In 1992 I stopped writing papers and began writing this book-a result of my experiments in computer-based education. I have nearly finished this book twice. The first time was a copy of my notes. The second time was just before the second edition of Weste and Eshragian was published-a hard act to follow. In order to finish in 1997 I had to stop updating and including new ideas and material and now this book consists of three parts: Chapters 1-8 are an introduction to ASICs, 9-14 cover ASIC logical design, and 15-17 cover the physical design of ASICs.

The book is intended for a wide audience. It may be used in an undergraduate or graduate course. It is also intended for those in industry who are involved with ASICs. Another function of this book is an "ASIC Encyclopedia," and therefore I have kept the background material needed to a minimum. The book makes extensive use of industrial tools and examples. The examples in Chapters 2 and 3 use tools and libraries from MicroSim (PSpice), Meta Software (HSPICE), Compass Design Automation (standard-cell and gate-array libraries), and Tanner Research (L-Edit). The programmable ASIC design examples in Chapter 4–8 use tools from Compass, Synopsys, Actel, Altera, and Xilinx. The examples in Chapter 9 (covering low-level design entry) used tools from Exemplar, MINC, AMD, UC Berkeley, Compass, Capilano, Mentor Graphics Corporation, and Cadence Design Systems. The VHDL examples in Chapter 10 (VHDL) were checked using QuickVHDL from Mentor, V-System Plus from Model Technology, and Scout from Cadence, V-System Plus, and VeriWell from Wellspring Solutions. The logic synthesis examples in

6

iii

Chapter 12 were checked with the ASIC Synthesizer product family from Compass and tools from Mentor, Synopsys, and UC Berkeley. The simulation examples in Chapter 13 were checked with QuickVHDL, V-System/Plus, PSpice, Verilog-XL, DesignWorks from Capilano Computing, CompassSim, QSim, MixSim, and HSPICE. The test examples in Chapter 14 were checked using test software from Compass, Cadence, Mentor, Synopsys and Capilano's DesignWorks. The physical design examples in Chapters 15–17 were generated and tested using Preview, Gate Ensemble, and Cell Ensemble (Cadence) as well as ChipPlanner, ChipCompiler, and PathFinder (Compass). All these tools are installed at the University of Hawaii.

I wrote the text using FrameMaker. This allows me to project the text and figures using an LCD screen and an overhead projector. I used a succession of Apple Macintosh computers: a PowerBook 145, a 520, and lastly a 3400 with 144MB of RAM, which made it possible for me to create updates to the index in just under one minute. Equations are "live" in FrameMaker. Thus,

book thickness = #pages × 0.0015 in./page ≈ (1000) (1.5 × 10<sup>-3</sup>) = 1.5 in.

can be updated in a lecture and the new result displayed. The circuit layouts are color EPS files with enhanced B&W PICT previews created using L-Edit from Tanner Research. All of the Verilog and VHDL code examples, compiler and simulation input/output, and the layout CIF that were used in the final version are included as conditional (hidden) text in the FrameMaker document, which is approximately 200MB and just over 6,000 pages (my original source material spans fourteen 560MB optical disks). Software can operate on the hidden text, allowing, for example, a choice of simulators to run the HDL code live in class. I converted draft versions of the VHDL and Verilog LRMs and related standards to FrameMaker and built hypertext links to my text, but copyright problems will have to be solved before this type of material may be published. I drew all the figures using FreeHand. They are "layered" allowing complex drawings to be built-up slowly or animated by turning layers on or off. This is difficult to utilize in book form, but can be done live in the classroom.

A course based on FPGAs can use Chapter 1 and Chapters 4–8. A course using commercial semicustom ASIC design tools may use Chapters 1–2 or Chapters 1–3 and then skip to Chapter 9 if you use schematic entry, Chapter 10 (if you use VHDL), or Chapter 11 (if you use Verilog) together with Chapter 12. All classes can use Chapters 13 and 14. FPGA-based classes may skim Chapters 15–17, but classes in semicustom design should cover these chapters. The chapter dependencies—Y (X) means Chapter Y depends on X—are approximately: 1, 2(1), 3(2), 4(2), 5(4), 6(5), 7(6), 8(7), 9(2), 10(2), 11(2), 12(10 or 11), 13(2), 14(13), 15(2), 16(15), 17(16).

I used the following references to help me with the orthography of complex terms, style, and punctuation while writing: *Merriam-Webster's Collegiate Dictionary*, 10th edition, 1996, Springfield, MA: Merriam-Webster, ISBN 0-87779-709-9, PE1628.M36; *The Chicago Manual of Style*, 14th edition, Chicago: University of

7

Chicago Press, 1993, ISBN 0-226-10389-7, Z253.U69; and *Merriam-Webster's Standard American Style Manual*, 1985, Springfield, MA: Merriam-Webster, ISBN 0-87779-133-3, PN147.W36. A particularly helpful book on technical writing is *BUGS in Writing* by Lyn Dupré, 1995, Reading, MA: Addison-Wesley, ISBN 0-201-60019-6, PE1408.D85 (Lyn's book grew from her unpublished work, Style SomeX, which I used).

The bibliography at the end of each chapter provides alternative sources if you cannot find what you are looking for. I have included the International Standard Book Number<sup>1</sup> (ISBN) and Library of Congress (LOC) Call Number for books, and the International Standard Serial Number<sup>2</sup> (ISSN) for journals (see the LOC information system, LOCIS, at http://www.loc.gov). I did not include references to material that I could not find myself (except where I have noted in the case of new or as yet unpublished books). The electronic references given in this text have (a last) access date of 4/19/97 and omit enclosing <> if the reference does not include spaces.

I receive a tremendous level of support and cooperation from industry in my work. I thank the following for help with this project: Cynthia Benn and Lyn Dupré for editing; Helen Goldstein, Peter Gordon, Susan London-Payne, Tracy Russ, and Juliet Silveri, all at Addison-Wesley; Matt Bowditch and Kim Arney at Argosy; Richard Lyon, Don North, William Rivard, Glen Stone, the managers of the Newton group, and many others at Apple Computer who provided financial support; Apple for providing support in the form of software and computers; Bill Becker, Fern Forcier, Donna Isidro, Mike Kliment, Paul McLellan, Tom Schaefer, Al Stein, Rich Talburt, Bill Walker, and others at Compass Design Automation and VLSI Technology for providing the opportunity for me to work on this book over many years and allowing me to test material inside these companies and on lecture tours they sponsored; Chuck Seitz at Caltech; Joseph Cavallaro, Bernie Chern, Jerry Dillion, Mike Foster, and Paul Hulina at the NSF; the NSF for financial support with a Presidential Young Investigator Award; Jim Rowson and Doug Fairbairn; Constantine Anagnostopolous, Pin Tschang and members of the ASIC design groups at Kodak for financial support; the disk-drive design group at Digital Equipment Corp. (Massachusetts), Hewlett-Packard, and Sun Microsystems for financial support; Ms. MOSIS and all of the staff at MOSIS who each have helped me at one point or another by providing silicon, technical support, and documentation; Bob Brodersen, Roger Howe, Randy Katz, and Ed Lee of UC Berkeley for help while I was visiting UCB; James Plummer of Stanford, for providing me with access to the Terman Engineering Library as a visiting scholar, as well as Abbas El Gamal and Paul Losleben, also at Stanford, for help on several occasions; Don Bouldin at University of Tennessee; Krzysztof Kozminski at MCNC for providing Uncle lay-

<sup>&</sup>lt;sup>1</sup>A code that uniquely identifies a book, the tenth and last digit is a check digit.

$<sup>^{2}</sup>$  This number uniquely identifies a serial (a magazine, a journal, and so on). It is a sevendigit number with an eighth check digit (which may be the roman numeral X, the value ten).

out software; Gershom Kedem at Duke University for the public domain tools his group has written; Sue Drouin, José De Castro, and others at Mentor Graphics Corporation in Oregon for providing documentation and tools; Vahan Kasardjhan, Gail Grego, Michele Warthen, Steve Gardner, and others at the University Program at Cadence Design Systems in San Jose who helped with tools, documentation, and support; Karen Dorrington and the Cadence group in Massachusetts; Andy Haines, Tom Koppin, Sherri Mieth, Velma Miller, Robert Nalesnik, Mike Sarpa, Telle Whitney, and others at Actel for software, hardware, parts, and documentation; Peter Alfke, Leslie Baxter, Brad Fawcett, Chris Kingsley, Karlton Lau, Rick Mitchell, Scott Nance, and Richard Ravel at Xilinx for support, parts, software, and documentation; Greg Hedmann at NorComp for data on FPGAs; Anna Acevedo, Suzanne Bailey, Antje MacNaughton, Richard Terrell, and Altera for providing software, hardware programmers, parts, and documentation; the documentation group and executive management at LSI Logic for tools, libraries, and documentation; Toshiba, NEC, AT&T/NCR, Lucent, and Hitachi (for documentation): NEC for their visiting scholar program at UH; Fred Furtek, Oscar Naval, and Claire Pinkham at Concurrent Logic, Randy Fish at Crosspoint, and Gary Banta at Plus Logic-all for documentation; Paul Titchener and others at Comdisco (now part of Cadence Design Systems) for providing design tools; John Tanner and his staff at Tanner Research for providing their tools and documentation; Mahendra Jain and Nanci Magoun, who let me debug early prototypes at the IDEA conference organized by ASIC Technology and News; Exemplar for providing documentation on its tools; MINC for providing a copy of its FPGA software and documentation; Claudia Traver and Synopsys for tools and documentation; Mentor Graphics Corporation for providing its complete range of software; Alain Hanover and others at ViewLogic for providing tools; Mary Shepherd and Jerry Walker at IEEE for help with permissions; Meta Software for providing HSPICE: Chris Dewhurst and colleagues at Capilano Computing for its design tools; Greg Seltzer (Model Technology) and Charley Rowley for providing V-System Plus with online documentation prototypes; Farallon and Telebit for the software and hardware I used for early experiments with telelectures. Many research students at the University of Hawaii helped me throughout this project including: Chin Huang, Clem Portmann, Christeen Gray, Karlton Lau, Jon Otaguro, Moe Lwin, Troy Stockstad, Ron Jorgenson, Derwin Mattos, William Rivard, Wendy Ching, Anil Aggarwal, Sudhakar Jilla, Linda Xu, Angshuman Saha, Harish Pareek, Claude van Ham, Wen Huang, Kumar Vadhri, Yan Zhong, Yatin Acharya, and Barana Ranaweera. Each of the classes that used early versions of this text at the University of Hawaii at Manoa have also contributed by finding errors. The remaining errors are mine.

Links to figures, software, code, problem solutions, and other resources for this book may be found at:

http://www.awl.com/cp/authors/smithm/asics/asics.html.

Michael John Sebastian Smith Palo Alto and Honolulu, 1997

## CONTENTS

#### **1 INTRODUCTION TO ASICs 1**

#### 1.1 Types of ASICs 4

- 1.1.1 Full-Custom ASICs 5

- 1.1.2 Standard-Cell-Based ASICs 6

- 1.1.3 Gate-Array-Based ASICs 11

- Channeled Gate Array 12 1.1.4

- 1.1.5 Channelless Gate Array 12

- Structured Gate Array 13 1.1.6 Programmable Logic 1.1.7

- Devices 14

- 1.1.8 Field-Programmable Gate Arrays 16

- 1.2 **Design Flow 16**

- 1.3 Case Study 18

- 1.4 Economics of ASICs 20

- 1.4.1 **Comparison Between ASIC Technologies 20**

- 1.4.2 Product Cost 20

- ASIC Fixed Costs 21 1.4.3

- 1.4.4 ASIC Variable Costs 25

- 1.5 **ASIC Cell Libraries 27**

- 1.6 Summary 30

- 1.7 Problems 31

- 1.8 **Bibliography 36**

- **References 38** 1.9

#### 2 CMOS LOGIC 39

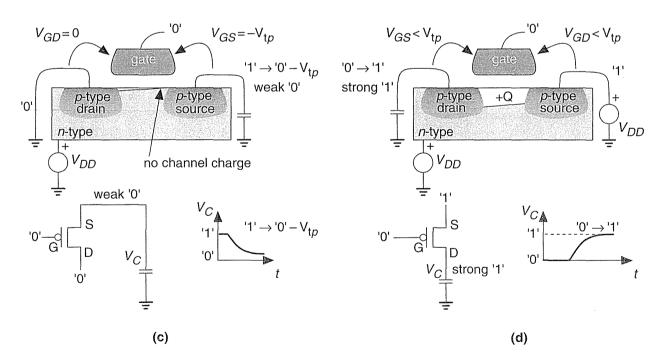

- 2.1 CMOS Transistors 41

- 2.1.1 P-Channel Transistors 45

- Velocity Saturation 45 2.1.2

- 2.1.3SPICE Models 47

- Logic Levels 47 2.1.4

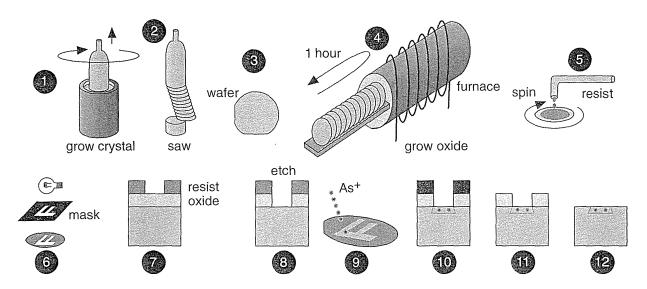

- 2.2 The CMOS Process 49

- 2.2.1 Sheet Resistance 55

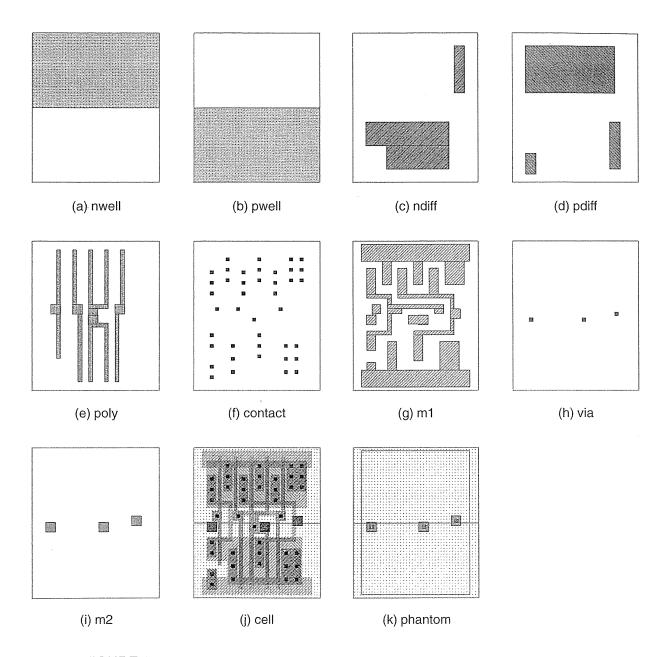

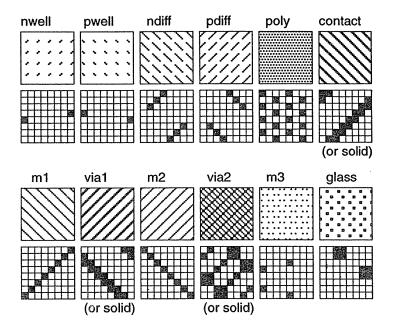

- 2.3 **CMOS** Design Rules 58

- 2.4 Combinational Logic Cells 60

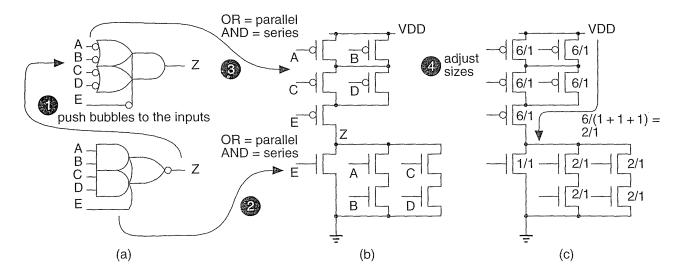

- 2.4.1 Pushing Bubbles 63

- 2.4.2 Drive Strength 65

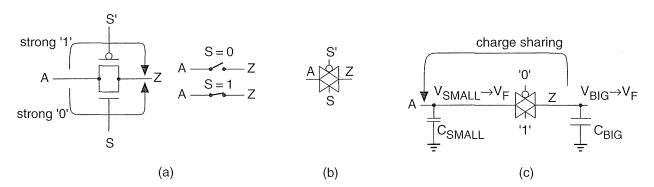

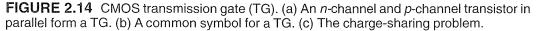

- 2.4.3 **Transmission Gates 66**

- 2.4.4 Exclusive-OR Cell 69

- 2.5Sequential Logic Cells 70

- 2.5.1 Latch 70

- 2.5.2 Flip-Flop 71

- 2.5.3 **Clocked Inverter 73**

- 2.6 Datapath Logic Cells 75

- 2.6.1 Datapath Elements 77

- Adders 79 2.6.2

- A Simple Example 85 2.6.3

- 2.6.4 Multipliers 87

- 2.6.5 Other Arithmetic Systems 94

- Other Datapath Operators 95 2.6.6

- 2.7 I/O Cells 99

- Cell Compilers 102 2.8

- 2.9 Summary 102

- 2.10 Problems 103

- 2.11 Bibliography 113

- References 114 2.12

#### **3 ASIC LIBRARY DESIGN 117**

- Transistors as Resistors 117 3.1

- 3.2 **Transistor Parasitic Capacitance 122**

- 3.2.1 Junction Capacitance 124

- 3.2.2 **Overlap Capacitance 124**

- 3.2.3 Gate Capacitance 124

- 3.2.4 Input Slew Rate 126

- 3.3 Logical Effort 129

- 3.3.1 Predicting Delay 134

- 3.3.2 Logical Area and Logical

- Efficiency 134

- Logical Paths 135 3.3.3

- 3.3.4 Multistage Cells 137

- **Optimum Delav 138** 3.3.5

- 3.3.6 **Optimum Number of Stages 140**

#### viii CONTENTS

- 3.4 Library-Cell Design 141

- 3.5 Library Architecture 142

- 3.6 Gate-Array Design 144

- 3.7 Standard-Cell Design 150

- 3.8 Datapath-Cell Design 152

- 3.9 Summary 155

- 3.10 Problems 155

- 3.11 Bibliography 167

- 3.12 References 168

#### 4 PROGRAMMABLE ASICs 169

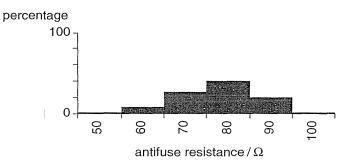

- 4.1 The Antifuse 170 4.1.1 Metal–Metal Antifuse 172

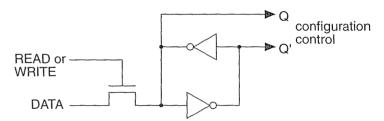

- 4.2 Static RAM 174

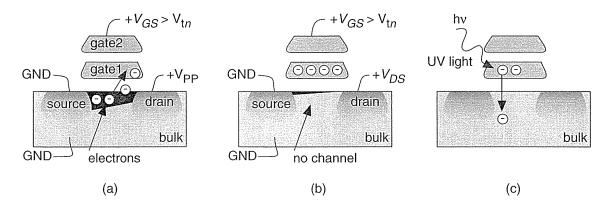

- 4.3 EPROM and EEPROM Technology 174

- 4.4 Practical Issues 176 4.4.1 FPGAs in Use 177

- 4.5 Specifications 178

- 4.6 PREP Benchmarks 179

- 4.7 FPGA Economics 180

4.7.1 FPGA Pricing 180

4.7.2 Pricing Examples 183

- 4.8 Summary 184

- 4.9 Problems 185

- 4.10 Bibliography 190

- 4.11 References 190

#### 5 PROGRAMMABLE ASIC LOGIC CELLS 191

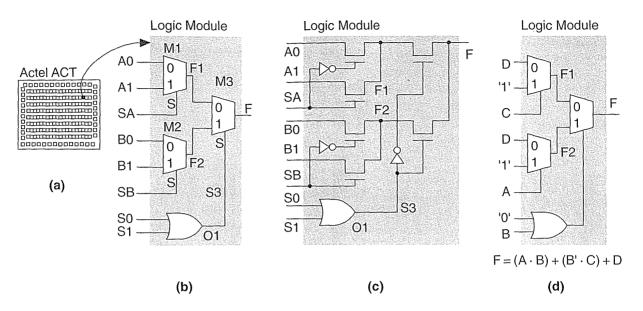

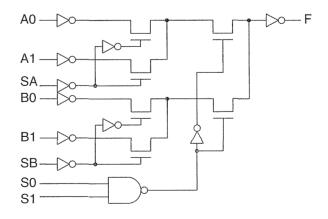

- 5.1 Actel ACT 191

- 5.1.1 ACT 1 Logic Module 191

- 5.1.2 Shannon's Expansion Theorem 192

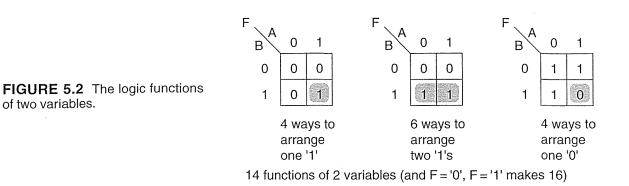

- 5.1.3 Multiplexer Logic as Function Generators 193

- 5.1.4 ACT 2 and ACT 3 Logic Modules 196

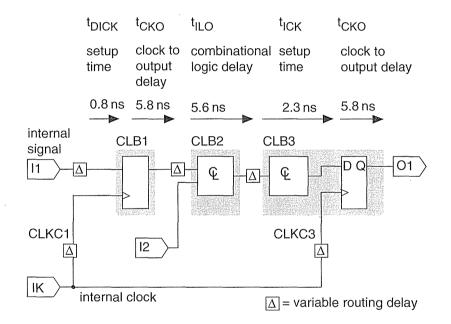

- 5.1.5 Timing Model and Critical Path 197

- 5.1.6 Speed Grading 201

- 5.1.7 Worst-Case Timing 201

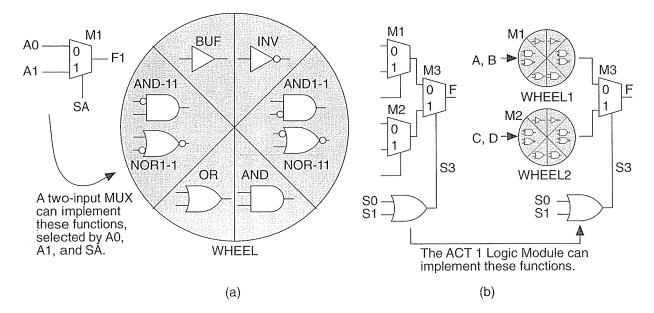

- 5.1.8 Actel Logic Module Analysis 204

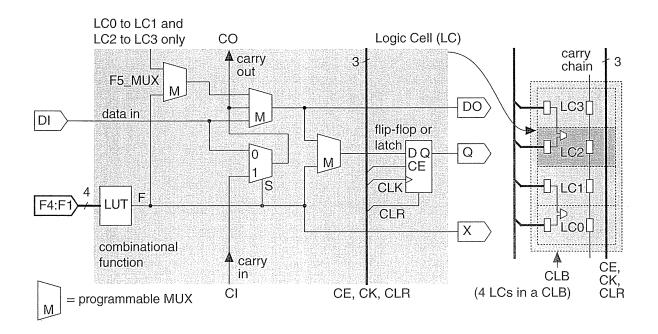

- 5.2 Xilinx LCA 204

- 5.2.1 XC3000 CLB 204

- 5.2.2 XC4000 Logic Block 206

- 5.2.3 XC5200 Logic Block 207

- 5.2.4 Xilinx CLB Analysis 207

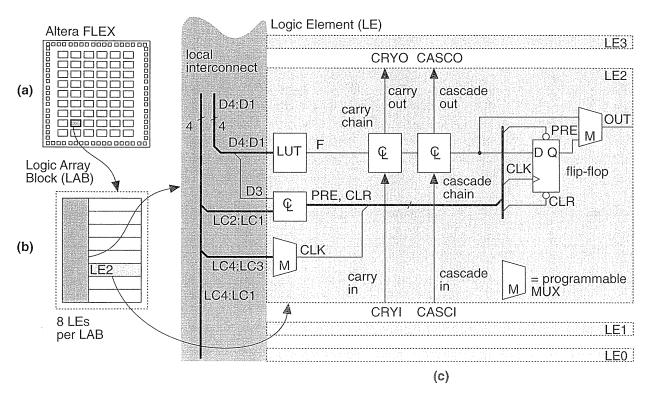

- 5.3 Altera FLEX 209

- 5.4 Altera MAX 209

- 5.4.1 Logic Expanders 211

- 5.4.2 Timing Model 215

- 5.4.3 Power Dissipation in Complex PLDs 217

- 5.5 Summary 218

- 5.6 Problems 224

- 5.7 Bibliography 229

- 5.8 References 230

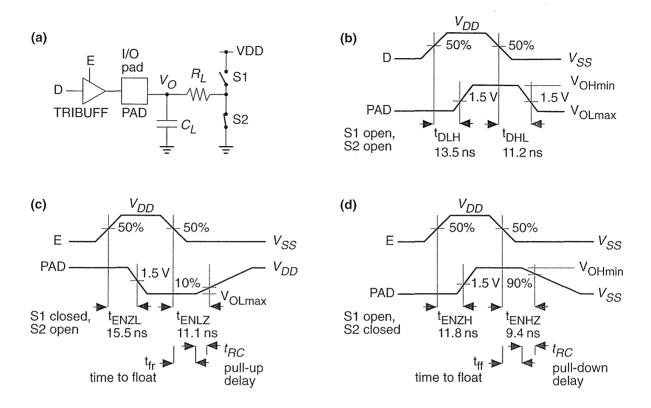

#### 6 PROGRAMMABLE ASIC I/O CELLS 231

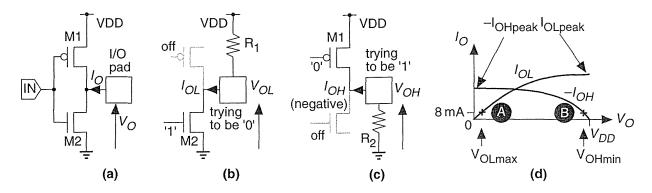

- 6.1 DC Output 232

- 6.1.1 Totem-Pole Output 234

- 6.1.2 Clamp Diodes 235

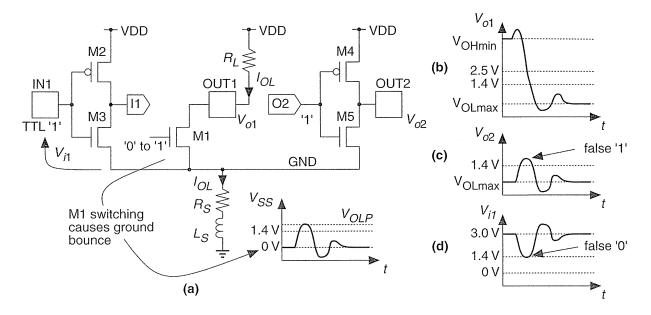

- 6.2 AC Output 235

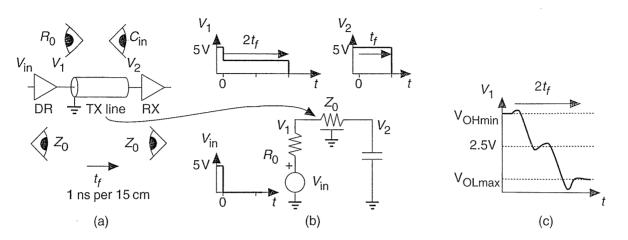

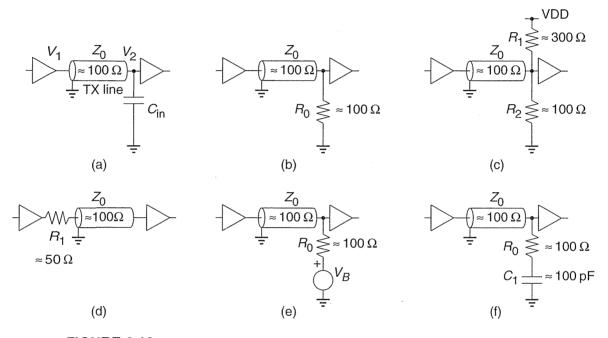

- 6.2.1 Supply Bounce 239

- 6.2.2 Transmission Lines 240

- 6.3 DC Input 243

- 6.3.1 Noise Margins 244

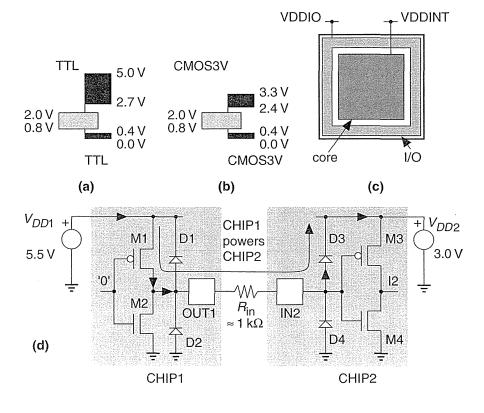

- 6.3.2 Mixed-Voltage Systems 246

- 6.4 AC Input 248

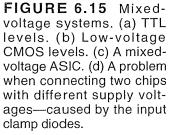

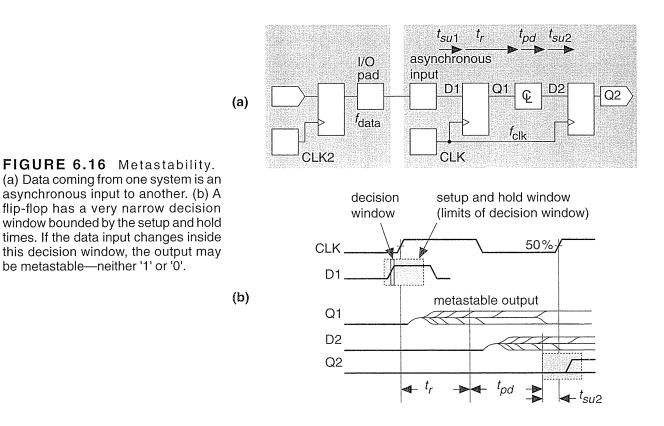

- 6.4.1 Metastability 249

- 6.5 Clock Input 253

- 6.5.1 Registered Inputs 253

- 6.6 Power Input 255

- 6.6.1 Power Dissipation 256

- 6.6.2 Power-On Reset 258

- 6.7 Xilinx I/O Block 258

- 6.7.1 Boundary Scan 260

- 6.8 Other I/O Cells 261

- 6.9 Summary 262

- 6.10 Problems 263

- 6.11 Bibliography 272

- 6.12 References 273

#### 7 PROGRAMMABLE ASIC INTERCONNECT 275

- 7.1 Actel ACT 275

- 7.1.1 Routing Resources 276

- 7.1.2 Elmore's Constant 278

CONTENTS ix

- 7.1.3 RC Delay in Antifuse Connections 280

- 7.1.4 Antifuse Parasitic Capacitance 281

- 7.1.5 ACT 2 and ACT 3 Interconnect 283

- 7.2 Xilinx LCA 284

- 7.3 Xilinx EPLD 288

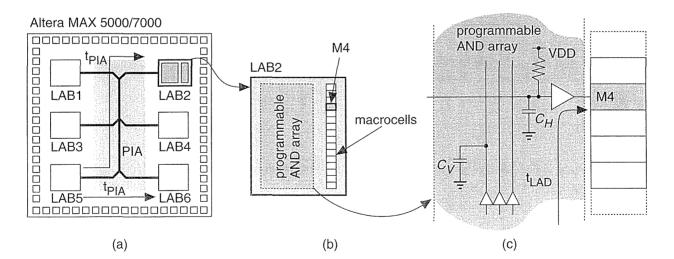

- 7.4 Altera MAX 5000 and 7000 289

- 7.5 Altera MAX 9000 290

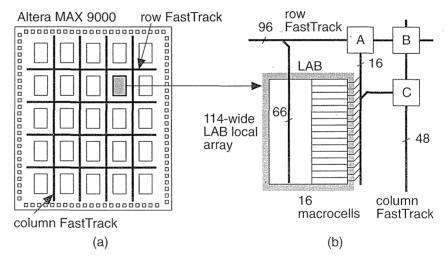

- 7.6 Altera FLEX 291

- 7.7 Summary 292

- 7.8 Problems 294

- 7.9 Bibliography 297

- 7.10 References 297

#### 8 PROGRAMMABLE ASIC DESIGN SOFTWARE 299

- 8.1 Design Systems 299

- 8.1.1 Xilinx 301

- 8.1.2 Actel 303

- 8.1.3 Altera 303

- 8.2 Logic Synthesis 304

- 8.2.1 FPGA Synthesis 305

- 8.3 The Halfgate ASIC 307

- 8.3.1 Xilinx 307

- 8.3.2 Actel 310

- 8.3.3 Altera 310

- 8.3.4 Comparison 315

- 8.4 Summary 316

- 8.5 Problems 316

- 8.6 Bibliography 320

- 8.6.1 FPGA Vendors 321

- 8.6.2 Third-Party Software 323

- 8.7 References 326

#### 9 LOW-LEVEL DESIGN ENTRY 327

- 9.1 Schematic Entry 328

- 9.1.1 Hierarchical Design 330

- 9.1.2 The Cell Library 330

- 9.1.3 Names 332

- 9.1.4 Schematic lcons and Symbols 333

- 9.1.5 Nets 336

- 9.1.6 Schematic Entry for ASICs and

- PCBs 336

- 9.1.7 Connections 338

- 9.1.8 Vectored Instances and

- Buses 338

- 9.1.9 Edit-in-Place 340

- 9.1.10 Attributes 341

- 9.1.11 Netlist Screener 341

- 9.1.12 Schematic-Entry tools 343

- 9.1.13 Back-Annotation 345

- 9.2 Low-Level Design Languages 345

- 9.2.1 ABEL 346

- 9.2.2 CUPL 348

- 9.2.3 PALASM 350

- 9.3 PLA Tools 353

- 9.4 EDIF 355

- 9.4.1 EDIF Syntax 355

- 9.4.2 An EDIF Netlist Example 357

- 9.4.3 An EDIF Schematic Icon 359

- 9.4.4 An EDIF Example 365

- 9.5 CFI Design Representation 369

- 9.5.1 CFI Connectivity Model 370

- 9.6 Summary 373

- 9.7 Problems 373

- 9.8 Bibliography 376

- 9.9 References 377

#### 10 VHDL 379

- 10.1 A Counter 380

- 10.2 A 4-bit Multiplier 381

- 10.2.1 An 8-bit Adder 381

- 10.2.2 A Register Accumulator 381

- 10.2.3 Zero Detector 383

- 10.2.4 A Shift Register 384

- 10.2.5 A State Machine 384

- 10.2.6 A Multiplier 385

- 10.2.7 Packages and Testbench 388

- 10.3 Syntax and Semantics of VHDL 390

- 10.4 Identifiers and Literals 392

- 10.5 Entities and Architectures 393

- 10.6 Packages and Libraries 398

- 10.6.1 Standard Package 399

- 10.6.2 Std\_logic\_1164 Package 400

- 10.6.3 Textio Package 402

- 10.6.4 Other Packages 403

- 10.6.5 Creating Packages 404

#### X CONTENTS

- 10.7 Interface Declarations 405 10.7.1 Port Declaration 406 10.7.2 Generics 410 10.8 Type Declarations 411 Other Declarations 413 10.9 10.9.1 **Object Declarations 414** 10.9.2 Subprogram Declarations 415 Alias and Attribute 10.9.3 **Declarations 418** 10.9.4 Predefined Attributes 419 Sequential Statements 419 10.10 10.10.1 Wait Statement 421 Assertion and Report State-10.10.2 ments 423 Assignment Statements 424 10.10.3 Procedure Call 426 10.10.4 10.10.5 If Statement 427 10.10.6 Case Statement 428 10.10.7 Other Sequential Control Statements 429 10.11 **Operators 430** 10.12 Arithmetic 432 10.12.1 IEEE Synthesis Packages 434 10.13 **Concurrent Statements 437** 10.13.1 Block Statement 438 10.13.2 Process Statement 440 Concurrent Procedure Call 441 10.13.3 **Concurrent Signal** 10.13.4 Assianment 442 10.13.5 Concurrent Assertion Statement 443 **Component Instantiation 444** 10.13.6 10.13.7 Generate Statement 444 Execution 445 10.14 10.15 Configurations and Specifications 447 10.16 An Engine Controller 449 10.17 Summary 456

- 10.18 Problems 459

- 10.19 Bibliography 477

- 10.20 References 478

#### 11 VERILOG HDL 479

- 11.1 A Counter 480

- 11.2 Basics of the Verilog Language 482

- 11.2.1 Verilog Logic Values 483

- 11.2.2 Verilog Data Types 483

- 11.2.3 Other Wire Types 486

- 11.2.4 Numbers 486

- 11.2.5 Negative Numbers 488

- 11.2.6 Strings 489

- 11.3 Operators 490

- 11.3.1 Arithmetic 492

- 11.4 Hierarchy 494

- 11.5 Procedures and Assignments 495

- 11.5.1 Continuous Assignment Statement 496

- 11.5.2 Sequential Block 497

- 11.5.3 Procedural Assignments 498

- 11.6 Timing Controls and Delay 498

- 11.6.1 Timing Control 498

- 11.6.2 Data Slip 501

- 11.6.3 Wait Statement 502

- 11.6.4 Blocking and Nonblocking Assignments 503

- 11.6.5 Procedural Continuous Assignment 504

- 11.7 Tasks and Functions 506

- 11.8 Control Statements 506

- 11.8.1 Case and If Statement 506

- 11.8.2 Loop Statement 507

- 11.8.3 Disable 508

- 11.8.4 Fork and Join 509

- 11.9 Logic-Gate Modeling 509

- 11.9.1 Built-in Logic Models 509

- 11.9.2 User-Defined Primitives 510

- 11.10 Modeling Delay 512

- 11.10.1 Net and Gate Delay 512

- 11.10.2 Pin-to-Pin Delay 513

- 11.11 Altering Parameters 515

- 11.12 A Viterbi Decoder 515

- 11.12.1 Viterbi Encoder 515

- 11.12.2 The Received Signal 519

- 11.12.3 Testing the System 521

- 11.12.4 Verilog Decoder Model 523

- 11.13 Other Verilog Features 532

- 11.13.1 Display Tasks 533

- 11.13.2 File I/O Tasks 533

- 11.13.3 Timescale, Simulation, and Timing-Check Tasks 534

- 11.13.4 PLA Tasks 537

- 11.13.5 Stochastic Analysis Tasks 538

- 11.13.6 Simulation Time Functions 539

- 11.13.7 Conversion Functions 539

- 11.13.8 Probability Distribution Functions 540

#### CONTENTS xi

| 11.13.9 | Programming Language |

|---------|----------------------|

|         | Interface 541        |

| _       |                      |

- 11.14 Summary 541

- 11.15 Problems 543

- 11.15.1 The Viterbi Decoder 556

- 11.16 Bibliography 557

- 11.17 References 557

#### 12 LOGIC SYNTHESIS 559

- 12.1 A Logic-Synthesis Example 560

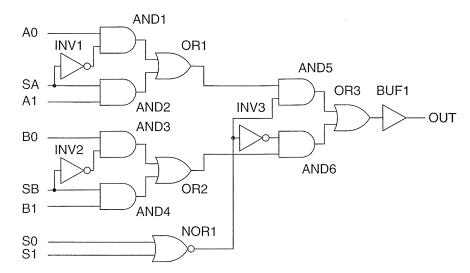

- 12.2 A Comparator/MUX 561 12.2.1 An Actel Version of the

- Comparator/MUX 567

- 12.3 Inside a Logic Synthesizer 569

- 12.4 Synthesis of the Viterbi Decoder 572

- 12.4.1 ASIC I/O 572

- 12.4.2 Flip-Flops 575

- 12.4.3 The Top-Level Model 575 12.5 Verilog and Logic Synthesis 580

- Verilog and Logic Synthesis 580 12.5.1 Verilog Modeling 580

- 12.5.2 Delays in Verilog 581

- 12.5.3 Blocking and Nonblocking

- Assignments 582 12.5.4 Combinational Logic in Verilog 582

- 12.5.5 Multiplexers In Verilog 584

- 12.5.6 The Verilog Case Statement 585

- 12.5.7 Decoders In Verilog 586

- 12.5.8 Priority Encoder in Verilog 587

- 12.5.9 Arithmetic in Verilog 587

- 12.5.10 Sequential Logic in Verilog 589

- 12.5.11 Component Instantiation in Verilog 590

- 12.5.12 Datapath Synthesis in Verilog 591

- 12.6 VHDL and Logic Synthesis 593

- 12.6.1 Initialization and Reset 593

- 12.6.2 Combinational Logic Synthesis in VHDL 594

- 12.6.3 Multiplexers in VHDL 594

- 12.6.4 Decoders in VHDL 595

- 12.6.5 Adders in VHDL 597

- 12.6.6 Sequential Logic in VHDL 597

- 12.6.7 Instantiation in VHDL 598

- 12.6.8 Shift Registers and Clocking in VHDL 601

- 12.6.9 Adders and Arithmetic

- Functions 603

- 12.6.10 Adder/Subtracter and Don't Cares 604

- 12.7 Finite-State Machine Synthesis 605 12.7.1 FSM Synthesis in Verilog 607 12.7.2 FSM Synthesis in VHDL 608

- Memory Synthesis 611

- 12.8 Memory Synthesis 611 12.8.1 Memory Synthesis in Verilog 611

- 12.8.2 Memory Synthesis in VHDL 612

- 12.9 The Multiplier 614 12.9.1 Messages During Synthesis 617

- 12.10 The Engine Controller 619

- 12.11 Performance-Driven Synthesis 620

- 12.12 Optimization of the Viterbi Decoder 625

- 12.13 Summary 628

- 12.14 Problems 629

- 12.15 Bibliography 638

- 12.16 References 639

#### 13 SIMULATION 641

- 13.1 Types of Simulation 641

- 13.2 The Comparator/MUX Example 643

- 13.2.1 Structural Simulation 644

- 13.2.2 Static Timing Analysis 647

- 13.2.3 Gate-Level Simulation 648

- 13.2.4 Net Capacitance 650

- 13.3 Logic Systems 652

- 13.3.1 Signal Resolution 653 13.3.2 Logic Strength 653

- 13.4 How Logic Simulation Works 656

- 13.4.1 VHDL Simulation Cycle 658 13.4.2 Delay 658

- 13.5 Cell Models 659

- 13.5.1 Primitive Models 659

- 13.5.2 Synopsys Models 660

- 13.5.3 Verilog Models 661

- 13.5.4 VHDL Models 663

- 13.5.5 VITAL Models 664

- 13.5.6 SDF in Simulation 667

- 13.6 Delay Models 669

- 13.6.1 Using a Library Data Book 670

- 13.6.2 Input-Slope Delay Model 672

- 13.6.3 Limitations of Logic Simulation 674

xii CONTENTS

| 13.7                        | Static Timing Analysis 675      |                         |  |

|-----------------------------|---------------------------------|-------------------------|--|

|                             | 13.7.1                          | Hold Time 678           |  |

|                             | 13.7.2                          | Entry Delay 679         |  |

|                             | 13.7.3                          | Exit Delay 680          |  |

|                             | 13.7.4                          | External Setup Time 681 |  |

| 13.8 Formal Verification 68 |                                 | Verification 682        |  |

|                             | 13.8.1                          | An Example 682          |  |

|                             | 13.8.2                          | Understanding Formal    |  |

|                             |                                 | Verification 684        |  |

|                             | 13.8.3                          | Adding an Assertion 685 |  |

|                             | 13.8.4                          | Completing a Proof 687  |  |

| 13.9                        | Switch-Level Simulation 688     |                         |  |

| 13.10                       | Transistor-Level Simulation 689 |                         |  |

|                             |                                 |                         |  |

- 13.10.1 A PSpice Example 689 13.10.2 SPICE Models 692

- 13.11 Summary 696

- 13.12 Problems 696

- 13.13 Bibliography 708

- 13.14 References 708

#### 14 TEST 711

- 14.1 The Importance of Test 712

- 14.2 Boundary-Scan Test 714

- 14.2.1 BST Cells 716

- 14.2.2 **BST Registers 718**

- 14.2.3 Instruction Decoder 719

- **TAP Controller 722**

- 14.2.5 Boundary-Scan Controller 724

- A Simple Boundary-Scan 14.2.6 Example 727

- 14.2.7 **BSDL 732**

- Faults 736 14.3

- Reliability 736 14.3.1

- 14.3.2 Fault Models 737

- 14.3.3 Physical Faults 738

- Stuck-at Fault Model 740 14.3.4

- 14.3.5 Logical Faults 741

- IDDQ Test 742 14.3.6

- 14.3.7 Fault Collapsing 743

- 14.3.8 Fault-Collapsing Example 743

#### Fault Simulation 745 14.4

- Serial Fault Simulation 747 14.4.1

- Parallel Fault Simulation 747 14.4.2

- 14.4.3 Concurrent Fault Simulation 747

- 14.4.4 Nondeterministic Fault Simulation 748

- 14.4.5 Fault-Simulation Results 748

- 14.4.6 Fault-Simulator Logic Systems 749

- 14.4.7 Hardware Acceleration 751

- 14.4.8 A Fault-Simulation Example 752

- 14.4.9 Fault Simulation in an ASIC **Desian Flow 754**

- 14.5 Automatic Test-Pattern Generation 755

- 14.5.1 The D-Calculus 755

- 14.5.2 A Basic ATPG Algorithm 757

- 14.5.3 The PODEM Algorithm 759

- Controllability and 14.5.4

- **Observability** 761 Scan Test 764

- 14.6 14.7 Built-in Self-test 766

- 14.7.1 **LFSR 766**

- 14.7.2 Signature Analysis 766

- 14.7.3 A Simple BIST Example 767

- 14.7.4 Aliasing 768

- LFSR Theory 771 14.7.5

- 14.7.6 LFSR Example 773

- 14.7.7 **MISR 775**

- 14.8 A Simple Test Example 778

- **Test-Logic Insertion 778** 14.8.1 14.8.2 How the Test Software

- Works 780 14.8.3

- ATVG and Fault Simulation 787

- 14.8.4 **Test Vectors 787**

- 14.8.5 Production Tester Vector Formats 789

- 14.8.6 Test Flow 791

- 14.9 The Viterbi Decoder Example 791

- Summary 794 14.10

- Problems 794 14.11

- **Bibliography 800** 14.12

- 14.13 References 801

#### **15 ASIC CONSTRUCTION 805**

- 15.1 Physical Design 805

- 15.2 CAD Tools 807

- 15.2.1 Methods and Algorithms 808

- System Partitioning 809 15.3

- Estimating ASIC Size 811 15.4

- 15.5 Power Dissipation 816

- 15.5.1 Switching Current 816

- 15.5.2 Short-Circuit Current 817

14.2.4

#### CONTENTS xiii

- 15.5.3 Subthreshold and Leakage Current 818

- 15.6 FPGA Partitioning 820

- 15.6.1 ATM Simulator 820

- 15.6.2 Automatic Partitioning with FPGAs 823

- 15.7 Partitioning Methods 824

- 15.7.1 Measuring Connectivity 824

- 15.7.2 A Simple Partitioning Example 826

- 15.7.3 Constructive Partitioning 827

- 15.7.4 Iterative Partitioning Improvement 828

- 15.7.5 The Kernighan–Lin Algorithm 829

- 15.7.6 The Ratio-Cut Algorithm 834

- 15.7.7 The Look-ahead Algorithm 835

- 15.7.8 Simulated Annealing 836

- 15.7.9 Other Partitioning Objectives 837

- 15.8 Summary 838

- 15.9 Problems 838

- 15.10 Bibliography 850

- 15.11 References 851

#### 16 FLOORPLANNING AND PLACEMENT 853

- 16.1 Floorplanning 853

- 16.1.1 Floorplanning Goals and Objectives 854

- 16.1.2 Measurement of Delay in Floorplanning 856

- 16.1.3 Floorplanning Tools 859

- 16.1.4 Channel Definition 861

- 16.1.5 I/O and Power Planning 864

- 16.1.6 Clock Planning 869

- 16.2 Placement 873

- 16.2.1 Placement Terms and Definitions 873

- 16.2.2 Placement Goals and Objectives 876

- 16.2.3 Measurement of Placement Goals and Objectives 877

- 16.2.4 Placement Algorithms 882

- 16.2.5 Eigenvalue Placement Example 885

- 16.2.6 Iterative Placement Improvement 887

- 16.2.7 Placement Using Simulated

- Annealing 890

- 16.2.8 Timing-Driven Placement Methods 891

- 16:2.9 A Simple Placement Example 893

- 16.3 Physical Design Flow 894

- 16.4 Information Formats 895

- 16.4.1 SDF for Floorplanning and Placement 895

- 16.4.2 PDEF 896

- 16.4.3 LEF and DEF 897

- 16.5 Summary 898

- 16.6 Problems 898

- 16.7 Bibliography 906

- 16.8 References 906

#### 17 ROUTING 909

- 17.1 Global Routing 910

- 17.1.1 Goals and Objectives 911

- 17.1.2 Measurement of Interconnect Delay 912

- 17.1.3 Global Routing Methods 915

- 17.1.4 Global Routing Between Blocks 916

- 17.1.5 Global Routing Inside Flexible Blocks 918

- 17.1.6 Timing-Driven Methods 920

- 17.1.7 Back-annotation 921

- 17.2 Detailed Routing 922

- 17.2.1 Goals and Objectives 926

- 17.2.2 Measurement of Channel Density 927

- 17.2.3 Algorithms 928

- 17.2.4 Left-Edge Algorithm 928

- 17.2.5 Constraints and Routing Graphs 928

- 17.2.6 Area-Routing Algorithms 931

- 17.2.7 Multilevel Routing 933

- 17.2.8 Timing-Driven Detailed Routing 933

- 17.2.9 Final Routing Steps 934

- 17.3 Special Routing 935

- 17.3.1 Clock Routing 935

- 17.3.2 Power Routing 936

- 17.4 Circuit Extraction and DRC 939

- 17.4.1 SPF, RSPF, and DSPF 939

- 17.4.2 Design Checks 944

- 17.4.3 Mask Preparation 945

#### xiv CONTENTS

- 17.5 Summary 946

- 17.6 Problems 947

- 17.7 Bibliography 956

- 17.8 References 957

#### A VHDL RESOURCES 961

- A.1 BNF 961

- A.2 VHDL Syntax 963

- A.3 BNF Index 973

- A.4 Bibliography 973

- A.5 References 976

#### B VERILOG HDL RESOURCES 979

- B.1 Explanation of the Verilog HDL BNF 979

- B.2 Verilog HDL Syntax 980

- B.3 BNF Index 994

- B.4 Verilog HDL LRM 994

- B.5 Bibliography 997

- B.6 References 999

#### **GLOSSARY 1000**

#### **INDEX 1006**

## INTRODUCTION TO ASICs

| 1.1 | Types of ASICs     | 1.6 | Summary      |

|-----|--------------------|-----|--------------|

| 1.2 | Design Flow        | 1.7 | Problems     |

| 1.3 | Case Study         | 1.8 | Bibliography |

| 1.4 | Economics of ASICs | 1.9 | References   |

1.5 ASIC Cell Libraries

An ASIC (pronounced "a-sick"; bold typeface defines a new term) is an **application-specific integrated circuit**—at least that is what the acronym stands for. Before we answer the question of what *that* means we first look at the evolution of the silicon chip or **integrated circuit** (IC).

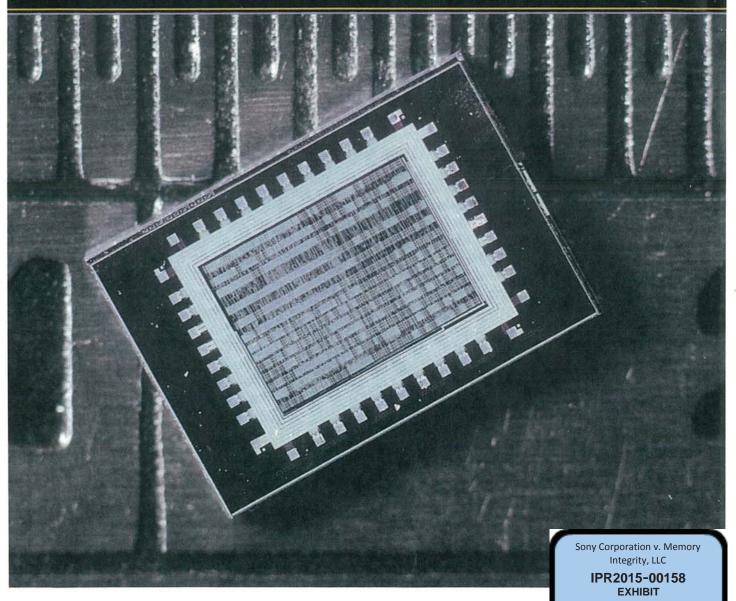

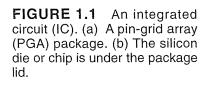

Figure 1.1(a) shows an IC package (this is a pin-grid array, or PGA, shown upside down; the pins will go through holes in a printed-circuit board). People often call the package a chip, but, as you can see in Figure 1.1(b), the silicon chip itself (more properly called a **die**) is mounted in the cavity under the sealed lid. A PGA package is usually made from a ceramic material, but plastic packages are also common.

1

The physical size of a silicon die varies from a few millimeters on a side to over 1 inch on a side, but instead we often measure the size of an IC by the number of logic gates or the number of transistors that the IC contains. As a unit of measure a **gate equivalent** corresponds to a two-input NAND gate (a circuit that performs the logic function,  $F = \overline{A \cdot B}$ ). Often we just use the term *gates* instead of gate equivalents when we are measuring chip size—not to be confused with the gate terminal of a transistor. For example, a 100 k-gate IC contains the equivalent of 100,000 two-input NAND gates.

The semiconductor industry has evolved from the first ICs of the early 1970s and matured rapidly since then. Early **small-scale integration** (**SSI**) ICs contained a few (1 to 10) logic gates—NAND gates, NOR gates, and so on—amounting to a few tens of transistors. The era of **medium-scale integration** (**MSI**) increased the range of integrated logic available to counters and similar, larger scale, logic functions. The era of **large-scale integration** (**LSI**) packed even larger logic functions, such as the first microprocessors, into a single chip. The era of **very large-scale integration** (**VLSI**) now offers 64-bit microprocessors, complete with cache memory and floating-point arithmetic units—well over a million transistors—on a single piece of silicon. As CMOS process technology improves, transistors continue to get smaller and ICs hold more and more transistors. Some people (especially in Japan) use the term **ultralarge scale integration** (**ULSI**), but most people stop at the term VLSI; otherwise we have to start inventing new words.

The earliest ICs used **bipolar technology** and the majority of logic ICs used either **transistor-transistor logic** (**TTL**) or emitter-coupled logic (ECL). Although invented before the bipolar transistor, the **metal-oxide-silicon** (**MOS**) transistor was initially difficult to manufacture because of problems with the oxide interface. As these problems were gradually solved, metal-gate *n*-channel MOS (**nMOS** or **NMOS**) technology developed in the 1970s. At that time MOS technology required fewer masking steps, was denser, and consumed less power than equivalent bipolar ICs. This meant that, for a given performance, an MOS IC was cheaper than a bipolar IC and led to investment and growth of the MOS IC market.

By the early 1980s the aluminum gates of the transistors were replaced by polysilicon gates, but the name MOS remained. The introduction of polysilicon as a gate material was a major improvement in CMOS technology, making it easier to make two types of transistors, *n*-channel MOS and *p*-channel MOS transistors, on the same IC—a **complementary MOS** (CMOS, never cMOS) technology. The principal advantage of CMOS over NMOS is lower power consumption. Another advantage of a polysilicon gate was a simplification of the fabrication process, allowing devices to be scaled down in size.

There are four CMOS transistors in a two-input NAND gate (and a two-input NOR gate too), so to convert between gates and transistors, you multiply the number of gates by 4 to obtain the number of transistors. We can also measure an IC process by the smallest resolvable **feature size** (roughly half the length of the smallest transistor) imprinted on the IC. Transistor dimensions are measured in microns (a

micron, 1  $\mu$ m, is a millionth of a meter). Thus we talk about a 0.2  $\mu$ m IC or say an IC is built in (or with) a 0.2  $\mu$ m process, meaning that the smallest transistors are approximtely 0.2  $\mu$ m in length. We give a special label,  $\lambda$  or **lambda**, to this smallest resolvable feature size. Since lambda is roughly equal to half of the smallest transistor length,  $\lambda \approx 0.1 \,\mu$ m in a 0.2  $\mu$ m process. Many of the drawings in this book use a scale marked with lambda for the same reason we place a scale on a map.

A modern submicron CMOS process is now just as complicated as a submicron bipolar or BiCMOS (a combination of bipolar and CMOS) process. However, CMOS ICs have established a dominant position, are manufactured in much greater volume than any other technology, and therefore, because of the economy of scale, the cost of CMOS ICs is less than a bipolar or BiCMOS IC for the same function. Bipolar and BiCMOS ICs are still used for special needs. For example, bipolar technology is generally capable of handling higher voltages than CMOS. This makes bipolar and BiCMOS ICs useful in power electronics, cars, telephone circuits, and so on.

Some digital logic ICs and their analog counterparts (analog/digital converters, for example) are **standard parts**, or standard ICs. You can select standard ICs from catalogs and data books and buy them from distributors. Systems manufacturers and designers can use the same standard part in a variety of different **microelectronic systems** (systems that use microelectronics or ICs).

With the advent of VLSI in the 1980s engineers began to realize the advantages of designing an IC that was customized or tailored to a particular system or application rather than using standard ICs alone. Microelectronic system design then becomes a matter of defining the functions that you can implement using standard ICs and then implementing the remaining logic functions (sometimes called **glue logic**) with one or more **custom ICs**. As VLSI became possible you could build a system from a smaller number of components by combining many standard ICs into a few custom ICs. Building a microelectronic system with fewer ICs allows you to reduce cost and improve reliability.

Of course, there are many situations in which it is not appropriate to use a custom IC for each and every part of an microelectronic system. If you need a large amount of memory, for example, it is still best to use standard memory ICs, either **dynamic random-access memory (DRAM** or dRAM), or **static RAM (SRAM** or sRAM), in conjunction with custom ICs.

One of the first conferences to be devoted to this rapidly emerging segment of the IC industry was the *IEEE Custom Integrated Circuits Conference* (CICC), and the proceedings of this annual conference form a useful reference to the development of custom ICs. As different types of custom ICs began to evolve for different types of applications, these new ICs gave rise to a new term: application-specific IC, or ASIC. Now we have the *IEEE International ASIC Conference*, which tracks advances in ASICs separately from other types of custom ICs. Although the exact definition of an ASIC is difficult, we shall look at some examples to help clarify what people in the IC industry understand by the term.

Examples of ICs that are *not* ASICs include standard parts such as: memory chips sold as a commodity item—ROMs, DRAM, and SRAM; microprocessors; TTL or TTL-equivalent ICs at SSI, MSI, and LSI levels.

Examples of ICs that *are* ASICs include: a chip for a toy bear that talks; a chip for a satellite; a chip designed to handle the interface between memory and a micro-processor for a workstation CPU; and a chip containing a microprocessor as a cell together with other logic.

As a general rule, if you can find it in a data book, then it is probably not an ASIC, but there are some exceptions. For example, two ICs that might or might not be considered ASICs are a controller chip for a PC and a chip for a modem. Both of these examples are specific to an application (shades of an ASIC) but are sold to many different system vendors (shades of a standard part). ASICs such as these are sometimes called **application-specific standard products (ASSPs)**.

Trying to decide which members of the huge IC family are application-specific is tricky—after all, every IC has an application. For example, people do not usually consider an application-specific microprocessor to be an ASIC. I shall describe how to design an ASIC that may include large cells such as microprocessors, but I shall not describe the design of the microprocessors themselves. Defining an ASIC by looking at the application can be confusing, so we shall look at a different way to categorize the IC family. The easiest way to recognize people is by their faces and physical characteristics: tall, short, thin. The easiest characteristics of ASICs to understand are physical ones too, and we shall look at these next. It is important to understand these differences because they affect such factors as the price of an ASIC and the way you design an ASIC.

#### **1.1** Types of ASICs

ICs are made on a thin (a few hundred microns thick), circular silicon **wafer**, with each wafer holding hundreds of die (sometimes people use dies or dice for the plural of die). The transistors and wiring are made from many layers (usually between 10 and 15 distinct layers) built on top of one another. Each successive **mask layer** has a pattern that is defined using a **mask** similar to a glass photographic slide. The first half-dozen or so layers define the transistors. The last half-dozen or so layers define the transistors (the **interconnect**).

A **full-custom IC** includes some (possibly all) logic cells that are customized and all mask layers that are customized. A microprocessor is an example of a fullcustom IC—designers spend many hours squeezing the most out of every last square micron of microprocessor chip space by hand. Customizing all of the IC features in this way allows designers to include analog circuits, optimized memory cells, or mechanical structures on an IC, for example. Full-custom ICs are the most expensive to manufacture and to design. The **manufacturing lead time** (the time it takes just to make an IC—not including design time) is typically eight weeks for a full-custom IC. These specialized full-custom ICs are often intended for a specific application, so we might call some of them full-custom ASICs.

We shall discuss full-custom ASICs briefly next, but the members of the IC family that we are more interested in are **semicustom ASICs**, for which all of the logic cells are predesigned and some (possibly all) of the mask layers are customized. Using predesigned cells from a **cell library** makes our lives as designers much, much easier. There are two types of semicustom ASICs that we shall cover: standard-cell-based ASICs and gate-array-based ASICs. Following this we shall describe the **programmable ASICs**, for which all of the logic cells are predesigned and none of the mask layers are customized. There are two types of programmable ASICs: the programmable logic device and, the newest member of the ASIC family, the field-programmable gate array.

#### 1.1.1 Full-Custom ASICs

In a **full-custom ASIC** an engineer designs some or all of the logic cells, circuits, or layout specifically for one ASIC. This means the designer abandons the approach of using pretested and precharacterized cells for all or part of that design. It makes sense to take this approach only if there are no suitable existing cell libraries available that can be used for the entire design. This might be because existing cell libraries are not fast enough, or the logic cells are not small enough or consume too much power. You may need to use full-custom design if the ASIC technology is new or so specialized that there are no existing cell libraries or because the ASIC is so specialized that some circuits must be custom designed. Fewer and fewer full-custom ICs are being designed because of the problems with these special parts of the ASIC. There is one growing member of this family, though, the mixed analog/digital ASIC, which we shall discuss next.

Bipolar technology has historically been used for precision analog functions. There are some fundamental reasons for this. In all integrated circuits the matching of component characteristics between chips is very poor, while the matching of characteristics between components on the same chip is excellent. Suppose we have transistors T1, T2, and T3 on an analog/digital ASIC. The three transistors are all the same size and are constructed in an identical fashion. Transistors T1 and T2 are located adjacent to each other and have the same orientation. Transistor T3 is the same size as T1 and T2 but is located on the other side of the chip from T1 and T2 and has a different orientation. ICs are made in batches called wafer lots. A wafer lot is a group of silicon wafers that are all processed together. Usually there are between 5 and 30 wafers in a lot. Each wafer can contain tens or hundreds of chips depending on the size of the IC and the wafer.

6

If we were to make measurements of the characteristics of transistors T1, T2, and T3 we would find the following:

- Transistors T1 will have virtually identical characteristics to T2 on the same IC. We say that the transistors **match** well or the **tracking** between devices is excellent.

- Transistor T3 will match transistors T1 and T2 on the same IC very well, but not as closely as T1 matches T2 on the same IC.

- Transistor T1, T2, and T3 will match fairly well with transistors T1, T2, and T3 on a different IC on the same wafer. The matching will depend on how far apart the two ICs are on the wafer.

- Transistors on ICs from different wafers in the same wafer lot will not match very well.

- Transistors on ICs from different wafer lots will match very poorly.

For many analog designs the close matching of transistors is crucial to circuit operation. For these circuit designs pairs of transistors are used, located adjacent to each other. Device physics dictates that a pair of bipolar transistors will always match more precisely than CMOS transistors of a comparable size. Bipolar technology has historically been more widely used for full-custom analog design because of its improved precision. Despite its poorer analog properties, the use of CMOS technology for analog functions is increasing. There are two reasons for this. The first reason is that CMOS is now by far the most widely available IC technology. Many more CMOS ASICs and CMOS standard products are now being manufactured than bipolar ICs. The second reason is that increased levels of integration require mixing analog and digital functions on the same IC: this has forced designers to find ways to use CMOS technology to implement analog functions. Circuit designers, using clever new techniques, have been very successful in finding new ways to design analog CMOS circuits that can approach the accuracy of bipolar analog designs.

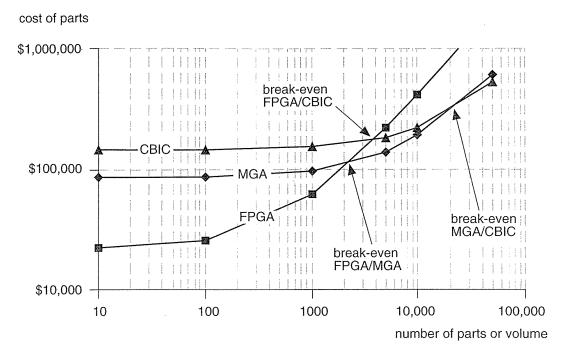

#### 1.1.2 Standard-Cell–Based ASICs

A **cell-based ASIC** (cell-based IC, or **CBIC**—a common term in Japan, pronounced "sea-bick") uses predesigned logic cells (AND gates, OR gates, multiplexers, and flip-flops, for example) known as **standard cells**. We could apply the term CBIC to any IC that uses cells, but it is generally accepted that a cell-based ASIC or CBIC means a standard-cell–based ASIC.

The standard-cell areas (also called flexible blocks) in a CBIC are built of rows of standard cells—like a wall built of bricks. The standard-cell areas may be used in combination with larger predesigned cells, perhaps microcontrollers or even micro-processors, known as **megacells**. Megacells are also called megafunctions, full-custom blocks, system-level macros (SLMs), fixed blocks, cores, or Functional Standard Blocks (FSBs).

The ASIC designer defines only the placement of the standard cells and the interconnect in a CBIC. However, the standard cells can be placed anywhere on the silicon; this means that all the mask layers of a CBIC are customized and are unique to a particular customer. The advantage of CBICs is that designers save time, money, and reduce risk by using a predesigned, pretested, and precharacterized **standard-cell library**. In addition each standard cell can be optimized individually. During the design of the cell library each and every transistor in every standard cell can be chosen to maximize speed or minimize area, for example. The disadvantages are the time or expense of designing or buying the standard-cell library and the time needed to fabricate all layers of the ASIC for each new design.

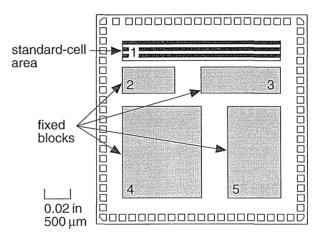

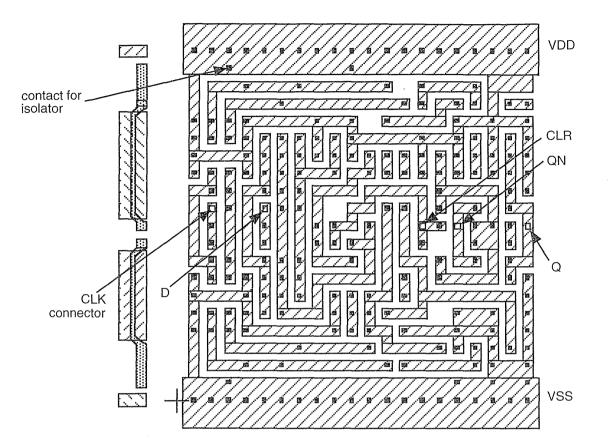

Figure 1.2 shows a CBIC (looking down on the die shown in Figure 1.1b, for example). The important features of this type of ASIC are as follows:

- All mask layers are customized-transistors and interconnect.

- Custom blocks can be embedded.

- Manufacturing lead time is about eight weeks.

**FIGURE 1.2** A cell-based ASIC (CBIC) die with a single standard-cell area (a flexible block) together with four fixed blocks. The flexible block contains rows of standard cells. This is what you might see through a low-powered microscope looking down on the die of Figure 1.1(b). The small squares around the edge of the die are bonding pads that are connected to the pins of the ASIC package.

Each standard cell in the library is constructed using full-custom design methods, but you can use these predesigned and precharacterized circuits without having to do any full-custom design yourself. This design style gives you the same performance and flexibility advantages of a full-custom ASIC but reduces design time and reduces risk.

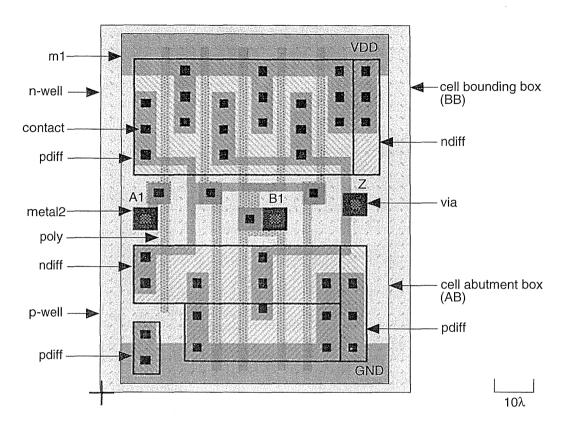

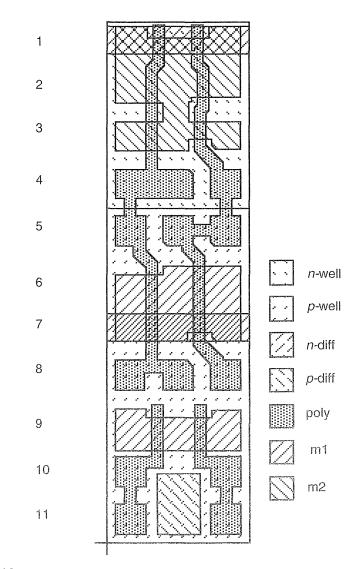

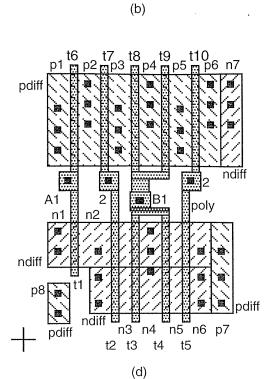

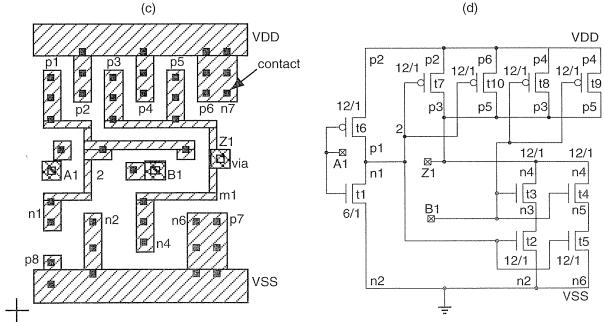

Standard cells are designed to fit together like bricks in a wall. Figure 1.3 shows an example of a simple standard cell (it is simple in the sense it is not maximized for density—but ideal for showing you its internal construction). Power and ground buses (VDD and GND or VSS) run horizontally on metal lines inside the cells.

Standard-cell design allows the automation of the process of assembling an ASIC. Groups of standard cells fit horizontally together to form rows. The rows stack vertically to form flexible rectangular blocks (which you can reshape during

8

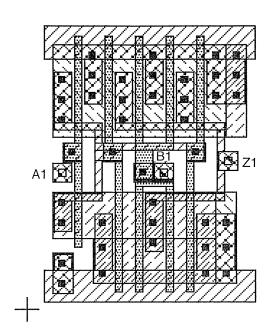

**FIGURE 1.3** Looking down on the layout of a standard cell. This cell would be approximately 25 microns wide on an ASIC with  $\lambda$  (lambda) = 0.25 microns (a micron is 10<sup>-6</sup> m). Standard cells are stacked like bricks in a wall; the abutment box (AB) defines the "edges" of the brick. The difference between the bounding box (BB) and the AB is the area of overlap between the bricks. Power supplies (labeled VDD and GND) run horizontally inside a standard cell on a metal layer that lies above the transistor layers. Each different shaded and labeled pattern represents a different layer. This standard cell has center connectors (the three squares, labeled A1, B1, and Z) that allow the cell to connect to others. The layout was drawn using ROSE, a symbolic layout editor developed by Rockwell and Compass, and then imported into Tanner Research's L-Edit.

design). You may then connect a **flexible block** built from several rows of standard cells to other standard-cell blocks or other full-custom logic blocks. For example, you might want to include a custom interface to a standard, predesigned microcontroller together with some memory. The microcontroller block may be a fixed-size megacell, you might generate the memory using a memory compiler, and the custom logic and memory controller will be built from flexible standard-cell blocks, shaped to fit in the empty spaces on the chip.

25

Both cell-based and gate-array ASICs use predefined cells, but there is a difference—we can change the transistor sizes in a standard cell to optimize speed and performance, but the device sizes in a gate array are fixed. This results in a trade-off in performance and area in a gate array at the silicon level. The trade-off between area and performance is made at the library level for a standard-cell ASIC.

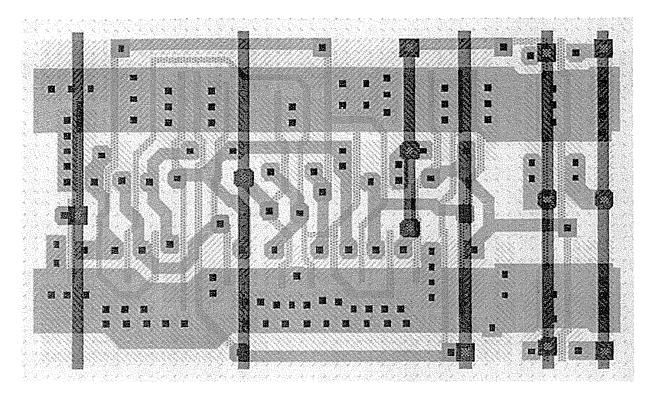

Modern CMOS ASICs use two, three, or more levels (or layers) of metal for interconnect. This allows wires to cross over different layers in the same way that we use copper traces on different layers on a printed-circuit board. In a two-level metal CMOS technology, connections to the standard-cell inputs and outputs are usually made using the second level of metal (metal2, the upper level of metal) at the tops and bottoms of the cells. In a three-level metal technology, connections may be internal to the logic cell (as they are in Figure 1.3). This allows for more sophisticated routing programs to take advantage of the extra metal layer to route interconnect over the top of the logic cells. We shall cover the details of routing ASICs in Chapter 17.

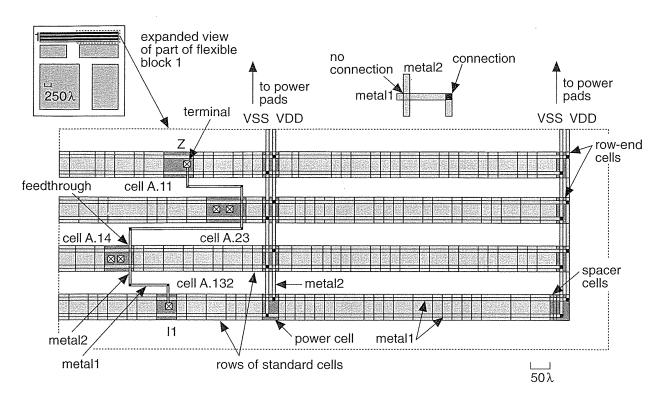

A connection that needs to cross over a row of standard cells uses a feedthrough. The term **feedthrough** can refer either to the piece of metal that is used to pass a signal through a cell or to a space in a cell waiting to be used as a feedthrough—very confusing. Figure 1.4 shows two feedthroughs: one in cell A.14 and one in cell A.23.

In both two-level and three-level metal technology, the power buses (VDD and GND) inside the standard cells normally use the lowest (closest to the transistors) layer of metal (metal1). The width of each row of standard cells is adjusted so that they may be aligned using spacer cells. The power buses, or rails, are then connected to additional vertical power rails using row-end cells at the aligned ends of each standard-cell block. If the rows of standard cells are long, then vertical power rails can also be run in metal2 through the cell rows using special power cells that just connect to VDD and GND. Usually the designer manually controls the number and width of the vertical power rails connected to the standard-cell blocks during physical design. A diagram of the power distribution scheme for a CBIC is shown in Figure 1.4.

All the mask layers of a CBIC are customized. This allows megacells (SRAM, a SCSI controller, or an MPEG decoder, for example) to be placed on the same IC with standard cells. Megacells are usually supplied by an ASIC or library company complete with behavioral models and some way to test them (a test strategy). ASIC library companies also supply compilers to generate flexible DRAM, SRAM, and ROM blocks. Since all mask layers on a standard-cell design are customized, memory design is more efficient and denser than for gate arrays.

For logic that operates on multiple signals across a data bus—a **datapath** (**DP**)—the use of standard cells may not be the most efficient ASIC design style. Some ASIC library companies provide a **datapath compiler** that automatically generates **datapath logic**. A **datapath library** typically contains cells such as adders, subtracters, multipliers, and simple **arithmetic and logical units** (ALUs). The con-

**FIGURE 1.4** Routing the CBIC (cell-based IC) shown in Figure 1.2. The use of regularly shaped standard cells, such as the one in Figure 1.3, from a library allows ASICs like this to be designed automatically. This ASIC uses two separate layers of metal interconnect (metal1 and metal2) running at right angles to each other (like traces on a printed-circuit board). Interconnections between logic cells uses spaces (called channels) between the rows of cells. ASICs may have three (or more) layers of metal allowing the cell rows to touch with the interconnect running over the top of the cells.

nectors of datapath library cells are **pitch-matched** to each other so that they fit together. Connecting datapath cells to form a datapath usually, but not always, results in faster and denser layout than using standard cells or a gate array.

Standard-cell and gate-array libraries may contain hundreds of different logic cells, including combinational functions (NAND, NOR, AND, OR gates) with multiple inputs, as well as latches and flip-flops with different combinations of reset, preset and clocking options. The ASIC library company provides designers with a data book in paper or electronic form with all of the functional descriptions and timing information for each library element.

#### 1.1.3 Gate-Array–Based ASICs

In a gate array (sometimes abbreviated to GA) or gate-array-based ASIC the transistors are predefined on the silicon wafer. The predefined pattern of transistors on a gate array is the base array, and the smallest element that is replicated to make the base array (like an M. C. Escher drawing, or tiles on a floor) is the base cell (sometimes called a primitive cell). Only the top few layers of metal, which define the interconnect between transistors, are defined by the designer using custom masks. To distinguish this type of gate array from other types of gate array, it is often called a masked gate array (MGA). The designer chooses from a gate-array library of predesigned and precharacterized logic cells. The logic cells in a gate-array library are often called macros. The reason for this is that the base-cell layout is the same for each logic cell, and only the interconnect (inside cells and between cells) is customized, so that there is a similarity between gate-array macros and a software macro. Inside IBM, gate-array macros are known as books (so that books are part of a library), but unfortunately this descriptive term is not very widely used outside IBM.

We can complete the diffusion steps that form the transistors and then stockpile wafers (sometimes we call a gate array a **prediffused array** for this reason). Since only the metal interconnections are unique to an MGA, we can use the stockpiled wafers for different customers as needed. Using wafers prefabricated up to the metallization steps reduces the time needed to make an MGA, the **turnaround time**, to a few days or at most a couple of weeks. The costs for all the initial fabrication steps for an MGA are shared for each customer and this reduces the cost of an MGA compared to a full-custom or standard-cell ASIC design.

There are the following different types of MGA or gate-array-based ASICs:

- Channeled gate arrays.

- Channelless gate arrays.

- Structured gate arrays.

The hyphenation of these terms when they are used as adjectives explains their construction. For example, in the term "channeled gate-array architecture," the *gate array* is *channeled*, as will be explained. There are two common ways of arranging (or arraying) the transistors on a MGA: in a channeled gate array we leave space between the rows of transistors for wiring; the routing on a channelless gate array uses rows of unused transistors. The channeled gate array was the first to be developed, but the channelless gate-array architecture is now more widely used. A structured (or embedded) gate array can be either channeled or channelless but it includes (or embeds) a custom block.

#### 1.1.4 Channeled Gate Array

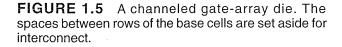

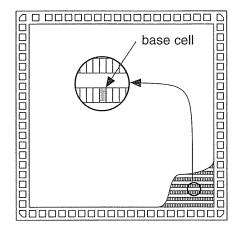

Figure 1.5 shows a **channeled gate array**. The important features of this type of MGA are:

- Only the interconnect is customized.

- The interconnect uses predefined spaces between rows of base cells.

- Manufacturing lead time is between two days and two weeks.

A channeled gate array is similar to a CBIC—both use rows of cells separated by channels used for interconnect. One difference is that the space for interconnect between rows of cells are fixed in height in a channeled gate array, whereas the space between rows of cells may be adjusted in a CBIC.

#### 1.1.5 Channelless Gate Array

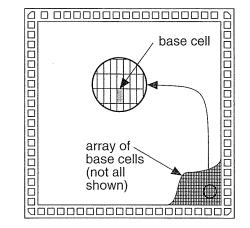

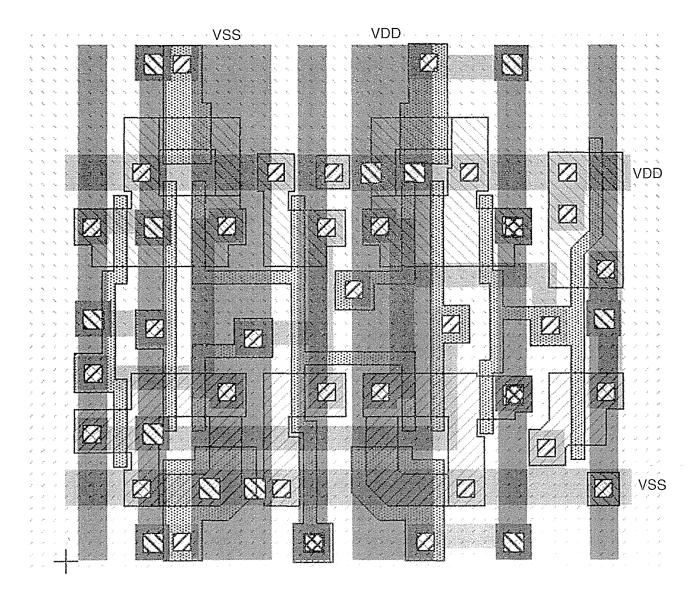

Figure 1.6 shows a **channelless gate array** (also known as a **channel-free gate array**, **sea-of-gates array**, or **SOG** array). The important features of this type of MGA are as follows:

- Only some (the top few) mask layers are customized—the interconnect.

- Manufacturing lead time is between two days and two weeks.

The key difference between a channelless gate array and channeled gate array is that there are no predefined areas set aside for routing between cells on a channelless gate array. Instead we route over the top of the gate-array devices. We can do this because we customize the contact layer that defines the connections between metal1, the first layer of metal, and the transistors. When we use an area of transistors for routing in a channelless array, we do not make any contacts to the devices lying underneath; we simply leave the transistors unused.

**FIGURE 1.6** A channelless gate-array or sea-ofgates (SOG) array die. The core area of the die is completely filled with an array of base cells (the base array).

The logic density—the amount of logic that can be implemented in a given silicon area—is higher for channelless gate arrays than for channeled gate arrays. This is usually attributed to the difference in structure between the two types of array. In fact, the difference occurs because the contact mask is customized in a channelless gate array, but is not usually customized in a channeled gate array. This leads to denser cells in the channelless architectures. Customizing the contact layer in a channelless gate array allows us to increase the density of gate-array cells because we can route over the top of unused contact sites.

#### 1.1.6 Structured Gate Array

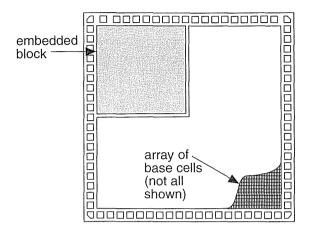

An embedded gate array or structured gate array (also known as masterslice or masterimage) combines some of the features of CBICs and MGAs. One of the disadvantages of the MGA is the fixed gate-array base cell. This makes the implementation of memory, for example, difficult and inefficient. In an embedded gate array we set aside some of the IC area and dedicate it to a specific function. This embedded area either can contain a different base cell that is more suitable for building memory cells, or it can contain a complete circuit block, such as a microcontroller.

Figure 1.7 shows an embedded gate array. The important features of this type of MGA are the following:

- Only the interconnect is customized.

- Custom blocks (the same for each design) can be embedded.

- Manufacturing lead time is between two days and two weeks.

An embedded gate array gives the improved area efficiency and increased performance of a CBIC but with the lower cost and faster turnaround of an MGA. One disadvantage of an embedded gate array is that the embedded function is fixed. For example, if an embedded gate array contains an area set aside for a 32 k-bit memory,

**FIGURE 1.7** A structured or embedded gate-array die showing an embedded block in the upper left corner (a static random-access memory, for example). The rest of the die is filled with an array of base cells.

but we only need a 16 k-bit memory, then we may have to waste half of the embedded memory function. However, this may still be more efficient and cheaper than implementing a 32 k-bit memory using macros on a SOG array.

ASIC vendors may offer several embedded gate array structures containing different memory types and sizes as well as a variety of embedded functions. ASIC companies wishing to offer a wide range of embedded functions must ensure that enough customers use each different embedded gate array to give the cost advantages over a custom gate array or CBIC (the Sun Microsystems SPARCstation 1 described in Section 1.3 made use of LSI Logic embedded gate arrays—and the 10K and 100K series of embedded gate arrays were two of LSI Logic's most successful products).

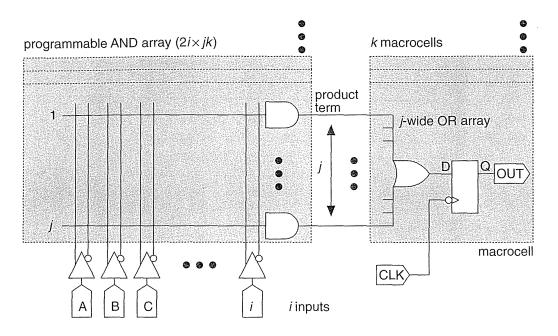

#### 1.1.7 Programmable Logic Devices

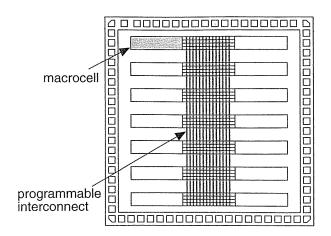

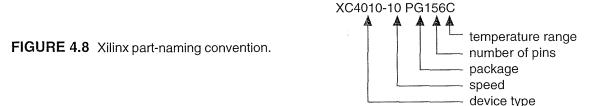

**Programmable logic devices** (**PLDs**) are standard ICs that are available in standard configurations from a catalog of parts and are sold in very high volume to many different customers. However, PLDs may be configured or programmed to create a part customized to a specific application, and so they also belong to the family of ASICs. PLDs use different technologies to allow programming of the device. Figure 1.8 shows a PLD and the following important features that all PLDs have in common:

- · No customized mask layers or logic cells

- Fast design turnaround

- A single large block of programmable interconnect

- A matrix of logic macrocells that usually consist of programmable array logic followed by a flip-flop or latch

The simplest type of programmable IC is a **read-only memory** (**ROM**). The most common types of ROM use a metal fuse that can be blown permanently (a **programmable ROM** or **PROM**). An **electrically programmable ROM**, or

**FIGURE 1.8** A programmable logic device (PLD) die. The macrocells typically consist of programmable array logic followed by a flip-flop or latch. The macrocells are connected using a large programmable interconnect block.

**EPROM**, uses programmable MOS transistors whose characteristics are altered by applying a high voltage. You can erase an EPROM either by using another high voltage (an **electrically erasable PROM**, or **EEPROM**) or by exposing the device to ultraviolet light (**UV-erasable PROM**, or **UVPROM**).

There is another type of ROM that can be placed on any ASIC—a **mask-programmable ROM** (mask-programmed ROM or masked ROM). A masked ROM is a regular array of transistors permanently programmed using custom mask patterns. An embedded masked ROM is thus a large, specialized, logic cell.

The same programmable technologies used to make ROMs can be applied to more flexible logic structures. By using the programmable devices in a large array of AND gates and an array of OR gates, we create a family of flexible and programmable logic devices called **logic arrays**. The company Monolithic Memories (bought by AMD) was the first to produce **Programmable Array Logic** (PAL<sup>®</sup>, a registered trademark of AMD) devices that you can use, for example, as transition decoders for state machines. A PAL can also include registers (flip-flops) to store the current state information so that you can use a PAL to make a complete state machine.

Just as we have a mask-programmable ROM, we could place a logic array as a cell on a custom ASIC. This type of logic array is called a **programmable logic array** (PLA). There is a difference between a PAL and a PLA: a PLA has a programmable AND logic array, or **AND plane**, followed by a programmable OR logic array, or **OR plane**; a PAL has a programmable AND plane and, in contrast to a PLA, a fixed OR plane.

Depending on how the PLD is programmed, we can have an **erasable PLD** (EPLD), or **mask-programmed PLD** (sometimes called a masked PLD but usually just PLD). The first PALs, PLAs, and PLDs were based on bipolar technology and used programmable fuses or links. CMOS PLDs usually employ floating-gate transistors (see Section 4.3, "EPROM and EEPROM Technology").

#### 1.1.8 Field-Programmable Gate Arrays

A step above the PLD in complexity is the **field-programmable gate array** (**FPGA**). There is very little difference between an FPGA and a PLD—an FPGA is usually just larger and more complex than a PLD. In fact, some companies that manufacture programmable ASICs call their products FPGAs and some call them **complex PLDs**. FPGAs are the newest member of the ASIC family and are rapidly growing in importance, replacing TTL in microelectronic systems. Even though an FPGA is a type of gate array, we do not consider the term gate-array–based ASICs to include FPGAs. This may change as FPGAs and MGAs start to look more alike.

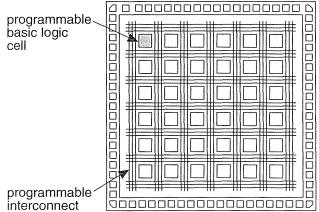

Figure 1.9 illustrates the essential characteristics of an FPGA:

- None of the mask layers are customized.

- A method for programming the basic logic cells and the interconnect.

- The core is a regular array of programmable basic logic cells that can implement combinational as well as sequential logic (flip-flops).

- A matrix of programmable interconnect surrounds the basic logic cells.

- Programmable I/O cells surround the core.

- Design turnaround is a few hours.

We shall examine these features in detail in Chapters 4–8.

**FIGURE 1.9** A field-programmable gate array (FPGA) die. All FPGAs contain a regular structure of programmable basic logic cells surrounded by programmable interconnect. The exact type, size, and number of the programmable basic logic cells varies tremendously.

#### **1.2** Design Flow

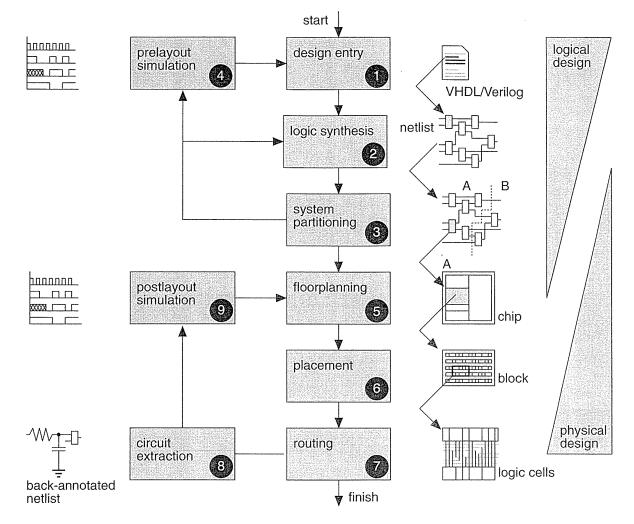

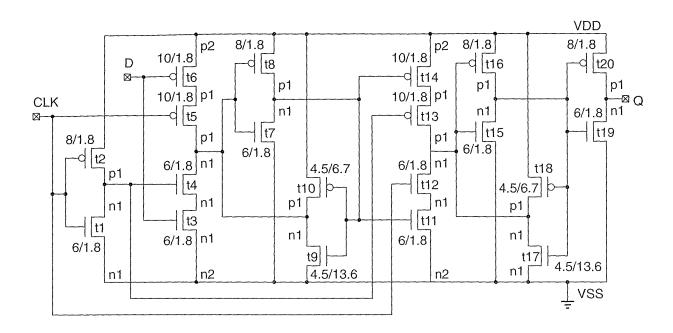

Figure 1.10 shows the sequence of steps to design an ASIC; we call this a **design flow**. The steps are listed below (numbered to correspond to the labels in Figure 1.10) with a brief description of the function of each step.

1. Design entry. Enter the design into an ASIC design system, either using a hardware description language (HDL) or schematic entry.

FIGURE 1.10 ASIC design flow.

- 2. *Logic synthesis*. Use an HDL (VHDL or Verilog) and a logic synthesis tool to produce a **netlist**—a description of the logic cells and their connections.

- 3. System partitioning. Divide a large system into ASIC-sized pieces.

- 4. Prelayout simulation. Check to see if the design functions correctly.

- 5. Floorplanning. Arrange the blocks of the netlist on the chip.

- 6. Placement. Decide the locations of cells in a block.

- 7. Routing. Make the connections between cells and blocks.

- 8. Extraction. Determine the resistance and capacitance of the interconnect.

9. *Postlayout simulation*. Check to see the design still works with the added loads of the interconnect.

Steps 1–4 are part of **logical design**, and steps 5–9 are part of **physical design**. There is some overlap. For example, system partitioning might be considered as either logical or physical design. To put it another way, when we are performing system partitioning we have to consider both logical and physical factors. Chapters 9–14 of this book is largely about logical design and Chapters 15–17 largely about physical design.

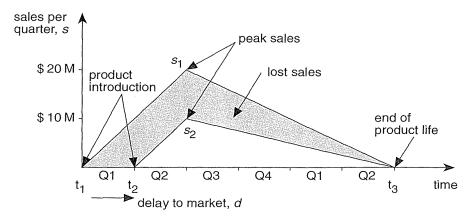

#### **1.3** Case Study

Sun Microsystems released the SPARCstation 1 in April 1989. It is now an old design but a very important example because it was one of the first workstations to make extensive use of ASICs to achieve the following:

- Better performance at lower cost

- Compact size, reduced power, and quiet operation

- Reduced number of parts, easier assembly, and improved reliability

The SPARCstation 1 contains about 50 ICs on the system motherboard excluding the DRAM used for the system memory (standard parts). The SPARCstation 1 designers partitioned the system into the nine ASICs shown in Table 1.1 and wrote specifications for each ASIC—this took about three months.<sup>1</sup> LSI Logic and Fujitsu designed the SPARC **integer unit** (IU) and **floating-point unit** (**FPU**) to these specifications. The clock ASIC is a fairly straightforward design and, of the six remaining ASICs, the video controller/data buffer, the RAM controller, and the **direct memory access** (**DMA**) controller are defined by the 32-bit **system bus** (**SBus**) and the other ASICs that they connect to. The rest of the system is partitioned into three more ASICs: the **cache controller**, **memory-management unit** (MMU), and the data buffer. These three ASICs, with the IU and FPU, have the most critical timing paths and determine the system partitioning. The design of ASICs 3–8 in Table 1.1 took five Sun engineers six months after the specifications were complete. During the design process, the Sun engineers simulated the entire SPARCstation 1—including execution of the Sun operating system (SunOS).

<sup>&</sup>lt;sup>1</sup>Some information in Section 1.3 and Section 15.3 is from the SPARCstation 10 Architecture Guide—May 1992, p. 2 and pp. 27–28 and from two publicity brochures (known as "sparkle sheets"). The first is "Concept to System: How Sun Microsystems Created SPARCstation 1 Using LSI Logic's ASIC System Technology," A. Bechtolsheim, T. Westberg, M. Insley, and J. Ludemann of Sun Microsystems; J-H. Huang and D. Boyle of LSI Logic. This is an LSI Logic publication. The second paper is "SPARCstation 1: Beyond the 3M Horizon," A. Bechtolsheim and E. Frank, a Sun Microsystems publication. I did not include these as references since they are impossible to obtain now, but I would like to give credit to Andy Bechtolsheim and the Sun Microsystems and LSI Logic engineers.

|   | SPARCstation 1 ASIC                   | Gates (k-gates) |

|---|---------------------------------------|-----------------|

| 1 | SPARC integer unit (IU)               | 20              |

| 2 | SPARC floating-point unit (FPU)       | 50              |

| 3 | Cache controller                      | 9               |

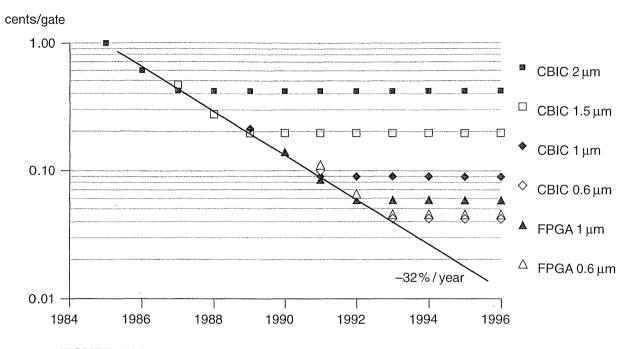

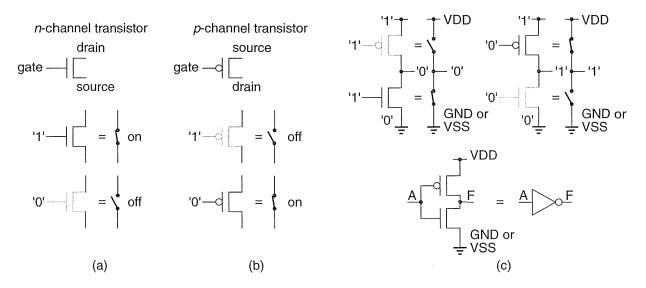

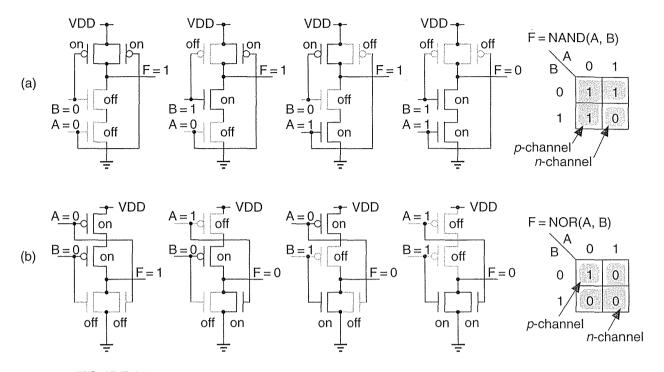

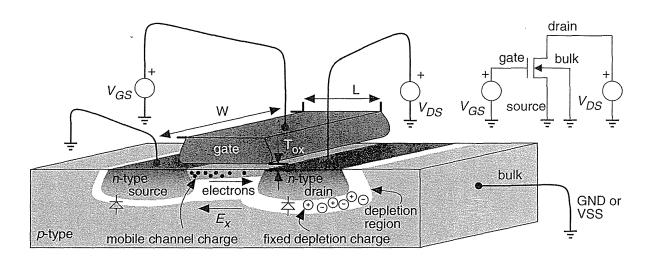

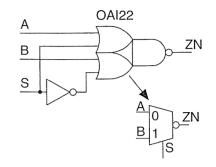

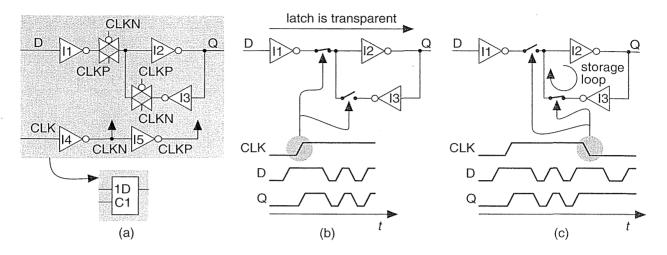

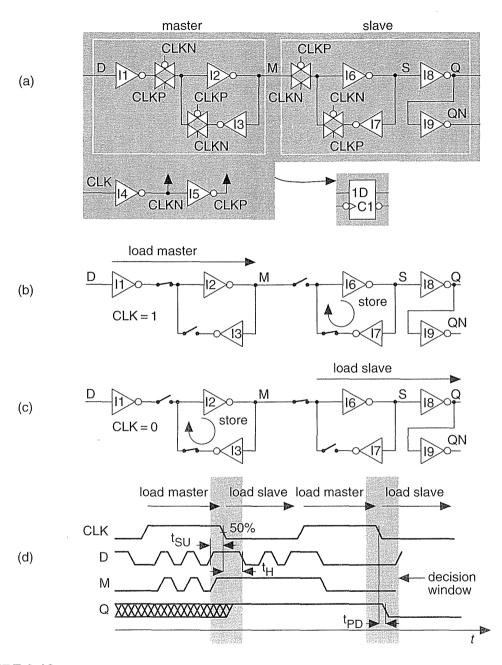

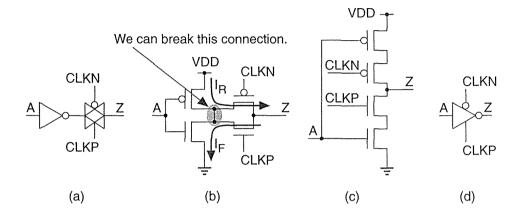

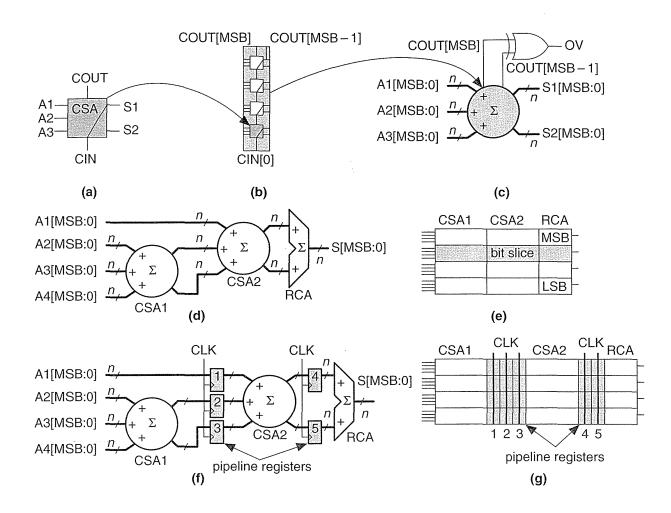

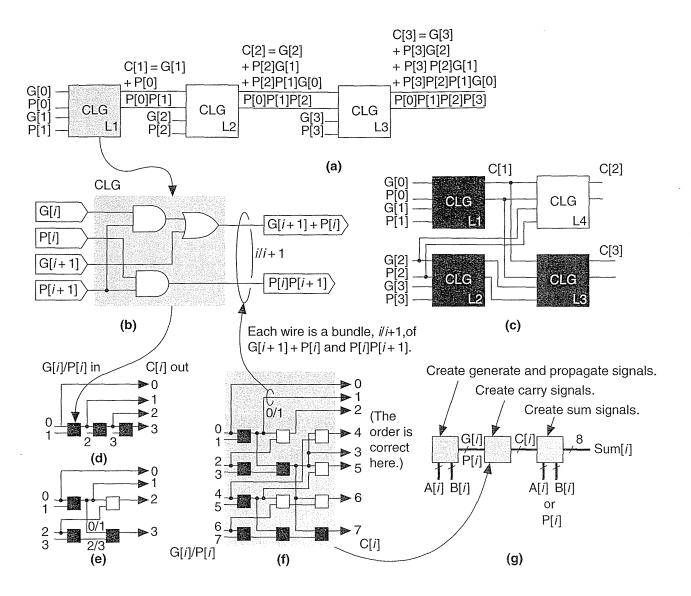

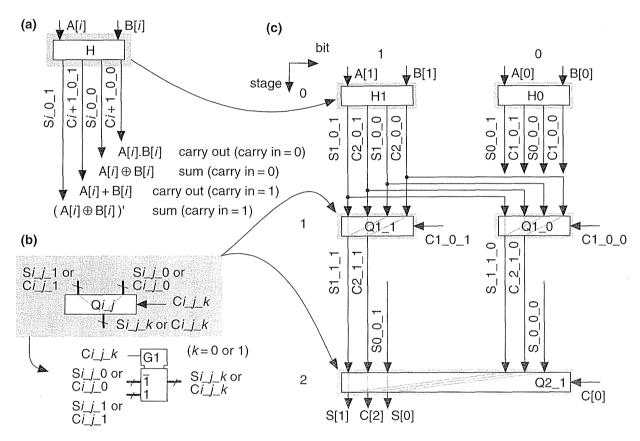

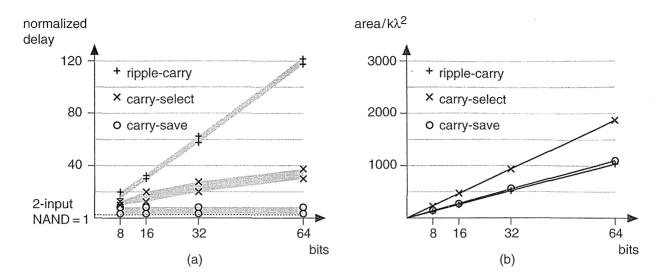

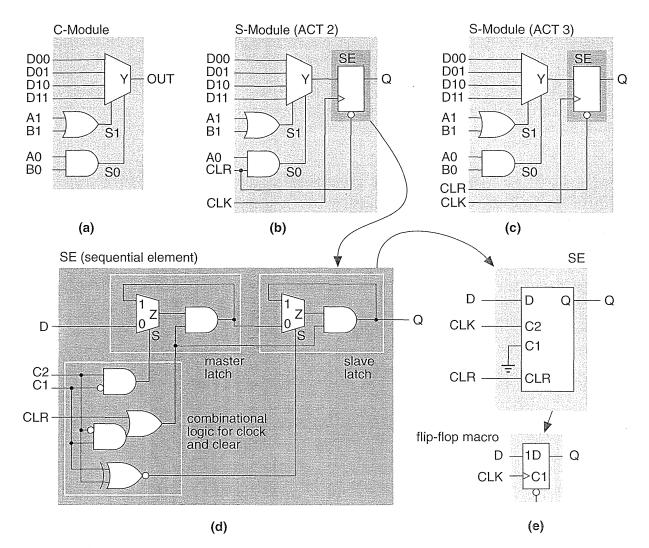

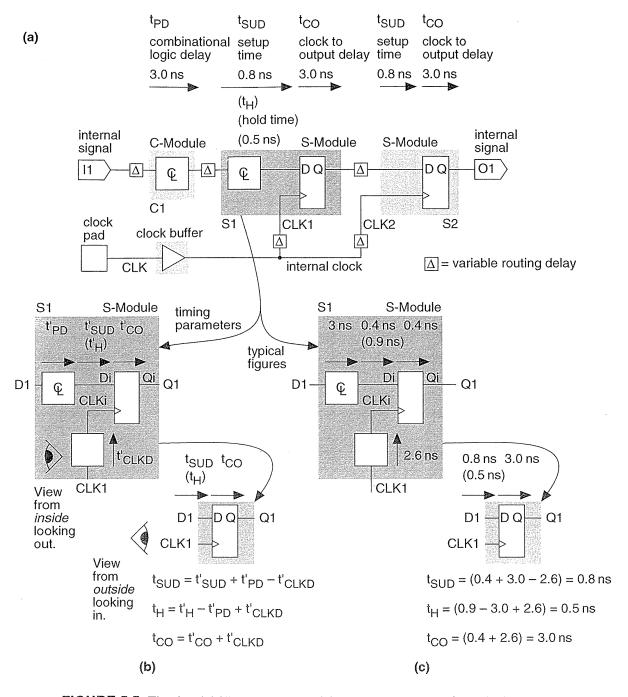

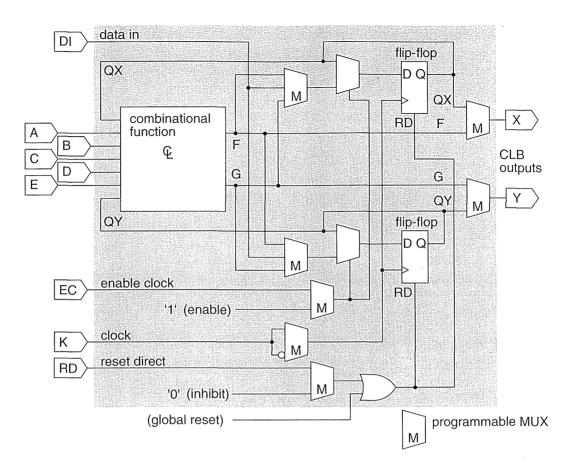

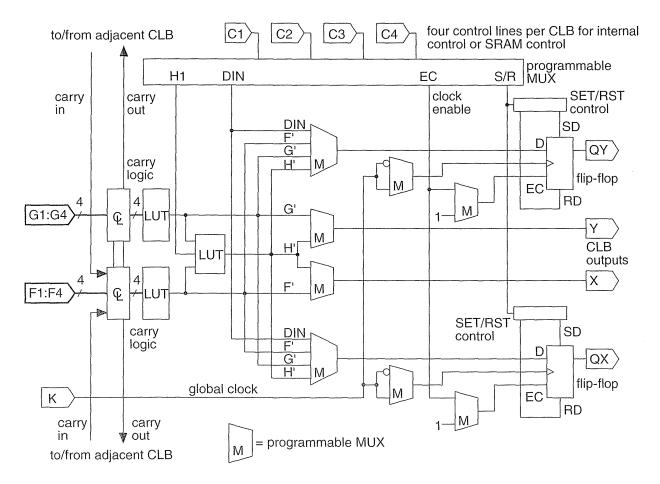

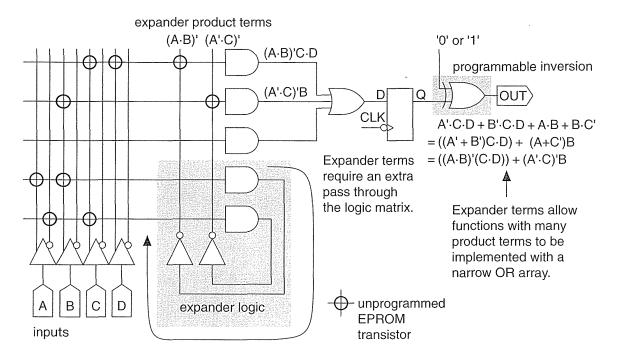

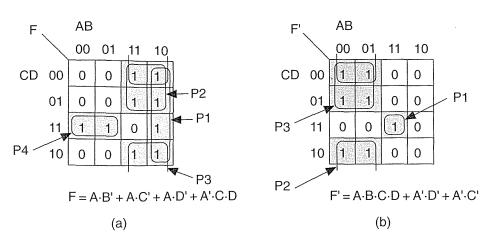

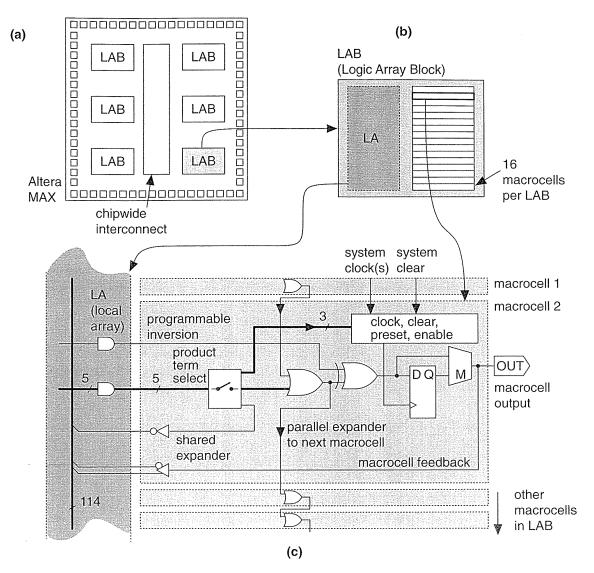

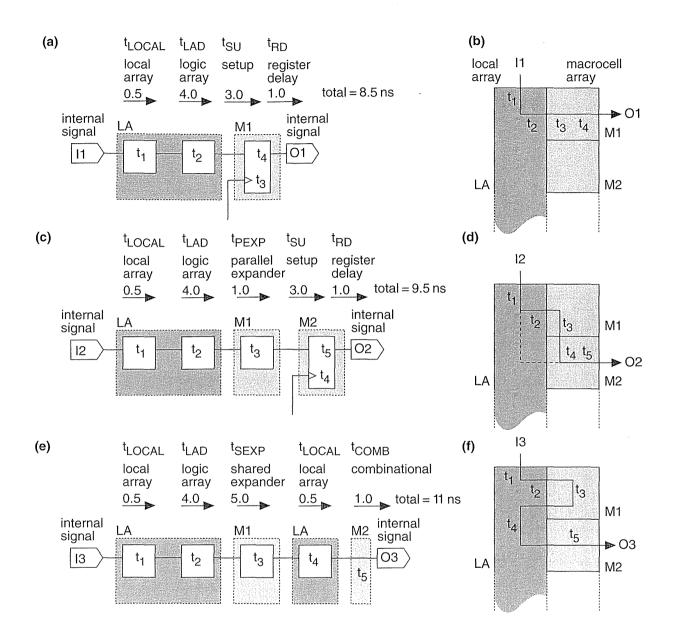

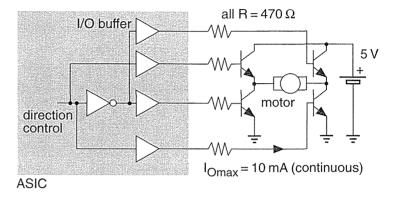

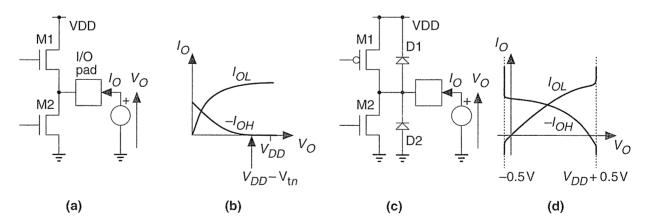

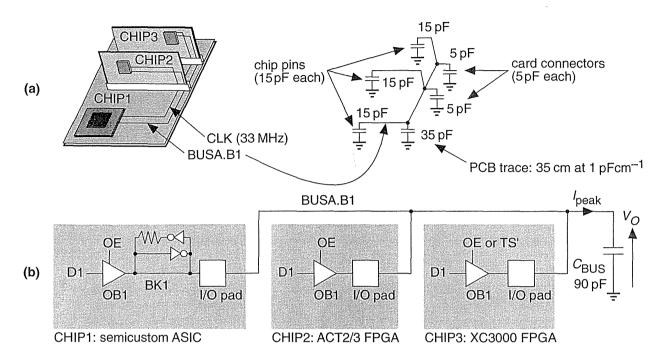

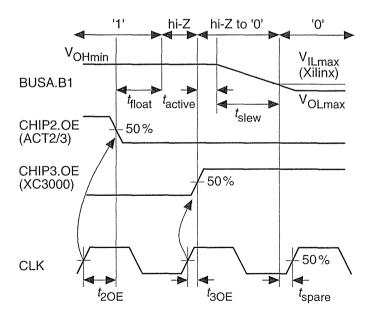

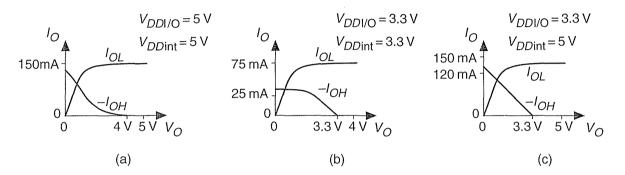

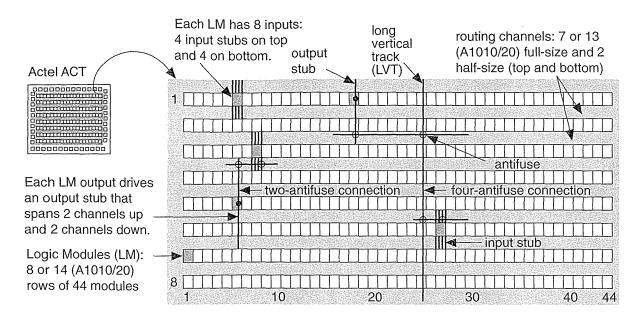

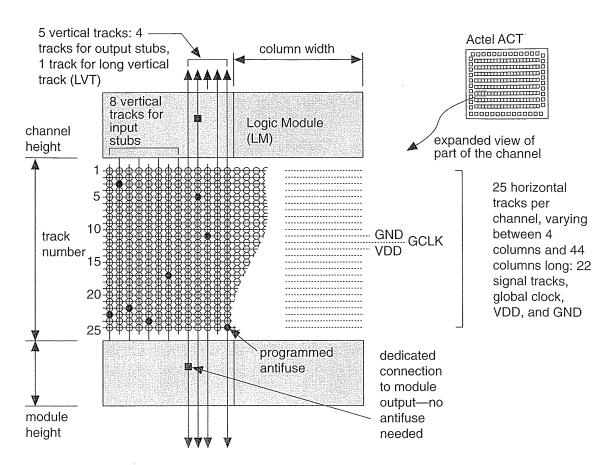

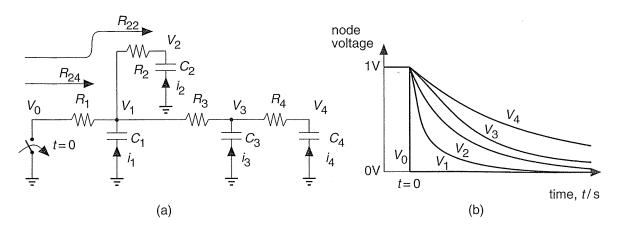

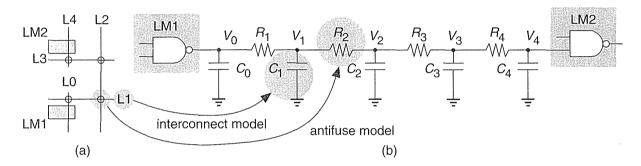

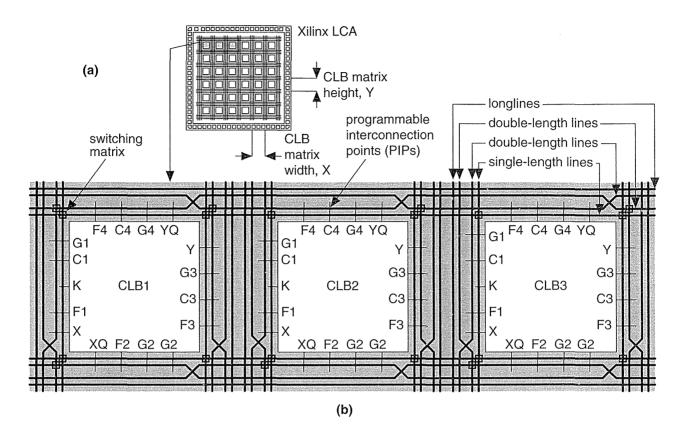

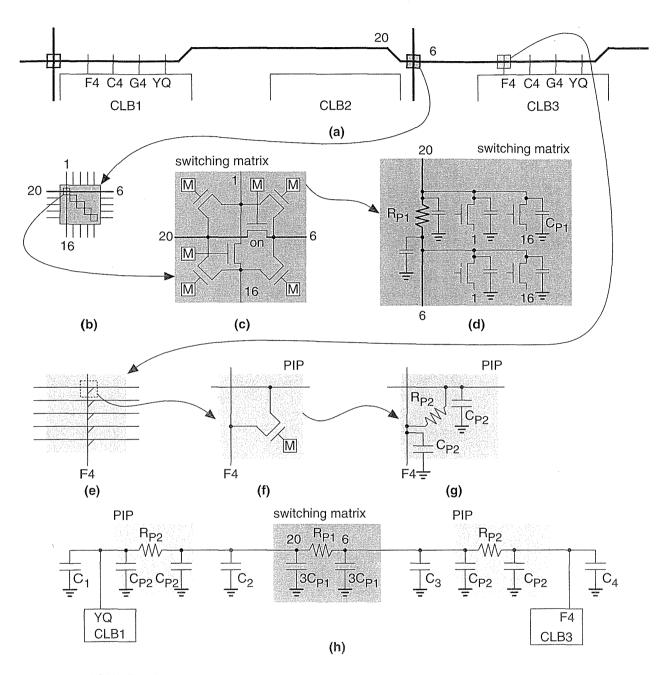

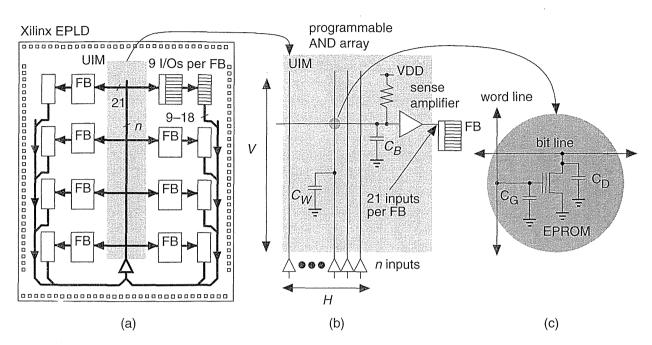

| 4 | Memory-management unit (MMU)          | 5               |