US006338109B1

#### (12) United States Patent Snyder et al.

#### (54) MICROCONTROLLER DEVELOPMENT SYSTEM AND APPLICATIONS THEREOF FOR DEVELOPMENT OF A UNIVERSAL SERIAL BUS MICROCONTROLLER

- (75) Inventors: Warren S. Snyder, Snohomish; Frederick D. Jaccard, Woodinville, both of WA (US)

- (73) Assignce: Cypress Semiconductor Corp., San Jose, CA (US)

- (\*) Notice: This patent issued on a continued prosecution application filed under 37 CFR 1.53(d), and is subject to the twenty year patent term provisions of 35 U.S.C. 154(a)(2).

Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 08/711,419

- (22) Filed: Aug. 30, 1996

- (51) Int. Cl.<sup>7</sup> ...... G06F 13/00

#### (56) References Cited

#### **U.S. PATENT DOCUMENTS**

| 3,833,888 A |   | 9/1974 | Stafford et al.      |

|-------------|---|--------|----------------------|

| 4,038,533 A |   | 7/1977 | Dummermuth           |

| 4,042,972 A |   | 8/1977 | Gruner et al.        |

| 4,433,378 A | * | 2/1984 | Leger 395/280        |

| 4,466,055 A |   | 8/1984 | Kinoshita et al.     |

| 4,511,968 A |   | 4/1985 | Fencsik et al.       |

| 5,047,926 A | * | 9/1991 | Kuo et al 395/183.05 |

| 5,241,631 A | * | 8/1993 | Smith et al 395/306  |

| 5,313,618 A | * | 5/1994 | Pawloski 703/28      |

#### (10) Patent No.: US 6,338,109 B1 (45) Date of Patent: \*Jan. 8, 2002

(List continued on next page.)

#### FOREIGN PATENT DOCUMENTS

#### WO WO 97/36230 10/1997

#### OTHER PUBLICATIONS

Universal Serial Bus Specification, Revision 1.0, pp. 1–268, Jan. 15, 1996.

Universal Host Controller Interface (UHCI) Design Guide, Revision 1.1, Intel, pp. 1–41, Mar. 1996.

Warren Snyder, "Dual ROM Microprogrammable Microprocessor and Universal Serial Bus Microcontroller Development System", U.S. Serial No. 08/705,807, Filed Aug. 30, 1996. (Now U.S. Patent No. 5,859,993—Issued Jan. 12, 1999).

Primary Examiner—Ayaz R. Sheikh

Assistant Examiner-Frantz Blanchard Jean

(74) Attorney, Agent, or Firm-Christopher P. Maiorana, P.C.

#### (57) ABSTRACT

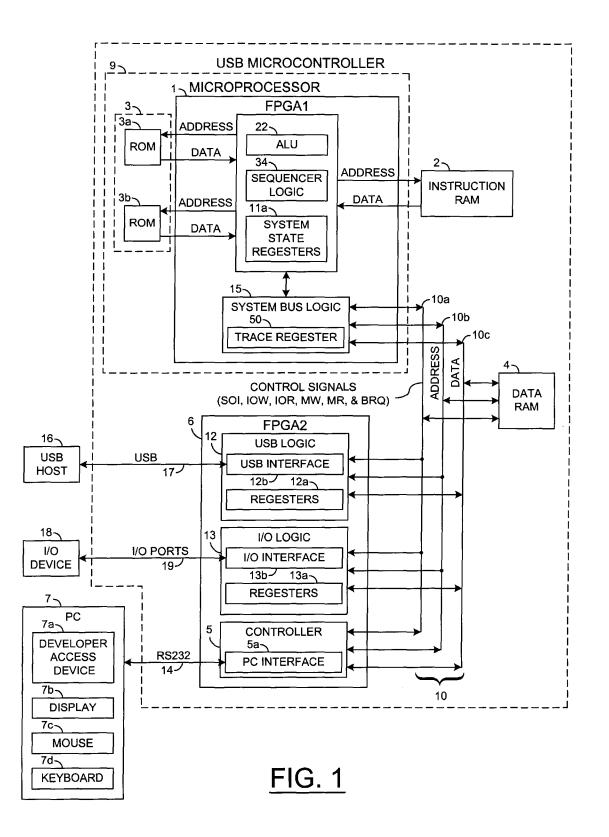

A microcontroller including a system bus; a microprocessor coupled to the system bus and configured to transfer data and control signals over the system bus; a memory device coupled to the microprocessor and mapped to the system bus and configured to store microprogram instructions for execution by the microprocessor; a controller coupled to the system bus and configured to transfer data and control signals to the microprocessor over the system bus; a host interface coupled to the system bus and configured to interface to a host computer and receive the data and the control signals over the system bus from the microprocessor; and an I/O interface to at least one I/O device and receive the data and the control signals over the system bus from the microprocessor.

#### 23 Claims, 2 Drawing Sheets

Page 2

#### U.S. PATENT DOCUMENTS

| U.S. PATENT DOCUMENTS                    | 5,689,684 A * 11/1997 Mulchandani et al 703/23 |

|------------------------------------------|------------------------------------------------|

|                                          | 5,691,994 A * 11/1997 Acosta et al 371/40.1    |

| 5,495,593 A * 2/1996 Elmer et al 711/103 | 5,758,107 A * 5/1998 Robles et al 395/307      |

| 5,546,562 A * 8/1996 Patel 395/500       | 5,805,792 A * 9/1998 Swoboda et al             |

| 5,664,123 A * 9/1997 Lee et al 395/309   | 5,941,979 A * 8/1999 Lentz 712/33              |

| 5.675.813 A 10/1997 Holmdahl             | -,                                             |

\* cited by examiner

CKF' O) Α RM A Find authenticated court documents without watermarks at docketalarm.com. 5

#### MICROCONTROLLER DEVELOPMENT SYSTEM AND APPLICATIONS THEREOF FOR DEVELOPMENT OF A UNIVERSAL SERIAL BUS MICROCONTROLLER

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

This invention relates to microprocessor development systems, and more particularly to a Universal Serial Bus 10 ("USB") microcontroller development system configured to aid in the design, debug, and testing of USB compliant devices and firmware.

2. Discussion of Background

USB is a peripheral bus standard that allows computer <sup>15</sup> peripherals to be attached to a personal computer without the need for specialized cards or other vendor specific hardware attachments. The USB standard specifies a common configuration for the connection of well known peripherals such as CD-ROM, tape and floppy disk drives, scanners, printers, <sup>20</sup> keyboards, joysticks, mice, telephones, modems, etc. In addition to well known peripheral devices, the USB standard has flexibility to accommodate less known and newly developed technologies. Information about the USB standard, including the specification for building USB compliant 25 devices, is currently available free of charge over the Internet.

Developers wishing to implement USB devices must build that device to the USB standard. Prior to fabricating IC's for USB standard devices, a developer will spend a significant amount of resources in testing and refinement of prototypes. An efficient method for testing USB compliant devices is needed to reduce the costs associated with prototype development and testing of those devices.

The design and manufacture of electronic devices such as counters, state machines, specialized registers, and microprocessors is currently aided by technologies that allow engineers to specify design characteristics of a circuit, such as storage device size, register types, connections and associated logic, in a Hardware Description Language ("HDL"). This source code or HDL is then compiled, allowing the electronic device to be simulated and debugged while implementing the specified circuit characteristics. Once the operation of device is verified, the compiled source code can be  $_{45}$ mapped to a specific architecture such as Application Specific Integrated Circuits ("ASICs") or Field Programmable Gate Arrays ("FPGAs"). This allows the system designer to produce a device with design flexibility and portability into various architecture families. 50

As an example, a 3-bit shift register can be implemented in a HDL such as Register Transfer Language ("RTL") with the following RTL statements:

| ENTITY  | shif  | ter3 IS port (                    |

|---------|-------|-----------------------------------|

| clk     | :     | IN BIT;                           |

| х       | :     | IN BIT;                           |

| q0      | :     | OUT BIT;                          |

| q1      | :     | OUT BIT;                          |

| q2      | :     | OUT BIT;                          |

| END shi | fter3 | ;                                 |

| ARCHIT  | ECI   | TURE struct OF shifter3 IS        |

| SIG     | NAL   | _q0_temp, q1_temp, q2_temp : BIT; |

| BEG     | GIN   |                                   |

|         | d1    | : DFF PORT MAP (x,clk,q0_temp);   |

|         | 42    | · DEE POPT MAP (a) temp all al    |

DOCKE

| -con |  |

|------|--|

|      |  |

| $q0 \ll q0$ _temp;                            |

|-----------------------------------------------|

| q1 <= q1temp;<br>q2 <= q2temp;<br>END struct; |

which defines the inputs and outputs of the shifter and then maps those bits to a series of D Flip-Flops. After compiling the source code and debugging the circuit, a netlist can be generated for a specific family of FPGA or ASIC devices to produce the circuit with the desired functionality.

#### SUMMARY OF THE INVENTION

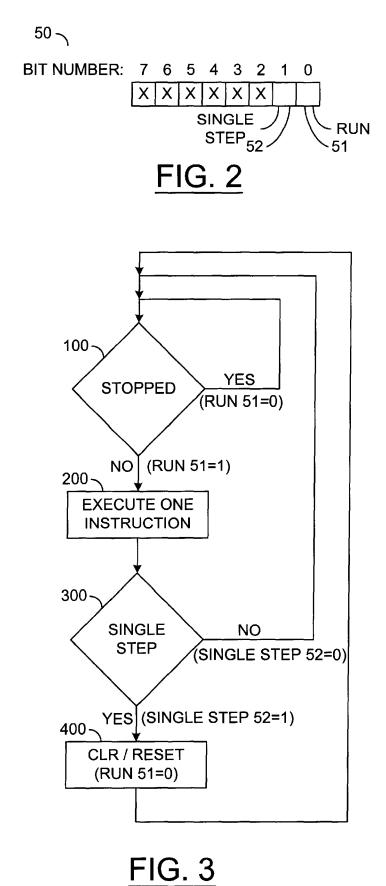

Accordingly, one object of the present invention is to provide a flexible USB microcontroller development system that allows for testing of USB compliant devices. The microcontroller includes a microprocessor with instruction RAM, a controller with a computer interface (e.g., RS-232) to a personal computer or other external computing device, data RAM, USB logic and registers for interfacing to a USB host computer, and I/O logic and registers for interfacing to an I/O device. The USB microcontroller development system includes the microcontroller, an external computer, a USB host computer, and an I/O device. The USB microcontroller development system allows both the microprocessor or an attached external computer to control the microcontroller. This is accomplished by mapping the USB microcontroller system state which includes the contents of the data RAM, the microprocessors system state registers including system state registers corresponding to the contents of the instruction RAM, the USB logic registers, and the I/O logic registers to a system bus. The controller or microprocessor places address, data, and control signals on the system bus which are decoded by various logic to allow reading or writing of the system state. The controller reads or writes the instruction RAM by reading or writing a program counter and an instruction register, included as part of the microprocessor's system state registers, via the system bus. Accordingly, the external computer connected to the controller via the RS-232 bus can read or write the USB microcontroller system state to aid in the design, debug, and testing of USB compliant devices and firmware.

It is also an object of the present invention to provide a development access device on the external computer for providing a user a graphical interface for controlling the USB microcontroller. The development access device displaying menus, buttons, text boxes etc. corresponding to the microprocessor's system state registers, the contents of the instruction RAM, the USB logic registers, and the I/O logic registers. The user, after selecting the appropriate menu, button, or filling in the appropriate text box, can read or write the corresponding microprocessor's system state registers, the contents of the instruction RAM, the USB logic registers, and the I/O logic registers via the external computer and computer interface to control the USB microcontroller.

It is yet another object of the present invention to provide a method for implementing the above USB microcontroller development system utilizing a Hardware Description Language. By utilizing a Hardware Description Language, the design engineers are free to concentrate on the design of important features of the system and it's functionality rather

than a gate level implementation of the system. After deter-65 mining top level characteristics and functional blocks of the system, an HDL program describing those characteristics

Find authenticated court documents without watermarks at docketalarm.com.

55

<sup>:</sup> DFF PORT MAP (q0\_temp,clk,q1\_temp); : DFF PORT MAP (q1\_temp,clk,q2\_temp);

## DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.