## EZ-USB FX1™ USB Microcontroller Full Speed USB Peripheral Controller

#### **Features**

- Single chip integrated USB transceiver, SIE, and enhanced 8051 microprocessor

- Fit, form, and function upgradable to the FX2LP (CY7C68013A)

- Pin compatible

- □ Object code compatible

- □ Functionally compatible (FX1 functionality is a subset of the FX2LP)

- Draws no more than 65 mA in any mode, making the FX1 suitable for bus powered applications

- Software: 8051 runs from internal RAM, which is:

- Downloaded using USB

- □ Loaded from EEPROM

- □ External memory device (128 pin configuration only)

- 16 KB of on-chip code/data RAM

- Four programmable BULK/INTERRUPT/ISOCHRONOUS endpoints

- □ Buffering options: double, triple, and quad

- Additional programmable (BULK/INTERRUPT) 64-byte endpoint

- 8- or 16-bit external data interface

- Smart media standard ECC generation

- GPIF

- □ Allows direct connection to most parallel interfaces; 8- and 16-bit

- □ Programmable waveform descriptors and configuration registers to define waveforms

- □ Supports multiple ready (RDY) inputs and Control (CTL) outputs

- Integrated, industry standard 8051 with enhanced features:

- □ Up to 48 MHz clock rate

- ☐ Four clocks for each instruction cycle

- □ Two USARTS

- ☐ Three counters or timers

- □ Expanded interrupt system

- □ Two data pointers

- 3.3 V operation with 5 V tolerant inputs

- Smart SIE

- Vectored USB interrupts

- Separate data buffers for the setup and DATA portions of a CONTROL transfer

- Integrated I<sup>2</sup>C controller, running at 100 or 400 KHz

- 48 MHz, 24 MHz, or 12 MHz 8051 operation

- Four integrated FIFOs

- □ Brings glue and FIFOs inside for lower system cost

- Automatic conversion to and from 16-bit buses

- ☐ Master or slave operation

- □ FIFOs can use externally supplied clock or asynchronous strobes

- □ Easy interface to ASIC and DSP ICs

- Vectored for FIFO and GPIF Interrupts

- Up to 40 general purpose IOs (GPIO)

- Four package options:

- 128-pin TQFP

- □ 100-pin TQFP

- □ 56-pin SSOP

- □ 56-pin QFN Pb-free

#### EXHIBIT 2034

LG Elecs. v. Cypress Semiconductor IPR2014-01386, U.S. Pat. 6,012,103

Errata: For information on silicon errata, see "Errata" on page 71. Details include trigger conditions, devices affected, and proposed workaround.

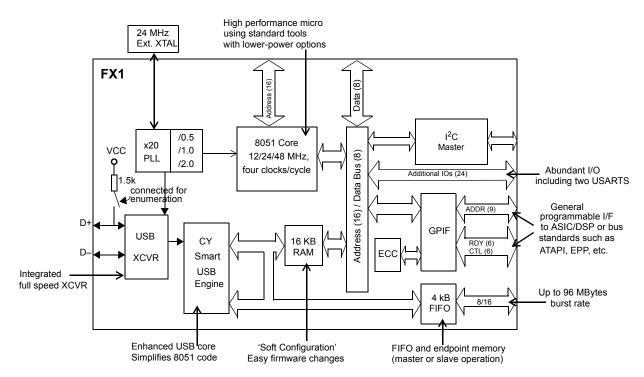

### **Logic Block Diagram**

#### **Contents**

| Functional Description              | 4  |

|-------------------------------------|----|

| Applications                        |    |

| Functional Overview                 | 4  |

| USB Signaling Speed                 | 4  |

| 8051 Microprocessor                 | 4  |

| I <sup>2</sup> C Bus                | 5  |

| Buses                               | 5  |

| USB Boot Methods                    | 5  |

| ReNumeration™                       | 6  |

| Bus-powered Applications            | 6  |

| Interrupt System                    | 6  |

| Reset and Wakeup                    | 8  |

| Program/Data RAM                    | 9  |

| Endpoint RAM                        |    |

| External FIFO Interface             | 11 |

| GPIF                                |    |

| ECC Generation                      | 13 |

| USB Uploads and Downloads           |    |

| Autopointer Access                  |    |

| I <sup>2</sup> C Controller         | 13 |

| Compatible with Previous Generation |    |

| EZ-USB FX2                          |    |

| Pin Assignments                     |    |

| CY7C64713 Pin Definitions           |    |

| Register Summary                    |    |

| Absolute Maximum Ratings            |    |

| Operating Conditions                |    |

| DC Characteristics                  |    |

| USB Transceiver                     |    |

| AC Electrical Characteristics       |    |

| USB Transceiver                     |    |

| PORTC Strobe Feature Timings        | 51 |

| 0                                                               | PIF Synchronous Signals                                                                                                                                                                                                               | 52                                       |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 3                                                               | lave FIFO Synchronous Read                                                                                                                                                                                                            | 53                                       |

| S                                                               | lave FIFO Asynchronous Read                                                                                                                                                                                                           | 54                                       |

|                                                                 | lave FIFO Synchronous Write                                                                                                                                                                                                           |                                          |

|                                                                 | lave FIFO Asynchronous Write                                                                                                                                                                                                          |                                          |

| S                                                               | lave FIFO Synchronous Packet End Strobe                                                                                                                                                                                               | 56                                       |

|                                                                 | lave FIFO Asynchronous Packet End Strobe                                                                                                                                                                                              |                                          |

|                                                                 | lave FIFO Output Enable                                                                                                                                                                                                               |                                          |

| S                                                               | lave FIFO Address to Flags/Data                                                                                                                                                                                                       | 58                                       |

|                                                                 | lave FIFO Synchronous Address                                                                                                                                                                                                         |                                          |

|                                                                 | lave FIFO Asynchronous Address                                                                                                                                                                                                        |                                          |

|                                                                 | equence Diagram                                                                                                                                                                                                                       |                                          |

|                                                                 | ing Information                                                                                                                                                                                                                       |                                          |

| С                                                               | rdering Code Definitions                                                                                                                                                                                                              | 64                                       |

|                                                                 | ige Diagrams                                                                                                                                                                                                                          | 65                                       |

|                                                                 | Flat Package No Leads (QFN) Package                                                                                                                                                                                                   |                                          |

|                                                                 | n Notes                                                                                                                                                                                                                               |                                          |

| Acror                                                           | ıyms                                                                                                                                                                                                                                  | 70                                       |

|                                                                 |                                                                                                                                                                                                                                       |                                          |

| Docu                                                            | ment Conventions                                                                                                                                                                                                                      | 70                                       |

| Docu<br>U                                                       | ment Conventionsnits of Measure                                                                                                                                                                                                       | <b>70</b>                                |

| Docui<br>U<br>Errata                                            | ment Conventionsnits of Measure                                                                                                                                                                                                       | <b>70</b><br>70<br><b>71</b>             |

| Docui<br>U<br>Errata<br>P                                       | ment Conventions                                                                                                                                                                                                                      | <b>70</b><br>70<br><b>71</b><br>71       |

| Docui<br>U<br>Errata<br>P<br>E                                  | ment Conventions  nits of Measure  art Numbers Affected  Z-USB FX1 Qualification Status                                                                                                                                               | <b>70</b><br>70<br><b>71</b><br>71       |

| Docui<br>U<br>Errata<br>P<br>E<br>E                             | ment Conventions  nits of Measure  art Numbers Affected  Z-USB FX1 Qualification Status  Z-USB FX1 Errata Summary                                                                                                                     | <b>70</b><br><b>71</b><br>71<br>71       |

| Docui<br>U<br>Errata<br>P<br>E<br>E<br>Docui                    | ment Conventions  nits of Measure  art Numbers Affected  Z-USB FX1 Qualification Status  Z-USB FX1 Errata Summary  ment History Page                                                                                                  | <b>70 71 71 71 71 71 72</b>              |

| Docui<br>U<br>Errata<br>P<br>E<br>E<br>Docui<br>Sales           | ment Conventions  nits of Measure  art Numbers Affected  Z-USB FX1 Qualification Status  Z-USB FX1 Errata Summary  ment History Page  , Solutions, and Legal Information                                                              | <b>7071</b> 717171 <b>72</b>             |

| Docui<br>U<br>Errata<br>P<br>E<br>E<br>Docui<br>Sales           | ment Conventions  nits of Measure  art Numbers Affected  Z-USB FX1 Qualification Status  Z-USB FX1 Errata Summary  ment History Page  , Solutions, and Legal Information  /orldwide Sales and Design Support                          | <b>7071</b> 717171 <b>7274</b>           |

| Docui<br>U<br>Errata<br>P<br>E<br>E<br>Docui<br>Sales           | ment Conventions  nits of Measure  art Numbers Affected  Z-USB FX1 Qualification Status  Z-USB FX1 Errata Summary  ment History Page  , Solutions, and Legal Information  /orldwide Sales and Design Support  roducts                 | <b>70</b> 70 71 71 71 <b>72</b> 74 74    |

| Docui<br>U<br>Errata<br>P<br>E<br>E<br>Docui<br>Sales<br>W<br>P | ment Conventions  nits of Measure  art Numbers Affected  Z-USB FX1 Qualification Status  Z-USB FX1 Errata Summary  ment History Page  , Solutions, and Legal Information  /orldwide Sales and Design Support  roducts  SoC® Solutions | <b>70</b> 70 71 71 <b>72 74</b> 74 74    |

| Docui<br>Errata<br>P<br>E<br>E<br>Docui<br>Sales<br>W<br>P      | ment Conventions  nits of Measure  art Numbers Affected  Z-USB FX1 Qualification Status  Z-USB FX1 Errata Summary  ment History Page  , Solutions, and Legal Information  /orldwide Sales and Design Support  roducts                 | <b>70</b> 71 71 71 <b>72 74</b> 74 74 74 |

#### **Functional Description**

EZ-USB FX1™ (CY7C64713) is a full speed, highly integrated, USB microcontroller. By integrating the USB transceiver, Serial Interface Engine (SIE), enhanced 8051 microcontroller, and a programmable peripheral interface in a single chip, Cypress has created a very cost effective solution that provides superior time-to-market advantages.

The EZ-USB FX1 is more economical, because it incorporates the USB transceiver and provides a smaller footprint solution than the USB SIE or external transceiver implementations. With EZ-USB FX1, the Cypress Smart SIE handles most of the USB protocol in hardware, freeing the embedded microcontroller for application specific functions and decreasing the development time to ensure USB compatibility.

The General Programmable Interface (GPIF) and Master/Slave Endpoint FIFO (8 or 16-bit data bus) provide an easy and glueless interface to popular interfaces such as ATA, UTOPIA, EPP, PCMCIA, and most DSP/processors.

Four Pb-free packages are defined for the family: 56-pin SSOP, 56-pin QFN, 100-pin TQFP, and 128-pin TQFP.

#### **Applications**

- DSL modems

- ATA interface

- Memory card readers

- Legacy conversion devices

- Home PNA

- Wireless LAN

- MP3 players

- Networking

The Reference Designs section of the cypress website provides additional tools for typical USB applications. Each reference design comes complete with firmware source and object code, schematics, and documentation. Please visit <a href="http://www.cypress.com">http://www.cypress.com</a> for more information.

#### **Functional Overview**

#### **USB Signaling Speed**

FX1 operates at one of the three rates defined in the USB Specification Revision 2.0, dated April 27, 2000:

Full speed, with a signaling bit rate of 12 Mbps.

FX1 does not support the low speed signaling mode of 1.5 Mbps or the high speed mode of 480 Mbps.

#### 8051 Microprocessor

The 8051 microprocessor embedded in the FX1 family has 256 bytes of register RAM, an expanded interrupt system, three timer/counters, and two USARTs.

#### 8051 Clock Frequency

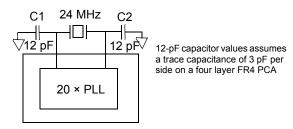

FX1 has an on-chip oscillator circuit that uses an external 24 MHz (±100 ppm) crystal with the following characteristics:

- Parallel resonant

- Fundamental mode

- 500 µW drive level

- 12 pF (5% tolerance) load capacitors.

An on-chip PLL multiplies the 24 MHz oscillator up to 480 MHz, as required by the transceiver/PHY, and the internal counters divide it down for use as the 8051 clock. The default 8051 clock frequency is 12 MHz. The clock frequency of the 8051 is dynamically changed by the 8051 through the CPUCS register.

The CLKOUT pin, which is three-stated and inverted using the internal control bits, outputs the 50% duty cycle 8051 clock at the selected 8051 clock frequency which is 48, 24, or 12 MHz.

#### **USARTS**

FX1 contains two standard 8051 USARTs, addressed by Special Function Register (SFR) bits. The USART interface pins are available on separate I/O pins, and are not multiplexed with port pins.

UART0 and UART1 can operate using an internal clock at 230 KBaud with no more than 1% baud rate error. 230 KBaud operation is achieved by an internally derived clock source that generates overflow pulses at the appropriate time. The internal clock adjusts for the 8051 clock rate (48, 24, 12 MHz) such that it always presents the correct frequency for 230-KBaud operation. [1]

#### Special Function Registers

Certain 8051 SFR addresses are populated to provide fast access to critical FX1 functions. These SFR additions are shown in Table 1 on page 5. Bold type indicates non-standard, enhanced 8051 registers. The two SFR rows that end with '0' and '8' contain bit addressable registers. The four I/O ports A–D use the SFR addresses used in the standard 8051 for ports 0–3, which are not implemented in the FX1. Because of the faster and more efficient SFR addressing, the FX1 I/O ports are not addressable in the external RAM space (using the MOVX instruction).

#### Note

1. 115-KBaud operation is also possible by programming the 8051 SMOD0 or SMOD1 bits to a '1' for UART0 and UART1, respectively.

Figure 1. Crystal Configuration

**Table 1. Special Function Registers**

| x | 8x    | 9x        | Ax           | Вх             | Сх     | Dx    | Ex  | Fx  |

|---|-------|-----------|--------------|----------------|--------|-------|-----|-----|

| 0 | IOA   | IOB       | IOC          | IOD            | SCON1  | PSW   | ACC | В   |

| 1 | SP    | EXIF      | INT2CLR      | IOE            | SBUF1  |       |     |     |

| 2 | DPL0  | MPAGE     | INT4CLR      | OEA            |        |       |     |     |

| 3 | DPH0  |           |              | OEB            |        |       |     |     |

| 4 | DPL1  |           |              | OEC            |        |       |     |     |

| 5 | DPH1  |           |              | OED            |        |       |     |     |

| 6 | DPS   |           |              | OEE            |        |       |     |     |

| 7 | PCON  |           |              |                |        |       |     |     |

| 8 | TCON  | SCON0     | IE           | IP             | T2CON  | EICON | EIE | EIP |

| 9 | TMOD  | SBUF0     |              |                |        |       |     |     |

| Α | TL0   | AUTOPTRH1 | EP2468STAT   | EP01STAT       | RCAP2L |       |     |     |

| В | TL1   | AUTOPTRL1 | EP24FIFOFLGS | GPIFTRIG       | RCAP2H |       |     |     |

| С | TH0   | reserved  | EP68FIFOFLGS |                | TL2    |       |     |     |

| D | TH1   | AUTOPTRH2 |              | GPIFSGLDATH    | TH2    |       |     |     |

| Е | CKCON | AUTOPTRL2 |              | GPIFSGLDATLX   |        |       |     |     |

| F |       | reserved  | AUTOPTRSETUP | GPIFSGLDATLNOX | _      |       |     |     |

#### I<sup>2</sup>C Bus

FX1 supports the  $I^2C$  bus as a master only at 100/400 KHz. SCL and SDA pins have open drain outputs and hysteresis inputs. These signals must be pulled up to 3.3 V, even if no  $I^2C$  device is connected.

#### Buses

All packages: 8 or 16-bit 'FIFO' bidirectional data bus, multiplexed on I/O ports B and D. 128-pin package: adds 16-bit output only 8051 address bus, 8-bit bidirectional data bus.

#### **USB Boot Methods**

During the power up sequence, internal logic checks the I<sup>2</sup>C port for the connection of an EEPROM whose first byte is either 0xC0 or 0xC2. If found, it uses the VID/PID/DID values in the EEPROM

in place of the internally stored values (0xC0). Alternatively, it boot-loads the EEPROM contents into an internal RAM (0xC2). If no EEPROM is detected, FX1 enumerates using internally stored descriptors. The default ID values for FX1 are VID/PID/DID (0x04B4, 0x6473, 0xAxxx where xxx=Chip revision). [2]

Table 2. Default ID Values for FX1

| Default VID/PID/DID |        |                                                                          |  |  |

|---------------------|--------|--------------------------------------------------------------------------|--|--|

| Vendor ID           | 0x04B4 | Cypress Semiconductor                                                    |  |  |

| Product ID          | 0x6473 | EZ-USB FX1                                                               |  |  |

| Device release      | 0xAnnn | Depends on chip revision (nnn = chip revision where first silicon = 001) |  |  |

#### Notes

2. The I2C bus SCL and SDA pins must be pulled up, even if an EEPROM is not connected. Otherwise this detection method does not work properly.

# DOCKET

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

### **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

#### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.