# TACHYON User's Manual

HPRC-5000

11,9534

11,9534

12,9534

12,9534

13,9534

14,9534

15,9534

16,9541

TAOSS 4 CHYON FINE CHONG KONG

DEFENDANT'S FRIAL EXHIBIT NO.

**D-84**

No. A 00CA 217 SS

PTI 172419

CROSSROADS EXHIBIT 2016

Oracle Corp. et al v Crossroads Systems, Inc.

IPR2014-01207

## **TACHYON**

User's Manual

HP Manual Part No. 5965-1247E Printed in USA May 1996

First Edition

## **Notice**

## Copyright and Trademark Information

This document contains proprietary information which is protected by copyright. All rights reserved. No part of this document may be photocopied, reproduced, or translated into another language without the prior written consent of Hewlett-Packard Company.

© Hewlett-Packard Company, 1993-1996. All rights reserved.

TACHYON is a trademark of the Hewlett-Packard Company.

Patents are pending for technical information presented in this document.

### Warranty

The information contained in this document is subject to change without notice. Hewlett-Packard makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

## **Print History**

#### **Technical Reference Specification Revisions**

Revision 1.2, December, 1993

Revision 1.4, January, 1994

Revision 1.5, January, 1994

Revision 2.0, April, 1994

Revision 2.1, April 25, 1994

Revision 3.0, July 15, 1994 Revision 4.0, December 16, 1994

Revision 5.0, Draft, April 26, 1995

Revision 5.0, May 25, 1995

#### User's Manual Revisions

1st Draft, August 1, 1995

2nd Draft, December 4, 1995.

3rd Draft, February 14, 1996

1th Draft, May 13, 1996 (Internal Distribution Only)

First Edition, May 27, 1996 (Printed and Bounded)

## Contents

|            | ·                                                                                  |       |

|------------|------------------------------------------------------------------------------------|-------|

| Tables     |                                                                                    | хi    |

|            | ***************************************                                            |       |

|            |                                                                                    |       |

| Pretace    | ,                                                                                  |       |

|            | Tachyon Errata                                                                     | xvii  |

|            | Target Audience                                                                    | vzá   |

|            | Notes, Cautions, and Warnings                                                      | vvii  |

|            | Document Use                                                                       | xvii  |

|            | Chapter Summaries                                                                  | xviii |

| •          | Document Conventions                                                               | XX    |

|            | Related Publications                                                               | ххі   |

|            | Technical Support                                                                  | xxii  |

|            | Homepage                                                                           | xxii  |

| •          | Pricing and Delivery                                                               | xxii  |

|            | Tachyon C Code                                                                     | xxii  |

| 1. Introd  | uction                                                                             | 1     |

| 1.1        | Tachyon Features                                                                   |       |

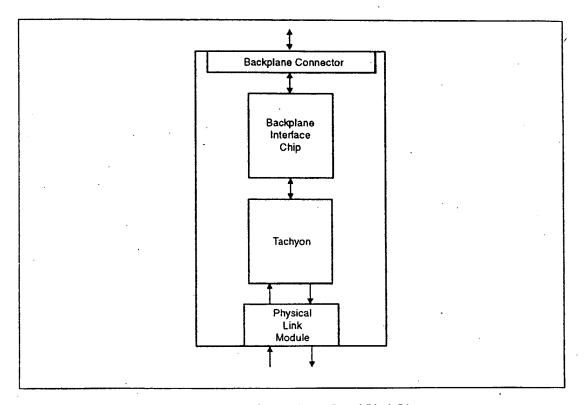

| 1.2        | Host Bus Adapter Board                                                             | 1 2   |

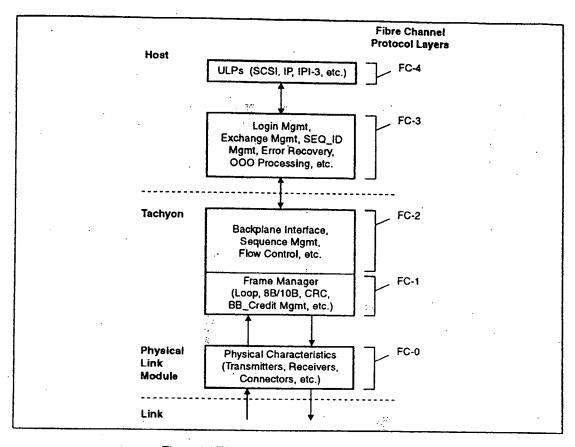

| 1.3        | Fibre Channel General Information                                                  | 3     |

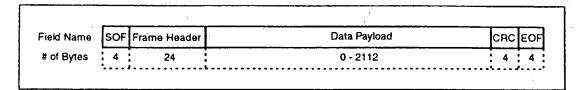

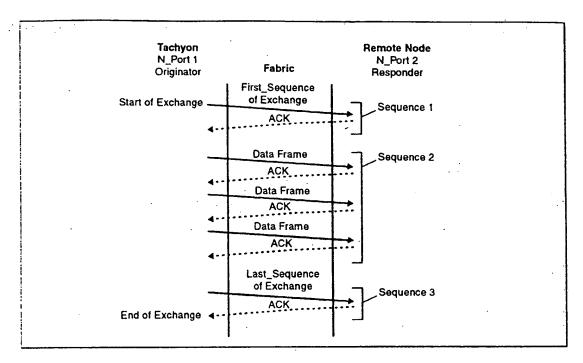

|            | 1.3.1 Fibre Channel Data Hierarchy                                                 | 3     |

|            | 1.3.2 Networking Encapsulation                                                     | 5     |

|            | 1.3.3 Mass Storage Encapsulation                                                   | 6     |

|            | 1.3.4 Fibre Channel Protocol for SCSI                                              | 6     |

|            | 1.3.5 Profile Support                                                              | 7     |

| 2 Archit   | ectural Overview                                                                   |       |

|            |                                                                                    | 9     |

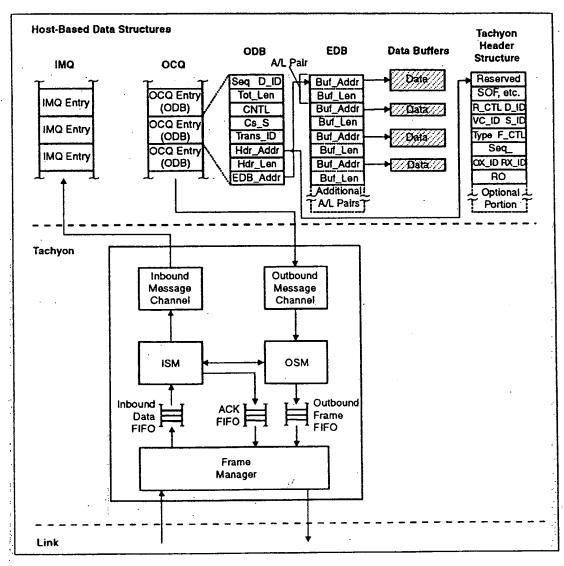

| 2.1        | Transmit Process Overview                                                          | 9     |

| 2.2        | Receive Process Overview                                                           | 11    |

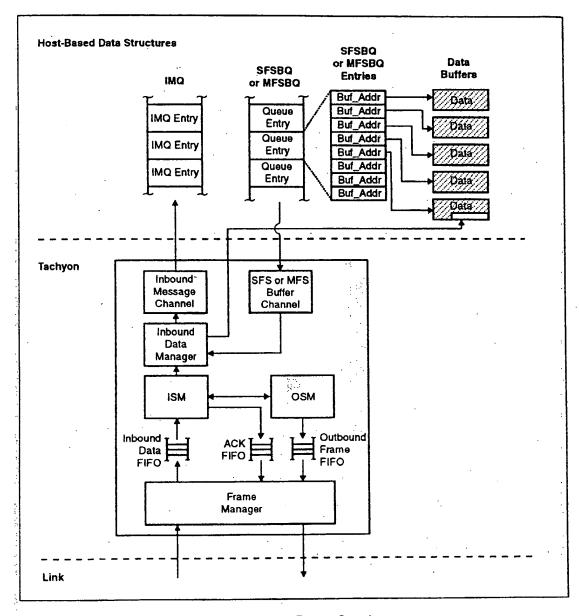

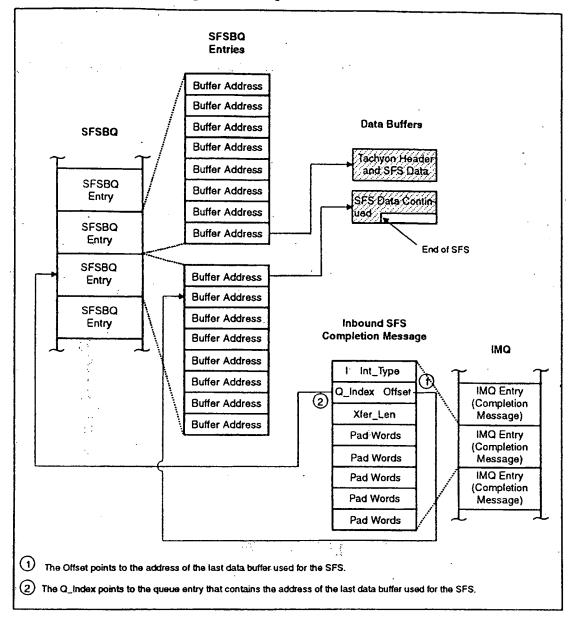

|            | 2.2.1 Single Frame Sequence Reception                                              | 12    |

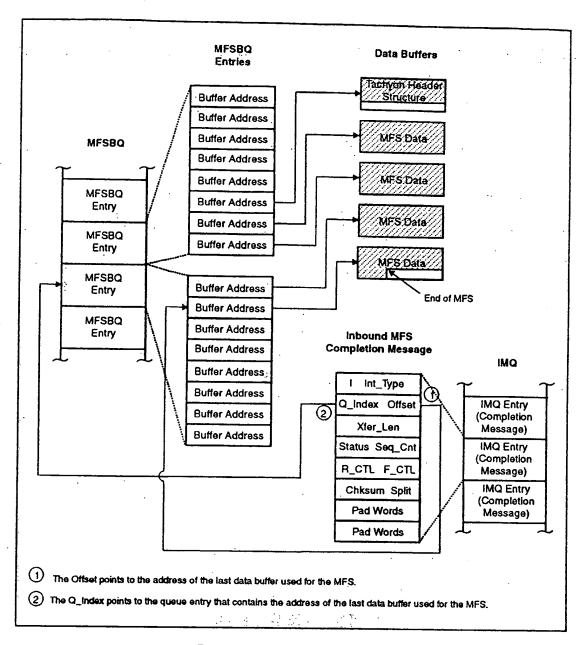

|            | 2.2.2 Multiframe Sequence, In Order Reception                                      | 12    |

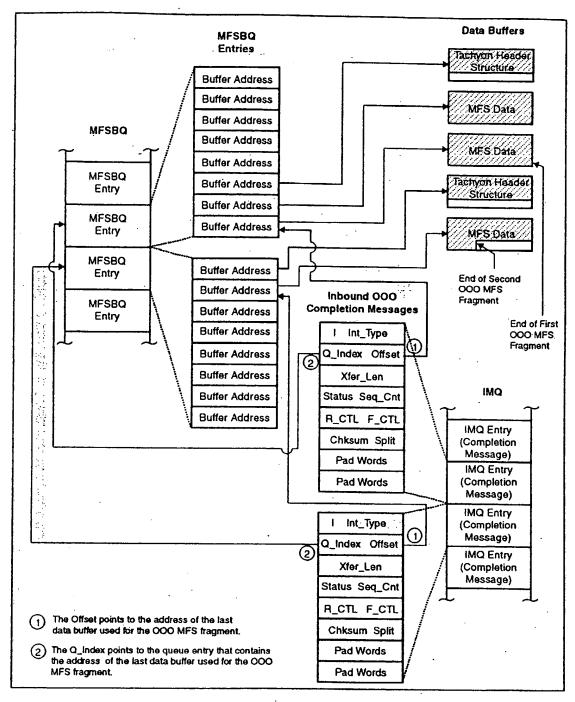

|            | 2.2.3 Multiframe Sequence, Out Of Order (OOO) Reception                            | 13    |

| 2.3        | 2.2.4 Multiframe Sequence, Deferred P_BSY Mode                                     | 13    |

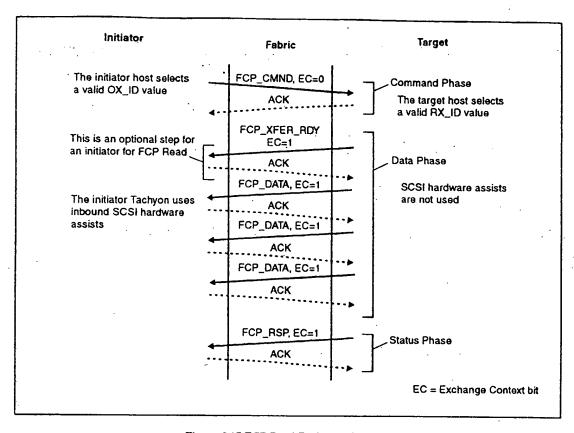

| 2.3        | SCSI Hardware Assists Overview 2.3.1 FCP Read for Tachyon as an Initiator          | 14    |

|            |                                                                                    | 14    |

|            | 2.3.2 FCP Read for Tachyon as a Target 2.3.3 FCP Write for Tachyon as an Initiator | 16    |

|            | 2.3.4 FCP Write for Tachyon as a Target                                            | 16    |

|            | 2.0.4 For write for facilyon as a rarger                                           | 16    |

| 3. Archite | ectural Details                                                                    | 17    |

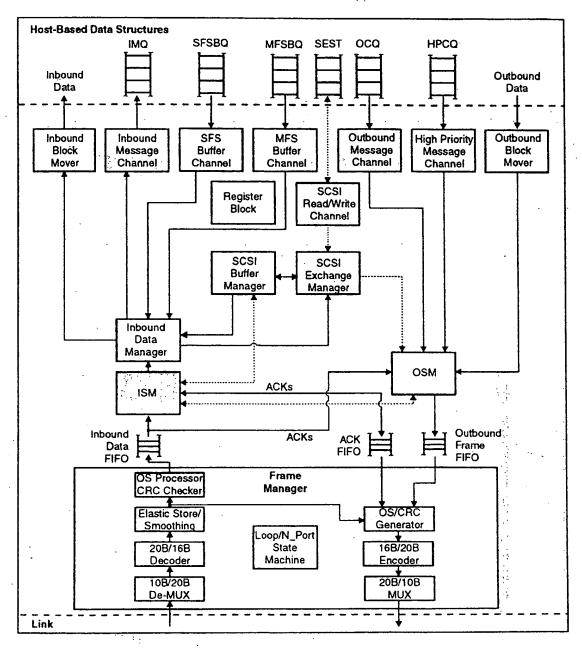

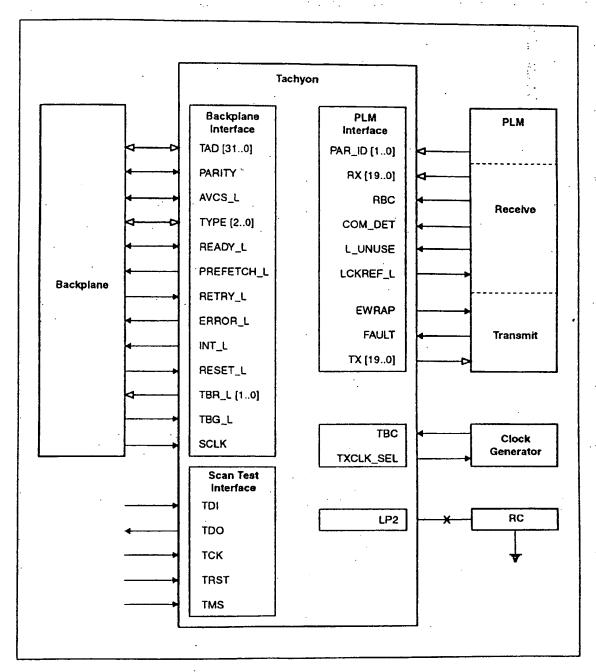

| 3.1        | Tachyon Internal Block Diagram                                                     | 17    |

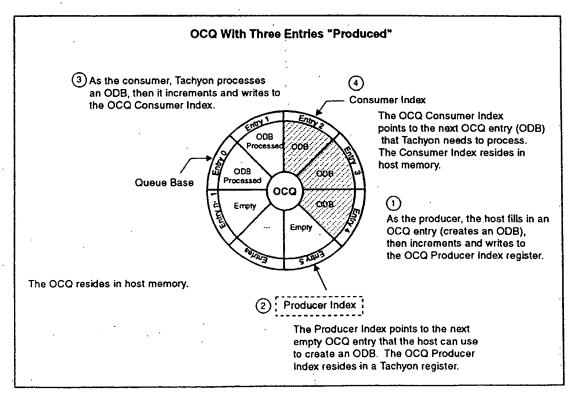

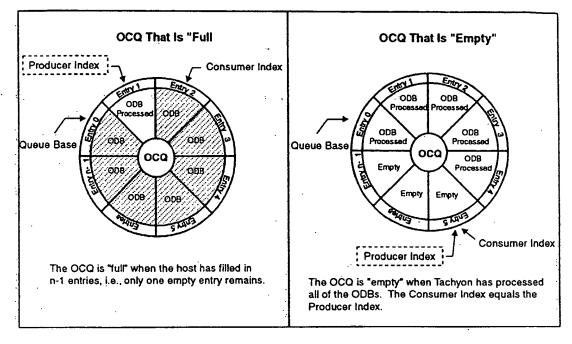

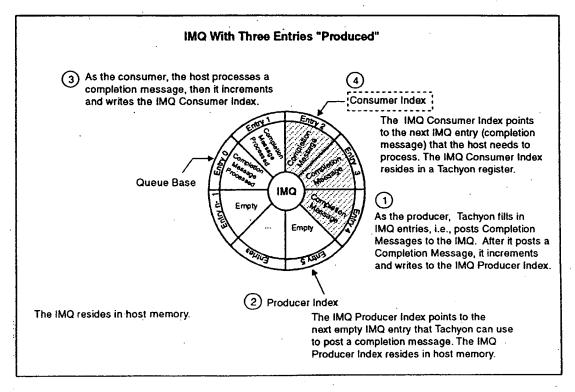

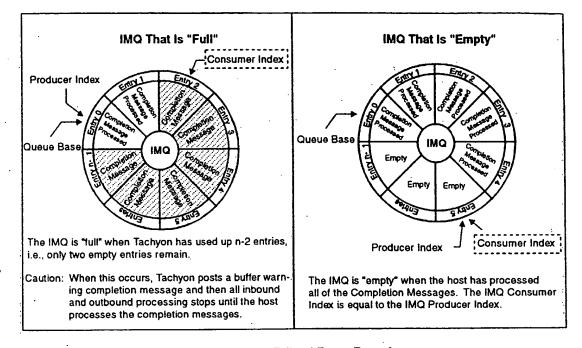

| 3.2        | Circular Queues                                                                    | 18    |

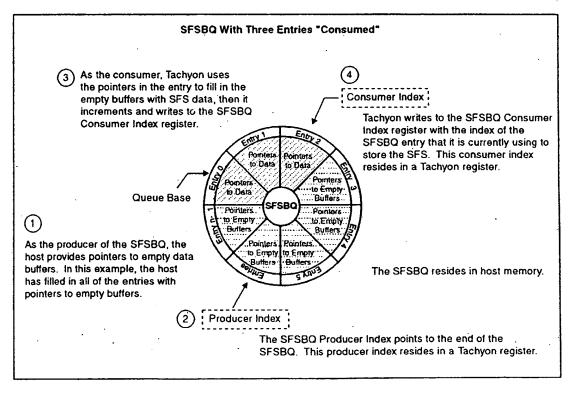

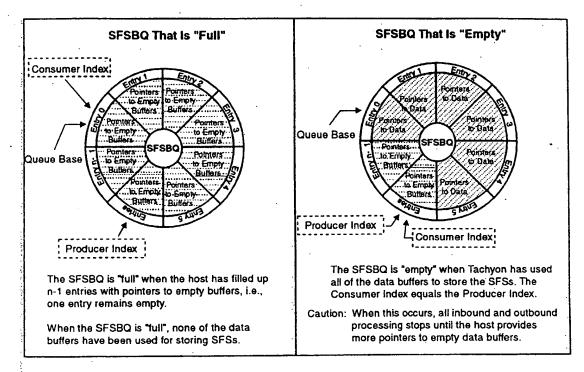

|            | 3.2.1 Overview                                                                     | 18    |

|            | 3.2.2 Producer and Consumer Indices                                                | 19    |

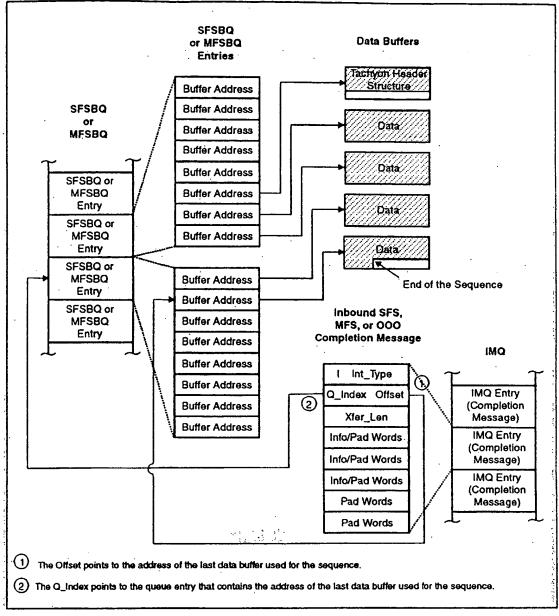

| 3.3        | Completion Messages                                                                | 26    |

|            | 3.3.1 Outbound Completion Messages                                                 | 27    |

|            | 3.3.2 Inbound Completion Messages                                                  | 27    |

|            | 3.3.3 Buffer Warning Completion Messages                                           | 30    |

|       |          | •                                                            |      |

|-------|----------|--------------------------------------------------------------|------|

|       | 3.3.4    | SCSI Completion Messages                                     | 31   |

|       | 3.3.5    | Frame Manager Interrupt Completion Message                   | 32   |

|       |          | Read Status Completion Message (Debugging)                   | 32   |

| N.    |          | Completion Messages with Interrupts                          | 32   |

|       | 3.3.8    | Interrupt Avoidance Techniques                               | 33   |

| 3.4   | Acknow   | rledgements (ACKs)                                           | 34   |

|       | 3.4.1    | Acknowledgement of Transmitted Frames                        | 34   |

|       | 3.4.2    | Acknowledgement of Received Frames                           | 34   |

| 3.5   |          | esponses, Rejects, and ACK Aborts                            | 36   |

|       | 3.5.1    | BSYs, RJTs, and ACK_ABTs of Transmitted Frames               | 36   |

|       | 3.5.2    | Busy (P_BSY) and Reject (P_RJT) Responses of Received Frames | 37   |

| 3.6   |          | it Details                                                   | 38   |

| 0.0   | 3.6.1    | Descriptions for the Transmit Process Blocks                 | 38   |

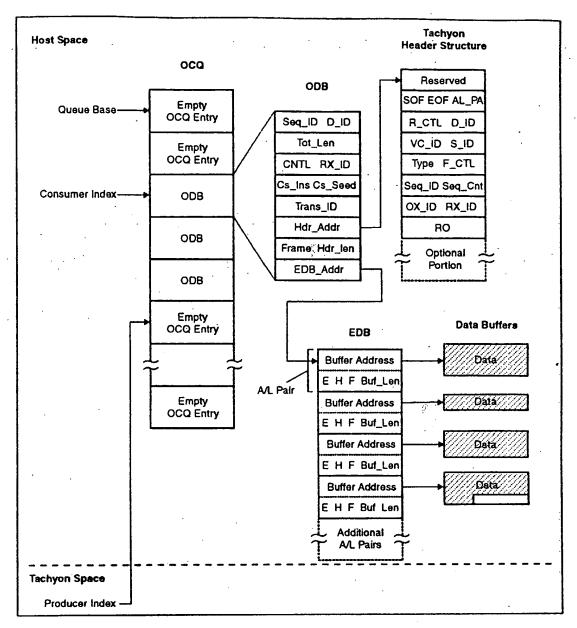

|       | 3.6.2    | Outbound Command Queue Transmit Details                      | 40   |

|       | 3.6.3    | Outbound Class 1 Sequences                                   | 42   |

|       | 3.6.4    | Outbound Class 2 Sequences                                   |      |

|       | 3.6.5    | Outbound Class 3 Sequences                                   | 44   |

|       | 3.6.6    | Transmitting L_Port Open Broadcast Replicate Frames          | 44   |

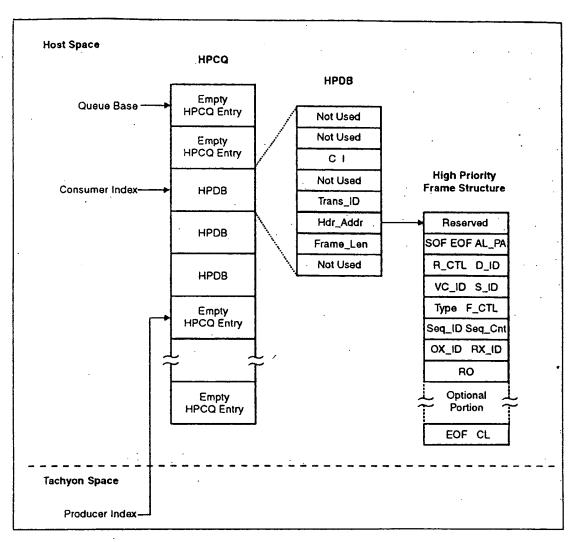

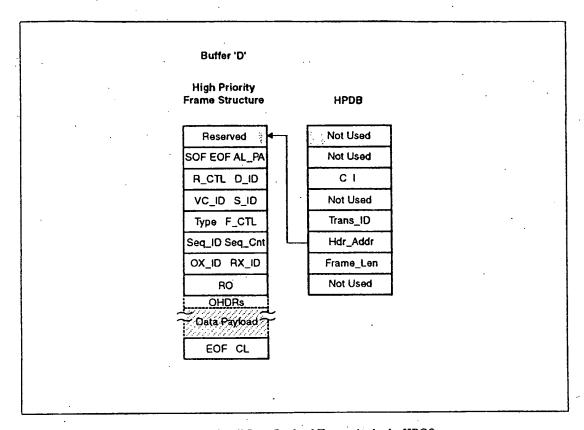

|       | 3.6.7    | High Priority Command Queue Transmit Details                 | 45   |

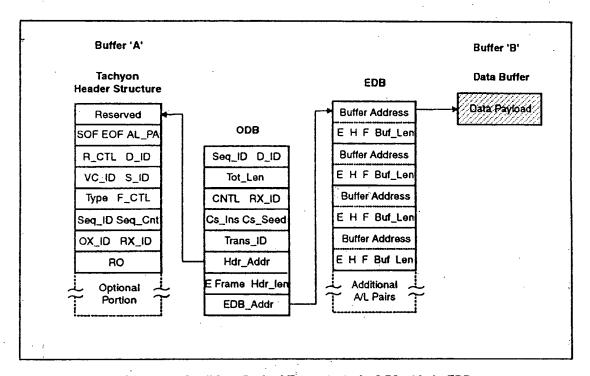

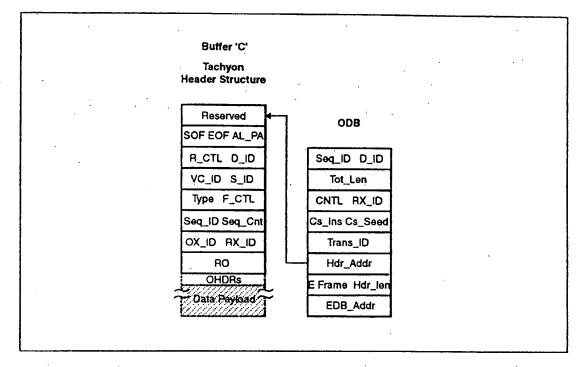

|       | 3.6.8    | Small Data Payload Transmit Processes                        |      |

|       | 3.6.9    | Recommended Transmit Methods                                 | 50   |

| 0.7   |          | SI Receive Details                                           | 51   |

| 3.7   | 3.7.1    | Descriptions for the Receive Process Blocks                  | 51   |

|       |          | Single Frame Sequence Reception                              | 55   |

|       | 3.7.2    | Multiframe Sequence, In Order Reception                      | 57   |

|       | 3.7.3    | Multiframe Sequence, Out of Order (OOO) Reception            | 59   |

|       | 3.7.4    | Multirame Sequence, Out of Order (OOO) reception             | 60   |

|       | 3.7.5    | Multiframe Sequence, Deferred P_BSY Mode                     | 61   |

|       | 3.7.6    | Expiration/Security Header Frame Reception                   | 61   |

|       | 3:7.7    | Open Broadcast Replicate Reception                           | 62   |

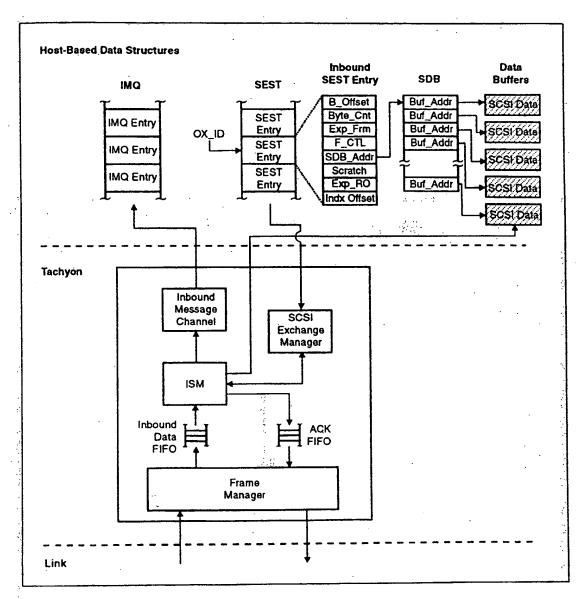

| . 3.8 |          | ardware Assists Details                                      | 62   |

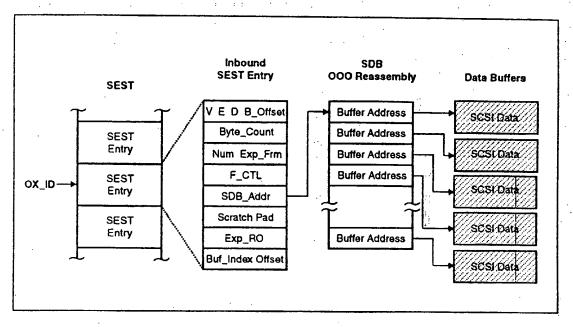

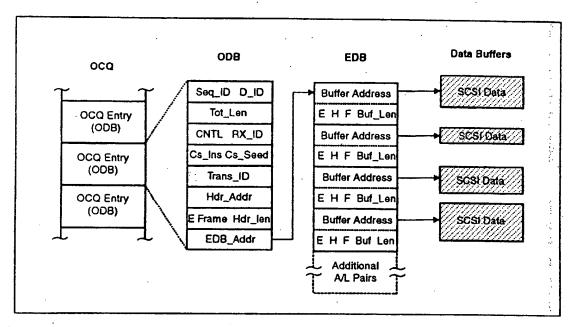

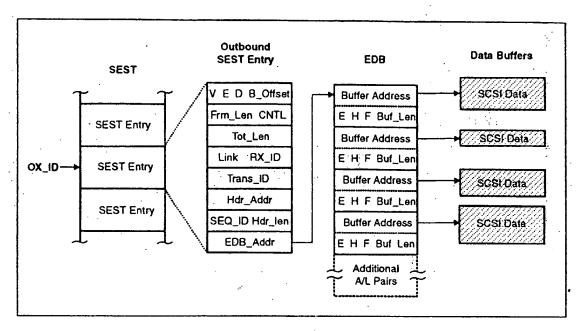

|       | 3.8.1    | Descriptions for the SCSI Hardware Assists Blocks            | 63   |

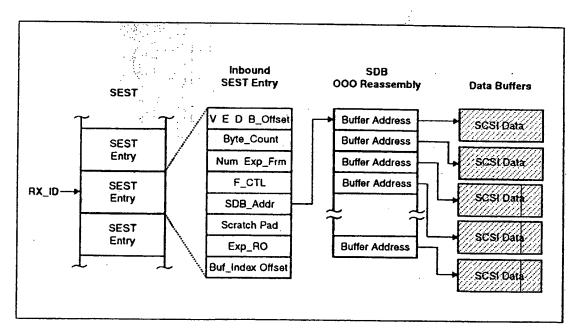

|       | 3.8.2    | SCSI Exchange State Table (SEST)                             | 64   |

|       | 3.8.3    | Invalidating and Re-Using Outbound SEST Entries              | 65   |

|       | 3.8.4    | Invalidating and Re-Using Inbound SEST Entries               | . 66 |

|       | 3.8.5    | SCSI Exception Processing in Tachyon                         | . 67 |

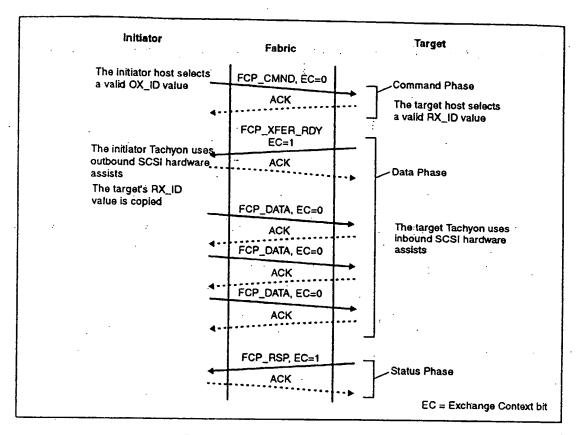

|       | 3.8.6    | FCP Read Exchange Example                                    |      |

|       | 3.8.7    | FCP Read Exchange, OOO Reassembly - Initiator Tachyon        | . 70 |

|       | 3.8.8    | FCP Read Exchange, In Order Reassembly - Initiator Tachyon   | . 72 |

|       | 3.8.9    | FCP Read Exchange - Target Tachyon                           | 74   |

|       | 3.8.10   | FCP Write Exchange Example                                   |      |

|       | : 3.8.11 | FCP Write Exchange - Initiator Tachyon                       | 13   |

|       | 3.8.12   | FCP Write, OOO Reassembly - Target Tachyon                   | 79   |

|       | 3.8.13   | FCP Write Exchange, In Order Reassembly - Target Tachyon     |      |

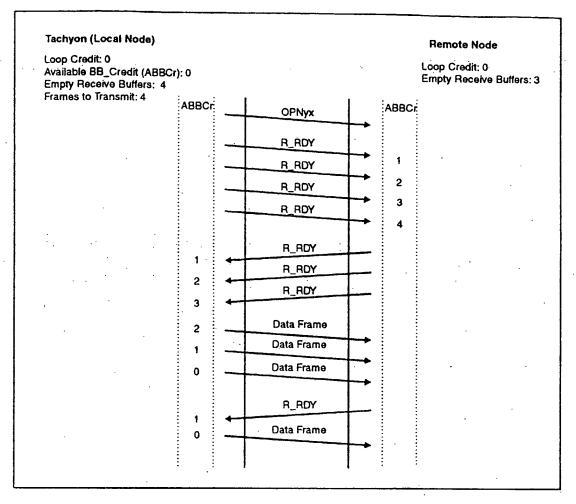

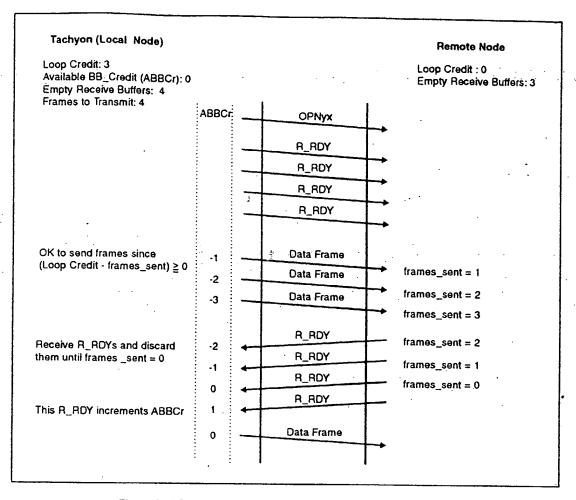

| 3.9   | Loop D   | Details                                                      | 81   |

|       | 3.9.1    | FC-AL Specification Deviations                               | . 81 |

|       | 3.9.2    | Power-On                                                     | 81   |

|       | 3.9.3    | Online                                                       | . 81 |

|       | 3.9.4    | Initialization                                               | 82   |

|       | 3.9.5    | Loop Situations After Initialization                         | . 83 |

|       | 3.9.6    | Opening a Device                                             | . 83 |

|       | 3.9.7    | Open Broadcast Replicate Support                             | . 80 |

|       | 3.9.8    | Open Selective Replicate (Multicast)                         | . 80 |

|       | 3.9.9    | TDANSFFR (XFFR) State                                        | . 01 |

|       | 3 9 10   |                                                              | . 87 |

First Edition

|                          | 0.011 Hoom common c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                   |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                          | 3.9.11 HOST CONTROL State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88                                                                                                                                |

|                          | 3.9.12 Programming the Frame Manager OFFLINE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 89                                                                                                                                |

|                          | 3.9.13 Programming the Frame Manager OFFLINE if in LOOP_FAIL State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 89                                                                                                                                |

|                          | 3.9.14 Determining the Link State of Tachyon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 89                                                                                                                                |

|                          | 3.9.15 Fabric Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                   |

|                          | 3.9.16 Loop Operation While Impersonating a Fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 90                                                                                                                                |

| 3.10                     | TCD/IDD Undergrow A solve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91                                                                                                                                |

| 3.10                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 92                                                                                                                                |

|                          | 3.10.1 Checksumming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 92                                                                                                                                |

|                          | 3.10.2 Outbound Checksum Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 92                                                                                                                                |

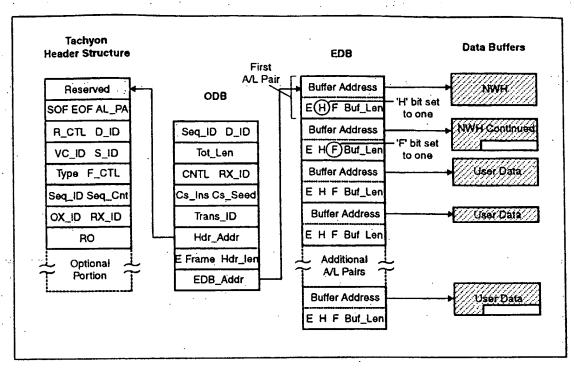

|                          | 3.10.3 Header/Data Splitting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 94                                                                                                                                |

| 3.11                     | Network Management Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 95                                                                                                                                |

|                          | lization and Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97                                                                                                                                |

| 4.1                      | Estimate Memory Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| 4.1                      | 4.1.1 Static Memory Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97                                                                                                                                |

|                          | The state of the s | 97                                                                                                                                |

|                          | 4.1.2 Dynamic Memory Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 98                                                                                                                                |

| 4.2                      | Initialize Tachyon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 99                                                                                                                                |

| 4.3                      | Program the Tachyon Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 99                                                                                                                                |

| 4.4                      | Build Data Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100                                                                                                                               |

| 4.5                      | Initialize the Frame Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 102                                                                                                                               |

|                          | 4.5.1 Determine the Link State of Tachyon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

| 4.6                      | The state of the control of the cont | 103                                                                                                                               |

|                          | Tachyon Configuration Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 104                                                                                                                               |

| 4.7                      | Testing Tachyon's Functionality Incrementally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 107                                                                                                                               |

| 4.8                      | Loopback Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 108                                                                                                                               |

|                          | 4.8.1 Loopback Intialization Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108                                                                                                                               |

| 4.9                      | Login Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   |

|                          | 4.9.1 Fabric Login Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100                                                                                                                               |

|                          | 4.9.2 N Port Login Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 103                                                                                                                               |