# intel.

## 8254 PROGRAMMABLE INTERVAL TIMER

- Compatible with All Intel and Most **Other Microprocessors**

- Handles Inputs from DC to 10 MHz

- 5 MHz 8254-5

- 8 MHz 8254

- 10 MHz 8254-2

- Status Read-Back Command

- Six Programmable Counter Modes

- Three Independent 16-Bit Counters

Dy [

De C 2

Ds 3

04 4

D3 0 5

01 07

Do C S

CLKOD 9

OUT 0 10

GATE O 11 GND C 12

02 6 8254 24 Vcc

23 WR

22 30

21 CS

20 A1 19 0 A0

17 0012

18 GATE 2

15 CLK 1

14 GATE 1

13 0UT 1 231164-2

Figure 2. Pin Configuration

- **Binary or BCD Counting**

- Single +5V Supply 1940

- Available in EXPRESS — Standard Temperature Range

The Intel® 8254 is a counter/timer device designed to solve the common timing control problems in microcomputer system design. It provides three independent 16-bit counters, each capable of handling clock inputs up to 10 MHz. All modes are software programmable. The 8254 is a superset of the 8253.

The 8254 uses HMOS technology and comes in a 24-pin plastic or CERDIP package.

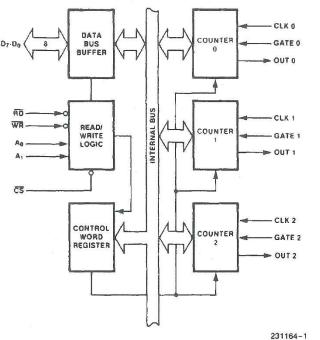

Figure 1. 8254 Block Diagram

Be sure to visit ChipDocs web site for more information. www.chipdocs.com

8254

| Symbol                          | Pin<br>No. | Туре | Table 1. Pin Description Name and Function                                                                                                                       |                                                              |  |

|---------------------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| D7-D0                           | 1-8        | 1/0  | DATA: Bi-directional three state data bus lines, connected to system data bus.                                                                                   |                                                              |  |

| CLK 0                           | 9          | 1    | CLOCK 0: Clock input of Counter 0.                                                                                                                               |                                                              |  |

| OUT 0                           | 10         | 0    | OUTPUT 0: Output of Counter 0.                                                                                                                                   |                                                              |  |

| GATE 0                          | 11         | l    | GATE 0: Gate input of Counter 0.                                                                                                                                 |                                                              |  |

| GND                             | 12         |      | GROUND: Power supply connection.                                                                                                                                 |                                                              |  |

| Vcc                             | 24         |      | POWER: + 5V power supply connection.                                                                                                                             |                                                              |  |

| WR                              | 23         | I    | WRITE CONTROL: This input is low during CPU write operations.                                                                                                    |                                                              |  |

| RD                              | 22         | 1    | READ CONTROL: This input is low during CPU read operations.                                                                                                      |                                                              |  |

| CS                              | 21         | I    | CHIP SELECT: A low on this input enables the 8254 to respond to RD and WR signals. RD and WR are ignored otherwise.                                              |                                                              |  |

| A <sub>1</sub> , A <sub>0</sub> | 2019       | I    | ADDRESS: Used to select one of the three Counters or the Control<br>Word Register for read or write operations. Normally connected to<br>the system address bus. |                                                              |  |

|                                 |            |      | A <sub>1</sub> A <sub>0</sub>                                                                                                                                    | Selects                                                      |  |

|                                 |            |      | 0 0<br>0 1<br>1 0<br>1 1                                                                                                                                         | Counter 0<br>Counter 1<br>Counter 2<br>Control Word Register |  |

| CLK 2                           | 18         | 1    | CLOCK 2: Clock input of Counter 2.                                                                                                                               |                                                              |  |

| OUT 2                           | 17         | 0    | OUT 2: Output of Counter 2.                                                                                                                                      |                                                              |  |

| GATE 2                          | 16         | 1    | GATE 2: Gate input of Counter 2.                                                                                                                                 |                                                              |  |

| CLK 1                           | 15         | 1 .  | CLOCK 1: Clock input of Counter 1.                                                                                                                               |                                                              |  |

| GATE 1                          | 14         | 1    | GATE 1: Gate input of Counter 1.                                                                                                                                 |                                                              |  |

| OUT 1                           | 13         | 0    | OUT 1: Output of Counter 1.                                                                                                                                      |                                                              |  |

#### FUNCTIONAL DESCRIPTION

#### General

The 8254 is a programmable interval timer/counter designed for use with Intel microcomputer systems. It is a general purpose, multi-timing element that can be treated as an array of I/O ports in the system software.

The 8254 solves one of the most common problems in any microcomputer system, the generation of accurate time delays under software control. Instead of setting up timing loops in software, the programmer configures the 8254 to match his requirements and programs one of the counters for the desired delay. After the desired delay, the 8254 will interrupt the CPU. Software overhead is minimal and variable length delays can easily be accommodated. Some of the other counter/timer functions common to microcomputers which can be implemented with the 8254 are:

- Real time clock

- Event-counter

- Digital one-shot

- Programmable rate generator

- Square wave generator

- Binary rate multiplier

- Complex waveform generator

- · Complex motor controller

#### **Block Diagram**

#### DATA BUS BUFFER

This 3-state, bi-directional, 8-bit buffer is used to interface the 8254 to the system bus (see Figure 3).

#### 3-63

www.chipdocs.com

Be sure to visit ChipDocs web site for more information.

intel.

8254

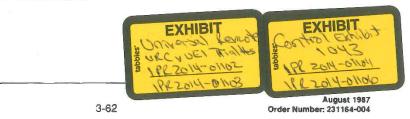

Figure 3. Block Diagram Showing Data Bus Buffer and Read/Write Logic Functions

#### **READ/WRITE LOGIC**

The Read/Write Logic accepts inputs from the system bus and generates control signals for the other functional blocks of the 8254. A<sub>1</sub> and A<sub>0</sub> select one of the three counters or the Control Word Register to be read from/written into. A "low" on the  $\overline{RD}$  input tells the 8254 that the CPU is reading one of the counters. A "low" on the  $\overline{WR}$  input tells the 8254 that the CPU is writing either a Control Word or an initial count. Both  $\overline{RD}$  and  $\overline{WR}$  are ignored unless the 8254 has been selected by holding  $\overline{CS}$  low.

#### CONTROL WORD REGISTER

The Control Word Register (see Figure 4) is selected by the Read/Write Logic when  $A_1, A_0 = 11$ . If the CPU then does a write operation to the 8254, the data is stored in the Control Word Register and is interpreted as a Control Word used to define the operation of the Counters.

The Control Word Register can only be written to; status information is available with the Read-Back Command.

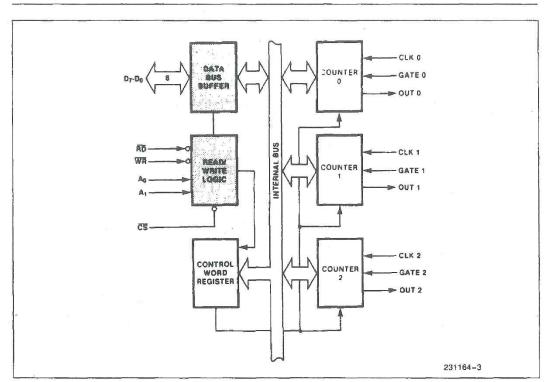

#### **COUNTER 0, COUNTER 1, COUNTER 2**

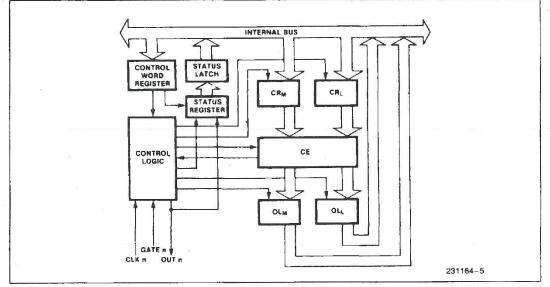

These three functional blocks are identical in operation, so only a single Counter will be described. The internal block diagram of a single counter is shown in Figure 5.

The Counters are fully independent. Each Counter may operate in a different Mode.

The Control Word Register is shown in the figure; it is not part of the Counter itself, but its contents determine how the Counter operates.

The status register, shown in Figure 5, when latched, contains the current contents of the Control Word Register and status of the output and null count flag. (See detailed explanation of the Read-Back command.)

The actual counter is labelled CE (for "Counting Element"). It is a 16-bit presettable synchronous down counter.

$OL_M$  and  $OL_L$  are two 8-bit latches. OL stands for "Output Latch"; the subscripts M and L stand for "Most significant byte" and "Least significant byte"

3-64

www.chipdocs.com

Be sure to visit ChipDocs web site for more information.

intപ്ര.

8254

Figure 4. Block Diagram Showing Control Word Register and Counter Functions

Figure 5. Internal Block Diagram of a Counter

3-65

www.chipdocs.com

R

Μ

Δ

D

Δ

)

Be sure to visit ChipDocs web site for more information.

respectively. Both are normally referred to as one unit and called just OL. These latches normally "follow" the CE, but if a suitable Counter Latch Command is sent to the 8254, the latches "latch" the present count until read by the CPU and then return to "following" the CE. One latch at a time is enabled by the counter's Control Logic to drive the internal bus. This is how the 16-bit Counter communicates over the 8-bit internal bus. Note that the CE itself cannot be read; whenever you read the count, it is the OL that is being read.

Similarly, there are two 8-bit registers called  $CR_M$  and  $CR_L$  (for "Count Register"). Both are normally referred to as one unit and called just CR. When a new count is written to the Counter, the count is stored in the CR and later transferred to the CE. The Control Logic allows one register at a time to be loaded from the internal bus. Both bytes are transferred to the CE simultaneously.  $CR_M$  and  $CR_L$  are cleared when the Counter is programmed. In this way, if the Counter has been programmed for one byte counts (either most significant byte only or least significant byte only) the other byte will be zero. Note that the CE cannot be written into; whenever a count is written, it is written into the CR.

The Control Logic is also shown in the diagram. CLK n, GATE n, and OUT n are all connected to the outside world through the Control Logic.

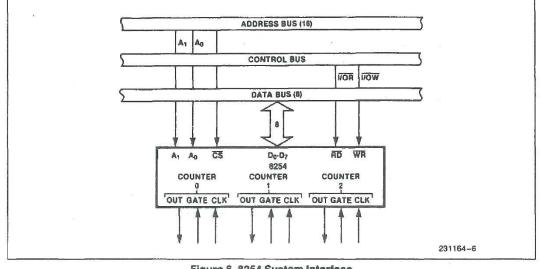

#### **8254 SYSTEM INTERFACE**

The 8254 is a component of the Intel Microcomputer Systems and interfaces in the same manner as all other peripherals of the family. It is treated by the system's software as an array of peripheral I/O ports; three are counters and the fourth is a control register for MODE programming.

Basically, the select inputs  $A_0, A_1$  connect to the  $A_0$ ,  $A_1$  address bus signals of the CPU. The CS can be derived directly from the address bus using a linear select method. Or it can be connected to the output of a decoder, such as an Intel 8205 for larger systems.

#### **OPERATIONAL DESCRIPTION**

#### General

After power-up, the state of the 8254 is undefined. The Mode, count value, and output of all Counters are undefined.

How each Counter operates is determined when it is programmed. Each Counter must be programmed before it can be used. Unused counters need not be programmed.

#### Programming the 8254

Counters are programmed by writing a Control Word and then an initial count.

The Control Words are written into the Control Word Register, which is selected when  $A_1,A_0 = 11$ . The Control Word itself specifies which Counter is being programmed.

Figure 6. 8254 System Interface

3-66

www.chipdocs.com

Be sure to visit ChipDocs web site for more information.

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

## LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

## FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

## E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.