# RELIABLE COMPUTER SYSTEMS

# **DESIGN AND EVALUATION**

SECOND EDITION

DANIEL P. SIEWIOREK ROBERT S. SWARZ

Copyright © 1992 by Digital Equipment Corporation.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without prior written permission of the publisher.

Printed in the United States of America. 987654321

Order number EY-H880E-DP

The Publisher offers discounts on bulk orders of this book. For information, please write:

Special Sales Department Digital Press One Burlington Woods Drive Burlington, MA 01003

Design: Outside Designs Production: Technical Texts Composition: DEKR Corporation Printer: Arcata/Halliday

Trademark products mentioned in this book are listed on page 890.

Views expressed in this book are those of the authors, not of the publisher. Digital Equipment Corporation is not responsible for any errors that may appear in this book.

#### Library of Congress Cataloging-in-Publication Data

Siewiorek, Daniel P.

Reliable computer systems : design and evaluation / Daniel P.

Siewiorek, Robert S. Swarz. — 2nd ed.

p. cm.

Rev. ed. of: The theory and practice of reliable system design.

Bedford, MA : Digital Press, c1982.

Includes bibliographical references and index.

ISBN 1-55558-075-0

1. Electronic digital computers—Reliability. 2. Fault-tolerant

computing. I. Swarz, Robert S. II. Siewiorek, Daniel P. Theory

and practice of reliable system design. III. Title.

QA76.5.5537 1992

004-dc20

92-10671

CIP

#### CREDITS

Figure 1–3: Eugene Foley, "The Effects of Microelectronics Revolution on Systems and Board Test," Computers, Vol. 12, No. 10 (October 1979). Copyright © 1979 IEEE. Reprinted by permission.

Figure 1-6: S. Russell Craig, "Incoming Inspection and Test Programs," Electronics Test (October 1980). Reprinted by permission.

Credits are continued on p. 885, which is considered a continuation of the copyright page.

# To Karon and Lonnie

# A Special Remembrance:

During the development of this book, a friend, colleague, and fault-tolerant pioneer passed away. Dr. Wing N. Toy documented his 37 years of experience in designing several generations of fault-tolerant computers for the Bell System electronic switching systems described in Chapter 8. We dedicate this book to Dr. Toy in the confidence that his writings will continue to influence designs produced by those who learn from these pages.

Preface xv

# I THE THEORY OF RELIABLE SYSTEM DESIGN

### I FUNDAMENTAL CONCEPTS 3

Physical Levels in a Digital System 5 Temporal Stages of a Digital System 6 Cost of a Digital System 18 Summary 21 References 21

# 2 FAULTS AND THEIR MANIFESTATIONS 22

System Errors 24 Fault Manifestations 31 Fault Distributions 49 Distribution Models for Permanent Faults: The MIL-HDBK-217 Model 57 Distribution Models for Intermittent and Transient Faults 65 Software Fault Models 73 Summary 76 References 76 Problems 77

1

#### 3 RELIABILITY TECHNIQUES 79 Steven A. Elkind and Daniel P. Siewiorek

System-Failure Response Stages 80 Hardware Fault-Avoidance Techniques 84 Hardware Fault-Detection Techniques 96 Hardware Masking Redundancy Techniques 138 Hardware Dynamic Redundancy Techniques 169 Software Reliability Techniques 201 Summary 219 References 219 Problems 221

# 4 MAINTAINABILITY AND TESTING TECHNIQUES 228

Specification-Based Diagnosis 229 Symptom-Based Diagnosis 260

Summary 268 References 268 Problems 269

#### 5 EVALUATION CRITERIA 271 Stephen McConnel and Daniel P. Siewiorek

Stephen Meedinier and Danier 1. Siewidrek

Introduction 271 Survey of Evaluation Criteria: Hardware 272 Survey of Evaluation Criteria: Software 279 Reliability Modeling Techniques: Combinatorial Models 285 Examples of Combinatorial Modeling 294 Reliability and Availability Modeling Techniques: Markov Models 305 Examples of Markov Modeling 334 Availability Modeling Techniques 342 Software Assistance for Modeling Techniques 349 Applications of Modeling Techniques to Systems Designs 356 Summary 391 References 391 Problems 392

#### 6 FINANCIAL CONSIDERATIONS 402

Fundamental Concepts 402 Cost Models 408 Summary 419 References 419 Problems 420

# II THE PRACTICE OF RELIABLE SYSTEM DESIGN 423

Fundamental Concepts 402 General-Purpose Computing 424 High-Availability Systems 424 Long-Life Systems 425 Critical Computations 425

#### 7 GENERAL-PURPOSE COMPUTING 427

Introduction 427 Generic Computer 427 DEC 430 IBM 431

The DEC Case: RAMP in the VAX Family 433 Daniel P. Siewiorek

The VAX Architecture 433 First-Generation VAX Implementations 439 Second-Generation VAX Implementations 455 References 484

The IBM Case Part I: Reliability, Availability, and Serviceability in IBM 308X and IBM 3090 Processor Complexes 485 Daniel P. Siewiorek ix

Technology 485 Manufacturing 486 Overview of the 3090 Processor Complex 493 References 507

The IBM Case Part II: Recovery Through Programming: MVS Recovery Management 508

C.T. Connolly Introduction 508 RAS Objectives 509 Overview of Recovery Management 509 MVS/XA Hardware Error Recovery 511 MVS/XA Serviceability Facilities 520 Availability 522 Summary 523 Bibliography 523 Reference 523

#### 8 HIGH-AVAILABILITY SYSTEMS 524

Introduction 524 AT&T Switching Systems 524 Tandem Computers, Inc. 528 Stratus Computers, Inc. 531 References 533

The AT&T Case Part 1: Fault-Tolerant Design of AT&T Telephone Switching System Processors 533

6

W.N. Toy

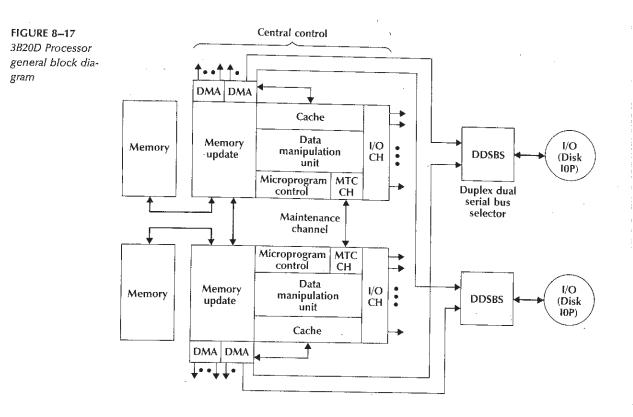

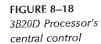

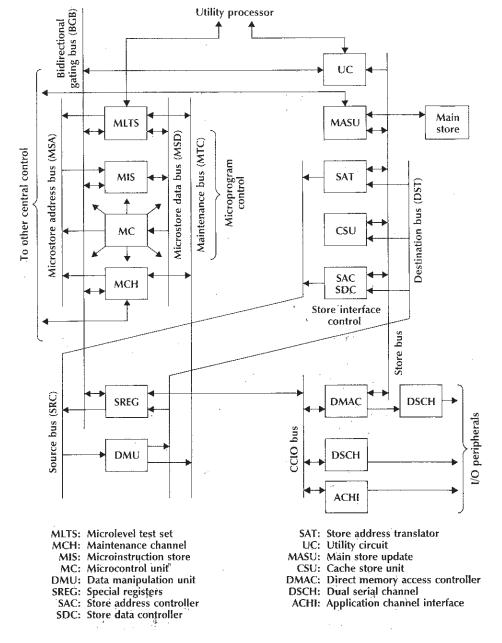

Introduction 533 Allocation and Causes of System Downtime 534 Duplex Architecture 535 Fault Simulation Techniques 538 First-Generation ESS Processors 540 Second-Generation Processors 544 Third-Generation 3B20D Processor 551 Summary 572 References 573

x

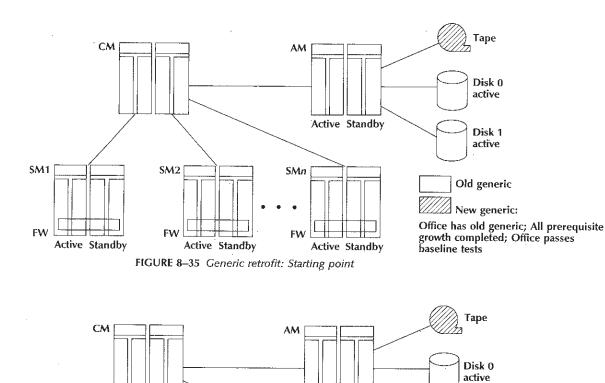

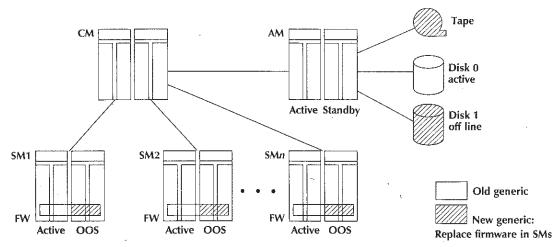

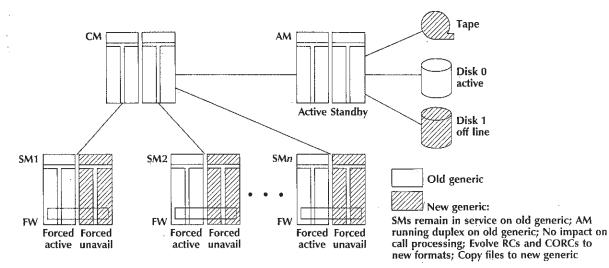

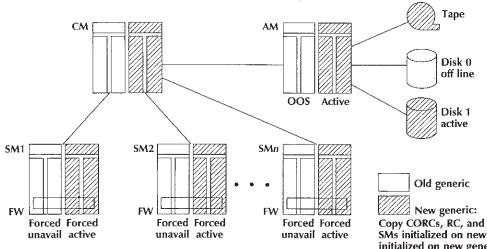

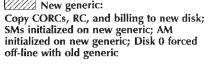

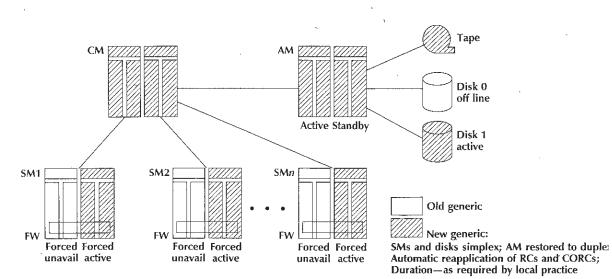

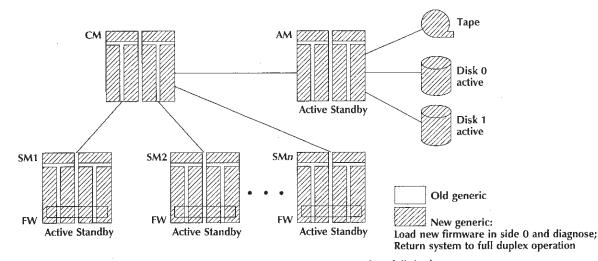

The AT&T Case Part II: Large-Scale Real-Time Program Retrofit Methodology in AT&T 5ESS® Switch 574

L.C. Toy

5ESS Switch Architecture Overview 574 Software Replacement 576 Summary 585 References 586

The Tandem Case: Fault Tolerance in Tandem Computer Systems 586 Joel Bartlett, Wendy Bartlett, Richard Carr, Dave Garcia, Jim Gray, Robert Horst,

Robert Jardine, Doug Jewett, Dan Lenoski, and Dix McGuire

Hardware 588

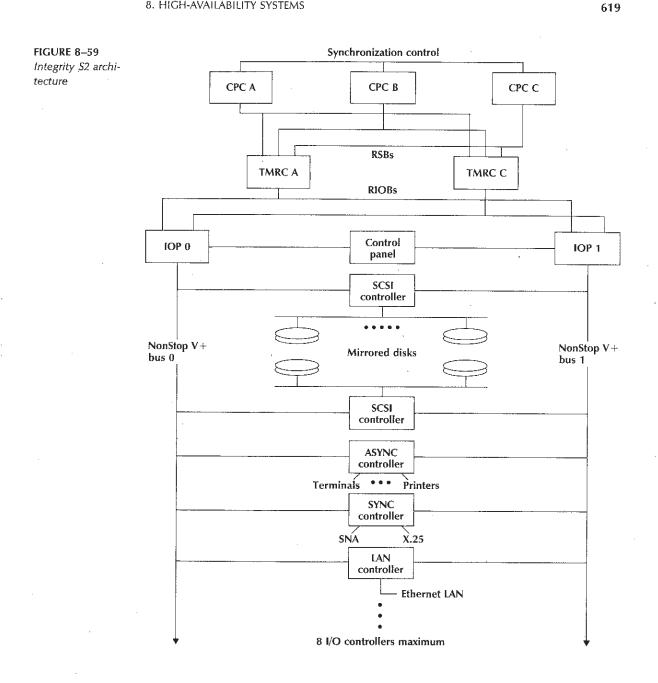

Processor Module Implementation Details 597 Integrity S2 618 Maintenance Facilities and Practices 622 Software 625 Operations 647 Summary and Conclusions 647

References 648

The Stratus Case: The Stratus Architecture ,648 Steven Webber

Stratus Solutions to Downtime 650 Issues of Fault Tolerance 652 System Architecture Overview 653 Recovery Scenarios 664 Architecture Tradeoffs 665 Stratus Software 666 Service Strategies 669 Summary 670

9 LONG-LIFE SYSTEMS 671

Introduction 671 Generic Spacecraft 671 Deep-Space Planetary Probes 676 Other Noteworthy Spacecraft Designs 679 References 679

The Galileo Case: Galileo Orbiter Fault Protection System 679 Robert W. Kocsis

The Galileo Spacecraft 680 Attitude and Articulation Control Subsystem 680 Command and Data Subsystem 683 AACS/CDS Interactions 687 Sequences and Fault Protection 688

Fault-Protection Design Problems and Their Resolution 689 Summary 690 References 690

#### 10 CRITICAL COMPUTATIONS 691

Introduction 691 C.vmp 691 SIFT 693

The C.vmp Case: A Voted Multiprocessor 694 Daniel P. Siewiorek, Vittal Kini, Henry Mashburn, Stephen McConnel, and Michael Tsao

System Architecture 694 Issues of Processor Synchronization 699 Performance Measurements 702 Operational Experiences 707 References 709

The SIFT Case: Design and Analysis of a Fault-Tolerant Computer for Aircraft Control 710 John H. Wensley, Leslie Lamport, Jack Goldberg, Milton W. Green, Karl N. Levitt,

P.M. Melliar-Smith, Robert E. Shostak, and Charles B. Weinstock Motivation and Background 710

SIFT Concept of Fault Tolerance 711 The SIFT Hardware 719 The Software System 723 The Proof of Correctness 728 Summary 733 Appendix: Sample Special Specification 733 References 735

# III A DESIGN METHODOLOGY AND EXAMPLE OF DEPENDABLE SYSTEM DESIGN 737

#### 11 A DESIGN METHODOLOGY 739

Daniel P. Siewiorek and David Johnson

Introduction 739

A Design Methodology for Dependable System Design 739

The VAXft 310 Case: A Fault-Tolerant System by Digital Equipment Corporation 745 William Bruckert and Thomas Bissett

Defining Design Goals and Requirements for the VAXft 310 746 VAXft 310 Overview 747 Details of VAXft 310 Operation 756

Summary 766

xii

#### CONTENTS

#### APPENDIXES 769

#### APPENDIX A 771

Error-Correcting Codes for Semiconductor Memory Applications: A State-of-the-Art Review 771 C.L. Chen and M.Y. Hsiao

Introduction 771 Binary Linear Block Codes 773 SEC-DEC Codes 775 SEC-DED-SBD Codes 778 SBC-DBD Codes 779 DEC-TED Codes 781 Extended Error Correction 784 Conclusions 786 References 786

#### APPENDIX B 787

Arithmetic Error Codes: Cost and Effectiveness Studies for Application in Digital System Design 787 Algirdas Avizienis

Methodology of Code Evaluation 787 Fault Effects in Binary Arithmetic Processors 790 Low-Cost Radix-2 Arithmetic Codes 794 Multiple Arithmetic Error Codes 799 References 802

#### APPENDIX C 803

Design for Testability—A Survey 803 Thomas W. Williams and Kenneth P. Parker Introduction 803 Design for Testability 807 Ad-Hoc Design for Testability 808 Structured Design for Testability 813 Self-Testing and Built-In Tests 821 Conclusion 828 References 829

#### APPENDIX D 831

Summary of MIL-HDBK-217E Reliability Model 831

Failure Rate Model and Factors 831 Reference 833

#### APPENDIX E 835

Algebraic Solutions to Markov Models 835 Jeffrey P. Hansen

Solution of MTTF Models 837

Complete Solution for Three- and Four-State Models 838 Solutions to Commonly Encountered Markov Models 839 References 839

GLOSSARY 841

**REFERENCES** 845

CREDITS 885

TRADEMARKS 890

INDEX 891

8

# HIGH-AVAILABILITY SYSTEMS

#### INTRODUCTION

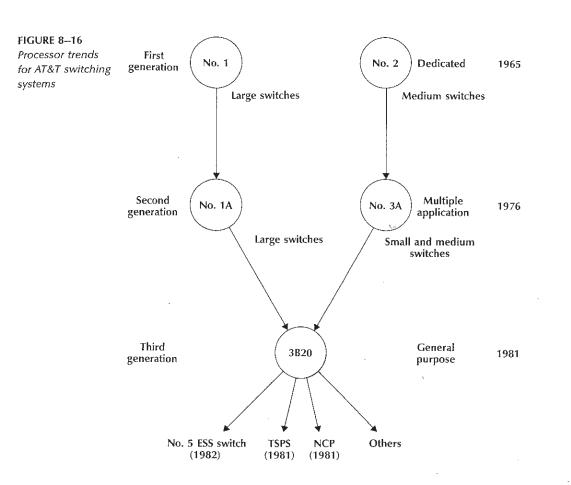

Dynamic redundancy is the basic approach used in high-availability systems. These systems are typically composed of multiple processors with extensive error-detection mechanisms. When an error is detected, the computation is resumed on another processor. The evolution of high-availability systems is traced through the family history of three commercial vendors: AT&T, Tandem, and Stratus.

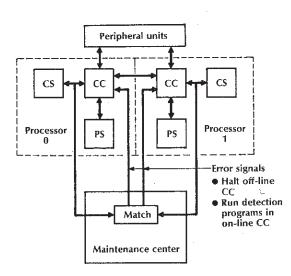

AT&T SWITCHING SYSTEMS AT&T pioneered fault-tolerant computing in the telephone switching application. The two AT&T case studies given in this chapter trace the variations of duplication and matching devised for the switching systems to detect failures and to automatically resume computations. The primary form of detection is hardware lock-step duplication and comparison that requires about 2.5 times the hardware cost of a nonredundant system. Thousands of switching systems have been installed and they are currently commercially available in the form of the 3B20 processor. Table 8–1 summarizes the evolution of the AT&T switching systems. It includes system characteristics such as the number of telephone lines accommodated as well as the processor model used to control the switching gear.

Telephone switching systems utilize natural redundancy in the network and its operation to meet an aggressive availability goal of 2 hours downtime in 40 years (3 minutes per year). Telephone users will redial if they get a wrong number or are disconnected. However, there is a user aggravation level that must be avoided: users will redial as long as errors do not happen too frequently. User aggravation thresholds are different for failure to establish a call (moderately high) and disconnection of an established call (very low). Thus, a telephone switching system follows a staged failure recovery process, as shown in Table 8–2.

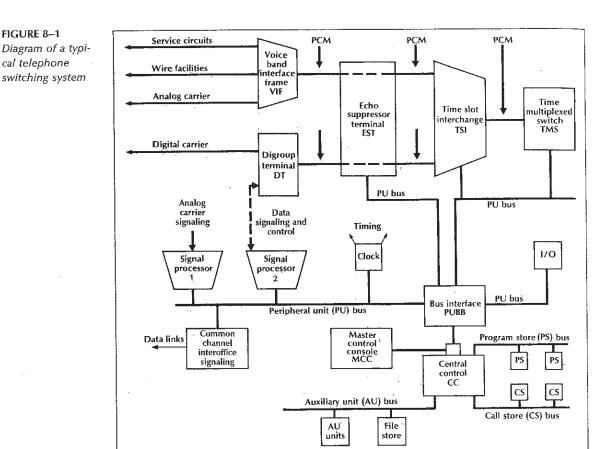

Figure 8–1 illustrates that the telephone switching application requires quite a different organization than that of a general-purpose computer. In particular, a substantial portion of the telephone switching system complexity is in the peripheral hardware. As depicted in Figure 8–1, the telephone switching system is composed of four major components: the transmission interface, the network, signal processors, and the central controller. Telephone lines carrying analog signals attach to the voice band interface frame (VIF), which samples and digitally encodes the analog signals. The output is pulse code modulated (PCM). The echo suppressor terminal (EST) removes echos that may have been introduced on long distance trunk lines. The PCM

| TABLE 8–1         Summary of         installed AT&T         telephone         switching systems | System | Number<br>of Lines | Year<br>Introduced | Number<br>Installed | Processor | Comments                                                             |

|-------------------------------------------------------------------------------------------------|--------|--------------------|--------------------|---------------------|-----------|----------------------------------------------------------------------|

|                                                                                                 | 1 ESS  | 5,000-65,000       | 1965               | 1,000               | No. 1     | First processor with<br>separate control and<br>data memories        |

|                                                                                                 | 2 ESS  | 1,000-10,000       | 1969               | 500                 | No. 2     |                                                                      |

|                                                                                                 | 1A ESS | 100,000            | 1976               | 2,000               | No. 1A    | Four to eight times<br>faster than No. 1                             |

|                                                                                                 | 2B ESS | 1,000–20,000       | 1975               | >500                | No. 3A    | Combined control and<br>data store;<br>microcoded; emulate:<br>No. 2 |

|                                                                                                 | 3 ESS  | 500-5,000          | 1976               | >500                | No. 3A    |                                                                      |

|                                                                                                 | 5 ESS  | 1,000-85,000       | 1982               | >1,000              | No. 3B    | Multipurpose processor                                               |

TABLE 8–2Levels of recoveryin a telephoneswitching system

| Phase | Recovery Action                                                                                                                                                 | Effect                                                       |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| 1     | Initialize specific transient memory.                                                                                                                           | Temporary storage affected; no calls lost                    |  |

| 2     | Reconfigure peripheral hardware. Initialize all transient memory.                                                                                               | Lose calls being established; calls<br>in progress not lost  |  |

| 3     | Verify memory operation, establish a<br>workable processor configuration, verify<br>program, configure peripheral hardware,<br>initialize all transient memory. | Lose calls being established; calls in progress not affected |  |

| 4     | Establish a workable processor<br>configuration, configure peripheral<br>hardware, initialize all memory.                                                       | All calls lost                                               |  |

signals are multiplexed onto a time-slotted digital bus. The digital bus enters a timespace-time network. The time slot interchange (TSI) switches PCM signals to different time slots on the bus. The output of the TSI goes to the time multiplexed switch (TMS), which switches the PCM signals in a particular time slot from any bus to any other bus. The output of the TMS returns to the TSI, where the PCM signals may be interchanged to another time slot. Signals intended for analog lines are converted from PCM to analog signals in the VIF. A network clock coordinates the timing for all of the switching functions.

The signal processors provide scanning and signal distribution functions, thus relieving the central processor of these activities. The common channel interface signaling (CCIS) provides an independent data link between telephone switching systems. The CCIS terminal is used to send supervisory switching information for the

various trunk lines coming into the office. The entire peripheral hardware is interfaced to the central control (CC) over AC-coupled buses. A telephone switching processor is composed of the central control, which manipulates data associated with call processing, administrative tasks, and recovery; program store; call store for storing transient information related to the processing of telephone calls; file store disk system used to store backup program copies; auxiliary units magnetic tapes storage containing basic restart programs and new software releases; input/output (I/O) interfaces to terminal devices; and master control console used as the control and display console for the system. In general, a telephone switching processor could be used to control more than one type of telephone switching system.

The history of AT&T processors is summarized in Table 8–3. Even though all the processors are based upon full duplication, it is interesting to observe the evolution from the tightly lock-stepped matching of every machine cycle in the early processors to a higher dependence on self-checking and matching only on writes to memory. Furthermore, as the processors evolved from dedicated, real-time controllers to mul-

TABLE 8–3 Summary of AT&T Telephone Switching Processors

| Processor/<br>Year<br>Introduced | Complexity<br>(Gates) | Unit_of<br>Switching | Matching                                                                                                                                                           | Other Error Detection/Correction                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------|-----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. 1, 1965                      | 12,000                | PS, CS, CC,<br>buses | Six internal nodes, 24<br>bits per node; one<br>node matched each<br>machine cycle; node<br>selected to be matched<br>dependent on instruc-<br>tion being executed | Hamming code on PS; parity on CS;<br>automatic retry on CS, PS; watch-<br>dog timer; sanity program to de-<br>termine if reorganization led to a<br>valid configuration                                                                                                                                                                                                                                                                       |

| No. 2, 1969                      | 5,000                 | Entire<br>computer   | Single match point on<br>call store input                                                                                                                          | Diagnostic programs; parity on PS;<br>detection of multiword accesses<br>in CS; watch-dog timer                                                                                                                                                                                                                                                                                                                                               |

| No. 1A, 1976                     | 50,000                | PS, CS, CC,<br>buses | 16 internal nodes, 24 bits<br>per node; two nodes<br>matched each machine<br>cycle                                                                                 | Two-parity bits on PS; roving spares<br>(i.e., contents of PS not com-<br>pletely duplicated, can be loaded<br>from disk upon error detection);<br>two-parity bits on CS; roving<br>spares sufficient for complete du-<br>plication of transient data; proces-<br>sor configuration circuit to search<br>automatically for a valid configura-<br>tion                                                                                         |

| No. 3A, 1975                     | 16,500                | Entire<br>computer   | None                                                                                                                                                               | On-line processor writes into both<br>stores; m-of-2m code on micro-<br>store plus parity; self-checking<br>decoders; two-parity bits on regis-<br>ters; duplication of ALU; watch-<br>dog timer; maintenance channel                                                                                                                                                                                                                         |

|                                  |                       | •                    |                                                                                                                                                                    | for observability and controllabil-<br>ity of the other processor; 25% of<br>logic devoted to self-checking<br>logic and 14% to maintenance                                                                                                                                                                                                                                                                                                   |

| 3B20D, 1981                      | 75,000                | Entire<br>computer   | None                                                                                                                                                               | access<br>On-line processor write into both<br>stores; byte parity on data paths;<br>parity checking where parity pre-<br>served, duplication otherwise;<br>modified Hamming code on main<br>memory; maintenance channel for<br>observability and controllability of<br>the other processor; 30% of con-<br>trol logic devoted to self-check-<br>ing; error-correction codes on<br>disks; software audits, sanity<br>timer, integrity monitor |

tiple-purpose processors, the operating system and software not only became more sophisticated but also became a dominant portion of the system design and maintenance effort.

The part I of the AT&T case study in this chapter, by Wing Toy, sketches the evolution of the telephone switching system processors and focuses on the latest member of the family, the 3B20D. Part II of the case study, by Liane C. Toy, outlines the procedure used in the 5ESS for updating hardware and/or software without incurring any downtime.

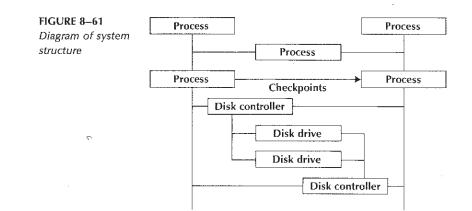

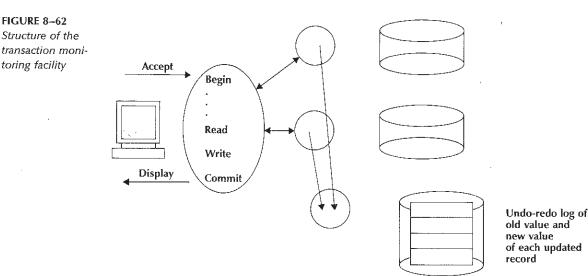

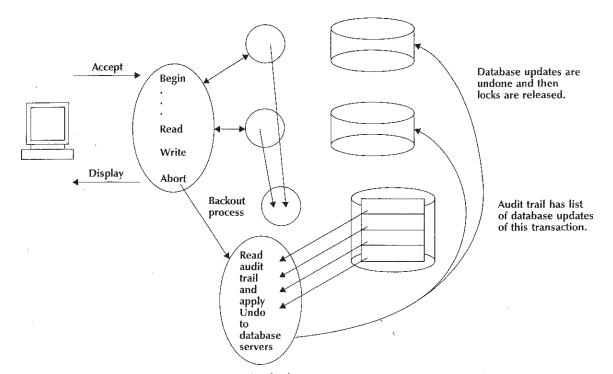

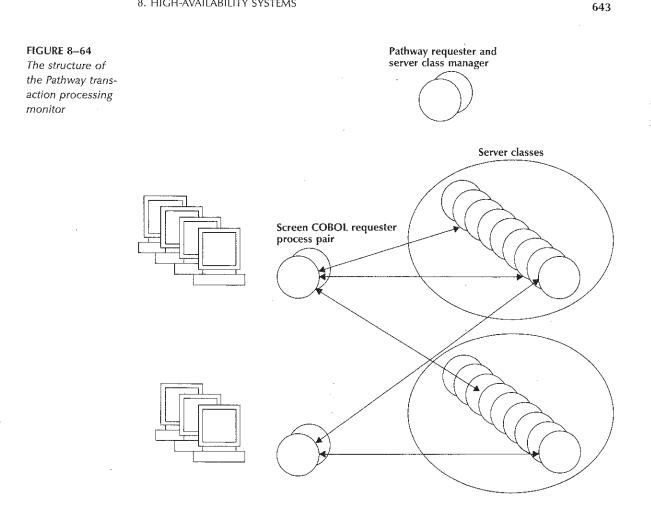

TANDEM COMPUTERS, INC. Over a decade after the first AT&T computer-controlled switching system was installed, Tandem designed a high-availability system targeted for the on-line transaction processing (OLTP) market. Replication of processors, memories, and disks was used not only to tolerate failures, but also to provide modular expansion of computing resources. Tandem was concerned about the propagation of errors, and thus developed a loosely coupled multiple computer architecture. While one computer acts as primary, the backup computer is active only to receive periodic checkpoint information. Hence, 1.3 physical computers are required to behave as one logical fault-tolerant computer. Disks, of course, have to be fully replicated to provide a complete backup copy of the database. This approach places a heavy burden upon the system and user software developers to guarantee correct operation no matter when or where a failure occurs. In particular, the primary memory state of a computation may not be available due to the failure of the processors. Some feel, however, that the multiple computer structure is superior to a lock-step duplication approach in tolerating design errors.

The architecture discussed in the Tandem case study, by Bartlett, Bartlett, Garcia, Gray, Horst, Jardine, Jewett, Lenoski, and McGuire, is the first commercially available, modularly expandable system designed specifically for high availability. Design objectives for the system include the following:

- "Nonstop" operation wherein failures are detected, components are reconfigured out of service, and repaired components are configured back into the system without stopping the other system components

- Fail-fast logic whereby no single hardware failure can compromise the data integrity of the system

- Modular system expansion through adding more processing power, memory, and peripherals without impacting applications software

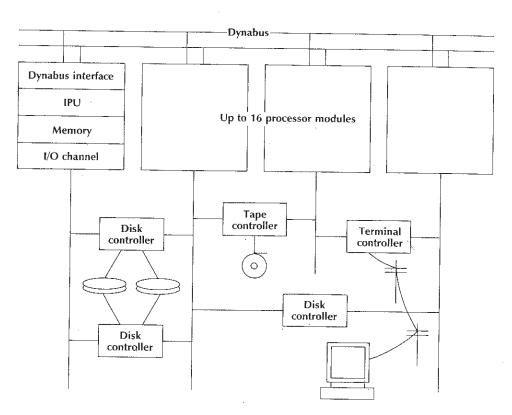

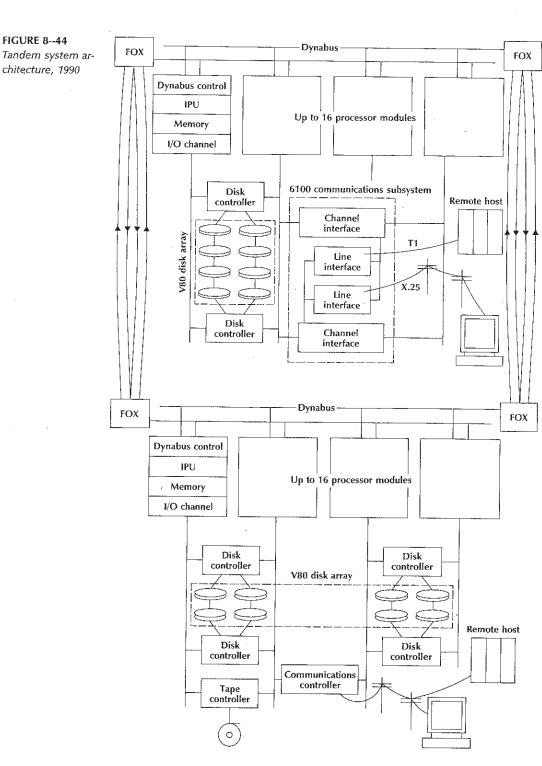

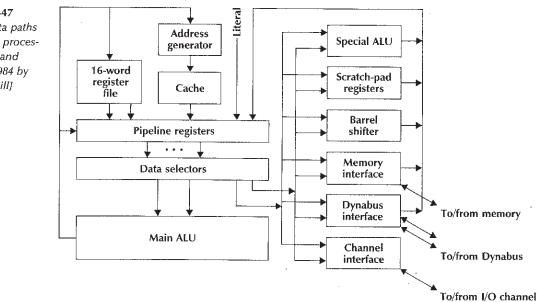

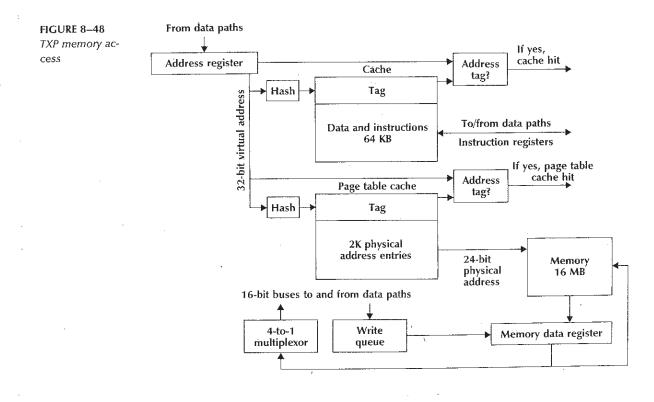

As in the AT&T switching systems, the Tandem architecture is designed to take advantage of the OLTP application to simplify error detection and recovery. The Tandem architecture is composed of up to 16 computers interconnected by two messageoriented Dynabuses. The hardware and software modules are designed to be fast-fail; that is, to rapidly detect errors and subsequent terminate processing. Software modules employ consistency checks and defensive programming techniques. Techniques employed in hardware modules include the following:

Checksums on Dynabus messages Parity on data paths Error-correcting code memory Watch-dog timers

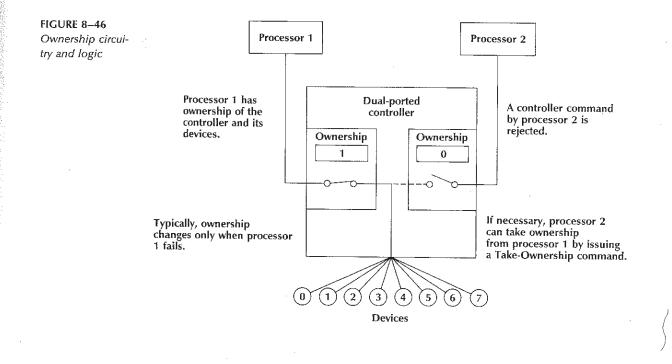

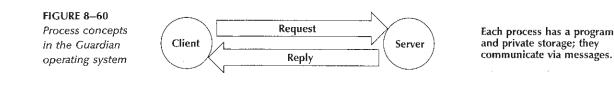

All I/O device controllers are dual ported for access by an alternate path in case of processor or I/O failure. The software builds a process-oriented system with all communications handled as messages on this hardware structure. This abstraction allows the blurring of the physical boundaries between processors and peripherals. Any I/O device or resource in the system can be accessed by a process, regardless of where the resource and process reside.

Retry is extensively used to access an I/O device. Initially, hardware/firmware retries the access assuming a temporary fault. Next, software retries, followed by alternative path retry and finally alternative device retry.

A network systems management program provides a set of operators that helps reduce the number of administrative errors typically encountered in complex systems. The Tandem Maintenance and Diagnostic System analyzes event logs to successfully call out failed field-replaceable units 90 percent of the time. Networking software exists that allows interconnection of up to 255 geographically dispersed Tandem systems. Tandem applications include order entry, hospital records, bank transactions, and library transactions.

Data integrity is maintained through the mechanisms of I/O "process pairs"; one I/O process is designated as primary and the other is designated as backup. All file modification messages are delivered to the primary I/O process. The primary sends a message with checkpoint information to the backup so that it can take over if the primary's processor or access path to the I/O device fails. Files can also be duplicated on physically distinct devices controlled by an I/O process pair on physically distinct processors. All file modification messages are delivered to both I/O processes. Thus, in the event of physical failure or isolation of the primary, the backup file is up-to-date and available.

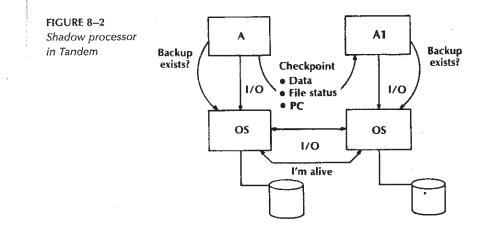

User applications can also utilize the process-pair mechanism. As an example of how process pairs work, consider the nonstop application, program A, shown in Figure 8–2. Program A starts a backup process, A1, in another processor. There are also duplicate file images, one designated primary and the other backup. Program A periodically (at user-specified points) sends checkpoint information to A1. A1 is the same program as A, but knows that it is a backup program. A1 reads checkpoint messages to update its data area, file status, and program counter.

The checkpoint information is inserted in the corresponding memory locations of the backup process, as opposed to the more usual approach of updating a disk file. This approach permits the backup process to take over immediately in the event of failure without having to perform the usual recovery journaling and disk accesses before processing resumes.

Program A1 loads and executes if the system reports that A's processor is down (error messages sent from A's operating system image or A's processor fails to respond

to a periodic "I'm alive" message). All file activity by A is performed on both the primary and backup file copies. When A1 starts to execute from the last checkpoints, it may attempt to repeat I/O operations successfully completed by A. The system file handler will recognize this and send A1 a successfully completed I/O message. Program A periodically asks the operating system if a backup process exists. Since one no longer does, it can request the creation and initialization of a copy of both the process and file structure.

A major issue in the design of loosely coupled duplicated systems is how both copies can be kept identical in the face of errors. As an example of how consistency is maintained, consider the interaction of an I/O processor pair as depicted in Table 8-4. Initially, all sequence numbers (SeqNo) are set to zero. The requester sends a request to the server. If the sequence number is less than the server's local copy, a failure has occurred and the status of the completed operation is returned. Note that the requested operation is done only once. Next, the operation is performed and a checkpoint of the request is sent to the server backup. The disk is written, the sequence number incremented to one, and the results checkpointed to the server backup, which also increments its sequence number. The results are returned from the server to the requestor. Finally the results are checkpointed to the requester backup, which also increments its sequence number.

Now consider failures. If either backup fails, the operation completes successfully. If the requester fails after the request has been made, the server will complete the operation but be unable to return the result. When the requester backup becomes active, it will repeat the request. Since its sequence number is zero, the server test at step 2 will return the result without performing the operation again. Finally, if the server fails, the server backup either does nothing or completes the operation using checkpointed information. When the requester resends the request, the new server (that is, the old server backup) either performs the operation or returns the saved results. More information on the operating system and the programming of nonstop applications can be found in Bartlett [1978].

531

pair transactions

| Step | Requester<br>SeqNo = 0                    | Requester Backup<br>SeqNo = 0 | ServerServer BackupSeqNo = 0SeqNo = 0                                               |

|------|-------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------|

| 1    | lssue<br>request<br>to write<br>record —— | ¢                             |                                                                                     |

| 2    |                                           |                               | If SeqNo <<br>MySeqNo, then<br>return saved status                                  |

| 3    |                                           |                               | Otherwise, read disk,<br>perform operation, ——— Saves request<br>checkpoint request |

| 4    |                                           | -                             | Write to disk<br>SeqNo = 1                                                          |

| 5    |                                           |                               | - Return results                                                                    |

| 6    | Checkpoint<br>results                     | ──► SeqNo = 1                 | ·                                                                                   |

Source: Bartlett, 1981; © 1981 ACM.

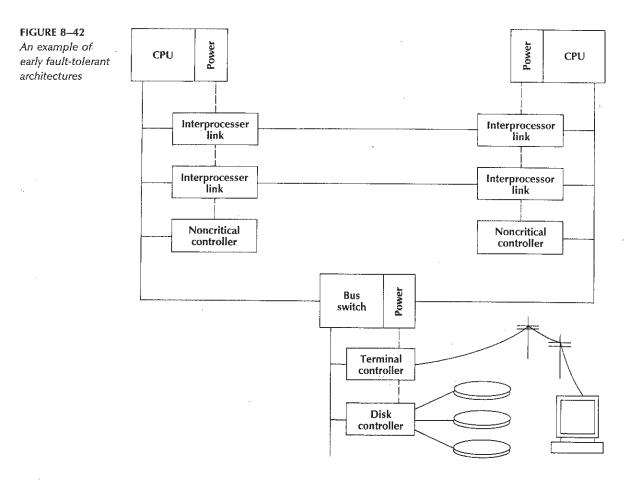

STRATUS COMPUTERS, INC. Whereas the Tandem architecture was based upon minicomputer technology, Stratus entered the OLTP market five years after Tandem by harnessing microprocessors. By 1980, the performance of microprocessor chips was beginning to rival that of minicomputers. Because of the smaller form factor of microprocessor chips, it was possible to place two microprocessors on a single board and to compare their output pins on every clock cycle. Thus, the Stratus system appears to users as a conventional system that does not require special software for error detection and recovery. The case study by Steven Webber describes the Stratus approach in detail.

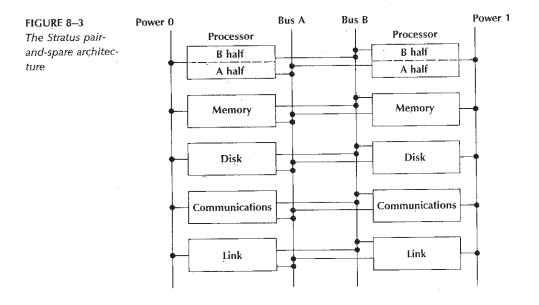

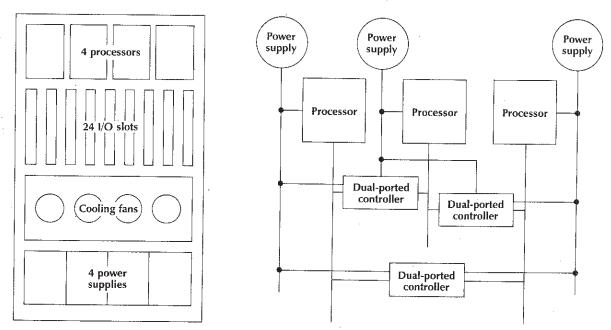

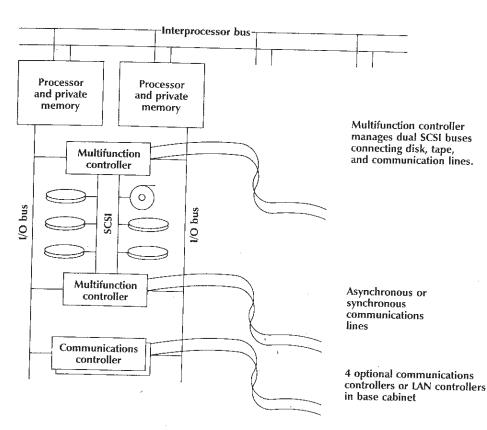

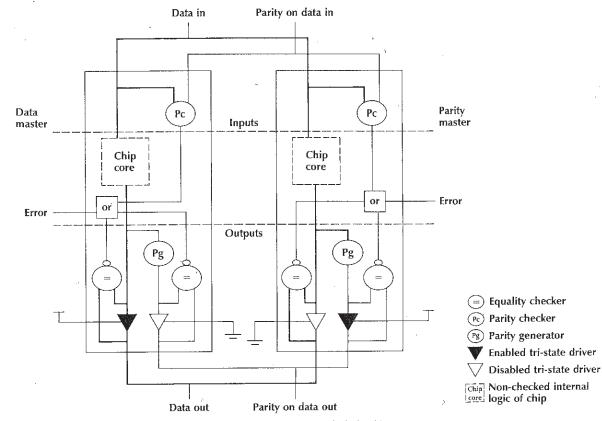

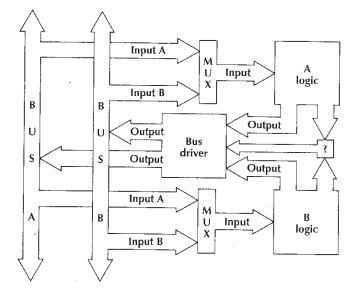

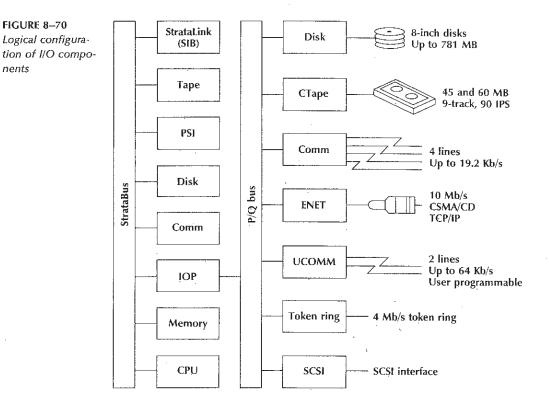

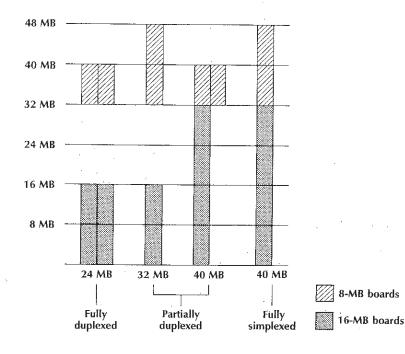

The design goal for Stratus systems is continuous processing, which is defined as uninterrupted operation without loss of data, performance degradation, or special programming. The Stratus self-checking, duplicate-and-match architecture is shown in Figure 8–3. A module (or computer) is composed of replicated power and backplane buses (StrataBus) into which a variety of boards can be inserted. Boards are logically divided into halves that drive outputs to and receive inputs from both buses. The bus drivers/receivers are duplicated and controlled independently. The logical halves are driven in lock-step by the same clock. A comparitor is used to detect any disagreements between the two halves of the board. Multiple failures that affect the two independent halves of a board could cause the module to hang as it alternated between buses seeking a fault-free path. Up to 32 modules can be interconnected into a system via a message-passing Stratus intermodule bus (SIB). Access to the SIB is by dual 14 megabyte-per-second links. Systems, in return, are tied together by an X.25 packet-switched network.

Now consider how the system in Figure 8-3 tolerates failure. The two processor boards (each containing a pair of microprocessors), each self-checking modules, are used in a pair-and-spare configuration. Each board operates independently. Each half of each board (for example, side A) received inputs from a different bus (for example, bus A) and drives a different bus (for example, bus A). Each bus is the wired-OR of one-half of each board (for example, bus A is the wired-OR of all A board halves). The boards constantly compare their two halves, and upon disagreement, the board removes itself from service, a maintenance interrupt is generated, and a red light is illuminated. The spare pair on the other processor board continues processing and is now the sole driver of both buses. The operating system executes a diagnostic on the failed board to determine whether the error was caused by a transient or permanent fault. In the case of a transient, the board is returned to service. Permanent faults are reported by phone to the Stratus Customer Assistance Center (CAC). The CAC reconfirms the problem, selects a replacement board of the same revision, prints installation instructions, and ships the board by overnight courier. The first time the user realizes there is a problem is when the board is delivered. The user removes the old board and inserts the new board without disrupting the system (that is, makes a "hot" swap). The new board interrupts the system, and the processor that has been running brings the replacement into full synchronization, at which point the full configuration is available again. Detection and recovery are transparent to the application software.

The detection and recovery procedures for other system components are similar, although the full implementation of pair-and-spare is restricted to only the processor and memory. The disk controllers contain duplicate read/write circuitry. Communica-

tions controllers are also self-checking. In addition, the memory controllers monitor the bus for parity errors. The controllers can declare a bus broken and instruct all boards to stop using that bus. Other boards monitor the bus for data directed to them. If the board detects an inconsistency but the memory controllers have not declared the bus broken, the board assumes that its bus receivers have failed and declares itself failed.

The Stratus hardware approach is attractive in that it does not require on-line recovery from faults. The spare component continues processing until its fault counterpart can be replaced. No data errors are injected into the system; hence, no software recovery mechanisms are required for the pair-and-spare components. Complexities caused by checkpointing/restart programming and other software fault-tolerant considerations are eliminated. In addition to ease in programming, the Stratus approach to maintenance reduces the yearly service cost to 6 percent of life-cycle cost, as compared to an industrial average of 9 percent.

REFERENCES

Bartlett, 1978, 1981.

# THE AT&T CASE

Part I: Fault-Tolerant Design of AT&T Telephone Switching System Processors

W.N. TOY

# INTRODUCTION

Except for computer systems used in space-borne vehicles and U.S. defense installations, no other application has a higher availability requirement than a stored-program-controlled (SPC) telecommunications switching system. SPC systems have been designed to be out of service no more than a few minutes per year. Furthermore, design objectives permit no more than 0.01 percent of the telephone calls to be processed incorrectly [Downing, Nowak, and Tuomenoksa, 1964]. For example, when a fault occurs in a system, few calls in progress may be handled incorrectly during the recovery process.

At the core of every system is a single high-speed central processor [Harr, Taylor, and Ulrich, 1969; Browne et al., 1969; Staehler, 1977]. To establish an ultrareliable switching environment, redundancy of system components, including duplication of the processor itself, is the approach taken to compensate for potential machine faults. Without this redundancy, a single component failure in the processor might cause a complete failure of the entire system. With duplication, a standby processor takes over control and provides continuous telephone service.

When the system fails, the fault must be quickly detected and isolated. Meanwhile, a rapid recovery of the call processing functions (by the redundant component(s) and/or processor) is necessary to maintain the system's high availability. Next, the fault must be diagnosed and the defective unit repaired or replaced. The failure rate and repair time must be such that the probability is very small for a failure to occur in the duplicate unit before the first unit is repaired.

#### ALLOCATION AND CAUSES OF SYSTEM DOWNTIME

534

The outage of a telephone (switching) office can be caused by facilities other than the processor. While a hardware fault in one of the peripheral units generally results in only a partial loss of service, it is possible for a fault in this area to bring the entire system down. By design, the processor has been allocated two-thirds of the system downtime. The other one-third is allocated to the remaining equipment in the system.

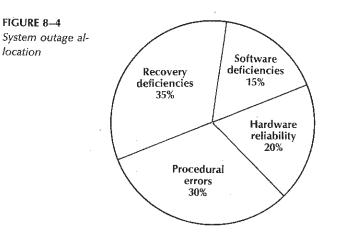

Field experience indicates that system outages due to the processor may be assigned to one of four categories, as shown in Figure 8–4 [Staehler and Watters, 1976]. The percentages in this figure represent the fraction of total downtime attributable to each cause. The four categories are as follows.

• Hardware Reliability: Before the accumulation of large amounts of field data, total system downtime was usually assigned to hardware. We now know that the situation is more complex. Processor hardware actually accounts for only 20 percent of the downtime. With growing use of stored program control, it has become increasingly important to make such systems more reliable. Redundancy is designed into all subsystems so that the system can go down *only* when a hardware failure occurs simultaneously in a unit and its duplicate. However, the data now show that good diagnostic and trouble location programs are also very critical parts of the total system reliability performance.

• Software Deficiencies: Software deficiencies include all software errors that cause memory mutilation and program loops that can only be cleared by major reinitialization. Software faults are the result of improper translation or implementation of the original algorithm. In some cases, the original algorithm may have been incorrectly specified. Program changes and feature additions are continuously incorporated into working offices. Software accounts for 15 percent of the downtime.

• *Recovery Deficiencies*: Recovery is the system's most complex and difficult function. Deficiencies may include the shortcomings of either hardware or software design to detect faults when they occur. When the faults go undetected, the system remains extensively impaired until the trouble is recognized. A recovery problem can also occur if the system is unable to properly isolate a faulty subsystem and configure a working system around it.

The many possible system states that may arise under trouble conditions make recovery a complicated process. Besides those problems already mentioned, unforeseen difficulties may be

encountered in the field and lead to inadequate recovery. Because of the large number of variables involved and because the recovery function is so strongly related to all other components of maintenance, recovery deficiencies account for 35 percent of the downtime.

• *Procedural Errors*: Human error on the part of maintenance personnel or office administrators can also cause the system to go down. For example, someone in maintenance may mistakenly pull a circuit pack from the on-line processor while repairing a defective standby processor. Inadequate and incorrect documentation (for example, user's manuals) may also be classified as human error. Obviously, the number of manual operations must be reduced if procedural errors are to be minimized. Procedural errors account for 30 percent of the downtime.

The shortcomings and deficiencies of current systems are being continually corrected to improve system reliability.

#### DUPLEX ARCHITECTURE

When a fault occurs in a nonredundant single processor, the system will remain down until the processor is repaired. In order to meet reliability requirements, *redundancy* is included in the system design, and continuous, correct operation is maintained by duplicating all functional units within the processor. If one of the units fails, the duplicated unit is switched in, maintaining continuous operation. Meanwhile, the defective unit is repaired. Should a fault occur in the duplicated unit during the repair interval, the system will, of course, go down. If the repair interval is relatively short, the probability of simultaneous faults occurring in two identical units is quite small. This technique of redundancy has been used throughout each AT&T switching system.

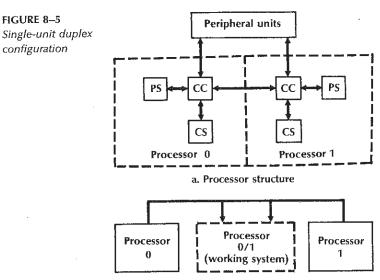

The first-generation electronic switching system (ESS) processor structure consists of two store communities: program store and call store. The program store is a read-only memory, containing the call processing, maintenance, and administration programs; it also contains long-term translation and system parameters. The call store contains the transient data related to telephone calls in progress. The memory is electrically alterable to allow its data to be changed frequently. In one particular arrangement, shown in Figure 8–5b, the complete processor is treated as a single functional block and is duplicated. This type of single-unit duplex system has two possible configurations: Either processor 0 or processor 1 can be assigned as the on-line working system, while the other unit serves as a standby backup. The mean time to failure (MITF), a measure of reliability, is given by the following expression [Smith, 1972]:

MTTF =  $\frac{\mu}{2\lambda^2}$

where  $\mu$  = repair rate (reciprocal of the repair time)  $\lambda$  = failure rate

The failure rate ( $\lambda$ ) of one unit is the sum of the failure rates of all components within the unit. For medium and small ESS processors, Figure 8–5a shows a system structure containing several functional units that are treated as a single entity, with  $\lambda$  still sufficiently small to meet the reliability requirement. The single-unit duplex configuration has the advantage of being very simple in terms of the number of switching blocks in the system. This configuration simplifies not only the recovery program but also the hardware interconnection by eliminating the additional access required to make each duplicated block capable of switching independently into the online system configuration.

In the large 1ES switching system, which contains many components, the MTTF becomes

b. Two possible configurations

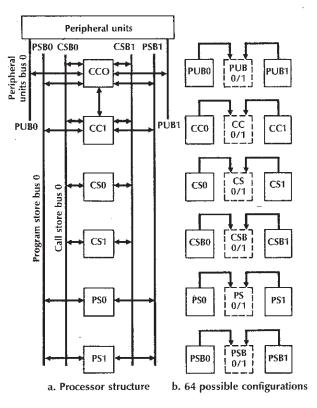

too low to meet the reliability requirement. In order to increase the MTTF, either the number of components (failure rate) or the repair time must be reduced. Alternatively, the single-unit duplex configuration can be partitioned into a multi-unit duplex configuration, as shown in Figure 8-6. In this arrangement, each subunit contains a small number of components and can be switched into a working system. The system will fail only if a fault occurs in the redundant subunit while the original is being repaired. Since each subunit contains fewer components, the probability of two simultaneous faults occurring in a duplicated pair of subunits is reduced. The MTTF of the multi-unit duplex configuration can be computed by considering the conditional probability of the failure of a duplicate subunit during the repair time of the original subunit.

An example of a multi-unit duplex configuration is shown in Figure 8-6. A working system is configured with a fault-free CCx-CSx-CSBx-PSx-PSBx-PUBx arrangement, where x is either subunit 0 or subunit 1. This arrangement means there are 26, or 64, possible combinations of system configurations. The MTTF is given by the following expression:

$$ATTF = \frac{r\mu}{2\lambda^2} \tag{1}$$

and

N

$$r = \frac{1}{\left(\lambda_{\rm CC}/\lambda\right)^2 + \left(\lambda_{\rm CS}/\lambda\right)^2 + \left(\lambda_{\rm CSB}/\lambda\right)^2 + \left(\lambda_{\rm PSB}/\lambda\right)^2 + \left(\lambda_{\rm PUB}/\lambda\right)^2}$$

(2)

The factor r is at a maximum when the failure rate ( $\lambda_i$ ) for each subunit is the same. In this case,

$$\lambda_{CC} = \lambda_{CS} = \lambda_{CSB} = \lambda_{PSB} = \lambda_{PUB} = \lambda_{i}$$

<sup>(3)</sup>

536

FIGURE 8-5

configuration

or

$$\lambda_i = \frac{i}{2}$$

where s = number of subunits in Eq. (2)

s = 6r = s

At best, the MTTF is improved by a factor corresponding to the number of partitioned subunits. This improvement is not fully realized, since equipment must be added to provide additional access and to select subunits. Partitioning the subsystem into subunits, as shown in Figure 8–6, results in subunits of different sizes. Again, the failure rate for each individual subunit will not be the same; hence, the *r*-factor will be smaller than 6. Because of the relatively large number of components used in implementing the 1ESS switch processor, the system is arranged in the multi-unit duplex configuration in order to meet the reliability requirement.

Reliability calculation is a process of predicting, from available failure rate data, the achievable reliability of a system and the probability of meeting the reliability objectives for telephone switching applications. These calculations are most useful and beneficial during the early stages of design in order to assess various types of redundancy and to determine the system's organi-

#### FIGURE 8–6 Multi-unit duplex configuration

(4)

zation. In the small and medium switches, the calculations support the use of single-unit duplex structures. For large systems, it is necessary to partition the system into a multi-unit duplex configuration.

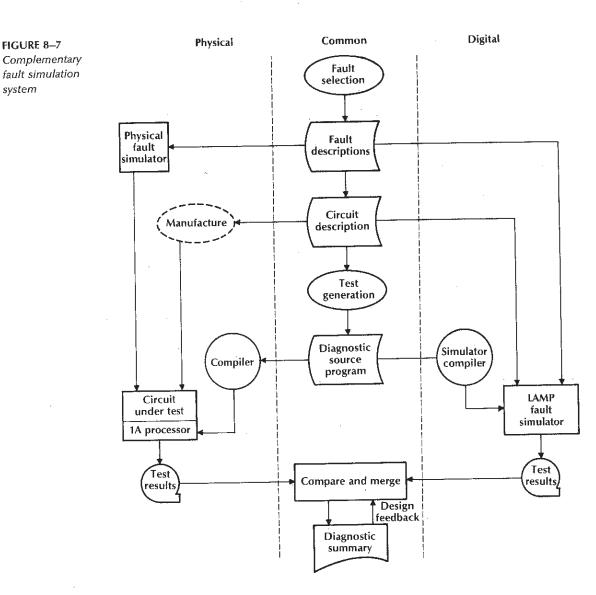

One of the more difficult tasks of maintenance design is fault diagnosis. The maintenance design's effectiveness in diagnostic resolution can be determined by simulation of the system's behavior in the presence of a specific fault. By means of simulation, design deficiencies can be identified and corrected prior to any system's deployment in the field. It is necessary to evaluate the system's ability to detect faults, to recover automatically back into a working system, and to provide diagnostics information when the fault is within a few replaceable circuit packs. Fault simulation, therefore, is an important aspect of maintenance design.

There are essentially two techniques used for simulating faults of digital systems: physical simulation and digital simulation. Physical simulation is a process of inserting faults into a physical working model. This method produces more realistic behavior under fault conditions than digital simulation does. A wider class of faults can be applied to the system, such as a blown fuse or shorted backplane interconnection. However, fault simulation cannot begin until the design has been completed and the equipment is fully operational. Also, it is not possible to insert faults that are internal to an integrated circuit.

Digital fault simulation is a means of predicting the behavior under failure of a processor modeled in a computer program. The computer used to execute the program (the host) is generally different from the processor that is being simulated (the object). Digital fault simulation gives a high degree of automation and excellent access to interior points of logic to monitor the signal flow. It allows diagnostic test development and evaluation to proceed well in advance of unit fabrication. The cost of computer simulation can be quite high for a large, complex system:

The physical fault simulation method was first employed to generate diagnostic data for the Morris Electronic Switching System [Tsiang and Ulrich, 1962]. Over 50,000 known faults were purposely introduced into the central control to be diagnosed by its diagnostic program. Test results associated with each fault were recorded. They were then sorted and printed in dictionary format to formulate a trouble-locating manual. Under trouble conditions, by consulting the manual, it was possible to determine a set of several suspected circuit packs that might contain the defective component. Use of the dictionary technique at the Morris system kept the average repair time low and made maintenance much easier.

The experience gained in the physical fault simulation was applied and extended in the 1ESS switch development [Downing, Nowak, and Tuomenoksa, 1964]. Each plug-in circuit pack was replaced by a fault simulator that introduced every possible type of single fault on the replaced package one at a time and then recorded the system reaction on magnetic tape. This procedure was followed for all circuit packs in the system. In addition to diagnostic data for dictionaries, additional data were collected to determine the adequacy of hardware and software in fault detection and system recovery. Deficiencies were corrected to improve the overall maintenance of the system.

A digital logic simulator, called LAMP [Chang, Smith, and Walford, 1974], was developed for the 1A system, and it played an important role in the hardware and diagnostics development of the 1A Processor. LAMP is capable of simulating a subsystem with as many as 65,000 logic gates. All classical faults for standard logic gates are simulatable with logic nodes stuck-at-0 or stuck-at-1. Before physical units are available, digital simulators can be very effective in verifying the design, evaluating diagnostic access, and developing tests. Physical fault simulation has been demonstrated in the System 1 processor to give a very realistic behavior under fault conditions. The integration of both techniques was employed in the development of the 1A processor to

#### 538

FAULT SIMULATION TECHNIQUES

FIGURE 8-7

system

take advantage of both processes. The use of complementary simulation allows faults to be simulated physically (in the system laboratory) and logically (on a computer). Most of the deficiencies of one simulation process are compensated for by the other. The complementary method provides both a convenient method for validating the results and more extensive fault simulation data than is possible if either process is used individually. Figure 8-7 shows the complementary process of fault simulation used in the 1A Processor development [Bowman et al., 1977; Goetz, 1974]. Maximum diagnostic performance was achieved from an integrated use of both simulation methods.

26

FIRST-GENERATION ESS PROCESSORS

The world's first stored-program-controlled switching system provided commercial telephone service at Morris, Illinois, in 1959 for about a year on a field-trial basis [Keister, Ketchledge, and Lovell, 1960]. The system demonstrated the use of stored program control and the basic main-tenance philosophy of providing continuous and reliable telephone service. The trial established valuable guides for designing a successor, the 1ESS switch.

#### 1ESS Switch Processor (No. 1 Processor)

The 1ESS switching system was designed to serve large metropolitan telephone offices, ranging from several thousand to 65,000 lines [Keister, Ketchledge, and Vaughan, 1964]. As in most large switching systems, the processor represents only a small percentage of the total system cost. Therefore, performance and reliability were of primary importance in the design of the No. 1 processor; cost was secondary. In order to meet the reliability standards established by electromechanical systems, all units essential to proper operation of the office are duplicated (see Figure 8–6). The multi-unit duplex configuration was necessary to increase the MTTF of the processor because of the large number of components in each of the functional blocks.

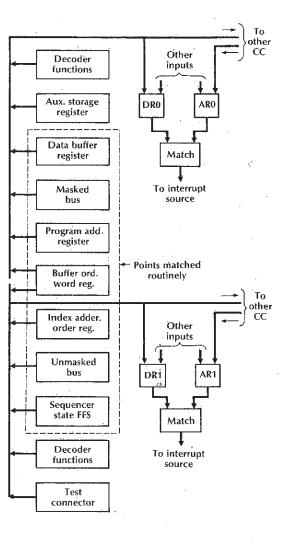

Even with duplication, troubles must be found and corrected quickly to minimize exposure to system failure due to multiple troubles. All units are monitored continually so that troubles in the standby units are found just as quickly as those in the on-line units. Monitoring is accomplished by running the on-line and standby units in synchronous and match mode of operation [Downing, Nowak, and Tuomenoksa, 1964]. Synchronization requires that clock timing signals be in close tolerance so that every operation in both halves is performed in step, and key outputs are compared for error detection. The synchronization of duplicated units is accomplished by having the on-line oscillator output drive both clock circuits. There are two match circuits in each central control (CC). Each matcher compares 24 bits within one machine cycle of 5.5 microseconds. Figure 8-8 shows that each matcher has access to six sets of internal nodes (24 bits per node). In the routine match mode, the points matched in each cycle are dependent upon the instruction that is being executed. The selected match points are those most pertinent to the data processing steps that occur during a given machine cycle. The two matchers in each CC compare the same sets of selected test points. If a mismatch occurs, an interrupt is generated, causing the fault-recognition program to run. The basic function of this program is to determine which half of the system is faulty. The suspected unit is removed from service, and the appropriate diagnostic program is run to pinpoint the defective circuit pack. The capability of each CC to compare a number of internal nodes provides a highly effective means of detecting hardware errors.

The No. 1 Processor was designed during the discrete component era (early 1960s), using individual components to implement logic gates [Cagle et al., 1964]. The CC contains approximately 12,000 logic gates. Although this number appears small when compared to large-scale integration (LSI) technology, the No. 1 Processor was a physically large machine for its time. The match circuits capable of comparing internal nodes are the primary tools incorporated into the CC for diagnosing as well as detecting troubles. Specified information can be sampled by the matchers and retained in the match registers for examination. This mode of operation obtains critical data during the execution of diagnostic programs.

The early program store used permanent magnet twister (PMT) modules as basic storage elements [Ault et al., 1964]. PMTs are a form of ROM in which system failures cannot alter the information content. Experience gained from the Morris field test system, which used the less reliable flying spot store, indicated that Hamming correction code was highly effective in providing continuous operation. At the time of development, it was felt that PMT modules might not be

FIGURE 8--8 No. 1 Processor's

CC match access

reliable enough. Consequently, the program store word included additional check bits for singlebit error correction (Hamming code). In addition, an overall parity check bit that covers both the data and their addresses is included in the word. The word size consists of 37 bits of information and seven check bits. When an error is corrected during normal operation, it is logged in an error counter. Also, detection of a single error in the address or a double error in the word will cause an automatic retry.

The call store is the temporary read and write memory for storing transient data associated with call processing. Ferrite sheet memory modules are the basic storage elements used in implementing the call store in the 1ESS switch [Genke, Harding, and Staehler, 1964]. The call store used in most No. 1 offices is smaller than the program store. (At the time of design, the cost per bit of call store was considerably higher than that of program store.) Also, ferrite sheet

memory modules were considered to be very reliable devices. Consequently, single-bit error detection rather than Hamming correction code was provided in the call store.

There are two parity check bits: one over both the address and the data; and the other over the address only. Again, as in the program store, automatic retry is performed whenever an error is detected, and the event is logged in an error counter for diagnostic use.

Troubles are normally detected by fault-detection circuits, and error-free system operation is recovered by fault recognition programs [Downing, Nowak, and Tuomenoksa, 1964]. This requires the on-line processor to be capable of making a proper decision. If this is not possible, an emergency action timer will time out and activate special circuits to establish various combinations of subsystems into a system configuration. A special program that is used to determine whether or not the assembled processor is sane takes the processor through a series of tests arranged in a maze. Only one correct path through the maze exists. If the processor passes through successfully, the timer will be reset, and recovery is successful. If recovery is unsuccessful, the timer will time out again, and the rearrangement of subsystems will be tried one at a time (for example, combination of CC, program store, and program store bus systems). For each selected combination, the special sanity program is started and the sanity timer is activated. This procedure is repeated until a working configuration is found. The sanity program and sanity timer determine if the on-line CC is functioning properly. The active CC includes the program

# 2ESS Switch Processor (No. 2 Processor)

The No. 2 Processor was developed during the mid-1960s [Spencer and Vigilante, 1969]. The 2ESS switch was designed for medium-sized offices ranging from 1,000 to 10,000 lines. The processor's design was derived from experience with the common stored program of a private branch exchange (PBX), the No. 101 [Seley and Vigilante, 1964]. Since the capacity requirement of the 2ESS switch was to be less than that of the 1ESS switch, cost became one of the more important design considerations. (Reliability is equally important in all systems.) The 2ESS switch contains much less hardware than the 1ESS switch. Understandably, its component failure rate is also substantially lower. Its CC contains approximately 5000 gates (discrete components). To reduce cost and increase reliability, resistor-transistor logic (RTL) gates were chosen for the 2ESS processor, since resistors are less expensive and more reliable than diodes [the No. 1 Processor used diode-transistor logic (DTL)].

Because the No. 2 Processor's CC, program store, and call store are smaller, they are grouped together as a single switchable block in the single-unit duplex configuration shown in Figure 8–5. Calculations indicate that its MTTF is approximately the same as the No. 1 multi-unit duplex structure, with each of the functional blocks and associated store buses grouped together as a switchable block. The use of only two subsystem configurations considerably reduces the amount of hardware needed to provide gating paths and control for each functional unit. Moreover, the recovery program is simplified, and the reliability of the system is improved.

The No. 2 Processor runs in the synchronous and match mode of operation [Beuscher et al., 1969]. The on-line oscillator output drives both clock circuits in order to keep the timing synchronized. The match operation is not as extensive as it is in the No. 1 Processor. For simplicity, there is only one matcher in the No. 2 Processor; it is located in the nonduplicated maintenance center (see Figure 8–9). The matcher always compares the call store input register in the two CCs when call store operations are performed synchronously. A fault in almost any part of either CC quickly results in a call store input register mismatch. This mismatch occurs because almost all data manipulation performed in both the program control and the input-output control involves

processed data returning to the call store. The call store input is the central point by which data eventually funnel through to the call store. By matching the call store inputs, an effective check of the system equipment is provided. Compared to the more complex matching of the No. 1 Processor, error detection in the No. 2 Processor may not be as instantaneous, since only one crucial node in the processor is matched. Certain faults in the No. 2 Processor will go undetected until the errors propagate into the call store. This interval is probably no more than tens or hundreds of microseconds. During such a short interval, the fault would affect only a single call.

The No. 2 Processor matcher is not used as a diagnostic tool as is the matcher in the No. 1 Processor. Therefore, additional detection hardware is designed into the No. 2 Processor to help diagnose as well as detect faults. When a mismatch occurs, the detection program is run in the on-line CC to determine if it contains the fault. This is done while the standby processor is disabled. If a solid fault in the on-line processor is detected by the mismatch detection program, the control is automatically passed to the standby processor, causing it to become the on-line processor. The faulty processor is disabled and diagnostic tests are called in to pinpoint the defective circuit pack.

The program store also uses PMT modules as basic storage elements, with a word size of 22 bits, half the width of the No. 1 Processor's word size. Experience gained in the design and operation of the No. 101 PBX showed that PMT stores are very reliable. The additional protection provided in the No. 1 Processor against memory faults by error correction was not considered to be as important in the No. 2 Processor. Thus, the need to keep the cost down led to the choice of error detection *only*, instead of the more sophisticated Hamming correction code.

Error detection works as follows: One of the 22 bits in a word is allocated as a parity check bit. The program store contains both program and translation data. Additional protection is provided by using odd parity for program words and even parity for translation data. This parity scheme detects the possibility of accessing the translation data area of memory as instruction words. For example, a software error may cause the program to branch into the data section of the memory and execute the data words as instruction words. The parity check would detect this problem immediately. The program store includes checking circuits to detect multiple-word

access. Under program control, the sense amplifier threshold voltage can be varied in two discrete amounts from its nominal value to obtain a measure of the operating margin. The use of parity check was the proper choice for the No. 2 Processor in view of the high reliability of these memory devices.

The No. 2 Processor call store uses the same ferrite sheet memory modules as the No. 1 Processor. However, the No. 2 Processor's data word is 16 bits wide instead of 24. Fault detection depends heavily upon the matching of the call store inputs when the duplex processors run in the synchronous mode. Within the call store circuit, the access circuitry is checked to see that access currents flow in the right direction at the correct time and that only two access switches are selected in any store operation, ensuring that only one word is accessed in the memory operation. Similarly, threshold voltages of the sense amplifiers may be varied under program control to evaluate the operating margins of the store. No parity check bit is provided in the call store.

Each processor contains a program timer that is designed to back up other detection methods. Normally, the on-line processor clears the timer in both processors at prescribed intervals if the basic call processing program cycles correctly. If, however, a hardware or software trouble condition exists (for example, a program may go astray or a longer program loop may prevent the timer from being cleared), the timer will time out and automatically produce a switch. The new on-line processor is automatically forced to run an initialization restart program that attempts to establish a working system. System recovery is simplified by using two possible system configurations rather than the multi-unit duplex system.

The advent of silicon integrated circuits (ICs) in the mid-1960s provided the technological climate for dramatic miniaturization, improved performance, and cost-reduced hardware. The term *1A technology* refers to the standard set of IC devices, apparatus, and design tools that were used to design the No. 1A Processor and the No. 3A Processor [Becker et al., 1977]. The choice of technology and the scale of integration level were dictated by the technological advances made between 1968 and 1970. Small-scale integration (SSI), made possible by bipolar technology, was capable of high yield production. Because of the processor cycle time, high-speed logic gates with propagation delays from 5–10 nanoseconds were designed and developed concurrent with the No. 1A Processor.

#### No. 1A Processor

The No. 1A Processor, successor to the No. 1 Processor, was designed primarily for the control of large local and toll switches with high processing capabilities (the 1A ESS and 4ESS switches, respectively) [Budlong et al., 1977]. An important objective in developing the 1A ESS switch was to maintain commonality with the 1ESS switch. High capacity was achieved by implementing the new 1A integrated technology and a newly designed system structure. These changes made possible an instruction execution rate that is four to eight times faster than the No. 1 Processor. Compatibility with the 1ESS system also allows the No. 1A Processor to be retrofitted into an inservice 1ESS, replacing the No. 1 Processor when additional capacity is needed. The first 1A Processor was put into service in January, 1976, as control for a 4ESS toll switch in Chicago. Less than one year later, the first 1A ESS system was put into commercial operation. By 1988, about 2000 systems were in service.

The No. 1A Processor architecture is similar to its predecessor in that all of its subsystems have redundant units and are connected to the basic CC via redundant bus systems [Bowman et al., 1977]. One of the No. 1A Processor's major architectural differences is its program store

SECOND-GENERATION PROCESSORS

[Ault et al., 1977]. It has a writable RAM instead of PMT ROM. By combining disk memory and RAM, the system has the same amount of memory as a system with PMT, but at a lower cost. Backup copy of program and translation data is kept on disk. Other programs (e.g., diagnostics) are brought to RAM as needed; the same RAM spare is shared among different programs. More important is the system's ability to change the content of the store quickly and automatically. This ability considerably simplifies the administration and updating of program and translation information in working offices.

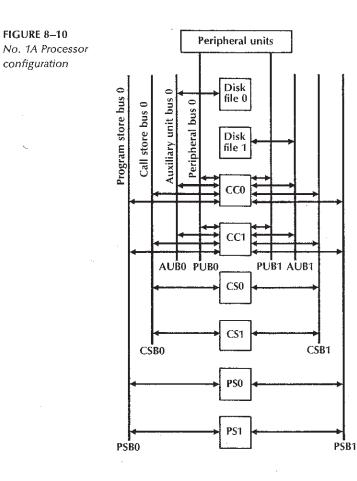

The additional disk (file store) subsystem adds flexibility to the No. 1A Processor [Ault et al., 1977], but it also increases the complexity of system recovery. Figure 8–10 shows the multi-unit duplex No. 1A Processor. This configuration is similar to the No. 1 Processor arrangement (see Figure 8–6) with a duplicated file store included. The file store communicates with the program store or call store via the CC and the auxiliary unit bus. This communication allows direct memory access between the file store and the program store or the call store. The disk file and the auxiliary unit bus are grouped together as a switchable entity.

Error detection is achieved by the duplicated and matched synchronous mode of operation, as in the No. 1 Processor. Both CCs operate in step and perform identical operations. The

matching is done more extensively in the 1A to obtain as complete a check as possible. There are two match circuits in each processor. Each matcher has the ability to compare 24 internal bits to 24 bits in its mate once every machine cycle. (A machine cycle is 700 nanoseconds.) Any one of 16 different 24-bit internal nodes can be selected for comparison. The choice is determined by the type of instruction that is being executed. Rather than compare the same nodes in both CCs, the on-line and the standby CCs are arranged to match different sets of data. Four distinct internal groups are matched in the same machine cycle to ensure the correct execution of any instruction.

The No. 1A Processor design is an improvement of the No. 1 Processor design. The No. 1A Processor incorporates much more checking hardware throughout various functional units, in addition to matching hardware. Checking hardware speeds up fault detection and also aids the fault recovery process by providing indications that help isolate the faulty unit. The matching is used in various modes for maintenance purposes. This capability provides powerful diagnostic tools in isolating faults.

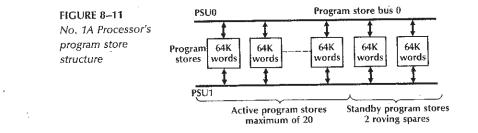

The program store and call store use the same hardware technology as in the No. 1 Processor. The CC contains approximately 50,000 logic gates. While the initial design of the stores called for core memories, they have been replaced with semiconductor dynamic MOS memories. The word size is 26 bits (24 data bits and 2 parity check bits). In the No. 1 Processor, the program store and the call store are fully duplicated. Because of their size, duplication requires a considerable amount of hardware, resulting in higher cost and increased component failures. To reduce the amount of hardware in the No. 1A Processor's store community, the memory is partitioned into blocks of 64K words, as shown in Figure 8-11. Two additional store blocks are provided as roving spares. If one of the program stores fails, a roving program store spare is substituted, and a copy of the program in the file store is transferred to the program store replacement. This type of redundancy has been made possible by the ability to regenerate data stored in a failing unit. Since a program store can be reloaded from the file store in less than a second, a roving spare redundancy plan is sufficient to meet the reliability requirement. As a result, Hamming correction code was not adopted in the No. 1A program store. However, it is essential that an error be detected quickly. Two parity check bits are generated over a partially overlapped, interleaved set of data bits and address. This overlapping is arranged to cope with particular memory circuit failures that may affect more than one bit of a word.

The 1A call stores contain both translation data backed up on the file stores and call-related transient data that are difficult to regenerate. The roving spare concept is expanded for the call stores to include sufficient spares to provide full duplication of transient data. If a fault occurs in a store that contains translation data, one of the duplicated stores containing transient call data is preempted and loaded with the necessary translation data from the duplicate in the file store. A parity check is done in the same manner as in the program store, using two check bits.

The combination of writable program store and file store provides a very effective and flexible system architecture for administrating and implementing a wide variety of features that are difficult to obtain in the 1ESS system. However, this architecture also complicates the process of fault recognition and recovery. Reconfiguration into a working system under trouble conditions is an extensive task, depending on the severity of the fault. (For example, it is possible for the processor to lose its sanity or ability to make proper decisions.) An autonomous hardware processor configuration (PC) circuit is provided in each CC to assist in assembling a working system. The PC circuit consists of various timers that ensure that the operational, fault recovery, and configuration programs are successfully executed. If these programs *are not* executed, the PC circuit controls the CC-to-program memory configuration, reloading program memory from file store when required, and isolating various subsystems from the CC until a working system is obtained.

547

#### No. 3A Processor

The No. 3A Processor was designed to control the small 3ESS switch [Irland and Stagg, 1974], which can handle from 500 to 5,000 lines. One of the major concerns in the design of this ESS was the cost of its processor. The low cost and high speed of integrated logic circuitry made it possible to design a cost-effective processor that performed better than its discrete component predecessor, the No. 2 Processor. The No. 3A project was started in early 1971. The first system cut into commercial service in late 1975.

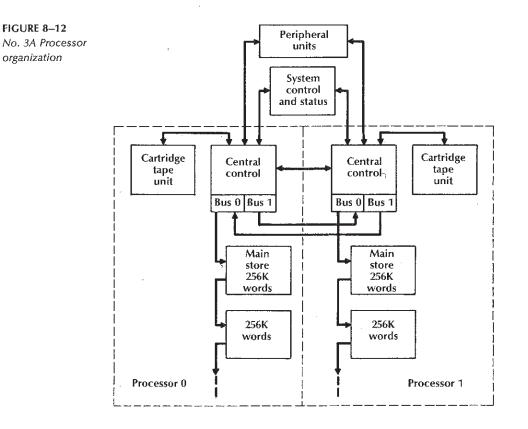

Because the number of components in the No. 3A Processor is considerably fewer than in the No. 1A Processor, all subsystems are fully duplicated, including the main store. The CC, the store bus, and the store are treated as a single switchable entity, rather than individual switchable units as in the No. 1A Processor. The system structure is similar to the 2ESS switch. Experience gained in the design and operation of the No. 2 provided valuable input for the No. 3 Processor design.

The 3A design makes one major departure from previous processor designs: It operates in the nonmatched mode of duplex operation. The primary purpose of matching is to detect errors. A mismatch, however, does not indicate *where* (in which one of the processors) the fault has occurred. A diagnostic fault-location program must be run to localize the trouble so that the defective unit can be taken off line. For this reason, the No. 3A Processor was designed to be self-checking, with detection circuitry incorporated as an integral part of the processor. Faults occurring during normal operation are discovered quickly by detecting hardware. Detection circuitry eliminates the need to run the standby system in the synchronous and match mode of operation or the need to run the fault recognition program to identify the defective unit when a mismatch occurs.

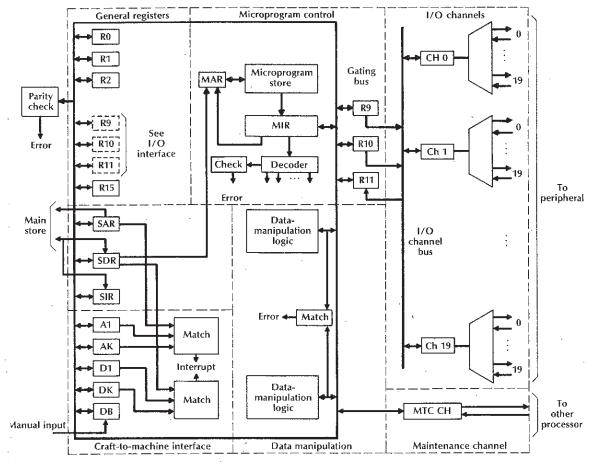

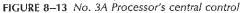

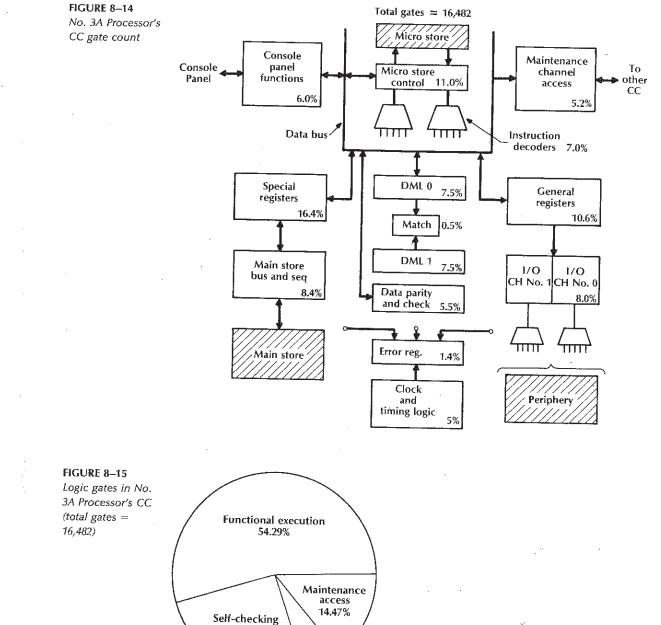

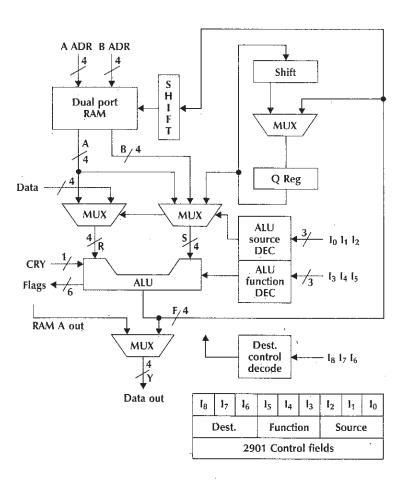

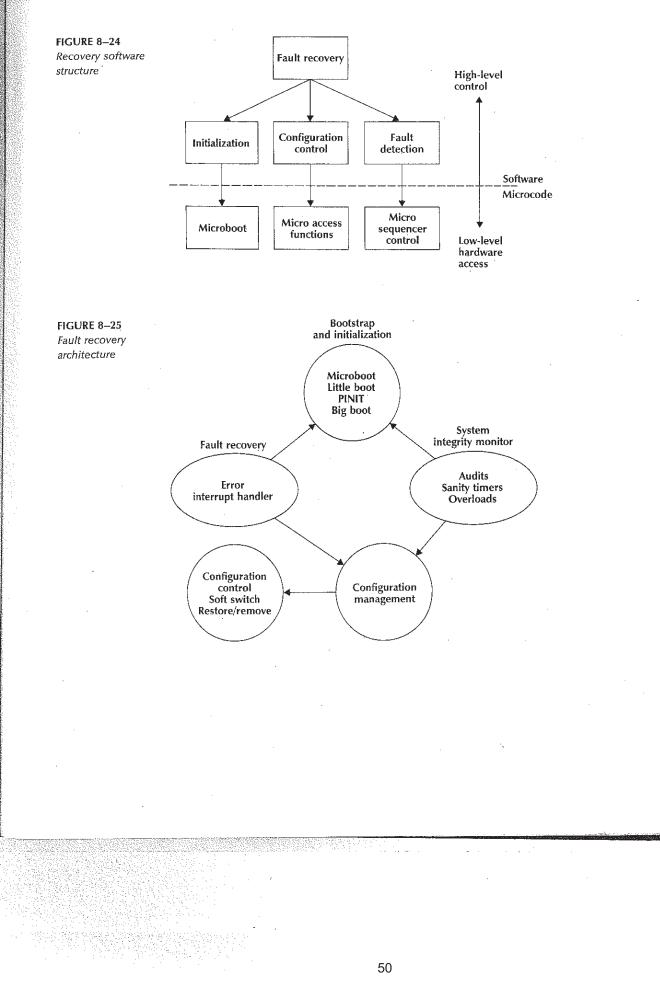

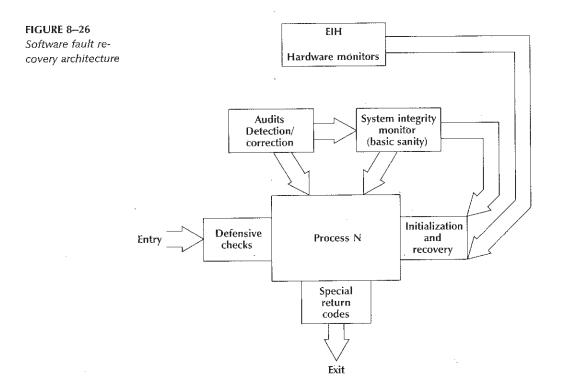

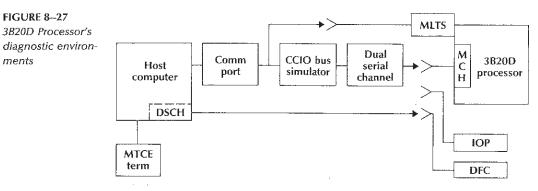

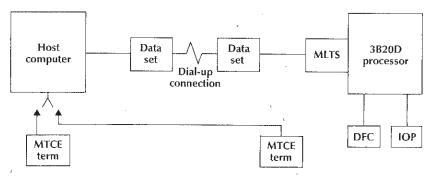

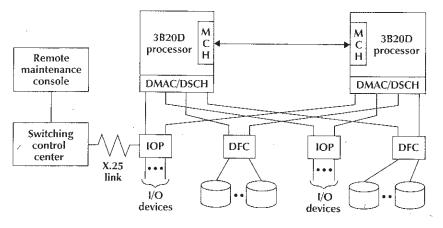

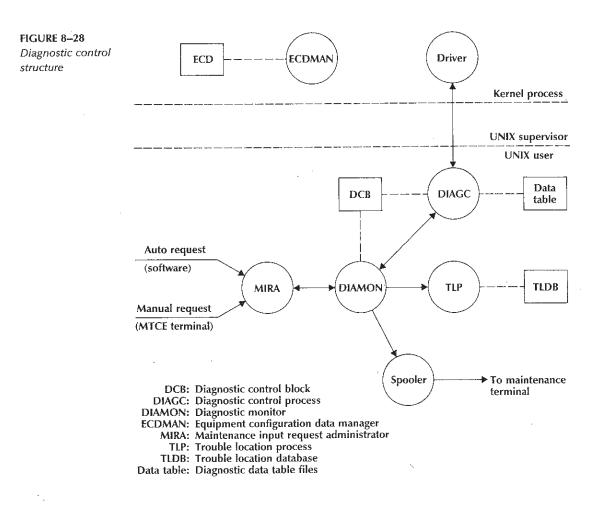

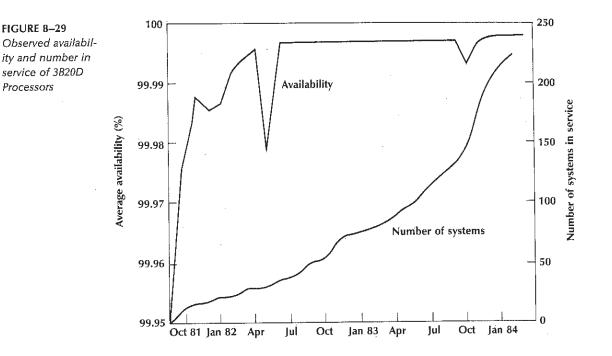

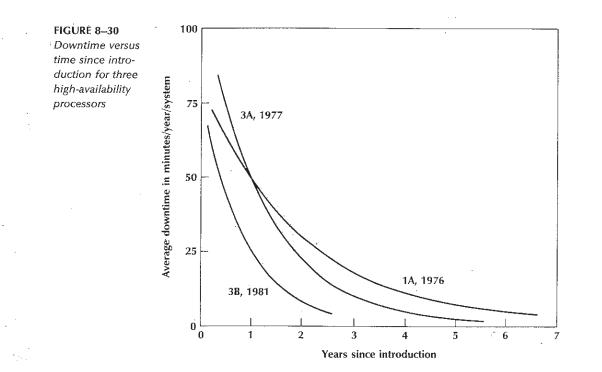

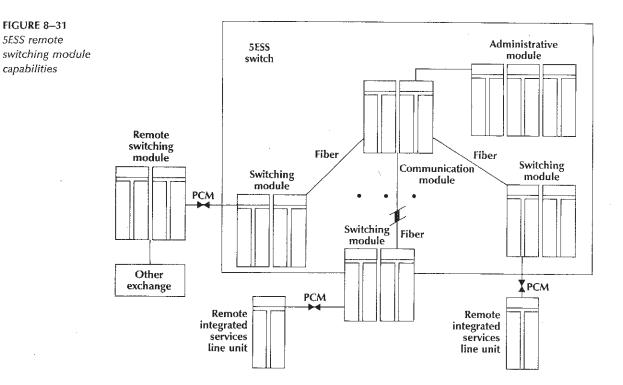

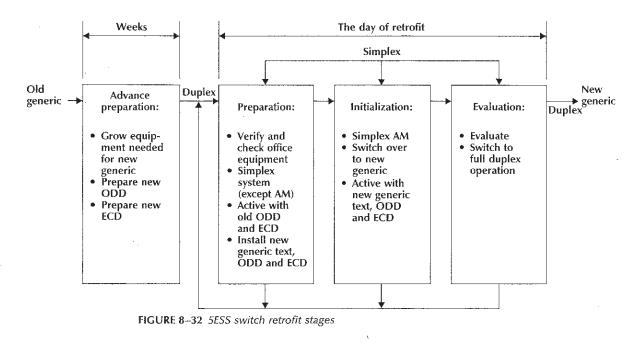

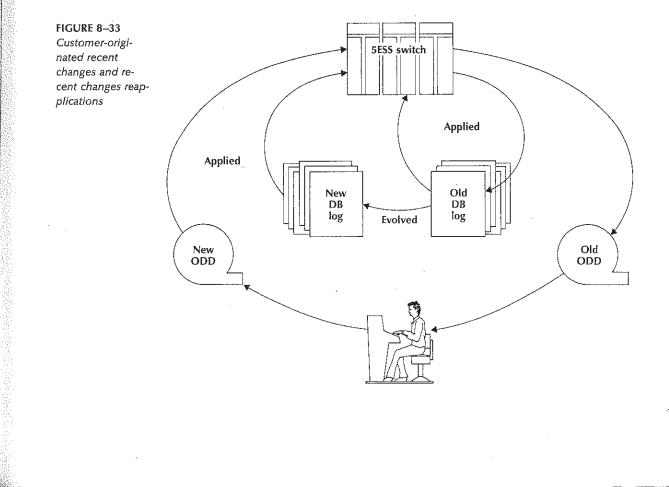

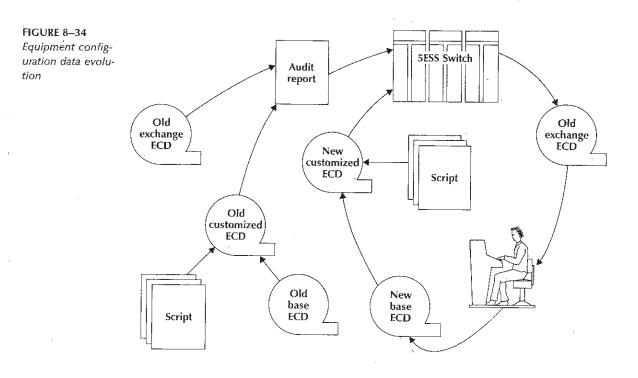

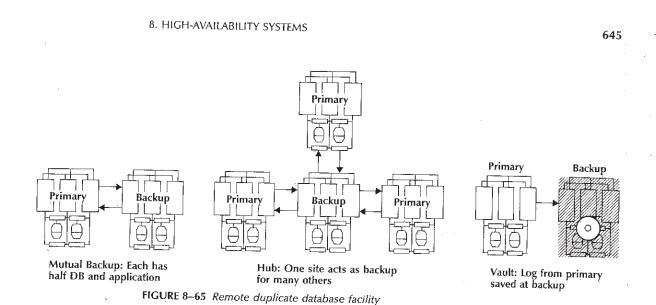

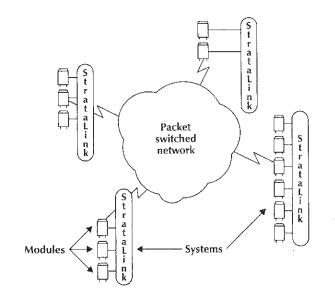

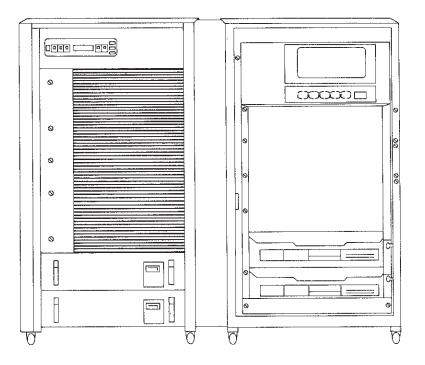

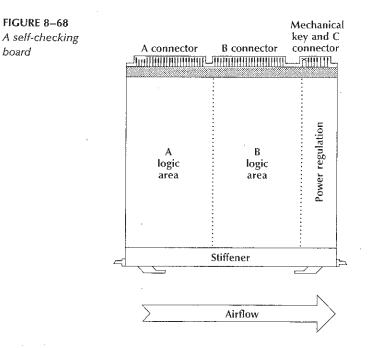

The synchronous and match mode arrangement of the No. 1 Processor and the No. 2 Processor provides excellent detection and coverage of faults. However, there are many instances (for example, periodic diagnostics, administration changes, recent change updates, and so on) when the system is not run in the normal match mode. Consequently, during these periods, the system is vulnerable to faults that may go undetected. The rapid advances in integrated circuit technology make possible the implementation of self-checking circuits in a cost-effective manner. Self-checking circuits eliminate the need for the synchronous and match mode of operation.