## United States Patent [19]

#### Rogers et al.

[11] Patent Number:

4,571,819

[45] Date of Patent:

Feb. 25, 1986

# [54] METHOD FOR FORMING TRENCH ISOLATION STRUCTURES

[75] Inventors: Steven H. Rogers, Midwest City,

Okla.; Randall S. Mundt, Colorado Springs; Denise A. Kaya, Woodland

Park, both of Colo.

[73] Assignee: NCR Corporation, Dayton, Ohio

[21] Appl. No.: 667,181

[22] Filed: Nov. 1, 1984

[51] Int. Cl.<sup>4</sup> ...... H01L 21/95 [52] U.S. Cl. ...... 29/576 W; 29/580;

148/1.5; 148/191; 148/DIG. 43; 148/DIG. 50; 148/DIG. 133; 357/49; 357/50; 357/54; 156/653; 427/93

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,104,086 | 8/1978  | Bondur et al   |         |          |

|-----------|---------|----------------|---------|----------|

| 4,356,211 | 10/1982 | Riseman .      |         |          |

| 4,396,460 | 8/1983  | Tamaki et al 2 | 9/576 W | / X      |

| 4,404,735 | 9/1983  | Sakurai .      |         |          |

| 4,506,434 | 3/1985  | Ogawa et al 2  | 9/576 W | / X      |

| 4,519,128 | 5/1985  | Chesebro et al | 357/49  | <b>X</b> |

#### FOREIGN PATENT DOCUMENTS

| 0113248 | 7/1982 | Japan       | 29/576 W |

|---------|--------|-------------|----------|

| 0050540 | 3/1984 | Japan       | 29/576 W |

| 8200782 | 9/1983 | Netherlands | 29/576 W |

#### OTHER PUBLICATIONS

Abbas, S. A., "Recessed Oxide Isolation Process" in *IBM Technical Disclosure Bulletin*, vol. 20, No. 1, Jun. 1977, pp. 144–145.

Rung et al., "Deep Trench Isolated CMOS Devices", IEDM 82, pp. 237-240.

Kurosawa et al., "A New Bird's-Beak Free Field Isolation Technology for VLSI Devices", IEDM 81, pp. 384-387.

Primary Examiner—Brian E. Hearn Assistant Examiner—Alan E. Schiavelli Attorney, Agent, or Firm—Wilbert Hawk, Jr.; Casimer K. Salys

#### [57] ABSTRACT

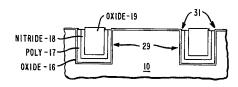

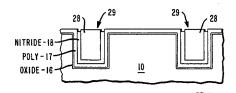

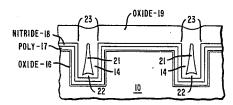

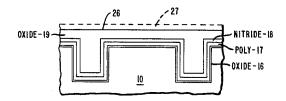

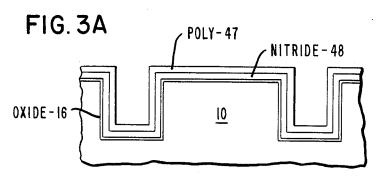

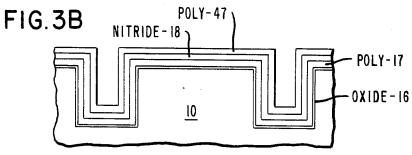

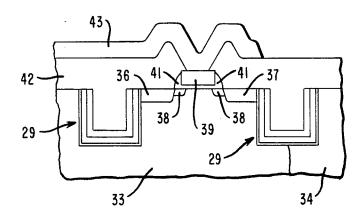

A method for forming trench isolation oxide using doped silicon dioxide which is reflowed at elevated temperatures to collapse any voids therein and produce surface planarity. An underlying layered composite selected from oxide, polysilicon and silicon nitride permits the formation and reflow of the doped isolation oxide and remains in place in the trench to contribute to the trench isolation structure.

#### 16 Claims, 10 Drawing Figures

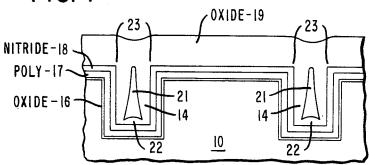

FIG.4

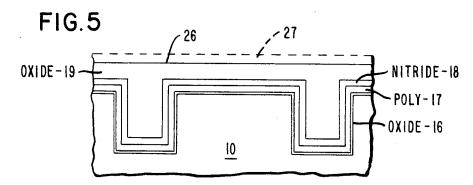

FIG. 6

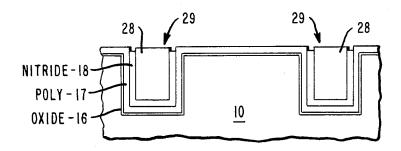

FIG. 7

NITRIDE - 18

POLY - 17

OXIDE - 16

10

FIG.8

## METHOD FOR FORMING TRENCH ISOLATION STRUCTURES

#### BACKGROUND OF THE INVENTION

This invention relates to techniques for electrically isolating semiconductor devices and components in monolithic integrated circuits. In particular, the invention is a method for forming void-free, planarized dielectric trench structures. The method uses doped oxide reflow to provide a void-free planar isolation layer and a multiple underlayer which functions as an etch stop and dopant/oxidation barrier.

Dielectric isolation techniques have been the preferred technology for isolating integrated circuits and 15 their constituent devices and elements, at least in part because of the ability to closely pack the isolation dielectric and the circuit elements. Integrated circuit isolation by the so-called local oxidation of silicon (LOCOS) has been known for a number of years, as 20 have the attendant problems. The well-known limitations of the LOCOS process include at least three factors which may constrain the process from applicability to future small geometry, highly dense LSI and VLSI structures. These limitations are, first, the formation of 25 the so-called bird's beak oxide configuration and the associated encroachment of the field oxide beneath the oxidation mask. Encroachment by the bird's beak oxide limits the percentage of chip surface area which is available for device formation. Secondly, the limited thick- 30 ness results in undesirably high circuit capacitances. Third, the characteristic non-planar surface topography makes it difficult to perform the increasingly high resolution photolithographic operations which are required to fabricate VSLI circuits. In turn, the decreased resolu- 35 tion increases the minimum feature sizes and minimum tolerances and, as a consequence, decreases the achievable device densities.

The use of LOCOS isolation has persisted, however, because of the past shortcomings of the available substi- 40 tute isolation technologies. Typical trench isolation processes involve etching grooves about 1 to 6 microns deep into the semiconductor substrate, filling the grooves with a suitable dielectric and performing a planarization operation. The dielectric material typi- 45 cally is undoped silicon dioxide or polysilicon. Typical prior art approaches are discussed, for example, in Rung, Momose and Nagakubo, "Deep Trench Isolated CMOS Devices", IEDM 82, pp. 237-240. The Rung et al. article discusses a trench isolation process which 50 involves oxidizing the silicon substrate trench sidewalls, filling the trench with polysilicon or deposited oxide, etching the poly/oxide, then capping the structure with oxide. Another typical trench isolation approach is described in the article "A New Bird's-Beak Free Field 55 Isolation Technology For VLSI Devices", by Kurosawa, Shibata and Iizuka, IEDM 81, pp. 384-387. The Kurosawa et al. technique involves the selective etching of stressed silicon dioxide following confomal deposition, combined with a lift-off of the silicon diox- 60 ide over the active regions.

In particular, trench isolation technology has the inherent potential advantages of small width-to-depth ratios, relative process simplicity, well-defined vertical-wall isolation regions and surface planarity. Like other 65 VSLI features, however, the width of isolation trenches must be scaled downward to near micron and even submicron size to achieve the densities required in

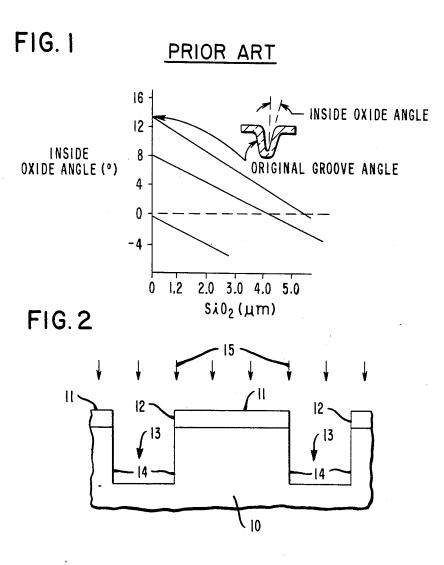

VSLI and future monolithic integrated circuit technologies. Unfortunately, it becomes increasingly difficult to completely fill the narrow, yet relatively deep trench configurations which are used for VSLI isolation. The resulting tendency to form voids is well-known and is shown, for example, by the data of Bondur et al, U.S. Pat. No. 4,104,086. Bondur et al. discloses a process for eliminating voids by precisely tapering the walls of the trenches, which tapers vary in relation to the sizes of the trenches. FIG. 1 illustrates the data of Bondur et al., which show that for vertical side wall trenches, the deposited silicon dioxide forms negative sloping side walls and, thus, voids.

Several approaches have been proposed which have as their purpose the control or elimination of such voids.

For example, Riseman, U.S. Pat. No. 4,356,211, forms a composite dual-oxide trench isolation structure in which a first oxide layer is formed, then a layer of polysilicon is deposited, anisotrophically etched, and heavily doped at the upper edge of the trench to accelerate silicon dioxide formation at such upper edge. Thereby the voids are sealed by the differential oxidation rate of the polysilicon. Clearly the parameters of the Riseman process do not provide for applications in which trenches of varying dimension are being processed simultaneously.

The above-mentioned Bondur et al. U.S. Pat. No. 4,104,086 uses tapered trench sidewalls to control the depth of isolation oxide voids relative to the substrate surface in a silicon substrate which has a highly doped near-surface region. Briefly, the Bondur et al process involves (1) forming the trench to a tapered profile, as by the use of reactive ion etching (RIE); (2) growing a thin layer of thermal oxide in the trench outline; (3) depositing CVD oxide; (4) etching back the CVD oxide using RIE; and (5) optionally, annealing in steam at 900° to 950° C. to enhance the "quality" of the silicon dioxide. The data disclosed in the Bondur et al patent indicate the vertical walls (which, of course, are desirable for density and resolution) inherently product voids in the deposited silicon oxide (see FIG. 1 herein). Also, the voids are buried deeper in the oxide relative to the substrate surface as the trench width increases and the taper increases. Conversely, the voids are formed closer to the surface and to exposure by the planarization etch-back in the case of narrower, vertical grooves.

Sakurai, U.S. Pat. No. 4,404,735, discloses a process for forming trench isolation structures. Initially, dry etching such as plasma etching, reactive sputter etching or ion beam etching is used for form the trench. The trench is then covered with a thin layer of deposited silicon dioxide which is formed to a thickness of between 500 to 1,000 angstroms to prevent substrate heating by the subsequent laser reflow process, prevent doping of the substrate from the isolation layer, and to isolate the silicon isolation layer from the substrate. Next, a CVD layer is formed to a thickness which is less than the trench depth and less than one-half the trench width using silicon or doped glass (phosphosilicate glass, PSG). The PSG/silicon is subsequently reflowed by laser heating. Essentially, the Sakurai process is a laser reflow process for filling narrow trenches from a thin silicon or PSG layer. In other words, the trenchfilling layer is formed to an initial shallow thickness within the trench and laser heating is used to redistribute material from outside the trenches into the trenches.

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.