## Petitioner's Exhibit CSC 1014

Petitioner Cypress Semiconductor Corp. - Ex. CSC 1014, p. 1

Executive Editor: Dan Joraanstad Sponsoring Editor: Jennifer Young Developmental Editor: Jamie Spencer Editorial Assistant: Laura Cheu Marketing Manager: Mary Tudor Production Editors: Megan Rundel, Brian Jones Text and Cover Design: Rob Hugel, XXX Design Copyeditor: Mary Prescott Proofreader: Elizabeth Wiltsee Illustrations: Rolin Graphics Inc. Indexer: Ira Kleinberg Composition: Rad Proctor, Proctor-Willenbacher Film: The Courier Connection Cover Printer: New England Book Components, Inc. Text Printer and Binder: Courier/Westford Senior Manufacturing Coordinator: Merry Free Osborn

The cover illustration is a reproduction of "Décalcomanie" by the twentieth-century Belgian surrealist painter René Magritte. We chose this particular painting by the author's favorite painter to reflect the duality of computer design. "Décalcomanie" © 1992 C. Herscovici/ARS, New York.

Copyright © 1994 by The Benjamin/Cummings Publishing Company, Inc.

All rights reserved. No part of this publication may be reproduced, stored in a database or retrieval system, distributed, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America. Published simultaneously in Canada.

## Library of Congress Cataloging-in-Publication Data

Katz, Randy H., 1955–

Contemporary logic design / Randy H. Katz. p. cm.

Includes bibliographical references and index. ISBN 0-8053-2703-7

1. Electronic digital computers—Circuits—Design. 2. Integrated circuits— Very large scale integration—Design—Data processing. 3. Logic design—Data processing. 4. Computer-aided design. I. Title. TK7888.4.K36 1994

93-9013

CIP

621.39'5-dc20

ISBN 0-8053-2703-7

3 4 5 6 7 8 9 10-CRW-999897969594

The Benjamin/Cummings Publishing Company, Inc. 390 Bridge Parkway Redwood City, California 94065

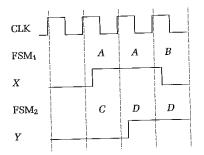

Figure 8.8 State and output changes associated with the FSM fragments of Figure 8.7.

Now that Y is 1,  $FSM_1$  goes to state B on the next rising edge. In this state, it will output a 0, but this is too late to affect  $FSM_2$ 's state change. It remains in state D.

## 8.2 Basic Design Approach

The counter design procedure presented in the last chapter forms the core of a more general procedure for arbitrary finite state machines. You will discover that the procedure must be significantly extended for the general case.

## 8.2.1 Finite State Machine Design Procedure

**Step 1**: Understand the problem. A finite state machine is often described in terms of an English-language specification of its behavior. It is important that you interpret this description in an unambiguous manner. For counters, it is sufficient simply to enumerate the sequence. For finite state machines, try some input sequences to be sure you understand the conditions under which the various outputs are generated.

**Step 2**: Obtain an abstract representation of the FSM. Once you understand the problem, you must place it in a form that is easy to manipulate by the procedures for implementing the finite state machine. A state diagram is one possibility. Other representations, to be introduced in the next section, include algorithmic state machines and specifications in hardware description languages.

Step 3: Perform state minimization. Step 2, deriving the abstract representation, often results in a description that has too many states. Certain paths through the state machine can be eliminated because their input/output behavior is duplicated by other function-

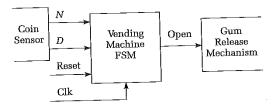

Figure 8.9 Vending machine block diagram.

the customer? Sometimes we have to make reasonable assumptions. For the first question, we assume that the coin sensor returns any coins it does not recognize, leaving N and D unasserted. For the latter, we assume that external logic resets the machine after the gum is delivered.

**Abstract Representations** Once you understand the behavior reasonably well, it is time to map the specification into a more suitable abstract representation. A good way to begin is by enumerating the possible unique sequences of inputs or configurations of the system. These will help define the states of the finite state machine.

For this problem, it is not too difficult to enumerate all the possible input sequences that lead to releasing the gum:

Three nickels in sequence: N, N, N

Two nickels followed by a dime: N, N, D

A nickel followed by a dime: N, D

A dime followed by a nickel: D, N

Two dimes in sequence: D, D

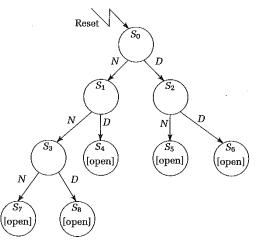

This can be represented as a state diagram, as shown in Figure 8.10. For example, the machine will pass through the states  $S_0$ ,  $S_1$ ,  $S_3$ ,  $S_7$  if the input sequence is three nickels.

To keep the state diagram simple and readable, we include only transitions that explicitly cause a state change. For example, in state  $S_0$ , if neither input N or D is asserted, we assume the machine remains in state  $S_0$  (the specification allows us to assume that N and D are never asserted at the same time). Also, we include the output Open only in states in which it is asserted. Open is implicitly unasserted in any other state.

**State Minimization** This nine-state description isn't the "best" possible. For one thing, since states  $S_4$ ,  $S_5$ ,  $S_6$ ,  $S_7$ , and  $S_8$  have identical behavior, they can be combined into a single state.

To reduce the number of states even further, we can think of each state as representing the amount of money received so far. For example,

Figure 8.10 Vending machine state diagram.

it shouldn't matter whether the state representing 10 cents was reached through two nickels or one dime.

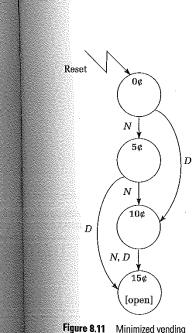

A state diagram derived in this way is shown in Figure 8.11. We capture the behavior in only four states, compared with nine in Figure 8.10. Also, as another illustration of a useful shorthand, notice the transition from state  $10 \notin$  to  $15 \notin$ . We interpret the notation "N, D" associated with this transition as "go to state  $15 \notin$  if N is asserted OR D is asserted."

In the next chapter, we will examine formal methods for finding a state diagram with the minimum number of states. The process of minimizing the states in a finite state machine description is called *state minimization*.

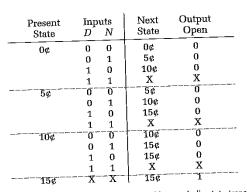

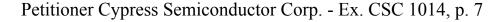

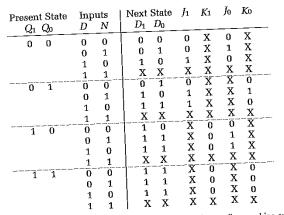

**State Encoding** At this point, we have a finite state machine with a minimum number of states, but it is still symbolic. See Figure 8.12 for the symbolic state transition table. The next step is *state encoding*.

The way you encode the state can have a major effect on the amount of hardware you need to implement the machine. A natural state assignment would encode the states in 2 bits: state  $0\phi$  as 00, state  $5\phi$  as 01, state  $10\phi$  as 10, and state  $15\phi$  as 11. A less obvious assignment could lead to reduced hardware. The *encoded* state transition table is shown in Figure 8.13.

In Chapter 9 we present a variety of methods and computer-based tools for finding an effective state encoding.

**Implementation** The next step is to implement the state transition table after choosing storage elements. We will look at implementations based on D and J-K flip-flops.

or it

we d.

bly

act ble rill

ble

.10.

l<sub>7</sub> if

nsi-

ther

(the

the

it is

ible.

vior,

each

iple,

rigure 8.11 Minimized vending machine state diagram.

Figure 8.12 Minimized vending machine symbolic state transition table.

| Present State<br>Q1 Q0 | Inp<br>D         | uts<br>N | Next State<br>D <sub>1</sub> D <sub>0</sub> | Output<br>Open |

|------------------------|------------------|----------|---------------------------------------------|----------------|

| 0 0                    | 0                | 0        | 0 0                                         | 0              |

| 0 0                    | õ                | 1        | 0 1                                         | 0              |

|                        | 1                | Ô        | 1 0                                         | 0              |

|                        | 1                | 1        | XX                                          | Х              |

|                        | -1               | <u>σ</u> | 01                                          | 0              |

| <u>ч</u>               | ŏ                | 1        | 1 0                                         | 0              |

|                        | 1                | ō        | 1 1                                         | 0              |

|                        | î                | 1        | ХХ                                          | х              |

|                        | - <del>0</del> - | <u>n</u> | 110                                         | <u>0</u>       |

|                        | õ                | 1        | 1 1                                         | 0              |

|                        | ĭ                | ō        | 1 1                                         | 0              |

|                        | 1                | 1        | X X                                         | х              |

| 1-1                    | ô-               |          | 11                                          | 1              |

| 1 1 .                  | ŏ                | 1        | 1 1                                         | 1              |

|                        | 1                | ō        | 1 1                                         | 1              |

|                        | 1                | 1        | X X                                         | Х              |

|                        |                  | -        |                                             |                |

Figure 8.13 Encoded vending machine state transition table.

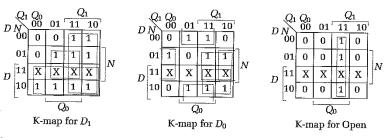

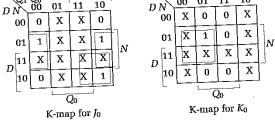

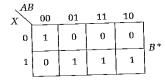

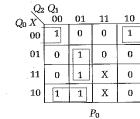

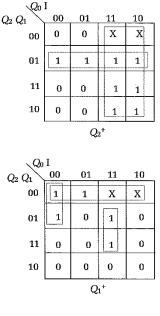

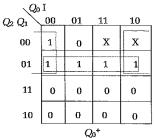

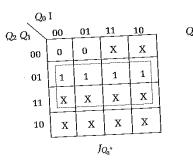

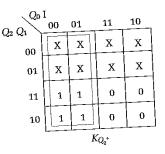

The K-maps for the D flip-flop implementation are shown in Figure 8.14. We filled these in directly from the encoded state transition table. The minimized equations for the flip-flop inputs and the output become

$$\begin{split} D_1 &= Q_1 + D + Q_0 \bullet N \\ D_0 &= N \bullet \overline{Q}_0 + Q_0 \bullet \overline{N} + Q_1 \bullet N + Q_1 \bullet D \\ \text{OPEN} &= Q_1 \bullet Q_0 \end{split}$$

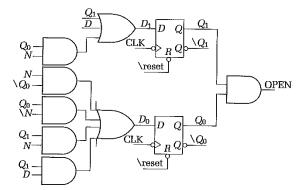

The logic implementation is shown in Figure 8.15. It uses eight gates and two flip-flops.

8.2 Basic Design Approach 393

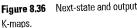

Figure 8.14 K-maps for D flip-flop implementation of vending machine.

Figure 8.15 Vending machine FSM implementation based on D flip-flops.

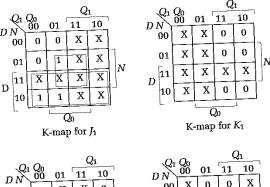

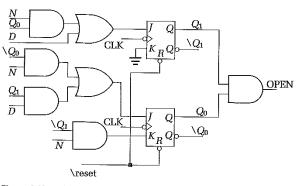

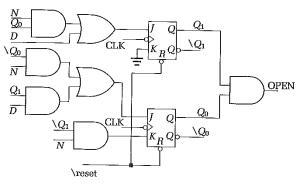

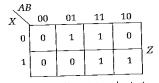

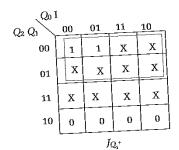

To implement the state machine using J-K flip-flops, we must remap the next-state functions as in Chapter 7. The remapped state transition table for J-K flip-flop implementation is shown in Figure 8.16. We give the K-maps derived from this table in Figure 8.17. The minimized equations for the flip-flop inputs become

$$J_1 = D + Q_0 \bullet N \qquad K_1 = 0$$

$$J_0 = \overline{Q}_0 \bullet N + Q_1 \bullet D \qquad K_0 = \overline{Q}_1 \bullet N$$

Figure 8.18 shows the logic implementation. Using J-K flip-flops moderately reduced the hardware: seven gates and two flip-flops.

**Discussion** We briefly described the complete finite state machine design process and illustrated it by designing a simple vending machine controller. Starting with an English-language statement of the task, we first described the machine in a more formal representation. In this case, we used state diagrams.

Figure 8.16 Remapped next-state functions for the vending machine example.

Figure 8.17 K-maps for *J-K* flip-flop implementation of vending machine.

Since more than one state diagram can lead to the same input/output behavior, it is important to find a description with as few states as possible. This usually reduces the implementation complexity of the finite state machine. For example, the state diagram of Figure 8.10 contains nine states and requires four flip-flops for its implementation. The minimized state

## 8.3 Alternative State Machine Representations 395

**Figure 8.18** *J-K* flip-flop implementation for the vending machine example,

diagram of Figure 8.11 has four states and can be implemented with only two flip-flops.

Once we have obtained a minimum finite state description, the next step is to choose a good encoding of the states. The right choice can further reduce the logic for the next-state and output functions. In the example, we used only the most obvious state assignment.

The final step is to choose a flip-flop type for the state registers. In the example, the implementation based on D flip-flops was more straightforward. We did not need to remap the flip-flop inputs, but we used more gates than the *J-K* flip-flop implementation. This is usually the case.

Now we are ready to examine some alternatives to the state diagram for describing finite state machine behavior.

## 8.3 Alternative State Machine Representations

it

e.

1-35

te

You have already seen how to describe finite state machines in terms of state diagrams and tables. However, it can be difficult to describe complex finite state machines in this way. Recently, hardware designers have shifted toward using alternative representations of FSM behavior that look more like software descriptions. In this section, we introduce algorithmic state machine (ASM) notation and hardware description languages (HDLs). ASMs are similar to program flowcharts, but they have a more rigorous concept of timing. HDLs look much like modern programming languages, but they explicitly support computations that can occur in parallel.

You may wonder what is wrong with state diagrams. The problem is that they do not adequately capture the notion of an *algorithm*—a welldefined sequence of steps that produce a desired sequence of actions based on input data. State diagrams are weak at capturing the structure behind complex sequencing. The representations discussed next do a better job of making this sequencing structure explicit.

8.3 Alternative State Machine Representations

Figure 8.18 J-K flip-flop implementation for the vending machine example.

diagram of Figure 8.11 has four states and can be implemented with only two flip-flops.

Once we have obtained a minimum finite state description, the next step is to choose a good encoding of the states. The right choice can further reduce the logic for the next-state and output functions. In the example, we used only the most obvious state assignment.

The final step is to choose a flip-flop type for the state registers. In the example, the implementation based on D flip-flops was more straightforward. We did not need to remap the flip-flop inputs, but we used more gates than the J-K flip-flop implementation. This is usually the case.

Now we are ready to examine some alternatives to the state diagram for describing finite state machine behavior.

#### 8.3 Alternative State Machine Representations

You have already seen how to describe finite state machines in terms of state diagrams and tables. However, it can be difficult to describe complex finite state machines in this way. Recently, hardware designers have shifted toward using alternative representations of FSM behavior that look more like software descriptions. In this section, we introduce algorithmic state machine (ASM) notation and hardware description languages (HDLs). ASMs are similar to program flowcharts, but they have a more rigorous concept of timing. HDLs look much like modern programming languages, but they explicitly support computations that can occur in parallel.

You may wonder what is wrong with state diagrams. The problem is that they do not adequately capture the notion of an algorithm—a welldefined sequence of steps that produce a desired sequence of actions based on input data. State diagrams are weak at capturing the structure behind complex sequencing. The representations discussed next do a better job of making this sequencing structure explicit.

Petitioner Cypress Semiconductor Corp. - Ex. CSC 1014, p. 10

#### Algorithmic State Machine Notation 8.3.1

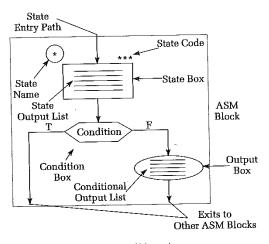

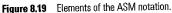

The ASM notation consists of three primitive elements: the state box, the decision box, and the output box, as shown in Figure 8.19. Each major unit, called an ASM block, consists of a state box and, optionally, a network of condition and output boxes. A state machine is in exactly one state or ASM block during the stable portion of the state time.

State Boxes There is one state box per ASM block, reached from other ASM blocks through a single state entry path. In addition, for each combination of inputs there is a single unambiguous exit path from the ASM block. The state box is identified by a symbolic state name—in a circle-and a binary-encoded state code, and it contains an output signal list.

The output list describes the signals that are asserted whenever the state is entered. Because signals may be expressed in either positive or negative logic, it is customary to place an "L." or "H." prefix before the signal name, indicating whether it is asserted low or high. You can also specify whether the signal is asserted immediately (I) or is delayed (no special prefix) until the next clocking event. A signal not mentioned in the output list is left unasserted.

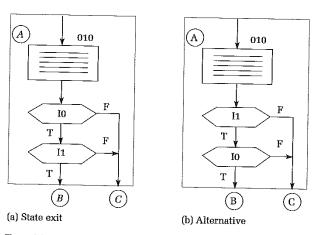

Condition Boxes The condition box tests an input to determine an exit path from the current ASM block to the block to be entered next. The order in which condition boxes are cascaded has no effect on the determination of the next ASM block. Figure 8.20(a) and (b) show functionally equivalent ASM blocks: state B is to be entered next if  $I_0$  and  $I_1$  are both 1; otherwise state C is next.

## 8.3 Alternative State Machine Representations 397

**Output Boxes** Any output boxes on the path from the state box to an exit contain signals that should be asserted along with the signals mentioned in the state box. The state machine advances from one state to the next in discrete rather than continuous steps. In this sense, ASM charts have different timing semantics than program flowcharts.

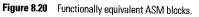

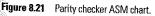

**Example The Parity Checker** As an example, we give the parity checker's ASM chart in Figure 8.21. It consists of two states, Even and Odd, encoded as 0 and 1, respectively. The input is the single bit X; the output is the single bit Z, asserted high when the finite state machine is in the Odd state.

We can derive the state transition table from the ASM chart. We simply list all the possible transition paths from one state to another and the input combinations that cause the transition to take place. For example, in state Even, when the input is 1, we go to state Odd. Otherwise we stay in state Even. For state Odd, if the input is 1, we advance to Even. Otherwise we remain in state Odd. The output Z is asserted only in state Odd. The transition table becomes:

| Input X | Present State | Next State | Output Z     |

|---------|---------------|------------|--------------|

| F       | Even          | Even       | Not asserted |

| Т       | Even          | Odd        | Not asserted |

| F       | Odd           | Odd        | Asserted     |

| Т       | Odd           | Even       | Asserted     |

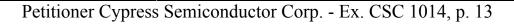

Figure 8.22 Vending machine ASM chart.

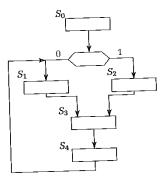

**Example Vending Machine Controller** We show the ASM chart for the vending machine in Figure 8.22. To extract the state transition table, we simply examine all exit paths from each state. For example, in the state  $0\phi$ , we advance to state  $10\phi$  when input *D* is asserted. If *N* is asserted, we go to state  $5\phi$ . Otherwise, we stay in state  $0\phi$ . The rest of the table can be determined by looking at the remaining states in turn.

## 8.3.2 Hardware Description Languages: VHDL

Hardware description languages provide another way to specify finite state machine behavior. Such descriptions bear some resemblance to a program written in a modern structured programming language. But again, the concept of timing is radically different from that in a program written in a sequential programming language. Unlike state diagrams or ASM charts, specifications in a hardware description language can actually be simulated. They are executable descriptions that can be used to verify that the digital system they describe behaves as expected.

VHDL (VHSIC hardware description language) is an industry standard. Although its basic concepts are relatively straightforward, its detailed

#### 8.3 Alternative State Machine Representations 399

syntax is beyond the scope of this text. However, we can illustrate its capabilities for describing finite state machines by examining a description of the parity checker written in VHDL:

```

ENTITY parity_checker IS

PORT (

x, clk: IN BIT;

z: OUT BIT);

END parity_checker;

ARCHITECTURE behavioral OF parity_checker IS

BEGIN

main: BLOCK (clk = '1' and not clk'STABLE)

TYPE state IS (Even, Odd);

SIGNAL state_register: state := Even;

BEGIN state_even:

BLOCK ((state_register = Even) AND GUARD)

BEGIN

state_register <= Odd WHEN x = '1'</pre>

ELSE Even

END BLOCK state_even;

BEGIN state_odd:

BLOCK ((state_register = Odd) AND GUARD)

BEGIN

state_register <= Even WHEN x = '1'

ELSE Odd;

END BLOCK state_odd;

z <= 'O' WHEN state_register = Even ELSE

'1' WHEN state_register = Odd;

END BLOCK main;

END behavioral;

```

Every VHDL description has two components: an *interface description* and an *architectural body*. The former defines the input and output connections or "ports" to the hardware entity being designed; the latter describes the entity's behavior.

The architecture block defines the behavior of the finite state machine. The values the *state register* can take on are defined by the type *state*, consisting of the symbols *Even* and *Odd*. We write VHDL statements that assign new values to the state register and the output Z, depending on the current value of input X, whenever we detect a rising clock edge.

Checking for events like a clock transition is handled through the VHDL concept of the *guard*, an expression that enables certain statements in the description when it evaluates to true. For example, the expression

## clk = '1' and not clk'stable

is a guard that evaluates to true whenever the clock signal has recently undergone a 0-to-1 transition. The main block is enabled for evaluation when this particular guard becomes true.

The description contains two subblocks, *state\_even* and *state\_odd*, that are enabled whenever the main guard is true and the machine is in the indicated state. Within each subblock, the state register receives a new assignment depending on the value of the input. Outside the subblocks, the output becomes 0 when the machine enters state Even and 1 when it enters state Odd.

## 8.3.3 ABEL Hardware Description Language

ABEL is a hardware description language closely tied to the specification of programmable logic components. It is also an industry standard and enjoys widespread use. The language is suitable for describing either combinational or sequential logic and supports hardware specification in terms of Boolean equations, truth tables, or state diagram descriptions. Although the detailed syntax and semantics of the language are beyond our scope, we can highlight its features with the parity checker finite state machine.

Let's look at the ABEL description of the parity checker:

```

module parity

title 'odd parity checker state machine

Joe Engineer, Itty Bity Machines, Inc.'

'p22v10';

device

u1

"Input Pins

clk, X, RESET pin 1, 2, 3;

"Output Pins

pin 21, 22;

Q,Z

istype 'pos,reg';

Q,Z

"State registers

SREG = [Q, Z];

EVEN = EO, OJ; "even number of O's

= [1, 1]; " odd number of O's

ODD

```

8.3 Alternative State Machine Representations 401

```

equations

[Q.ar, Z.ar] = RESET;"Reset to state $0

state_diagram SREG

state EVEN:

if X then ODD

else EVEN;

state ODD:

if X then EVEN

else ODD;

test_vectors (Eclk, RESET, X] -> ESREG])

EO,1,.X.] -> EEVEN];

E.C., 0, 13 -> CODD];

E.C.,0,13 -> EEVEN3;

E.C.,0,13 -> EODD3;

E.C.,0,0] -> EODD];

C.C.,0,13 -> EEVEN3;

E.C.,0,13 -> EODD3;

E.C.,0,0] -> EODD];

E.C.,0,0] -> EODD];

E.C.,0,0] -> EODD];

```

end parity;

An ABEL description consists of several sections: module, title, descriptions, equations, truth tables, state diagrams, and test vectors, some of which are optional. Every ABEL description begins with a module statement and an optional title statement. These name the module and provide some basic documentation about its function.

These are followed by the description section. The elements of this section are the kind of device being programmed, the specification of inputs and outputs, and the declaration of which signals constitute the state of the finite state machine.

We must first describe the device selected for the implementation. It is a P22V10 PAL, with 12 inputs, 10 outputs, and embedded flip-flops associated with the outputs. For identification within the schematic, we call the device u1.

Next come the pin descriptions. The finite state machine's inputs are the clock clk, data X, and the *RESET* signal. The outputs are the state Q and the output Z. These are assigned to specific pins on the PAL. For example, pin 1 is connected to the clock inputs of the internal flip-flops.

Many of the attributes of a PAL are selectable, so the description may need to make explicit choices. The next line of the description tells ABEL that Q and Z are POSitive logic outputs of the PAL's internal flipflops (REG) associated with particular output pins. The P22V10 PAL

also supports negative logic outputs as well as outputs that bypass the internal flip-flops.

The state of the finite state machine is represented by the outputs Q and Z. EVEN is defined as the state where Q and Z are 0. ODD is defined as the state where Q and Z are 1.

The equation section defines outputs in terms of Boolean equations of the inputs. In this case, the asynchronous reset (.ar) inputs of the Qand Z flip-flops are driven high when the RESET signal is asserted.

The state\_diagram section describes the transitions among states using a programming language-like syntax. If we are in EVEN and the input X is asserted, we change to ODD. Otherwise we stay in EVEN. Similarly, if we are in ODD and X is asserted, we return to EVEN. Otherwise we stay in state ODD. ABEL supports a variety of control constructs, including such things as case statements.

The final section in this example is for  $test\_vectors$ . This is a tabular listing of the expected input/output behavior of the finite state machine. The first entry describes what happens when RESET is asserted: independent of the current value of X, the machine is forced to EVEN. The rest of the entries describe the state sequence for the input string 111011000. The ABEL system simulates the description to ensure that the behavior matches the specified behavior of the test vectors.

The major weakness of an ABEL description is that it forces the designer to understand many low-level details about the target PAL. Nevertheless, the state diagram description is an intuitively simple way to describe the behavior of a state machine.

## 8.4 Moore and Mealy Machine Design Procedure

There are two basic ways to organize a clocked sequential network:

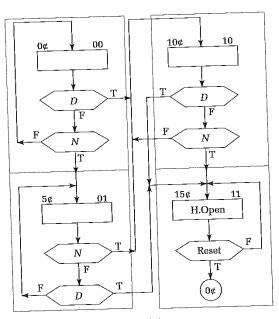

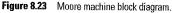

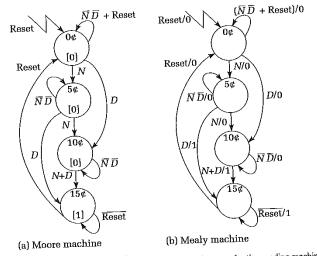

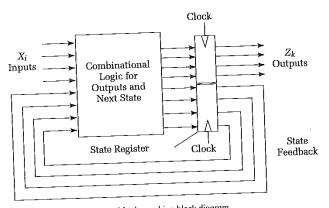

■ Moore machine: The outputs depend only on the present state. See the block diagram in Figure 8.23. A combinational logic block maps the inputs and the current state into the necessary flip-flop inputs to store the appropriate next state. The outputs are computed by a combinational logic block whose only inputs are the flip-flops' state outputs. The outputs change *synchronously* with the state transition and the clock edge. The finite state machines you have seen so far are all Moore machines.

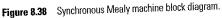

*Mealy machine*: The outputs depend on the present state and the present value of the inputs. See Figure 8.24. The outputs can change immediately after a change at the inputs, independent of the clock. A Mealy machine constructed in this fashion has *asynchronous* outputs.

Moore outputs are synchronous with the clock, only changing with state transitions. Mealy outputs are asynchronous and can change in response to any changes in the inputs, independent of the clock. This

#### 8.4 Moore and Mealy Machine Design Procedure 403

Figure 8.24 Mealy machine block diagram.

gives Moore machines an advantage in terms of disciplined timing methodology. However, there is a synchronous variation of the Mealy machine, which we describe later.

## 8.4.1 State Diagram and ASM Chart Representations

An ASM chart intended for Moore implementation would have no conditional output boxes. The necessary outputs are simply listed in the state box. Conditional output boxes in the ASM chart usually imply a Mealy implementation.

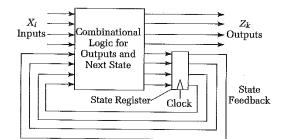

Figure 8.25 shows the notations for Mealy and Moore state diagrams, using the vending machine example. For Moore machines, the outputs are associated with the state in which they are asserted. Arcs are labeled with the input conditions that cause the transition from the state at the tail of the arc to the state at its head. Combinational logic functions are perfectly acceptable as arc labels.

In Mealy machines, the outputs are associated with the transition arcs rather than the state bubble. A slash separates the inputs from the

Figure 8.25 Moore and Mealy machine state diagrams for the vending machine FSM.

outputs. For example, if we are in state 10¢ and either N or D is asserted, Open will be asserted. Any glitch on N or D could cause the gum to be delivered by mistake.

The state diagrams in this figure are labeled more completely than our previous examples. For example, we make explicit the transitions that cause the machine to stay in the same state. We usually eliminate such transitions to simplify the state diagram. We also associate explicit output values with each transition in the Mealy state diagram and each state in the Moore state diagram. A common simplification places the output on the transition or in the state only when it is asserted. You should clarify your assumptions whenever you draw state diagrams.

## 8.4.2 Comparison of the Two Machine Types

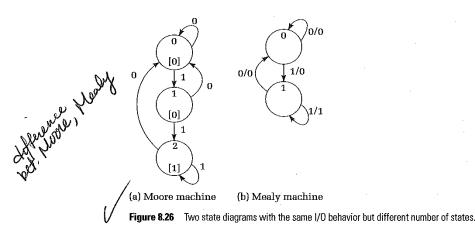

Because it can associate outputs with transitions, a Mealy machine can often generate the same output sequence in fewer states than a Moore machine.

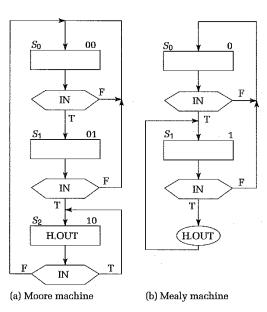

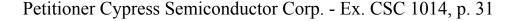

Consider a finite state machine that asserts its single output whenever its input string has at least two 1's in sequence. The minimum Moore and Mealy state diagrams are shown in Figure 8.26. The equivalent ASM charts are in Figure 8.27.

To represent the 1's sequence, the Moore machine requires two states to distinguish between the first and subsequent 1's. The first state has output 0, while the second has output 1. The Mealy machine accomplishes this

404

with a single state reached by two different transitions. For the first 1, the transition has output 0. For the second and subsequent 1's, the transition has output 1. Despite the Mealy machine's timing complexities, designers like its reduced state count.

Figure 8.27 ASM equivalents of Figure 8.26.

is

Petitioner Cypress Semiconductor Corp. - Ex. CSC 1014, p. 20

8.4.3

Figure 8.28 Mystery Moore finite state machine.

## Examples of Moore and Mealy Machines

**Example** Moore Machine Description To better understand the timing behavior of Moore and Mealy machines, let's begin by *reverse engineering* some finite state machines. We will work backward from a circuit-level implementation of the finite state machine to derive an ASM chart or state diagram that describes the machine's behavior.

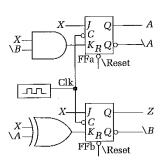

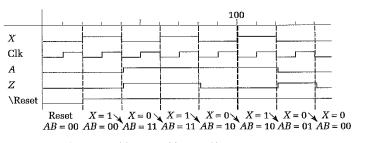

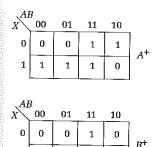

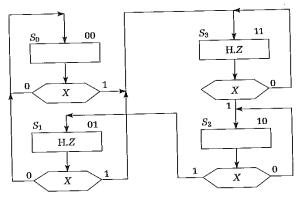

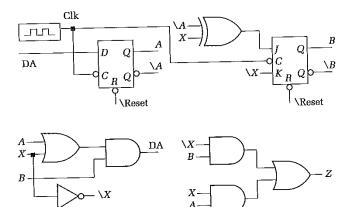

Figure 8.28 shows schematically a finite state machine with single data input X and output Z. The FSM is a Moore machine because the output is a combinational logic function (in this case a trivial one) of the state alone. The state register is implemented by two master/slave J-K flip-flops, named A and B, respectively. The machine can be in any one of up to four valid states. The output Z and the state bit B are the same.

**Signal Trace Method** There are two systematic approaches to determining the state transitions: *exhaustive signal tracing* and *extraction of the next state/output functions*. We examine the former here and the latter in the next subsection.

Signal tracing uses a collection of input sequences to exercise the various state transitions of the machine. To see how it works, let's start by generating a sample input sequence.

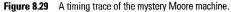

It is reasonable to assume that the FSM is initially reset and that it has been placed in state A = 0, B = 0. Figure 8.29 contains the timing waveform you would see after presenting the input sequence 1 0 1 0 1 0 to the machine. Because the FSM is implemented with master/slave flip-flops, the state time begins with the falling edge of the clock. Input X must be stable throughout the high time of the clock to guard against ones catching problems.

The sequence of events in Figure 8.29 is as follows. The asserted reset signal places the FSM in state 00. After the falling edge, input X goes high just after time step 20. At the next rising edge, the input is sampled and the next state is determined, but this is not presented to

8.4 Moore and Mealy Machine Design Procedure 407

| A | В | X | • A+ | B+ | Z |

|---|---|---|------|----|---|

| 0 | 0 | 0 | ?    | ?  | 0 |

|   |   | 1 | 1    | 1  | 0 |

| 0 | 1 | 0 | 0    | 0  | 1 |

|   |   | 1 | ?    | ?  | 1 |

| 1 | 0 | 0 | 1    | 0  | 0 |

|   |   | 1 | 0    | 1  | 0 |

| 1 | 1 | 0 | 1    | 1  | 1 |

|   |   | 1 | 1    | 0  | 1 |

|   |   |   |      |    |   |

Figure 8.30 Partial state transition table derived from the signal trace.

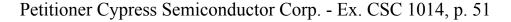

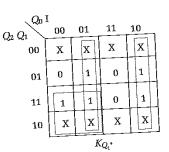

1 Figure 8.31 Next-state K-maps.

0 1

1

the outputs until the falling edge at time step 40. After a short propagation delay, the state becomes 11. We express the transition as "a 1 input in state 00 leads to state 11."

During the next state time, X is 0, and the FSM stays in state 11 as seen at time step 60. X now changes to 1, and at the next falling edge the state changes to 10.

The input next changes to 0, causing the state machine to remain in state 10 at time step 100. A transition to 1 causes it to change to state 01 after time step 120. The final transition to 0 leaves the machine in state 00.

Figure 8.30 contains the partial transition table we deduce from this input sequence. We would have to generate additional input sequences to fill in the missing transitions. For example, an input sequence from the reset state starting with a 0 would fill in the missing transition from state 00. The sequence 1 1 1 1, tracing from state 00 to 11 to 10 to 01, would catch the remaining transition.

Next State/Output Function Analysis Signal tracing is acceptable for a small FSM, but it becomes intractable for more complex finite state machines. With a single input and 2 bits of state, the example FSM has eight different transitions, two from each of four states. And the number of combinations doubles for each additional input bit and doubles again for each state bit.

Our alternative method derives the next-state functions directly from the combinational logic equations at the flip-flop inputs and the output function from the flip-flop outputs. For the mystery machine, these are

$$J_a = X K_a = X \bullet \overline{B} Z = B$$

$$J_b = X K_b = X \oplus \overline{A}$$

We can now express the flip-flop outputs,  $A^+$  and  $B^+$ , in terms of the excitation equations for the J-K flip-flop. We simply substitute the logic functions at the inputs into the excitation equations:

$$A^{+} = J_{a} \bullet A + \overline{K}_{a} \bullet A = X \bullet \overline{A} + (\overline{X} + B) \bullet A$$

$$B^{+} = J_{b} \bullet \overline{B} + \overline{K}_{b} \bullet B = X \bullet \overline{B} + (X \bullet \overline{A} + \overline{X} \bullet A) \bullet B$$

The next-state functions,  $A^+$  and  $B^+$ , are now expressed in terms of the current state, A and B, and the input X. We show the K-maps that correspond to these functions in Figure 8.31.

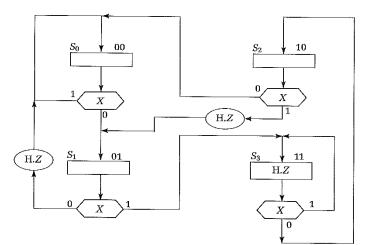

The missing state transitions are now obvious. In state 00 with input 0, the next state is  $A^+ = 0$  and  $B^+ = 0$ . In state 01 with input 1, the next state is  $A^+ = 1$ ,  $B^+ = 1$ . With its behavior no longer a mystery, we show the ASM chart for this finite state machine in Figure 8.32. In the figure, we assume the following symbolic state assignment:  $S_0 = 00$ ,  $S_1 = 01$ ,  $S_2 = 10, S_3 = 11.$

Figure 8.32 ASM chart for the mystery Moore machine.

**Example Mealy Machine Description** Continuing with our reverse engineering exercise, consider the circuit of Figure 8.33. Once again, the FSM has one input, X, and one output, Z. This time the output is a function of the current state, denoted by A and B, and the input X. The state register is implemented by one D flip-flop and one master/slave J-K flip-flop.

Before examining a signal trace, we must understand the conditions under which the Mealy machine's inputs are sampled and the outputs are valid. The next state is computed from the current state and the inputs, so exactly when are the inputs sampled? The answer depends on the kinds of flip-flops used to implement the state register. In the example, our use of a master/slave flip-flop dictates that the inputs must

Figure 8.33 Circuit schematic of the mystery Mealy machine.

Petitioner Cypress Semiconductor Corp. - Ex. CSC 1014, p. 23

#### 8.4 Moore and Mealy Machine Design Procedure 409

be stable during the high time of the clock (to avoid ones catching) and must be valid a setup time before the falling edge.

Technically, the outputs are valid only at the end of the state time, determined by the falling edge of the clock. In other words, the output for the current state is valid just as the machine enters its next state! If we are using a master/slave flip-flop and if the inputs do not change during the high time of the clock, then the outputs may also be valid during the clock high time.

Negative edge-triggered systems require that the inputs be stable before the falling edge that delineates the state times. This means that the outputs cannot be determined until just before the falling edge. The output remains valid only as long as it takes to compute a new output in the new state.

Similarly, for positive edge-triggered systems the outputs are valid at the rising edge. Again, the output is considered valid just before the clock edge that causes the machine to enter its new state.

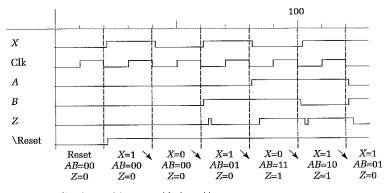

Figure 8.34 gives the timing waveform that corresponds to the input sequence 10101, after a reset to state 00. In state 00, reading a 1 keeps the machine in state 00 (time step 40).

Reading a 0 then advances the machine to state 01 (time step 60). The waveform for output Z has a glitch. The valid output is determined only at the end of the state time. In this case, the output is 0.

A 1 in state 01 leads to state 11 (time step 80). Again, the output in this state is the value of Z at the falling edge and thus is 1.

Reading a 0 in state 11 moves us to state 10 (time step 100), with the output continuing to be asserted despite the momentary glitch.

A 1 in state 10 leads us to state 01 (time step 120). The output goes low and will stay that way as long as the input X stays high.

| A | В | X | A+ | $B^+$ | <u>Z</u> |

|---|---|---|----|-------|----------|

| 0 | 0 | 0 | 0  | 1     | 0        |

|   |   | 1 | 0  | 0     | 0        |

| 0 | 1 | 0 | ?  | ?     | ?        |

| Ŭ | - | 1 | 1  | 1     | 0        |

| 1 | 0 | Õ | 2  | ?     | ?        |

|   |   | 1 | 0  | 1     | 1        |

| 1 | 1 | 0 | 1  | 0     | 1        |

|   | - | 1 | ?  | ?     | የ        |

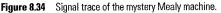

We show the partial state transition table in Figure 8.35. The input sequence produced only five of the eight state transitions. To complete the state diagram, we would have to generate additional sequences to traverse the missing transitions.

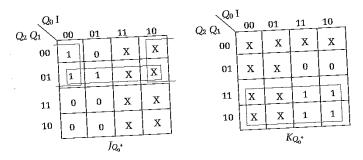

Alternatively, we can discover the complete set of transitions by analyzing the next-state and output functions directly, just as we did in the Moore machine:

$$A^{+} = B (A + X) = A \bullet B + B \bullet X$$

$$B^{+} = J_{b} \bullet \overline{B} + \overline{K}_{b} \bullet B = (\overline{A} \oplus X) \bullet \overline{B} + X \bullet B$$

$$= (\overline{A} \bullet \overline{X} + A \bullet X) \overline{B} + X \bullet B$$

$$= A \bullet \overline{B} \bullet X + \overline{A} \bullet \overline{B} \bullet \overline{X} + B \bullet X$$

$$Z = A \bullet X + B \bullet \overline{X}$$

Since A is a D flip-flop, the function for  $A^+$  is exactly the combinational logic function at its input. B is a J-K flip-flop, so we determine the function for  $B^+$  by substituting the logic functions at the J and K inputs into the J-K excitation function.

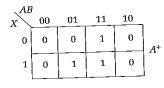

We give the next-state and output K-maps in Figure 8.36. The missing transitions are from state 01 to 00 on input 0, 10 to 00 on input 0, and 11 to 11 on input 1. The respective outputs are 1, 0, and 1. Assuming that  $S_0$ ,  $S_1$ ,  $S_2$ , and  $S_3$  correspond to encoded states 00, 01, 10, 11, we show the ASM chart for the mystery machine in Figure 8.37.

States, Transitions, and Outputs in Mealy and Moore Machines Suppose that a given state machine has M inputs and N outputs and is being implemented using L flip-flops. You might ask a number of questions to bound the complexity of this state machine. For example, what are the minimum and maximum numbers of states that such a machine might have? With L flip-flops, the implementation has the power to represent  $2^L$  states. But for a specific FSM as few as 1 and as many as  $2^L$  of these might be valid states.

What are the minimum and maximum numbers of state transitions that can begin in a given state? Since there must be an exit transition for each possible input combination, the minimum and the maximum are the same:  $2^{M}$  transitions.

A similar question involves the minimum and maximum numbers of state transitions that can end in a given state. Because we can have start-up states reachable only on reset, the minimum number of input transitions is 0. Since a single state could conceivably be the target of all the transitions of the finite state machine, the maximum number of input transitions is  $2^{M} * 2^{L}$ , the number of possible input combinations multiplied by the number of states.

8.4 Moore and Mealy Machine Design Procedure 411

A final question is the minimum and maximum numbers of patterns that can be observed on the machine's outputs. The minimum number of unique output patterns is 1, of course. Every state and every transition can be associated with the same pattern.

The maximum number depends on the kind of machine. For a Mealy machine, the maximum number of output patterns is the smaller of the number of transitions,  $2^{M} * 2^{L}$ , or the number of possible output patterns,  $2^{N}$ . If the number of transitions exceeds the number of possible output patterns, then some must be repeated. In the Moore machine, the maximum is the smaller of the number of states,  $2^{L}$ , and the number of possible output patterns,  $2^{N}$ . If the number of states exceeds the number of output patterns, then some patterns will also need to be repeated.

As an example, consider a Moore machine with two inputs, one flipflop, and three outputs. The state, transition, and output bounds are:

Minimum number of states: 1

Maximum number of states: 2

Minimum number of output transitions (per state): 4

Maximum number of output transitions (per state): 4

Minimum number of input transitions (per state): 0

Maximum number of input transitions (per state): 8

Minimum number of observed output patterns: 1

Maximum number of observed output patterns: 2

In this case, the output patterns are limited by the number of states.

Figure 8.37 ASM chart for the mystery Mealy machine.

**Synchronous Mealy Machines** The glitches in the output in Figure 8.34 are inherent in the asynchronous nature of the Mealy machine. As you have already seen, glitches are undesirable in real hardware controllers. But because Mealy machines encode control in fewer states, saving on state register flip-flops, it is still desirable to use them.

This leads to alternative *synchronous* design styles for Mealy machines. Simply stated, the way to construct a synchronous Mealy machine is to break the direct connection between inputs and outputs by introducing storage elements.

One way to do this is to synchronize the Mealy machine outputs with output flip-flops. See Figure 8.38. The flip-flops are clocked with the same edge as the state register. This has the effect of converting the Mealy machine into a Moore machine, by making the outputs part of the state encoding! However, this machine does not have exactly the same input/output behavior as the original Mealy machine (can you figure out why?). We will have more to say about synchronous Mealy machines in Chapter 10.

**Discussion** In general, fully synchronous finite state machines are much easier to implement and debug than asynchronous machines. If you were using discrete TTL components, you would usually prefer the Moore machine organization, even though it may require more states. You should use edge-triggered flip-flops for the state registers.

Synchronous Mealy machines can be constructed in TTL logic, but the designer must be careful. The approach leads to more complex designs that may affect the input/output timing of the FSM. You should use asynchronous Mealy machines only after very careful analysis of the input/output timing behavior of the finite state machine.

# Finite State Machine Optimization

Nature is as complex as it needs to be . . . and no more. —A. Einstein

10

te

i-

s эd

## Introduction

We are now ready to complete the finite state machine design process introduced in Chapter 8. The steps of Chapter 8 yield an abstract description of the state machine. This may be a state diagram, an ASM chart, or a hardware description language specification. Deriving a symbolic state transition table from one of these is straightforward. In this chapter, we concentrate on state minimization, state assignment, and choice of flip-flops.

We show why finite state machine "optimization" (*improvement* might be a better word) is still important, even in today's era of very large scale integrated circuits. We present pencil-and-paper methods, as well as more formal techniques suitable for computer implementation, for reducing the number of states and for choosing a state encoding.

Then we examine the approaches for choosing the machine's flipflops and how the choice affects the next-state and output combinational functions. The right choice of flip-flop leads to a smaller gate count and thus fewer components to implement the machine.

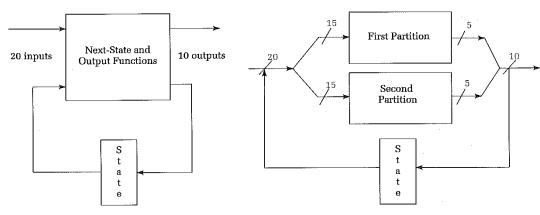

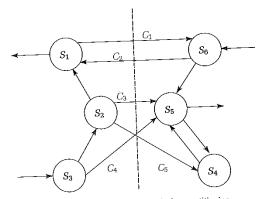

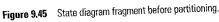

Finally, we develop techniques for partitioning complex finite state machines into simpler, smaller, communicating machines. You may be

forced to partition your state machine because it cannot fit into a given programmable logic component. This could arise, for example, because of limited logic resources, such as input/outputs, product terms, or flip-flops. In this chapter, we emphasize the following techniques and concepts:

- Procedures for optimizing a finite state machine. You will learn the methods for state minimization and state assignment.

- Application of modern computer-aided design tools for state assignment. CAD tools make it possible for you to evaluate the implementation complexity of alternative state assignments very rapidly.

- Partitioning methods. You will learn the techniques for breaking finite state machines into smaller, communicating state machines that are well suited for implementation with programmable logic.

## 9.1 Motivation for Optimization

To review, the finite state machine design process consists of (1) understanding the problem, (2) obtaining a formal description (ultimately, a symbolic state transition table), (3) minimizing the number of states, (4) encoding the states, (5) choosing the flip-flops to implement the state registers, and finally (6) implementing the finite state machine's nextstate and output functions. This chapter starts at step 3 and carries us through to the final implementation at step 6, using methods based on discrete logic gates. We discuss the use of programmable logic for finite state machine implementation in the next chapter.

## 9.1.1 Two State Diagrams, Same I/O Behavior

In the age of very large scale integrated circuits, why should we bother to minimize a finite state machine implementation? After all, as long as the input/output behavior of the machine is correct, it really doesn't matter how it is implemented. Or does it?

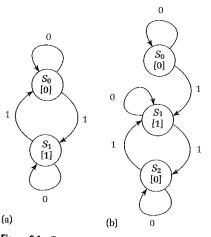

Figure 9.1 shows two different state diagrams for the odd parity checker of Section 8.2. They have identical output behavior for all input strings. You should try some inputs to convince yourself. We define *equivalence* of finite state machines as follows. Two machines are equivalent if their input/output behavior is identical for all possible input strings.

For a particular finite state machine, there are many equivalent forms. Rather than reusing states while deriving the state diagram, you could simply introduce a new state whenever you need one (to keep the number of states finite, you will need to reuse some of them, of course).

The two implementations of the state diagrams of Figure 9.1 are certainly not the same. The machine with more states requires more flipflops and more complex next-state logic.

9.1 Motivation for Optimization 451

ven

e of ops. ts: the

ign-

1en-

sing

ines

dery, a

, (4) state

lext-

s us

l on

nite

ther

g as

əsn't

cker

ings.

ce of

r in-

ilent

you

) the

:se).

cer-

flip-

Figure 9.1 Two equivalent state diagrams for the odd parity checker.

## 9.1.2 Advantages of Minimum States

In general, you will find it is worthwhile to implement the finite state machine in as few states as possible. This usually reduces the number of logic gates and flip-flops you need for the machine's implementation.

Similarly, judicious mapping between symbolic and encoded states can reduce the implementation logic. For the parity checker, our implementation in Chapter 8 required no gates because we made a good state assignment that naturally matched the control input to the toggle flip-flop.

A state diagram with n states must be implemented with at least k flip-flops, where  $2^{k-1} < n \le 2^k$ . By reducing the number of states to  $2^{k-1}$  or less, you can save a flip-flop. For example, suppose you are given a finite state machine with five state flip-flops. This machine can represent up to 32 states. If you can reduce the number of states to 16 or less, you save a flip-flop.

Even when reducing the number of states is not enough to eliminate a flip-flop, it still has advantages. With fewer states, you introduce more don't-care conditions into the next-state and output functions, making their implementation simpler. Less logic usually means shorter critical timing paths and a higher clock rate for the system.

More important, today's programmable logic provides limited gate and flip-flop counts on a single programmable logic chip. A typical programmable logic part might have "2000 gate equivalents" (rarely approached in practice) yet provide only 64 flip-flops! An important goal of state reduction is to make the implementation "fit" in as few components as possible. The fewer components you use, the shorter the design time and the lower the manufacturing cost.

State reduction techniques also allow you to be sloppy in obtaining the initial finite state machine description. If you have introduced a few redundant states, you will find and eliminate them by using the state reduction techniques introduced next.

#### State Minimization/Reduction 9.2

State reduction identifies and combines states that have equivalent "behavior." Two states have equivalent behavior if, for all input combinations, their outputs are the same and they change to the same or equivalent next states.

For example, in Figure 9.1(b), states  $S_0$  and  $S_2$  are equivalent. Both states output a 0; both change to  $S_1$  on a 1 and self-loop on a 0. Combining these into a single state leads to Figure 9.1(a). On all input strings, the output sequence of either state diagram is exactly the same,

Algorithms for state reduction begin with the symbolic state transition table. First, we group together states that have the same state outputs (Moore machine) or transition outputs (Mealy machine). These are potentially equivalent, since states cannot be equivalent if their outputs differ.

Next, we examine the transitions to see if they go to the same next state for every input combination. If they do, the states are equivalent and we can combine them into a renamed new state. We then change all transitions into the newly combined states. We repeat the process until no additional states can be combined.

In the following two subsections, we examine alternative algorithms for state reduction: row matching and implication charts. The former is a good pencil-and-paper method, but does not always obtain the best reduced state table. Implication charts are more complex to use by hand, but they are easy to implement via computer and do find the best solution.

We can always combine the two approaches. Row matching quickly reduces the number of states. The more complicated implication chart method, now working with fewer states, finds the equivalent states missed by row matching more rapidly.

#### **Row-Matching Method** 9.2.1

Let's begin our investigation of the row-matching method with a detailed example. We will see how to transform an initial state diagram for a simple sequence detector into a minimized, equivalent state diagram.

Four-Bit Sequence Detector: Specification and Initial State Diagram Let's consider a sequence-detecting finite state machine with the following specification. The machine has a single input X and output Z. The output is asserted after each 4-bit input sequence if it consists of one of the binary strings 0110 or 1010. The machine returns to the reset state after each 4-bit sequence.

452

We will assume a Mealy implementation. Some sample behavior of the finite state machine is

$X = 0010 \ 0110 \ 1100 \ 1010 \ 0011 \ \dots$

$Z = 0000 \ 0001 \ 0000 \ 0001 \ 0000 \ \dots$

The output is asserted only after the previous four serial inputs match one of the specified strings. Also, the input patterns do not overlap: the machine makes a decision to assert its output after each group of 4 bits.

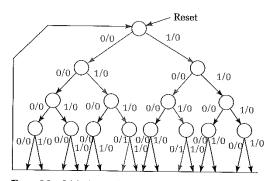

Because this finite state machine recognizes finite length strings, we can place an upper bound on the number of states needed to recognize any particular binary string of length four. Figure 9.2 shows the state diagram. There are 16 unique paths through the state diagram, one for each possible 4-bit pattern. This adds up to 15 states and 30 transitions. We highlight the paths leading to recognition of the strings 0110 and 1010 in the figure. Only two of the transitions have a 1 output, representing the accepted strings.

Four-Bit Sequence Detector: State Table and Row-Matching Method We can combine many of the states in Figure 9.2 without changing the input/output behavior of the finite state machine. But how do we find these equivalent states in a systematic fashion?

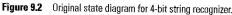

First, we look at the state transition table, as shown in Figure 9.3. This table is in a slightly different format than we have seen so far. It contains one row per state, with multiple next-state and output columns based on the input combinations. It gives exactly the same information as a table with separate rows for each state and input combination.

The input sequence column is a documentation aid, describing the partial string as seen so far. When read from left to right, it describes the sequence of input bits that lead to the given state.

's g

e er

454 Chapter 9 Finite State Machine Optimization

| _              | D             | Next<br>X-0     |                  | Outp $X=0$ |   |

|----------------|---------------|-----------------|------------------|------------|---|

| Input Sequence | Present State | <u>S1</u>       | $\overline{S_2}$ | 0          | 0 |

| Reset          | $S_0$         | $S_3$           | S <sub>4</sub>   | 0          | 0 |

| 0              | $S_1 \\ S_2$  | $S_5$           | $S_6$            | 0          | 0 |

| 1              |               | S7              | $S_8$            | 0          | 0 |

| 00             |               | $S_9$           | $S_{10}$         | 0          | 0 |

| 01             | 1 -           | S <sub>11</sub> | $S_{12}$         | 0          | 0 |

| 10             |               | $ S_{13} $      | $S_{14}$         | 0          | 0 |

| 11             |               | 50              | $S_0$            | 0          | 0 |

| 000            |               | S <sub>0</sub>  | $S_0$            | 0          | 0 |

| 001            |               | So              | $S_0$            | 0          | 0 |

| 010            |               | S <sub>0</sub>  | $S_0$            | 1          | 0 |

| 10             |               | S <sub>0</sub>  |                  | 0          | 0 |

| 10             |               |                 |                  | 1          | 0 |

| 10             |               | $S_0$           |                  | 0          | 0 |

| 11             |               | S               |                  | ) 0        | 0 |

| 11             | 1 014         | - 0             |                  |            |   |

Next we examine the rows of the state transition table to find any with identical next-state and output values (hence the term "row matching"). For this finite state machine, we can combine  $S_{10}$  and  $S_{12}$ . Let's call the new state  $S_{10}$  and use it to rename all transitions to  $S_{10}$  or  $S_{12}$ . The revised state table is shown in Figure 9.4.

**Four-Bit Sequence Detector: Row-Matching Iteration** We continue matching rows until we can no longer combine any. In Figure 9.4,  $S_7$ ,  $S_8$ ,  $S_9$ ,  $S_{11}$ ,  $S_{13}$ , and  $S_{14}$  all have the same next states and outputs. We combine them into a renamed state  $S_7$ '. The table, with renamed transitions, is shown in Figure 9.5.

( 5

(1

0/0

0,1/0 6,1/0 Figure 4-bit st

| Input Sequence | Present State  | Next<br>X=0     | State<br>X=1     | Outy<br>X=0 |   |

|----------------|----------------|-----------------|------------------|-------------|---|

| Input Sequence |                | $S_1$           | $S_2$            | 0           | 0 |

| Reset          |                | $S_3$           | S4               | 0           | 0 |

| 0              | $S_1$          | $S_5$           | $S_6$            | 0           | 0 |

| 1              | $S_2$          |                 |                  | 0           | 0 |

| 00             | S              | S7              | $\overline{S_8}$ | Ö           | ŏ |

| 01             | S <sub>4</sub> | $S_9$           | $S_{10}$         |             |   |

| 10             | $S_5$          | S11             | $S_{10}$         | 0           | 0 |

| 10             | $S_6$          | S <sub>13</sub> | $S_{14}$         | 0           | 0 |

|                | 57<br>57       | S <sub>0</sub>  | $S_0$            | 0           | 0 |

|                | S8             | $S_0$           | $S_0$            | 0           | 0 |

| 001            |                |                 | $\tilde{S_0}$    | 0           | 0 |

| 010            |                | 50              |                  | 1           |   |

| 011 or 101     |                |                 |                  | 10          | 0 |

| 100            |                | S <sub>0</sub>  | <u> </u>         | 0           | ŏ |

| 110            | $S_{13}$       | $S_0$           | $S_0$            | -           | 0 |

| 111            | $S_{14}$       | $S_0$           | $S_0$            | 0           | 0 |

|                |                |                 |                  |             |   |

Figure 9.4 Revised state transition table after  $S_{10}$  and  $S_{12}$  combined.

Petitioner Cypress Semiconductor Corp. - Ex. CSC 1014, p. 33

|                  |               | Next      |          | Out |     |

|------------------|---------------|-----------|----------|-----|-----|

| Input Sequence   | Present State | X=0       | X=1      | X=0 | X=1 |

| Reset            | $S_0$         | $S_1$     | $S_2$    | 0   | 0   |

| 0                | $S_1$         | $S_3$     | $S_4$    | 0   | 0   |

| 1                | $S_2$         | $S_5$     | $S_6$    | 0   | 0   |

| 00               | $S_3$         | $S_7$     | $S_7$    | 0   | 0   |

| 01               | $S_4$         | $S_7$     | $S_{10}$ | 0   | 0   |

| 10               | $S_5$         | $S_7^{!}$ | $S_{10}$ | 0   | 0   |

| 11               | $S_6$         | $S_7^{i}$ | $S_7$    | 0   | 0   |

| not (011 or 101) | $S_7$         | $S_0$     | $S_0$    | 0   | 0   |

| 011 or 101       | $S_{10}$      | $S_0$     | $S_0$    | 1   | 0   |

Figure 9.5 Revised state transition table after S<sub>7</sub>, S<sub>8</sub>, S<sub>9</sub>, S<sub>11</sub>, S<sub>13</sub>, S<sub>14</sub> combined.

|                  |               | Next State |              | Out         | put         |

|------------------|---------------|------------|--------------|-------------|-------------|

| Input Sequence   | Present State | X=0        | <i>X</i> =1  | <i>X</i> =0 | <i>X</i> =1 |

| Reset            | $S_0$         | $S_1$      | $S_2$        | 0           | 0           |

| 0                | $S_1$         | $S_3$      | $S_4$        | 0           | 0           |

| 1                | $S_2$         | $S_4$      | $S_3$        | 0           | 0           |

| 00 or 11         | $S_3$         | $S_7$      | $S_7^1$      | 0           | 0           |

| 01 or 10         | $S'_4$        | $S_7$      | $S_{10}^{l}$ | 0           | 0           |

| not (011 or 101) | S'7           | $S_0$      | $S_0$        | 0           | 0           |

| 011 or 101       | $S_{10}$      | $S_0$      | $S_0$        | 1           | 0           |

**Figure 9.6** Final reduced state transition table after  $S_3$ ,  $S_6$  and  $S_4$ ,  $S_5$  combined.

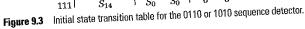

Figure 9.7 Reduced state diagram for 4-bit string recognizer.

| Now states $S_3$ and $S_6$ can be combined, as can $S_4$ and $S_5$ . We call the         |

|------------------------------------------------------------------------------------------|

| combined states $S_{3}'$ and $S_{4}'$ , respectively. The final reduced state transition |

| table is shown in Figure 9.6. In the process, we have reduced 15 states to               |

| just 7 states. This allows us encode the state in 3 bits rather than 4. The re-          |

| duced state diagram is given in Figure 9.7.                                              |

Limitations of the Row-Matching Method Unfortunately, row matching does not always yield the most reduced state table. We can prove this with a simple counterexample. Figure 9.8 shows the state table for the three-state odd parity checker of Figure 9.1. Although states  $S_0$  and  $S_2$  have the same output, they do not have the same next state. Thus, they cannot be combined by simple row matching. The problem is the self-loop transitions on input 0. If we combined these two states, the self-loop would be maintained, but this is not found by row matching. We need another, more rigorous method for state reduction.

| Next State    |       |             |        |  |  |  |

|---------------|-------|-------------|--------|--|--|--|

| Present State | X=0   | <i>X</i> =1 | Output |  |  |  |

| $S_0$         | $S_0$ | $S_1$       | 0      |  |  |  |

| $S_1$         | $S_1$ | $S_2$       | 1      |  |  |  |

| $S_2$         | $S_2$ | $S_1$       | 0      |  |  |  |

Figure 9.8 State table for three-state odd parity checker.

## 9.2.2 Implication Chart Method

The implication chart method is a more systematic approach to finding the states that can be combined into a single reduced state. As you might suspect, the method is more complex and is better suited for machine implementation than hand use.

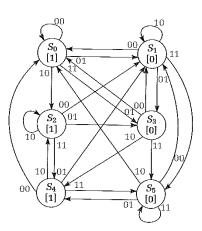

Three-Bit Sequence Detector: Specification and Initial State Table We illustrate its use with another example. Your goal is to design a binary sequence detector that will output a 1 whenever the machine has observed the serial sequence 010 or 110 at the inputs. We call this machine a 3-bit sequence detector. Figure 9.9 shows its initial state table.

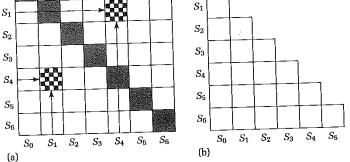

**Data Structure: The Implication Chart** The method operates on a data structure that enumerates all possible combinations of states taken two at a time, called an *implication chart*. Figure 9.10(a) shows the chart with an entry for every pair of states. This form of the chart is more complicated than it needs to be. For example, the diagonal entries are not needed: it does not reduce states to combine a state with itself! And

|                |                  | Next State |       | Outj        | put |

|----------------|------------------|------------|-------|-------------|-----|

| Input Sequence | Present State    | X=0        | X=1   | <i>X</i> =0 | X=1 |

| Reset          | $\overline{S_0}$ | $S_1$      | $S_2$ | 0           | 0   |

| 0              | $S_1$            | $S_3$      | $S_4$ | 0           | 0   |

| 1              | $\tilde{S_2}$    | $S_5$      | $S_6$ | 0           | 0   |

|                | $S_3$            | $S_0$      | $S_0$ | 0           | -0  |

| 01             | $S_4$            | $S_0$      | $S_0$ | 1           | 0   |

| 10             | $S_5$            | $S_0$      | $S_0$ | 0           | 0   |

| 11             | $S_6$            | S          | $S_0$ | 1           | 0   |

Figure 9.9 Initial state transition table for the 3-bit sequence detector.

Figure 9.10 Matrix for state combinations and the corresponding implication chart.

Petitioner Cypress Semiconductor Corp. - Ex. CSC 1014, p. 35

9.2 State Minimization/Reduction 457

the upper and lower triangles of entries are symmetric. The chart entry for  $S_i$  and  $S_j$  contains the same information as that for  $S_j$  and  $S_i$ . Thus, we work with the reduced structure of Figure 9.10(b).

We fill in the implication chart as follows. Let  $X_{ij}$  be the entry whose row is labeled by state  $S_i$  and whose column is labeled by state  $S_j$ . If we were able to combine states  $S_i$  and  $S_j$ , it would imply that their nextstate transitions for each input combination must also be equivalent. The chart entry contains the next-state combinations that must be equivalent for the row and column states to be equivalent. If  $S_i$  and  $S_j$  have different outputs or next-state behavior, an X is placed in the entry. This indicates that the two states can never be equivalent.

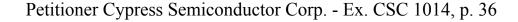

**Three-Bit Sequence Detector: Initial Implication Chart** The implication chart for the example state table is shown in Figure 9.11.  $S_0$ ,  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_5$  have the same outputs and are candidates for being combined. Similarly, states  $S_4$  and  $S_6$  might also be combined. Any combination of states across the two groups, such as  $S_1$  and  $S_4$ , is labeled by an X in the chart. Since their outputs are different, they can never be equivalent.

Э

е

ł

To fill in the chart entry for (row)  $S_1$  and (column)  $S_0$ , we look at the next-state transitions.  $S_0$  goes to  $S_1$  on 0 and  $S_2$  on 1, while  $S_1$  goes to  $S_3$  and  $S_4$ , respectively. We fill the chart in with  $S_1$ - $S_3$ , the transitions on 0, and  $S_2$ - $S_4$ , the transitions on 1. We call these groupings *implied state pairs*. The entry means that  $S_0$  and  $S_1$  cannot be equivalent unless  $S_1$  is equivalent to  $S_3$  and  $S_2$  is equivalent to  $S_4$ . The rest of the entries are filled in similarly.

At this point, the chart already contains enough information to eliminate many impossible equivalent pairs. For example, we already know that  $S_2$  and  $S_4$  cannot be equivalent: they have different output behavior. Thus there is no way that  $S_0$  can be equivalent to  $S_1$ .

Finding these cases is straightforward. We visit the entries in sequence. For example, start with the top square in the first column and advance from top to bottom and left to right. If square  $S_i, S_j$  contains the implied state pair  $S_m$ - $S_n$  and square  $S_m, S_n$  contains an X, then mark  $S_i, S_j$  with an X as well.

**Sequence Detector Example: First Marking Pass** Figure 9.12 contains the results of this first marking pass. Entry  $S_2,S_0$  is marked with an X because the chart entry for the implied state pair  $S_2$ - $S_6$  is already marked with an X. Entry  $S_3,S_0$  is also marked, because entry  $S_1,S_0$  (as well as  $S_2,S_0$ ) has just been marked. The same is true for  $S_5,S_0$ . By the end of the pass, the only entries not marked are  $S_2,S_1; S_5,S_3;$  and  $S_6,S_4$ .

**Sequence Detector Example: Second Marking Pass** We now make a second pass through the chart to see if we can add any new markings. Entry  $S_2, S_1$  remains unmarked. Nothing in the chart refutes that  $S_3$  and  $S_5$  are equivalent. The same is true of  $S_4$  and  $S_6$ .

Chapter 9 Finite State Machine Optimization

Continuing,  $S_3, S_5$  and  $S_4, S_6$  are now obviously equivalent. They have identical outputs and transfer to the same next state  $(S_0)$  for all input combinations.

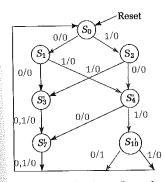

Since no new markings have been added, the algorithm stops. The unmarked entries represent equivalences between the row and column indices:  $S_1$  is equivalent to  $S_2$ ,  $S_3$  to  $S_5$ , and  $S_4$  to  $S_6$ . The final reduced state table is shown in Figure 9.13.

Multi-Input Example: State Diagram and Transition Table We can generalize the procedure for finite state machines with more than one input. The only difference is that there are more implied state pairs: one for each input combination.

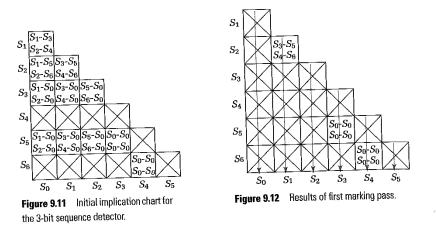

Let's consider the state diagram for a two-input Moore machine shown in Figure 9.14. Each state has four next-state transitions, one for each possible input condition. The derived state transition table is given in Figure 9.15.

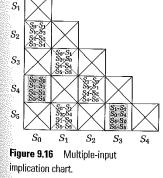

Multi-Input Example: Implication Chart Processing Figure 9.16 shows the implication chart derived from the state transition table. Let's see how some of the entries are filled in. Since  $S_1$  and  $S_0$  have different state outputs, we place X in entry  $S_1, S_0$ . For the  $S_2, S_0$  entry, we list the implied state pairs under the input conditions 00, 01, 10, 11. Because  $S_0$

| Input Sequence                          | Present State i         |                              | State<br>X=1 (                   | Out<br><i>X=</i> 0 |                  |

|-----------------------------------------|-------------------------|------------------------------|----------------------------------|--------------------|------------------|

| Reset<br>0 or 1<br>00 or 10<br>01 or 11 | $S_0$<br>$S_1$<br>$S_3$ | $S_1' \\ S_3' \\ S_0 \\ S_0$ | $S_1$<br>$S_4$<br>$S_0$<br>$S_0$ | 0<br>0<br>0<br>1   | 0<br>0<br>0<br>0 |

Figure 9.13 Final reduced state transition table for the 3-bit sequence detector.

458

Figure 9.14 Multiple-input state diagram.

| Present          | Next State |                  |       |       | Output |

|------------------|------------|------------------|-------|-------|--------|

| State            | 00         | 01               | 10    | 11    | 1      |

| $S_0$            | $S_0$      | $\overline{S_1}$ | $S_2$ | $S_3$ | 1      |

| $S_1$            | $S_0$      | $S_3$            | $S_1$ | $S_5$ | 0      |

| $S_2$            | $S_1$      | $S_3$            | $S_2$ | $S_4$ | 1      |

| $\overline{S_3}$ | $S_1$      | $S_0$            | $S_4$ | $S_5$ | 0      |

| $S_4$            | $S_0$      | $S_1$            | $S_2$ | $S_5$ | 1      |

| $S_5$            | $S_1$      | $S_4$            | $S_0$ | $S_5$ | 0 ·    |

Figure 9.15 Multiple-input state transition table.

stays in  $S_0$  on input 00, while  $S_2$  goes to  $S_1$  on 00, we add the implied state pair  $S_0$ - $S_1$  to the entry. On input 01,  $S_0$  goes to  $S_1$ ,  $S_2$  goes to  $S_3$ , and we add  $S_1$ - $S_3$  to the entry. Similarly, we add the pairs  $S_2$ - $S_2$  on 10 and  $S_3$ - $S_4$  on 11 to the entry and fill in the rest of the entries.

Now we begin the marking pass. Working down the columns, we cross out entry  $S_2$ - $S_0$  because  $S_0,S_1$  is already crossed out. The same thing happens to the entries  $S_3,S_1$ ;  $S_5,S_1$ ; and  $S_4,S_2$ . This leaves  $S_4,S_0$  and  $S_5,S_3$  unmarked (these are highlighted in the figure). Their being unmarked implies that  $S_4$  is equivalent to  $S_0$  (renamed  $S_0$ ) and  $S_3$  is equivalent to  $S_5$  ( $S_3$ ). The reduced state table is given in Figure 9.17.

| Present | 1         | Vext      | State  |                | Output |

|---------|-----------|-----------|--------|----------------|--------|

| State   | 00        | 01        | 10     | 11             | -      |

| $S_0$   | $S_0^{i}$ | $S_1$     | $S_2$  | $S_3$          | 1      |

| $S_1$   | $S_0^{i}$ | $S_3$     | $S_1$  | $S_3$          | 0      |

| $S_2$   | $S_1$     | $S_3$     | $S_2$  | $S_0$          | 1      |

| $S_3$   | $S_1$     | $S_0^{l}$ | $S_0'$ | $S_3^{\prime}$ | 0      |

| Figure 9.17 | Multiple-input reduced state table. |

|-------------|-------------------------------------|

|-------------|-------------------------------------|

# 460 Chapter 9 Finite State Machine Optimization

Figure 9.18 Implication chart for three-state odd parity checker.

**Example** State Reduction of Parity Checker Finite State Machine The row-matching method could not combine states  $S_0$  and  $S_2$  in the three-state parity checker of Figure 9.1. Can the implication chart method do the job? The implication chart for the state transition table of Figure 9.8 is given

In a implication chart for the state transition time the because their outin Figure 9.18.  $S_1, S_0$  and  $S_2, S_1$  are marked immediately because their outputs differ. The remaining square is left unmarked, implying that  $S_0$  and  $S_2$ are equivalent. This is the correct reduced state transition table.

**Implication Chart Summary** The algorithm for state reduction using the implication chart method consists of the following steps:

- 1. Construct the implication chart, consisting of one square for each possible combination of states taken two at a time.

- 2. For each square labeled by states  $S_i$  and  $S_p$  if the outputs of the states differ, mark the square with an X; these states are *not* equivalent. Otherwise, they may be equivalent. Within the square, write implied pairs of next states for all input combinations.

- **3.** Systematically advance through the squares of the implication chart. If the square labeled by states  $S_i, S_j$  contains an implied pair  $S_m, S_n$  and square  $S_m, S_n$  is marked with an X, then mark  $S_i, S_j$  with an X. Since  $S_m$  and  $S_n$  are not equivalent, neither are  $S_i$  and  $S_j$ .

- 4. Continue executing step 3 until no new squares are marked with an X.

- 5. For each remaining unmarked square  $S_i, S_j$ , you can conclude that states  $S_i$  and  $S_j$  are equivalent.

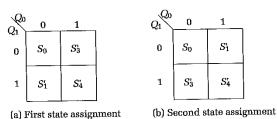

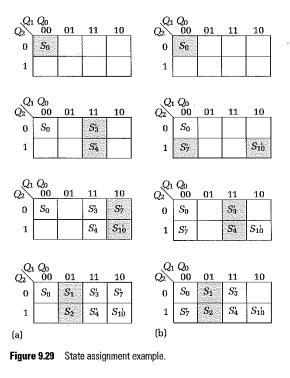

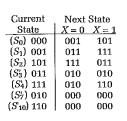

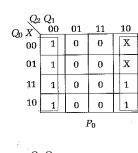

## 9.3 State Assignment

The number of gates needed to implement a sequential logic network depends strongly on how we assign *encoded* Boolean values to *symbolic* states. Unfortunately, the only way to obtain the best possible assignment is to try every choice for the encoding, an extremely large number for real state machines. For example, a four-state finite state machine, such as the traffic light controller of the last chapter, has 4! (4 factorial) = 4 \* 3 \* 2 \* 1 = 24 different encodings (see Figure 9.19).

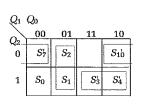

## 9.3.1 Traffic Light Controller

To illustrate the impact of state encoding on the next-state and output logic, let's use the symbolic state transition table for the traffic light controller, shown in Figure 9.20. The input combinations that cause the state transitions are shown at the left of the table. The symbolic state names HG, HY, FG, FY represent the states highway green/farmroad red, highway yellow/farmroad red, highway red/farmroad green, and highway red/farmroad yellow. We have already encoded the traffic light outputs: 00 = Green, 01 = Yellow, and 10 = Red.

9.3 State Assignment 461

| HG | ΗY | FG | FY        | HG | ΗY | FG | FY |

|----|----|----|-----------|----|----|----|----|

| 00 | 01 | 10 | 11        | 10 | 00 | 01 | 11 |

| 00 | 01 | 11 | 10        | 10 | 00 | 11 | 01 |

| 00 | 10 | 01 | 11        | 10 | 01 | 00 | 11 |

| 00 | 10 | 11 | <b>01</b> | 10 | 01 | 11 | 00 |

| 00 | 11 | 01 | 10        | 10 | 11 | 00 | 01 |

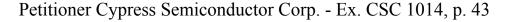

| 00 | 11 | 10 | 01        | 10 | 11 | 01 | 00 |