# FIELD-PROGRAMMABLE GATE ARRAY TECHNOLOGY

edited by Stephen M. Trimberger

Δ

1

Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

# FIELD-PROGRA ARRAY TEC

edite

Stephen M. Xil

with contr.

Stephen M. Xii

> Dennis I Telle V Ac

an The Technical Staff of edite Robert H

KLUWER ACADE Boston / Dord

SYNOPS

2

Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

DOCKET

Distributors for North America: Kluwer Academic Publishers 101 Philip Drive Assinippi Park Norwell, Massachusetts 02061 USA

Distributors for all other countries: Kluwer Academic Publishers Group Distribution Centre Post Office Box 322 3300 AH Dordrecht, THE NETHERLANDS

Library of Congress Cataloging-in-Publication Data

Field -programmable gate array technology / edited by Stephen M. Trimberger.

p. cm.

Includes bibliographical references and index.

ISBN 0-7923-9419-4 (acid-free paper)

1. Gate array circuits. 2. Programmable logic devices.

3. Programmable array logic. I. Trimberger, Stephen, 1955 -TK7895.G36F54 1994

621.39'5--dc20

93-39703 CIP

Copyright © 1994 by Kluwer Academic Publishers

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, mechanical, photo-copying, recording, or otherwise, without the prior written permission of the publisher, Kluwer Academic Publishers, 101 Philip Drive, Assinippi Park, Norwell, Massachusetts 02061.

Printed on acid-free paper.

Printed in the United States of America

who

3

SYNOPS

Find authenticated court documents without watermarks at docketalarm.com.

#### FPGA Technology

SRAM Programmable FPGAs

nets and paths with maximum delay values. These constraints can be provided as annotation in the schematic or in a separate design constraints file.

Manual intervention in FPGA partitioning can take the form of a CLBMAP, a schematic-level constraint that forces the partitioner to accept a user-defined mapping for part of the logic. The CLBMAP is a cell in the library that a designer connects in parallel with the logic it is mapping. The CLBMAP represents no logic, but its connections are used to guide the partitioner to implement the mapped logic in a single CLB. A designer can go further, designing in terms of CLBs with their programming.

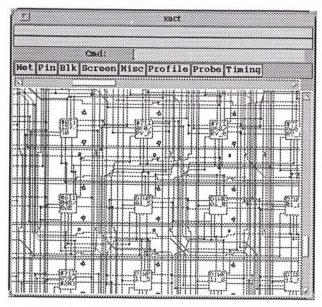

The XACT Design Editor (XDE) (figure 2.4.6) is an interactive graphical editor similar in concept to MPGA wiring editors. XDE contains both the logical and physical descriptions of the design. Users modify both descriptions simultaneously as they design the circuit. A designer can use XDE to pre-place and route CLBs or to do post-placement and routing fixup. XDE can also be used as a complete design system, allowing a designer to map the logic manually onto the device. XDE can accept a netlist as input, or a design can be created and implemented completely in XDE.

Figure 2.4.6. XDE Screen.

XDE includes the checking and editing functions required for manual design, including a design rules checker, a timing verifier and a router. XDE allows a designer to turn on or off individual pips in the interconnect, to set the functionality of function tables, and to control the functions in CLBs and IOBs.

DOCKE

XDE provides the front-end interface to the or simple modifications of the design. It includes internal signals routed out to unused pads to all for debugging a design. The probe modification version of the design that is then loaded into the probe points separately from the base design, so prototype debugging is complete.

## 2.5. The Future

FPGAs are similar to MPGAs in many respects, that a researcher can draw upon to apply in this architecture is large and relatively unexplored, research. These unexplored areas may eventuall terms of density and performance. Since softwa software questions will opened or re-opened by

### **Programming Technology**

The CPLD-style array architectures, built with cannot be scaled beyond thousands of gates of quadratically, as does static power consumption capacity EPROM devices show significantly devices, as well as massive power requirement consumption requires a multi-level logic org architectures described in this chapter. EPROM built in large arrays, so they become inefficient in to extend EPROM-based architectures to large section into a straightforward memory array, an FPGA, basically building an SRAM FPGA with

Large antifuse-programmed devices rely on we themselves. A single ten-thousand-gate antifu million antifuses. Although only a few percent we architecture relies on those few percent being FPGA will fail to program correctly, and must be fail to program is not a serious issue with smat dollars and programming yield is above 99 per cost hundreds of dollars and the programming yi that customers will accept discarding 20% of antifuse manufacture limits the size of antifuse-b

SRAM-programmed devices have none of thes technology improvements and have very low po with very high quality and fully tested at the factor