US006363520B1

# (12) United States Patent

### Boubezari et al.

(10) Patent No.: US 6,363,520 B1

(45) Date of Patent: Mar. 26, 2002

#### (54) METHOD FOR TESTABILITY ANALYSIS AND TEST POINT INSERTION AT THE RT-LEVEL OF A HARDWARE DEVELOPMENT LANGUAGE (HDL) SPECIFICATION

- (75) Inventors: Samir Boubezari, Mountain View, CA

(US); Eduard Cerny; Bozena

Kaminska, both of Montreal (CA);

Benoit Nadeau-Dostie, Aylmer (CA)

- (73) Assignee: LogicVision, Inc., San Jose, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 09/098,555

- (22) Filed: Jun. 16, 1998

- (51) Int. Cl.<sup>7</sup> ..... G06F 17/50; G06F 17/10;

- (58) Field of Search ...... 716/18, 4

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

| 4,791,578 A | * 12/1988 | Fazio et al 364/488    |

|-------------|-----------|------------------------|

| 5,043,986 A | 8/1991    | Agrawal et al 371/25.1 |

| 5,329,533 A | 7/1994    | Lin 371/22.3           |

| 5,379,303 A | * 1/1995  | Levitt 371/27          |

| 5,450,414 A | 9/1995    | Lin 371/22.3           |

| 5,513,123 A | * 4/1996  | Dey et al 364/489      |

| 5,828,828 A | * 10/1998 | Lin et al 395/183.06   |

| 6,038,691 A | * 3/2000  | Nakao et al 714/733    |

#### OTHER PUBLICATIONS

H. Fujiwara, Computational Complexity of Controllability/ Observability Problems for Combinational Circuits, 18th International Symposium on Fault–Tolerant Computing, pp. 64–69, Jun. 1988.\* C.H. Chen et al., An Approach to Functional Level Testability Analysis, 1989 International Test Conference, pp. 373–380, Aug. 1989.\*

C.H. Chen et al., Behavioral Synthesis for Testability, 1992 IEEE/ACM International Conference on Computer–Aided Design, pp. 612–615, Nov. 1992.\*

C.P. Ravikumar et al., HISCOAP: A Hierarchical Testability Analysis Tool, 8th International Conference on VLSI Design, pp. 272–277, Jan. 1995.\*

Y. Fang et al., Efficient Testability Enhancement for Combinational Circuit, 1995 International Conference on Computer Design, pp. 168–172, Oct. 1995.\*

S. Boubezari et al., Testability Analysis and Test-Point Insertion in RTL VHDL Specifications for Scan-Based BIST, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, pp. 1327–1340, Sep. 1999.\*

(List continued on next page.)

Primary Examiner—Matthew Smith Assistant Examiner—A. M. Thompson (74) Attorney, Agent, or Firm—Sheridan Ross P.C.

### (57) **ABSTRACT**

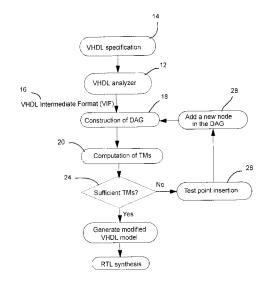

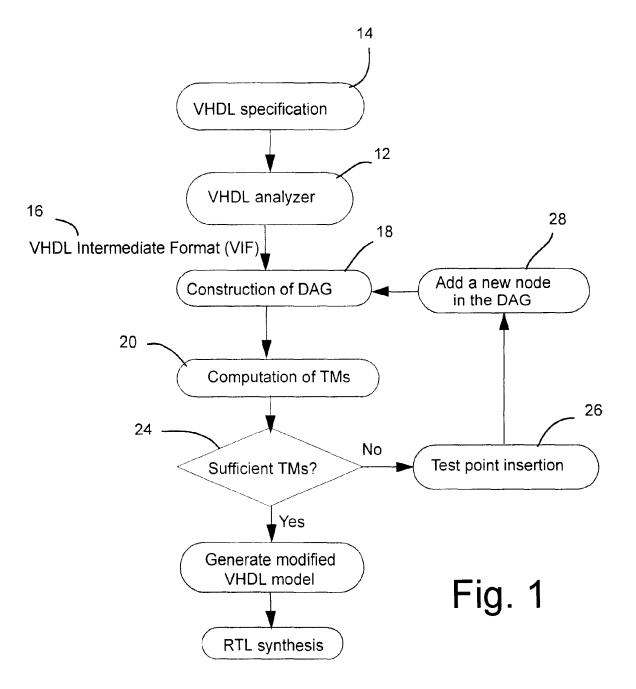

A method is provided for producing a synthesizable RT-Level specification, having a testability enhancement from a starting RT-Level specification representative of a circuit to be designed, for input to a synthesis tool to generate a gate-level circuit. The method includes the steps of performing a testability analysis on a Directed Acyclic Graph by computing and propagating Testability Measures forward and backward through VHDL statements, identifying the bits of each signal and/or variable, and adding test point statements into the specification at the RT-Level to improve testability of the circuit to be designed. The computation of Controllability and Observability method is purely functional, and does not subsume the knowledge of a gate-level implementation of the circuit being analyzed.

#### 36 Claims, 7 Drawing Sheets

# **R** M Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

### OTHER PUBLICATIONS

M.H. Gentil et al., A New High Level Testability Measure: Description and Evaluation, 12th IEEE VLSI Test Symposium 1994, pp. 421–426, Apr. 1994.\*

T.C. Lee et al., Behavioral Synthesis for Easy Testability in Data Path Allocation, IEEE 1992 International Conference on Computer Design, pp. 29–32, Oct. 1992.\*

P. Vishakantaiah et al., "AMBIANT": Automatic Generation of Behavioral Modifications for Testability", IEEE ICCD, pp. 63–66, Oct. 1993.

S. Bhattacharya et al., "Transformations and Resynthesis for Testability of RT–Level Control–Data Path Specifications", IEEE Trans. on (VLSI) Systems, vol. 1, No. 3, Sep. 1993, 15 pp.

H. Chen et al., "Structural and Behavioral Synthesis for Testability Techniques", IEEE Trans. on Cad, vol. 13, No. 6, Jun. 1994.

W. Mao et al., "Improving Gate–Level Fault Coverage by RTL Fault Grading", IEEE ITC pp. 150–159, 1996.

C. Papachristou et al., "Test Synthesis in the Behavioral Domain", IEEE International Test Conference, 1995, pp. 693–702.

B.H. Seiss et al., "Test Point Insertion for Scan-Based BIST", Proc. of European Test Conference, pp. 253–262, 1991.

C.H. Cho et al., "B–algorithm: A Behavior Test Generation Algorithm", IEEE International Test Conference, 1994, pp. 968–979.

X. Gu et al., "Testability Analysis and Improvement from VHDL Behavioral Specifications", Proc. EURO–DAC, pp. 644–649, 1994.

L.J. Avra et al., "High Level Synthesis of Testable Designs: An Overview of University Systems", IEEE TC Test Synthesis Seminar, 1994, pp. 1.1.1.–1.1.8.

S. Dey et al., "Transforming Behavioral Specifications to Facilitate Synthesis of Testable Designs" IEEE ITC pp. 184–193, 1994.

\* cited by examiner

**DOCKET A L A R M** Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

DOCKET

Δ

entity MOORE is -- Moore machine when S2 => port(X, CLOCK: in BIT; Z <= '1'; Z: out BIT); if X = '0' then NEXT\_STATE <= S2; end; architecture BEHAV of MOORE is else type STATE\_TYPE is (S0, S1, S2, S3); NEXT\_STATE <= S3; signal CURRENT\_STATE, NEXT\_STATE: end if; STATE\_TYPE; when S3 => begin Z <= '0'; -- Process to hold combinational logic if X = '0' then COMBIN: process(CURRENT\_STATE, X) NEXT\_STATE <= S3; begin else case CURRENT\_STATE is NEXT\_STATE <= S1; when S0 => end if; Z <= '0'; end case; if X = '0' then end process COMBIN; NEXT\_STATE <= S0; -- Process to hold synchronous elements (flipelse flops) NEXT\_STATE <= S2; SYNCH: process end if; when S1 => begin Z <= '1': wait until CLOCK = '1'; if X = '0' then NEXT\_STATE <= S0; CURRENT\_STATE <= NEXT\_STATE; else end process SYNCH; NEXT\_STATE <= S2; end BEHAV;

# Fig. 2

Find authenticated court documents without watermarks at docketalarm.com.

Fig. 3

**DOCKET A L A R M** Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

### **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.